500V, 30A, 30MHz

# MOSFET Half Bridge Hybrid

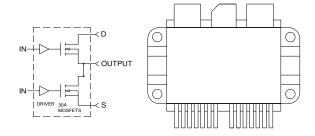

The DRF1400 is a half bridge hybrid containing two high power gate drivers and two power MOSFETs. It was designed to provide the system designer increased flexibility, higher performance and lowered cost over a non-integrated solution. This low parasitic approach, coupled with the Schmitt trigger input, Kelvin signal ground, anti-Ring function Invert and Non-invert select pin provide improved stability and control in Kilowatt to Multi-Kilowatt, High Frequency ISM applications.

#### **FEATURES**

- Switching Frequency: DC TO 30MHz

- Inverting Non-Inverting Select

- Low Pulse Width Distortion

- Single Power Supply (Per Section)

- 1V CMOS Schmitt Trigger Input 1V Hysteresis

- Switching Speed 3-4ns

- B<sub>Vds</sub> = 500V

- I<sub>ds</sub> = 30A avg. Per-section

- R<sub>ds(on)</sub> ≤ .24 Ohm

- P<sub>D</sub> = 550W Per-section

- RoHS Compliant

#### **TYPICAL APPLICATIONS**

- Class D Half Bridge RF Generetors

- Switch Mode Power Amplifiers

- HV Pulse Generators

- Ultrasound Transducer Drivers

- · Acoustic Optical Modulators

## **Driver Absolute Maximum Ratings**

| Symbol            | Parameter             | Ratings   | Unit |

|-------------------|-----------------------|-----------|------|

| V <sub>DD</sub>   | Supply Voltage        | 15        | \/   |

| IN, FN            | Input Single Voltages | 7 to +5.5 | V    |

| I <sub>O PK</sub> | Output Current Peak   | 8         | Α    |

| $T_{JMAX}$        | Operating Temperature | 175       | °C   |

# **Driver Specifications**

| Symbol                     | Parameter                  | Min | Тур  | Max | Unit |

|----------------------------|----------------------------|-----|------|-----|------|

| $V_{_{\mathrm{DD}}}$       | Supply Voltage             | 8   | 12   | 15  | V    |

| IN                         | Input Voltage              | 3   |      | 5   | V    |

| IN <sub>(R)</sub>          | Input Voltage Rising Edge  |     | 3    |     | 20   |

| IN <sub>(F)</sub>          | Input Voltage Falling Edge |     | 3    |     | ns   |

| I <sub>DDQ</sub>           | Quiescent Current          |     | 2    |     | mA   |

| I <sub>o</sub>             | Output Current             |     | 8    |     | Α    |

| C <sub>oss</sub>           | Output Capacitance         |     | 2500 |     | 25   |

| C <sub>iss</sub>           | Input Capacitance          |     | 3    |     | pF   |

| R <sub>IN</sub>            | Input Parallel Resistance  |     | 1    |     | mΩ   |

| V <sub>T(ON)</sub>         | Input, Low to High Out     | 0.8 |      | 1.1 | V    |

| V <sub>T(OFF)</sub>        | Input, High to Low Out     | 1.9 |      | 2.2 | ľ    |

| T <sub>DLY</sub>           | Time Delay (throughput)    |     | 38   |     | ns   |

| t <sub>r</sub>             | Rise Time                  |     | 5    |     |      |

| t <sub>r</sub>             | Fall Time                  |     | 5    |     | ns   |

| $T_{\scriptscriptstyle D}$ | Prop. Delay                |     | 35   |     |      |

### **MOSFET Absolute Maximum Ratings (Per-Section)**

**DRF1400**

| Symbol                                 | Parameter                                       | Min | Тур  | Max | Unit |

|----------------------------------------|-------------------------------------------------|-----|------|-----|------|

| BV <sub>DSS</sub> Drain Source Voltage |                                                 | 500 |      |     | V    |

| I <sub>D</sub>                         | Continuous Drain Current T <sub>HS</sub> = 25°C |     |      | 30  | Α    |

| R <sub>DS(on)</sub>                    | Drain-Source On State Resistance                |     | 0.24 |     | Ω    |

**Dynamic Characteristics (Per-Section)**

| Symbol           | Parameter                    | Min | Тур  | Max | Unit |

|------------------|------------------------------|-----|------|-----|------|

| C <sub>iss</sub> | Input Capacitance            |     | 1800 |     |      |

| C <sub>oss</sub> | Output Capacitance           |     | 335  |     | pF   |

| C <sub>rss</sub> | Reverse Transfer Capacitance |     | 75   |     |      |

**Thermal Characteristics (Total Package)**

| Symbol            | Parameter                                            | Ratings    | Unit  |

|-------------------|------------------------------------------------------|------------|-------|

| $R_{	heta_JC}$    | Junction to Case Thermal Resistance                  | .06        | °C/W  |

| R <sub>ØJHS</sub> | Junction to Heat Sink Thermal Resistance             | .134       | C/VV  |

| T <sub>JSTG</sub> | Storage Junction Temperature                         | -55 to 150 | °C    |

| P <sub>D</sub>    | Maximum Power Dissipation @ T <sub>SINK</sub> = 25°C | 1.1        | KW    |

| P <sub>DC</sub>   | Total Power Dissipation @ T <sub>C</sub> = 25°C      | 2.5        | I NVV |

|                       | Section A and B Output Switching Performance         |      |     |     |     |

|-----------------------|------------------------------------------------------|------|-----|-----|-----|

| Symbol                | Characteristic                                       | Min  | Тур | Max | Тур |

| T <sub>on</sub>       | Leading Edge 10% to 90%                              | 2    | 3   | 4   |     |

| T <sub>OFF</sub>      | Trailing Edge 10% to 90%                             | 45   | TBD | 49  |     |

| T <sub>DLY(ON)</sub>  | Total Throughput Delay Time, ON                      | 47   | TBD | 45  |     |

| T <sub>DLY(OFF)</sub> | Total Throughput Delay Time, OFF                     | 49   | 50  | 51  | ns  |

| $\Delta T_{DLY(ON)}$  | Delta T <sub>ON</sub> Delay between Section A and B  | -0.5 | 0   | 1.5 |     |

| $\Delta T_{DLY(OFF)}$ | Delta T <sub>OFF</sub> Delay between Section A and B | 0    | 0.6 | 1.3 |     |

Microsemi reserves the right to change, without notice, the specifications and information contained herein.

Figure 1, DRF1400 Test Circuit Diagram

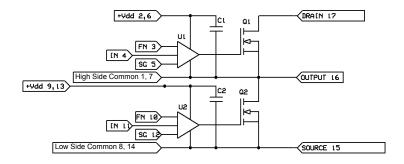

The DRF1400 is configured as a Half Bridge Hybrid incorporating two independent channels consisting of a driver, a high voltage MOSFET and by-pass capacitors. The function of the by-pass capacitors C1 and C2 is to reduce the internal parasitic loop inductance. This coupled with the tight geometry of the hybrid allows optimal gate drive to the MOSFET. This low parasitic approach coupled with the Schmitt trigger input (IN), Kelvin signal ground (SG) and the Anti-Ring function; provide improved stability and control in Kilowatt to Multi-Kilowatt high frequency applications. The IN pin should be referenced to the Kelvin Ground (SG) and is applied to a Schmitt Trigger. The SG pin is a Kelvin return for the IN pin only. The signal is then applied to the intermediate drivers and level shifters; this section contains proprietary circuitry designed specifically for ring abatement. To further increase the utility of the device the driver die and the MOSFET die are adjacent die selected. This provides a very close match in the turn on and propagation delays.

None of the inputs to U1 or U2 of the DRF1400 are isolated for direct connection to a ground referenced power supply or control circuitry. **Isolation appropriate to the application is the responsibility of the end user.** It is imperative that high output currents be restricted to the Drain (17), Source (15) Output (16) and the C3 Bypass (18, 19) connection pins by design. See DRF100 for more information on Driver IC used in the device.

The Function (FN, pin 3 or pin 9) is the invert or non-invert select Pin, it is Internally held high.

| Truth Table * Referenced to SG |      |     |  |  |

|--------------------------------|------|-----|--|--|

| FN (pin 3) IN (pin 4) MOSFET   |      |     |  |  |

| HIGH                           | HIGH | ON  |  |  |

| HIGH                           | LOW  | OFF |  |  |

| LOW                            | HIGH | OFF |  |  |

| LOW                            | LOW  | ON  |  |  |

| Truth Table * Referenced to SG |      |     |  |  |

|--------------------------------|------|-----|--|--|

| FN (pin 9) IN (pin 10) MOSFET  |      |     |  |  |

| HIGH                           | HIGH | ON  |  |  |

| HIGH                           | LOW  | OFF |  |  |

| LOW                            | HIGH | OFF |  |  |

| LOW                            | LOW  | ON  |  |  |

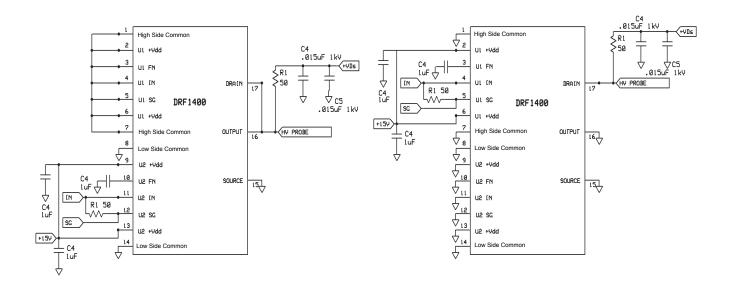

Figure 2, DRF1400 Test Circuit

The test circuit illustrated in Figure 2 was used to evaluate the DRF1400. The input control signal is applied via IN and SG pins using RG188. This provides excellent noise immunity and control of the signal ground currents. The  $\pm V_{DD}$  inputs (pins 2, 6, 8 and 12) should be heavily by-passed by 1uF capacitors as close to the pins as possible. The capacitors used for this function must be capable of supporting the RMS currents and frequency of the gate load. A 50 Ohm (RL) load is used to evaluate the output performance.

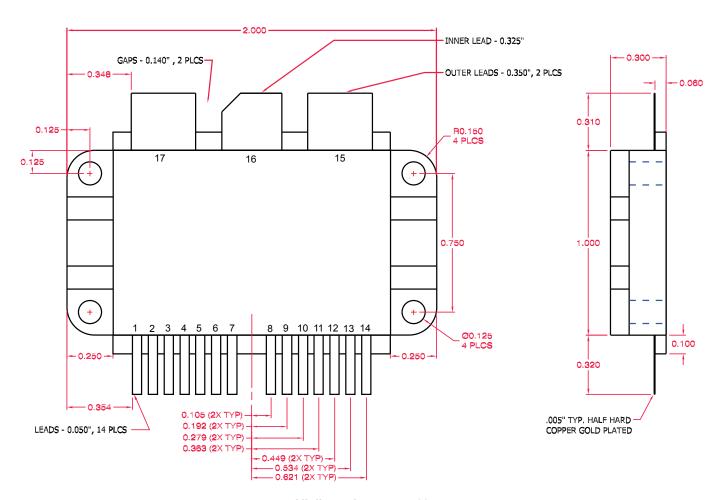

| Pin Assignments |               |  |  |

|-----------------|---------------|--|--|

| Pin 1           | High Side GND |  |  |

| Pin 2           | U1 +Vdd       |  |  |

| Pin 3           | U1 FN         |  |  |

| Pin 4           | U1 IN         |  |  |

| Pin 5           | U1 SG         |  |  |

| Pin 6           | U1 +Vdd       |  |  |

| Pin 7           | High Side GND |  |  |

| Pin 8           | Low Side GND  |  |  |

| Pin 9           | U2 +Vdd       |  |  |

| Pin 10          | U2 FN         |  |  |

| Pin 11          | U2 IN         |  |  |

| Pin 12          | U2 SG         |  |  |

| Pin 13          | U2 +Vdd       |  |  |

| Pin 14          | Low Side GND  |  |  |

| Pin 15          | Source        |  |  |

| Pin 16          | Output        |  |  |

| Pin 17          | Drain         |  |  |

All dimensions are ± .005

Figure 4, DRF1400 Mechanical Outline