# MC68HC11F1 MC68HC11FC0

# **Technical Summary**8-Bit Microcontroller

### 1 Introduction

The MC68HC11F1 is a high-performance member of the M68HC11 family of microcontroller units (MCUs). High-speed expanded systems required the development of this chip with its extra input/output (I/O) ports, an increase in static RAM (one Kbyte), internal chip-select functions, and a non-multiplexed bus which reduces the need for external interface logic. The timer, serial I/O, and analog-to-digital (A/D) converter enable functions similar to those found in the MC68HC11E9.

The MC68HC11FC0 is a low cost, high-speed derivative of the MC68HC11F1. It does not have EEPROM or an analog-to-digital converter. The MC68HC11FC0 can operate at bus speeds as high as six MHz.

This document provides a brief overview of the structure, features, control registers, packaging information and availability of the MC68HC11F1 and MC68HC11FC0. For detailed information on M68HC11 subsystems, programming and the instruction set, refer to the *M68HC11 Reference Manual* (M68HC11RM/AD).

#### 1.1 Features

- MC68HC11 CPU

- 512 Bytes of On-Chip Electrically Erasable Programmable ROM (EEPROM) with Block Protect (MC68HC11F1 only)

- 1024 Bytes of On-Chip RAM (All Saved During Standby)

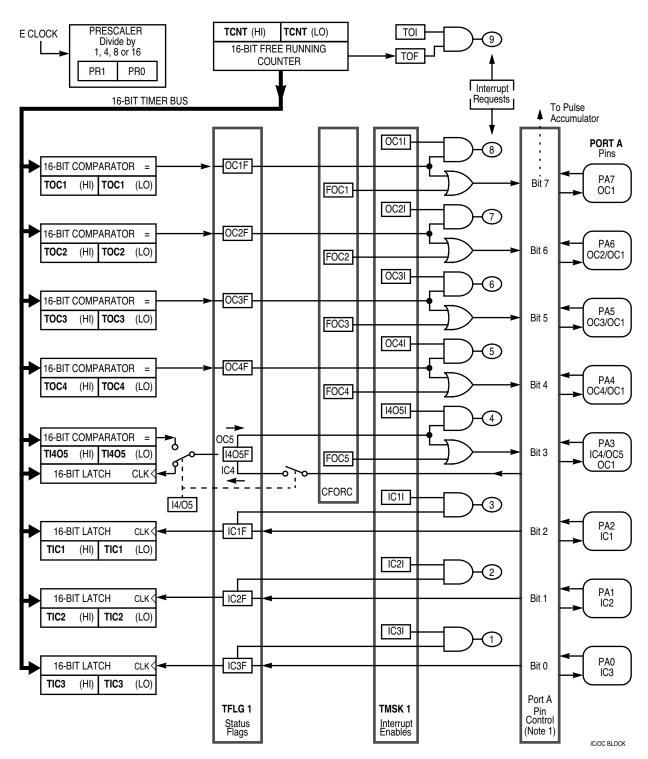

- Enhanced 16-Bit Timer System

- 3 Input Capture (IC) Functions

- 4 Output Compare (OC) Functions

- 4th IC or 5th OC (Software Selectable)

- On-Board Chip-Selects with Clock Stretching

- Real-Time Interrupt Circuit

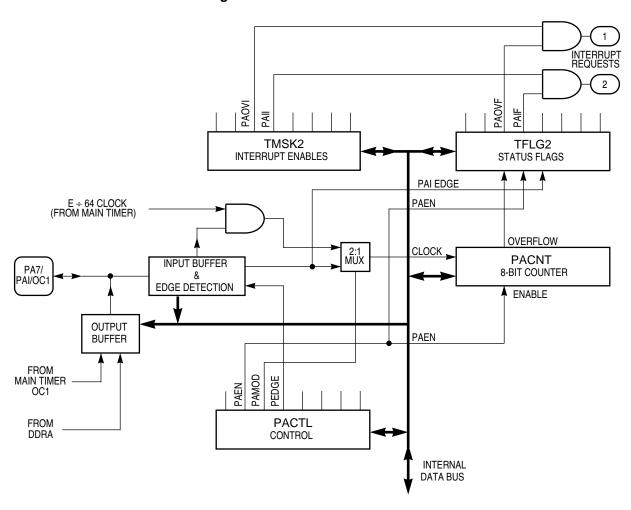

- 8-Bit Pulse Accumulator

- Synchronous Serial Peripheral Interface (SPI)

- Asynchronous Nonreturn to Zero (NRZ) Serial Communication Interface (SCI)

- Power saving STOP and WAIT Modes

- Eight-Channel 8-Bit A/D Converter (MC68HC11F1 only)

- Computer Operating Properly (COP) Watchdog System and Clock Monitor

- Bus Speeds of up to 6 MHz for the MC68HC11FC0 and up to 5 MHz for the MC68HC11F1

- 68-Pin PLCC (MC68HC11F1 only), 64-Pin QFP (MC68HC11FC0 only), and 80-pin TQFP package options

### 1.2 Ordering Information

The following devices all have 1024 bytes of RAM. In addition, the MC68HC11F1 devices have 512 bytes of EEPROM. None of the devices contain on-chip ROM.

Table 1 MC68HC11F1 Standard Device Ordering Information

| Package                    | Temperature       | Frequency | MC Order Number |  |

|----------------------------|-------------------|-----------|-----------------|--|

|                            | 0° to +70°        | 5 MHz     | MC68HC11F1PU5   |  |

|                            |                   | 2 MHz     | MC68HC11F1CPU2  |  |

|                            | -40° to +85°C     | 3 MHz     | MC68HC11F1CPU3  |  |

|                            | -40 to +65 C      | 4 MHz     | MC68HC11F1CPU4  |  |

| 80-Pin Thin Quad Flat Pack |                   | 5 MHz     | MC68HC11F1CPU5  |  |

| (TQFP)<br>(14 mm X 14 mm,  |                   | 2 MHz     | MC68HC11F1VPU2  |  |

| 1.4 mm thick)              | – 40° to + 105° C | 3 MHz     | MC68HC11F1VPU3  |  |

|                            |                   | 4 MHz     | MC68HC11F1VPU4  |  |

|                            |                   | 2 MHz     | MC68HC11F1MPU2  |  |

|                            | – 40° to + 125° C | 3 MHz     | MC68HC11F1MPU3  |  |

|                            |                   | 4 MHz     | MC68HC11F1MPU4  |  |

|                            | 0° to +70°        | 5 MHz     | MC68HC11F1FN5   |  |

|                            |                   | 2 MHz     | MC68HC11F1CFN2  |  |

|                            | – 40° to + 85° C  | 3 MHz     | MC68HC11F1CFN3  |  |

|                            | - 40 10 + 05 0    | 4 MHz     | MC68HC11F1CFN4  |  |

|                            |                   | 5 MHz     | MC68HC11F1CFN5  |  |

| 68-Pin PLCC                |                   | 2 MHz     | MC68HC11F1VFN2  |  |

|                            | – 40° to + 105° C | 3 MHz     | MC68HC11F1VFN3  |  |

|                            |                   | 4 MHz     | MC68HC11F1VFN4  |  |

|                            |                   | 2 MHz     | MC68HC11F1MFN2  |  |

|                            | – 40° to + 125° C | 3 MHz     | MC68HC11F1MFN3  |  |

|                            |                   | 4 MHz     | MC68HC11F1MFN4  |  |

Table 2 MC68HC11F1 Extended Voltage (3.0 to 5.5 V) Device Ordering Information

| Package                    | Temperature   | Frequency | MC Order Number |

|----------------------------|---------------|-----------|-----------------|

| 68-Pin Plastic Leaded Chip | 0° to +70°C   | 3 MHz     | MC68L11F1FN3    |

| Carrier (PLCC)             | −40° to +85°C | 3 MHz     | MC68L11F1CFN3   |

| 80-Pin Thin Quad Flat Pack | 0° to +70°C   | 3 MHz     | MC68L11F1PU3    |

| (TQFP)                     | −40° to +85°C | 3 MHz     | MC68L11F1CPU3   |

Table 3 MC68HC11FC0 Standard Device Ordering Information

| Package                              | Temperature   | Frequency | MC Order Number |

|--------------------------------------|---------------|-----------|-----------------|

| 04 51 0 4 51 4 5 4                   | –40° to +85°C | 4 MHz     | MC68HC11FC0CFU4 |

| 64-Pin Quad Flat Pack<br>(QFP)       | -40 to +65 C  | 5 MHz     | MC68HC11FC0CFU5 |

| (4.1)                                | 0° to 70° C   | 6 MHz     | MC68HC11FC0FU6  |

| 00 8: 7: 0 15: 0                     | –40° to +85°C | 4 MHz     | MC68HC11FC0CPU4 |

| 80-Pin Thin Quad Flat Pack<br>(TQFP) | -40 to +65 C  | 5 MHz     | MC68HC11FC0CPU5 |

| (12.1)                               | 0° to 70° C   | 6 MHz     | MC68HC11FC0PU6  |

### Table 4 MC68HC11FC0 Extended Voltage (3.0 to 5.5 V) Device Ordering Information

| Package                    | Temperature  | Frequency | MC Order Number |

|----------------------------|--------------|-----------|-----------------|

| 64-Pin Quad Flat Pack      |              | 3 MHz     | MC68L11FC0FU3   |

| (QFP)                      | _0° to +70°C | 4 MHz     | MC68L11FC0FU4   |

| 80-Pin Thin Quad Flat Pack | -0 10 +70 C  | 3 MHz     | MC68L11FC0PU3   |

| (TQFP)                     |              | 4 MHz     | MC68L11FC0PU4   |

# **Freescale Semiconductor, Inc.**TABLE OF CONTENTS

| Sec | tion                  |                                                 | Page |

|-----|-----------------------|-------------------------------------------------|------|

| 1   |                       | Introduction                                    | 1    |

|     | 1.1                   | Features                                        |      |

|     | l.2<br>l.3            | Ordering Information                            |      |

| 2   |                       | Pin Assignments and Signal Descriptions         | 8    |

|     | 2.1                   | MC68HC11F1 Pin Assignments                      | _    |

|     | 2.2                   | MC68HC11FC0 Pin Assignments                     |      |

|     | 2.3                   | Pin Descriptions                                |      |

| 3   |                       | Control Registers                               | 14   |

|     | 3.1                   | MC68HC11F1 Control Registers                    |      |

| _   | 3.2                   | MC68HC11FC0 Control Registers                   |      |

| 4   |                       | Operating Modes and System Initialization       | 18   |

|     | ŀ.1<br>ŀ.2            | Operating Modes Memory Maps                     |      |

|     | 1.3                   | System Initialization Registers                 |      |

| 5   |                       | Resets and Interrupts                           | 25   |

| _   | 5.1                   | Interrupt Sources                               | _    |

| 5   | 5.2                   | Reset and Interrupt Registers                   | 26   |

| 6   |                       | Electrically Erasable Programmable ROM          | 29   |

| _   | 6.1                   | EEPROM Operation                                |      |

|     | 6.2<br>6.3            | EEPROM Registers EEPROM Programming and Erasure |      |

|     | 5.4                   | CONFIG Register Programming                     |      |

| 7   |                       | Parallel Input/Output                           | 33   |

|     | <b>7</b> .1           | Port A                                          |      |

|     | 7.2                   | Port B                                          |      |

|     | 7.3<br>7.4            | Port C                                          |      |

| -   | . <del>4</del><br>7.5 | Port E                                          |      |

|     | 7.6                   | Port F                                          | 33   |

| -   | 7.7                   | Port G                                          |      |

|     | 7.8                   | Parallel I/O Registers                          |      |

| 8   |                       | Chip-Selects                                    | 38   |

|     | 3.1<br>3.2            | Chip-Select Operation                           |      |

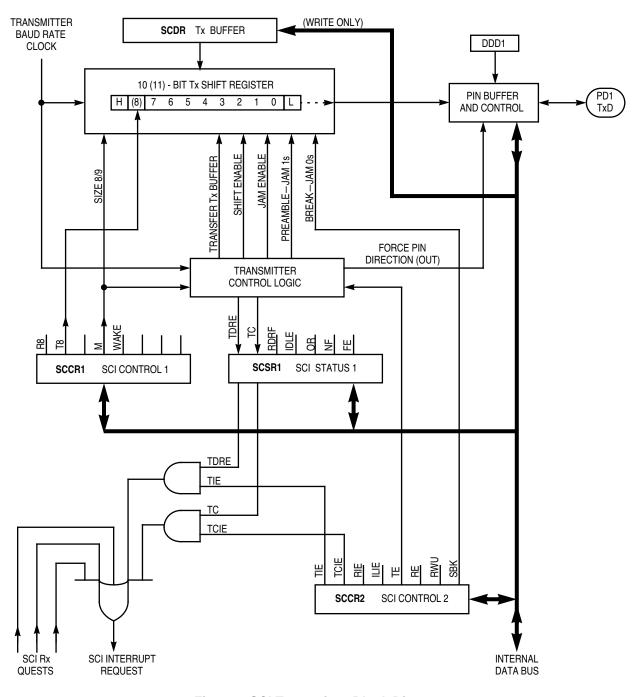

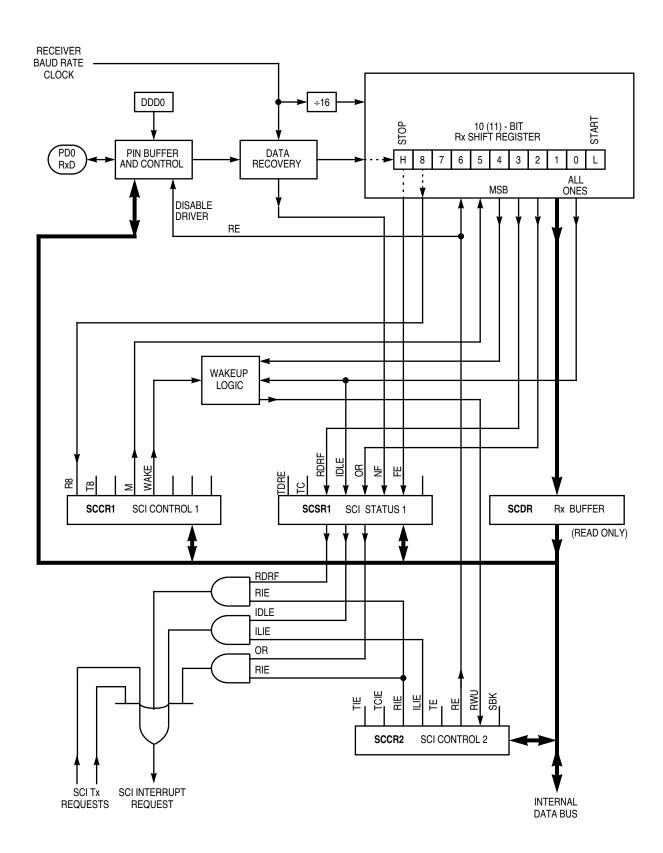

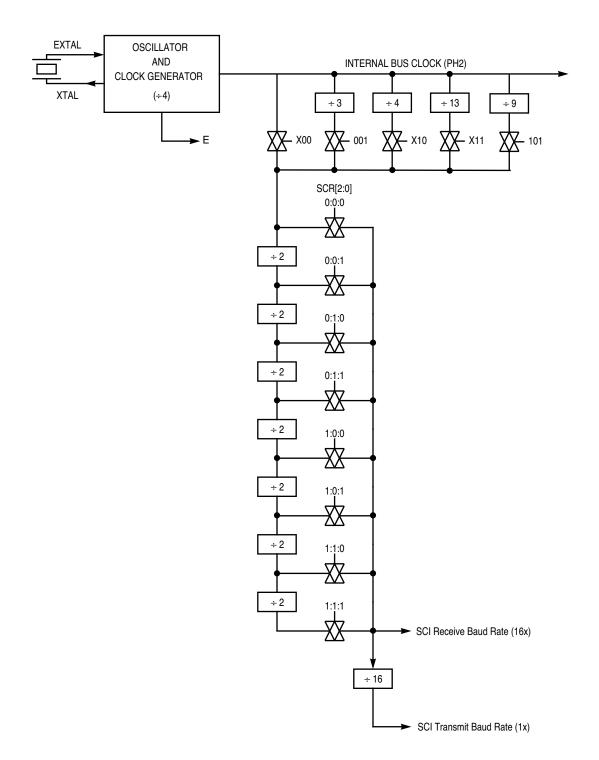

| 9   |                       | Serial Communications Interface (SCI)           | 42   |

| _   | 9.1                   | SCI Block Diagrams                              |      |

|     | 9.2                   | SCI Registers                                   |      |

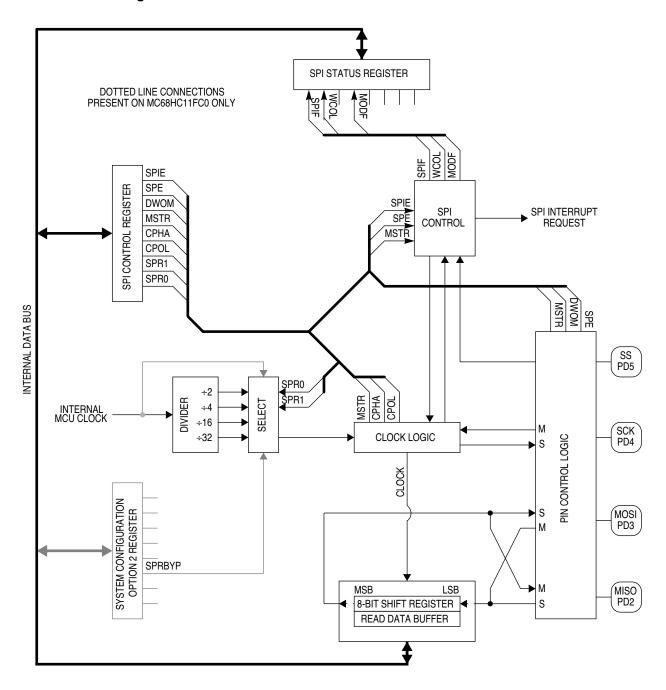

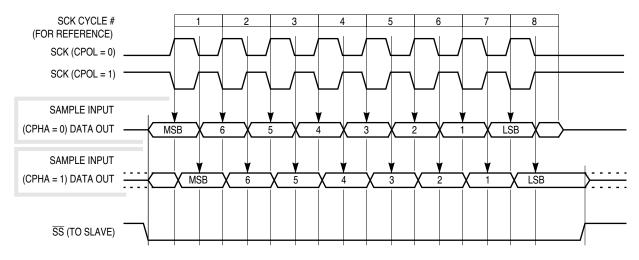

| 10  |                       | Serial Peripheral Interface                     | 49   |

|     | 0.1                   | SPI Block Diagram                               |      |

|     | 0.2                   | SPI Registers                                   |      |

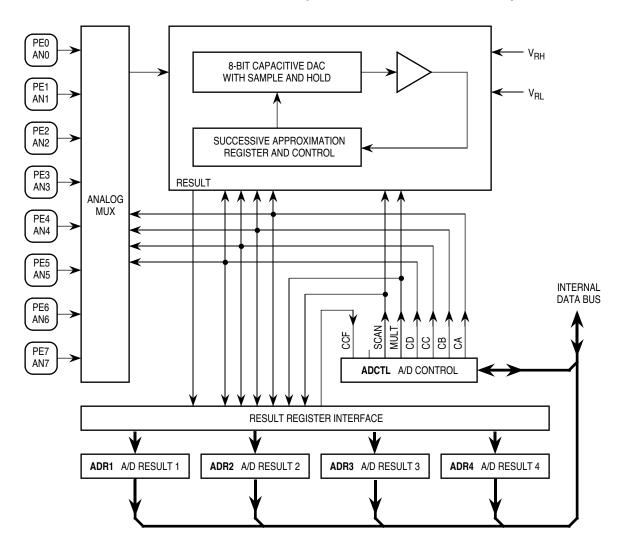

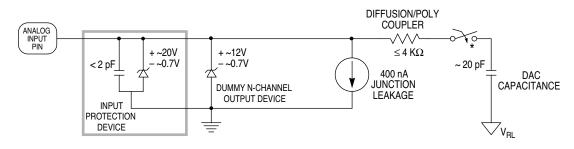

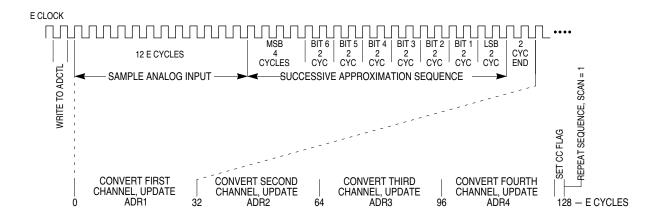

| 11  |                       | Analog-to-Digital Converter                     | 53   |

|     | 1.1<br>1.2            | Input Pins Conversion Sequence                  |      |

|     | 1.2                   | A/D Registers                                   |      |

| 12  | -                     | Main Timer                                      | 57   |

|     | 2.1                   | Timer Operation                                 |      |

|     | 2.2                   | Timer Registers                                 |      |

| 13  |                       | Pulse Accumulator                               | 64   |

|     | 3.1                   | Pulse Accumulator Block Diagram                 |      |

| 1   | 3.2                   | Pulse Accumulator Registers                     | 64   |

# **Freescale Semiconductor, Inc.**REGISTER INDEX

| Register |                                              | Address | Page       |

|----------|----------------------------------------------|---------|------------|

| ADCTL    | A/D Control/Status                           | \$1030  | 55         |

| BAUD     | Baud Rate                                    | \$102B  | 44         |

| BPROT    | Block Protect                                | \$1035  | 29         |

| CFORC    | Timer Force Compare                          | \$100B  | 59         |

| CONFIG   | EEPROM Mapping, COP, EEPROM Enables          | \$103F  | 24, 28, 30 |

| COPRST   | Arm/Reset COP Timer Circuitry                | \$103A  | 27         |

| CSCTL    | Chip-Select Control                          | \$105D  | 39         |

| CSGADR   | General-Purpose Chip-Select Address Register | \$105E  | 40         |

| CSGSIZ   | General-Purpose Chip-Select Size Register    | \$105F  | 40         |

| CSSTRH   | Clock Stretching                             | \$105C  | 38         |

| DDRA     | Port A Data Register                         | \$1001  | 34         |

| DDRC     | Data Direction Register for Port C           | \$1007  | 35         |

| DDRD     | Data Direction Register for Port D           | \$1009  | 36         |

|          | Data Direction Register for Port G           |         |            |

|          | Highest Priority Interrupt and Miscellaneous |         |            |

|          | RAM and I/O Mapping                          |         |            |

|          | Output Compare 1 Data                        |         |            |

|          | Output Compare 1 Mask                        |         |            |

|          | System Configuration Option Register 2       |         |            |

|          | System Configuration Options                 |         |            |

|          | Pulse Accumulator Count                      |         |            |

|          | Pulse Accumulator Control                    |         |            |

|          | Port A Data                                  |         | ,          |

| PORTB    | Port B Data                                  | \$1004  | 35         |

| PORTC    | Port C Data                                  | \$1006  | 35         |

| PORTD    | Port D Data                                  | \$1008  | 36         |

| PORTE    | Port E Data                                  | \$100A  | 36         |

| PORTF    | Port F Data                                  | \$1005  | 35         |

| PORTG    | Port G Data                                  | \$1002  | 34         |

| PPROG    | EEPROM Programming Control                   | \$103B  | 30         |

|          | SCI Control 1                                |         |            |

| SCCR2    | SCI Control 2                                | \$102D  | 46         |

| SCDR     | Serial Communications Data Register          | \$102F  | 48         |

|          | SCI Status                                   |         |            |

| SPCR     | Serial Peripheral Control                    | \$1028  | 50         |

| SPDR     | SPI Data                                     | \$102A  | 51         |

| SPSR     | Serial Peripheral Status                     | \$1029  | 51         |

|          | Timer Count                                  |         |            |

|          | Timer Control 1                              |         |            |

| TCTL2    | Timer Control 2                              | \$1021  | 61         |

| TEST1    | Factory Test                                 | \$103E  | 24         |

|          | Timer Interrupt Flag 1                       |         |            |

| TFLG2    | Timer Interrupt Flag 2                       | \$1025  | 62, 65     |

|          | Timer Input Capture 4/Output Compare 5       |         |            |

|          | Timer Input Capture                          |         |            |

|          | Timer Interrupt Mask 1                       |         |            |

|          | Timer Interrupt Mask 2                       |         |            |

|          | Timer Output Compare                         |         |            |

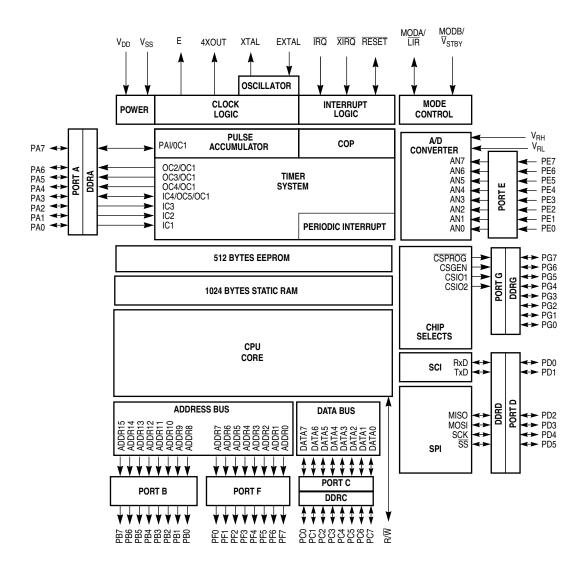

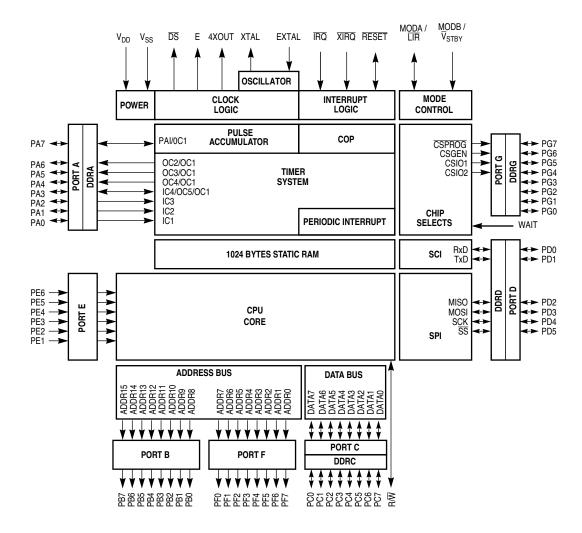

### 1.3 Block Diagrams

Figure 1 MC68HC11F1 Block Diagram

Figure 2 MC68HC11FC0 Block Diagram

### 2 Pin Assignments and Signal Descriptions

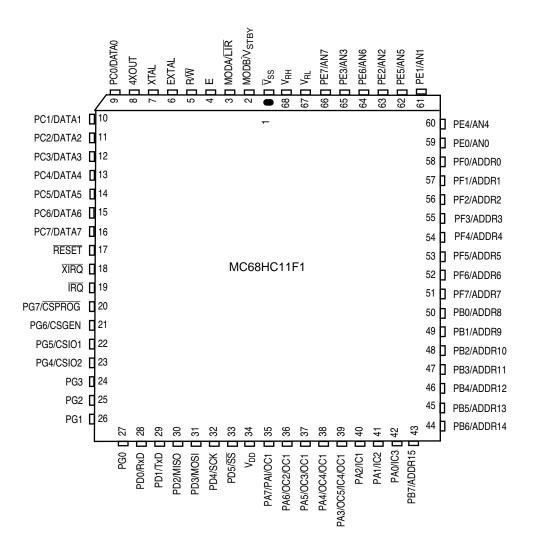

### 2.1 MC68HC11F1 Pin Assignments

Figure 3 MC68HC11F1 68-Pin PLCC Pin Assignments

Figure 4 Pin Assignments for the MC68HC11F1 80-Pin QFP

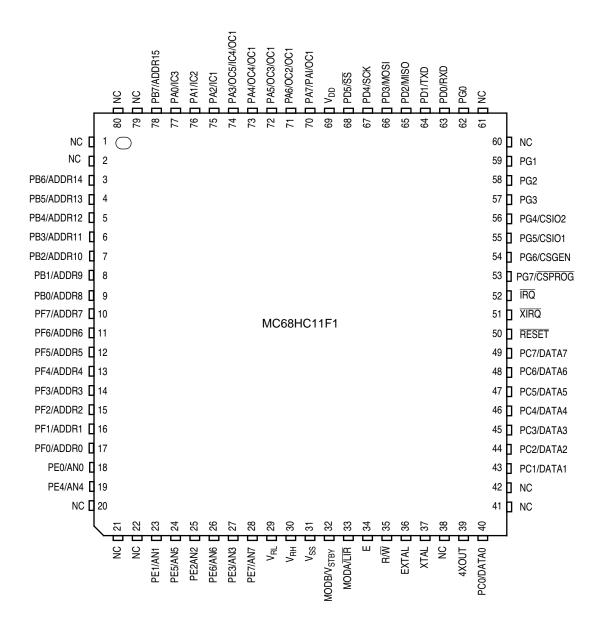

### 2.2 MC68HC11FC0 Pin Assignments

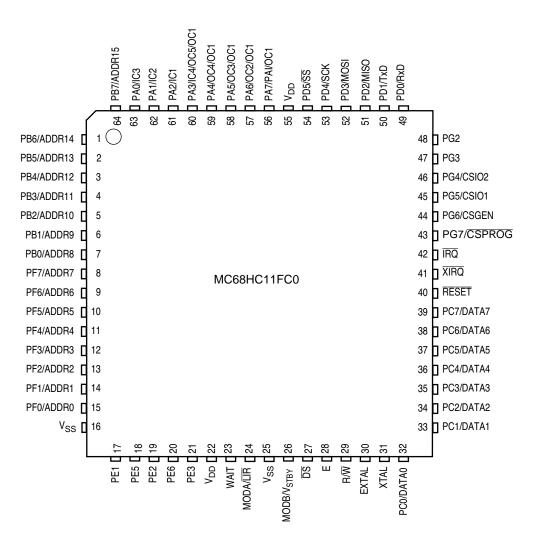

Figure 5 MC68HC11FC0 64-Pin QFP Pin Assignments

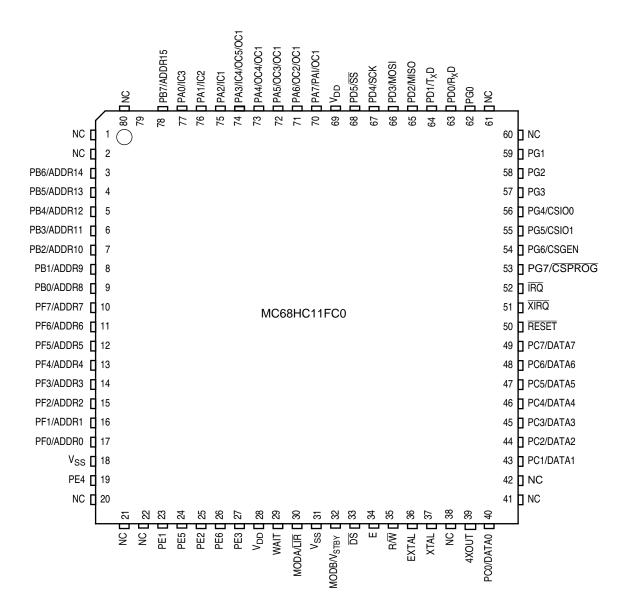

Figure 6 MC68HC11FC0 80-Pin TQFP Pin Assignments

### 2.3 Pin Descriptions

### $V_{DD}$ and $V_{SS}$

V<sub>DD</sub> is the positive power input to the MCU, and V<sub>SS</sub> is ground.

#### **RESET**

This active-low input initializes the MCU to a known startup state. It also acts as an open-drain output to indicate that an internal failure has been detected in either the clock monitor or the COP watchdog circuits.

### **XTAL and EXTAL**

These two pins provide the interface for either a crystal or a CMOS-compatible clock to drive the internal clock circuitry. The frequency applied to these pins is four times the desired bus frequency (E clock).

Ε

This pin provides an output for the E clock, the basic timing reference signal for the bus circuitry. The address bus is active when E is low, and the data bus is active when E is high.

#### $\overline{\mathsf{DS}}$

The data strobe output is the inverted E clock. DS is present on the MC68HC11FC0 only.

#### WAIT

This input is used to stretch the bus cycle to accommodate slower devices. The MCU samples the logic level at this pin on the rising edge of E clock. If it is high, the MCU holds the E clock high for the next four EXTAL clock cycles. If it is low, the E clock responds normally, going low two EXTAL cycles later. The WAIT pin is present on the MC68HC11FC0 only.

#### **4XOUT**

This pin provides a buffered oscillator signal to drive another M68HC11 MCU. The 4XOUT pin is not present on the 64-pin QFP MC68HC11FC0 package.

#### **IRQ**

This active-low input provides a means of generating asynchronous, maskable interrupt requests for the CPU.

#### XIRQ

This interrupt request input can be made non-maskable by clearing the X bit in the MCU's condition code register.

#### MODA/LIR and MODB/VSTBY

The logic level applied to the MODA and MODB pins at reset determines the MCU's opreating mode (see **Table 7** in **4 Operating Modes and System Initialization**). After reset, MODA functions as  $\overline{\text{LIR}}$ , an open-drain output that indicates the start of an instruction cycle. MODB functions as  $V_{\text{STBY}}$ , providing a backup battery to maintain the contents of RAM when  $V_{\text{DD}}$  falls.

### R/W

In expanded and test modes, R/W indicates the direction of transfers on the external data bus.

# $V_{RH}$ and $V_{RL}$

These pins provide the reference voltage for the analog-to-digital converter. Use bypass capacitors to minimize noise on these signals. Any noise on V<sub>RH</sub> and V<sub>RL</sub> will directly affect A/D accuracy. These pins are not present on the MC68HC11FC0.

### **Port Signals**

On the MC68HC11F1, 54 pins are arranged into six 8-bit ports (ports A, B, C, E, F, and G) and one 6-bit port (port D). On the MC68HC11FC0, either 52 or 49 pins are available, depending on the package. General-purpose I/O port signals are discussed briefly in the following pragraphs. For additional information, refer to **7 Parallel Input/Output**.

#### **Port A Pins**

Port A is an 8-bit general-purpose I/O port (PA[7:0]) with a data register (PORTA) and a data direction register (DDRA). Port A pins share functions with the 16-bit timer system. Out of reset, PA[7:0] are general-purpose high-impedance inputs.

#### **Port B Pins**

Port B is an 8-bit output-only port. In single-chip modes, port B pins are general-purpose output pins (PB[7:0]). In expanded modes, port B pins act as the high-order address lines ADDR[15:8].

#### **Port C Pins**

Port C is an 8-bit general-purpose I/O port with a data register (PORTC) and a data direction register (DDRC). In single-chip modes, port C pins are general-purpose I/O pins PC[7:0]. In expanded modes, port C pins are configured as data bus pins DATA[7:0].

#### **Port D Pins**

Port D is a 6-bit general-purpose I/O port with a data register (PORTD) and a data direction register (DDRD). The six port D lines PD[5:0] can be used for general-purpose I/O or for the serial communications interface (SCI) or serial peripheral interface (SPI) subsystems.

#### **Port E Pins**

Port E is an 8-bit input-only port that is also used as the analog input port for the analog-to-digital converter. Port E pins that are not used for the A/D system can be used as general-purpose inputs. However, PORTE should not be read during the sample portion of an A/D conversion sequence.

### **NOTE**

The A/D system is not available on the MC68HC11FC0. PE7 and PE0 are not available on the 80-pin MC68HC11FC0. PE7, PE4, and PE0 are not available on the 64-pin MC68HC11FC0.

### **Port F Pins**

Port F is an 8-bit output-only port. In single-chip mode, port F pins are general-purpose output pins PF[7:0]. In expanded mode, port F pins act as the low-order address outputs ADDR[7:0].

### **Port G Pins**

Port G is an 8-bit general-purpose I/O port. When enabled, four chip select signals are alternate functions of PG[7:4].

### NOTE

PG[1:0] are not available on the 64-pin MC68HC11FC0.

# **3 Control Registers**

The MC68HC11F1 and MC68HC11FC0 control registers determine most of the system's operating characteristics. They occupy a 96-byte relocatable memory block. Their names and bit mnemonics are summarized in the following table. Addresses shown are the default locations out of reset.

### 3.1 MC68HC11F1 Control Registers

### Table 5 MC68HC11F1 Register and Control Bit Assignments

|        |        |       |       | - 5   |       |       |       |       |               |

|--------|--------|-------|-------|-------|-------|-------|-------|-------|---------------|

|        | Bit 7  | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 | 7             |

| \$1000 | PA7    | PA6   | PA5   | PA4   | PA3   | PA2   | PA1   | PA0   | PORTA         |

| \$1001 | DDA7   | DDA6  | DDA5  | DDA4  | DDA3  | DDA2  | DDA1  | DDA0  | DDRA          |

| \$1002 | PG7    | PG6   | PG5   | PG4   | PG3   | PG2   | PG1   | PG0   | PORTG         |

| \$1003 | DDG7   | DDG6  | DDG5  | DDG4  | DDG3  | DDG2  | DDG1  | DDG0  | DDRG          |

| \$1004 | PB7    | PB6   | PB5   | PB4   | PB3   | PB2   | PB1   | PB0   | PORTB         |

| \$1005 | PF7    | PF6   | PF5   | PF4   | PF3   | PF2   | PF1   | PF0   | PORTF         |

| \$1006 | PC7    | PC6   | PC5   | PC4   | PC3   | PC2   | PC1   | PC0   | PORTC         |

| \$1007 | DDC7   | DDC6  | DDC5  | DDC4  | DDC3  | DDC2  | DDC1  | DDC0  | DDRC          |

| \$1008 | 0      | 0     | PD5   | PD4   | PD3   | PD2   | PD1   | PD0   | PORTD         |

| \$1009 | 0      | 0     | DDD5  | DDD4  | DDD3  | DDD2  | DDD1  | DDD0  | DDRD          |

| \$100A | PE7    | PE6   | PE5   | PE4   | PE3   | PE2   | PE1   | PE0   | PORTE         |

| \$100B | FOC1   | FOC2  | FOC3  | FOC4  | FOC5  | 0     | 0     | 0     | CFORC         |

| \$100C | OC1M7  | OC1M6 | OC1M5 | OC1M4 | OC1M3 | 0     | 0     | 0     | OC1M          |

| \$100D | OC1D7  | OC1D6 | OC1D5 | OC1D4 | OC1D3 | 0     | 0     | 0     | OC1D          |

| \$100E | Bit 15 | 14    | 13    | 12    | 11    | 10    | 9     | Bit 8 | TCNT (High)   |

| \$100F | Bit 7  | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 | TCNT (Low)    |

| \$1010 | Bit 15 | 14    | 13    | 12    | 11    | 10    | 9     | Bit 8 | TIC1 (High)   |

| \$1011 | Bit 7  | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 | TIC1 (Low)    |

| \$1012 | Bit 15 | 14    | 13    | 12    | 11    | 10    | 9     | Bit 8 | TIC2 (High)   |

| \$1013 | Bit 7  | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 | TIC2 (Low)    |

| \$1014 | Bit 15 | 14    | 13    | 12    | 11    | 10    | 9     | Bit 8 | TIC3 (High)   |

| \$1015 | Bit 7  | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 | TIC3 (Low)    |

| \$1016 | Bit 15 | 14    | 13    | 12    | 11    | 10    | 9     | Bit 8 | TOC1 (High)   |

| \$1017 | Bit 7  | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 | TOC1 (Low)    |

| \$1018 | Bit 15 | 14    | 13    | 12    | 11    | 10    | 9     | Bit 8 | TOC2 (High)   |

| \$1019 | Bit 7  | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 | TOC2 (Low)    |

| \$101A | Bit 15 | 14    | 13    | 12    | 11    | 10    | 9     | Bit 8 | TOC3 (High)   |

| \$101B | Bit 7  | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 | TOC3 (Low)    |

| \$101C | Bit 15 | 14    | 13    | 12    | 11    | 10    | 9     | Bit 8 | TOC4 (High)   |

| \$101D | Bit 7  | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 | TOC4 (Low)    |

| \$101E | Bit 15 | 14    | 13    | 12    | 11    | 10    | 9     | Bit 8 | TI4/O5 (High) |

| \$101F | Bit 7  | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 | TI4/O5 (Low)  |

| \$1020 | OM2    | OL2   | OM3   | OL3   | OM4   | OL4   | OM5   | OL5   | TCTL1         |

| \$1021 | EDG4B  | EDG4A | EDG1B | EDG1A | EDG2B | EDG2A | EDG3B | EDG3A | TCTL2         |

|        |        | •     |       |       | •     | •     |       |       | _             |

# Table 5 MC68HC11F1 Register and Control Bit Assignments (Continued)

| \$1022 OC1I OC2I OC3I OC4I I4/O5I IC1I IC2I IC3I TMS \$1023 OC1F OC2F OC3F OC4F I4/O5F IC1F IC2F IC3F TFL \$1024 TOI RTII PAOVI PAII 0 0 PR1 PR0 TMS \$1025 TOF RTIF PAOVF PAIF 0 0 0 TFL \$1026 0 PAEN PAMOD PEDGE 0 I4/O5 RTR1 RTR0 PAC \$1027 Bit 7 6 5 4 3 2 1 Bit 0 PAC | G1<br>GK2<br>G2<br>CTL<br>CNT<br>CR |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|

| \$1024 TOI RTII PAOVI PAII 0 0 PR1 PR0 TMS \$1025 TOF RTIF PAOVF PAIF 0 0 0 TFL \$1026 0 PAEN PAMOD PEDGE 0 I4/05 RTR1 RTR0 PAC                                                                                                                                              | GK2<br>G2<br>CTL<br>CNT<br>CR       |

| \$1025 TOF RTIF PAOVF PAIF 0 0 0 0 TFL \$1026 0 PAEN PAMOD PEDGE 0 14/05 RTR1 RTR0 PAC                                                                                                                                                                                       | G2<br>CTL<br>CNT<br>CR<br>CR        |

| \$1026 0 PAEN PAMOD PEDGE 0 I4/05 RTR1 RTR0 PAC                                                                                                                                                                                                                              | TL<br>:NT<br>:R<br>:R               |

|                                                                                                                                                                                                                                                                              | CNT<br>CR<br>SR                     |

| \$1027   Bit 7   6   5   4   2   2   4   Bit 0   BAC                                                                                                                                                                                                                         | R<br>R                              |

| \$1027 Bit 7 6 5 4 3 2 1 Bit 0 PAC                                                                                                                                                                                                                                           | R                                   |

| \$1028 SPIE SPE DWOM MSTR CPOL CPHA SPR1 SPR0 SPC                                                                                                                                                                                                                            |                                     |

| \$1029 SPIF WCOL 0 MODF 0 0 0 SPS                                                                                                                                                                                                                                            | R                                   |

| \$102A Bit 7 6 5 4 3 2 1 Bit 0 SPD                                                                                                                                                                                                                                           |                                     |

| \$102B TCLR SCP2 SCP1 SCP0 RCKB SCR2 SCR1 SCR0 BAU                                                                                                                                                                                                                           | ID                                  |

| \$102C R8 T8 0 M WAKE 0 0 SCC                                                                                                                                                                                                                                                | R1                                  |

| \$102D TIE TCIE RIE ILIE TE RE RWU SBK SCO                                                                                                                                                                                                                                   | R2                                  |

| \$102E TDRE TC RDRF IDLE OR NF FE 0 SCS                                                                                                                                                                                                                                      | R                                   |

| \$102F Bit 7 6 5 4 3 2 1 Bit 0 SCD                                                                                                                                                                                                                                           | R                                   |

| \$1030 CCF 0 SCAN MULT CD CC CB CA ADO                                                                                                                                                                                                                                       | TL                                  |

| \$1031 Bit 7 6 5 4 3 2 1 Bit 0 ADR                                                                                                                                                                                                                                           | R1                                  |

| \$1032 Bit 7 6 5 4 3 2 1 Bit 0 ADR                                                                                                                                                                                                                                           | 22                                  |

| \$1033 Bit 7 6 5 4 3 2 1 Bit 0 ADR                                                                                                                                                                                                                                           | 23                                  |

| \$1034 Bit 7 6 5 4 3 2 1 Bit 0 ADR                                                                                                                                                                                                                                           | 84                                  |

| \$1035 0 0 PTCON BPRT3 BPRT2 BPRT1 BPRT0 BPR                                                                                                                                                                                                                                 | OT                                  |

| \$1036 Res                                                                                                                                                                                                                                                                   | erved                               |

| \$1037 Res                                                                                                                                                                                                                                                                   | erved                               |

| \$1038 GWOM CWOM CLK4X LIRDV 0 SPRBYP 0 0 OPT                                                                                                                                                                                                                                | 2                                   |

| \$1039 0 0 IRQE DLY CME FCME CR1 CR0 OPT                                                                                                                                                                                                                                     | ION                                 |

| \$103A Bit 7 6 5 4 3 2 1 Bit 0 COF                                                                                                                                                                                                                                           | PRST                                |

| \$103B ODD EVEN 0 BYTE ROW ERASE EELAT EEPGM PPR                                                                                                                                                                                                                             | OG                                  |

| \$103C RBOOT SMOD MDA IRV PSEL3 PSEL2 PSEL1 PSEL0 HPR                                                                                                                                                                                                                        | RIO                                 |

| \$103D RAM3 RAM2 RAM1 RAM0 REG3 REG2 REG1 REG0 INIT                                                                                                                                                                                                                          |                                     |

| \$103E TILOP 0 OCCR CBYP DISR FCM FCOP 0 TES                                                                                                                                                                                                                                 | T1                                  |

| \$103F                                                                                                                                                                                                                                                                       | NFIG                                |

| \$1040 Res                                                                                                                                                                                                                                                                   | erved                               |

| to<br>\$105B Res                                                                                                                                                                                                                                                             | erved                               |

|                                                                                                                                                                                                                                                                              | TRH                                 |

| \$105D   I01EN   I01PL   I02EN   I02PL   GCSPR   PCSEN   PSIZA   PSIZB   CSC                                                                                                                                                                                                 |                                     |

|                                                                                                                                                                                                                                                                              | SADR                                |

| \$105F   I01AV   I02AV   0   GNPOL   GAVLD   GSIZA   GSIZB   GSIZC   CSG                                                                                                                                                                                                     |                                     |

# 3.2 MC68HC11FC0 Control Registers

### Table 6 MC68HC11FC0 Register and Control Bit Assignments

| <b>0</b> 4000 | Bit 7  | 6     | 5     | 4     | 3      | 2     | 1     | Bit 0 | 70074         |

|---------------|--------|-------|-------|-------|--------|-------|-------|-------|---------------|

| \$1000        | PA7    | PA6   | PA5   | PA4   | PA3    | PA2   | PA1   | PA0   | PORTA         |

| \$1001        | DDA7   | DDA6  | DDA5  | DDA4  | DDA3   | DDA2  | DDA1  | DDA0  | DDRA          |

| \$1002        | PG7    | PG6   | PG5   | PG4   | PG3    | PG2   | PG1   | PG0   | PORTG         |

| \$1003        | DDG7   | DDG6  | DDG5  | DDG4  | DDG3   | DDG2  | DDG1  | DDG0  | DDRG          |

| \$1004        | PB7    | PB6   | PB5   | PB4   | PB3    | PB2   | PB1   | PB0   | PORTB         |

| \$1005        | PF7    | PF6   | PF5   | PF4   | PF3    | PF2   | PF1   | PF0   | PORTF         |

| \$1006        | PC7    | PC6   | PC5   | PC4   | PC3    | PC2   | PC1   | PC0   | PORTC         |

| \$1007        | DDC7   | DDC6  | DDC5  | DDC4  | DDC3   | DDC2  | DDC1  | DDC0  | DDRC          |

| \$1008        | 0      | 0     | PD5   | PD4   | PD3    | PD2   | PD1   | PD0   | PORTD         |

| \$1009        | 0      | 0     | DDD5  | DDD4  | DDD3   | DDD2  | DDD1  | DDD0  | DDRD          |

| \$100A        | PE7    | PE6   | PE5   | PE4   | PE3    | PE2   | PE1   | PE0   | PORTE         |

| \$100B        | FOC1   | FOC2  | FOC3  | FOC4  | FOC5   | 0     | 0     | 0     | CFORC         |

| \$100C        | OC1M7  | OC1M6 | OC1M5 | OC1M4 | OC1M3  | 0     | 0     | 0     | OC1M          |

| \$100D        | OC1D7  | OC1D6 | OC1D5 | OC1D4 | OC1D3  | 0     | 0     | 0     | OC1D          |

| \$100E        | Bit 15 | 14    | 13    | 12    | 11     | 10    | 9     | Bit 8 | TCNT (High)   |

| \$100F        | Bit 7  | 6     | 5     | 4     | 3      | 2     | 1     | Bit 0 | TCNT (Low)    |

| \$1010        | Bit 15 | 14    | 13    | 12    | 11     | 10    | 9     | Bit 8 | TIC1 (High)   |

| \$1011        | Bit 7  | 6     | 5     | 4     | 3      | 2     | 1     | Bit 0 | TIC1 (Low)    |

| \$1012        | Bit 15 | 14    | 13    | 12    | 11     | 10    | 9     | Bit 8 | TIC2 (High)   |

| \$1013        | Bit 7  | 6     | 5     | 4     | 3      | 2     | 1     | Bit 0 | TIC2 (Low)    |

| \$1014        | Bit 15 | 14    | 13    | 12    | 11     | 10    | 9     | Bit 8 | TIC3 (High)   |

| \$1015        | Bit 7  | 6     | 5     | 4     | 3      | 2     | 1     | Bit 0 | TIC3 (Low)    |

| \$1016        | Bit 15 | 14    | 13    | 12    | 11     | 10    | 9     | Bit 8 | TOC1 (High)   |

| \$1017        | Bit 7  | 6     | 5     | 4     | 3      | 2     | 1     | Bit 0 | TOC1 (Low)    |

| \$1018        | Bit 15 | 14    | 13    | 12    | 11     | 10    | 9     | Bit 8 | TOC2 (High)   |

| \$1019        | Bit 7  | 6     | 5     | 4     | 3      | 2     | 1     | Bit 0 | TOC2 (Low)    |

| \$101A        | Bit 15 | 14    | 13    | 12    | 11     | 10    | 9     | Bit 8 | TOC3 (High)   |

| \$101B        | Bit 7  | 6     | 5     | 4     | 3      | 2     | 1     | Bit 0 | TOC3 (Low)    |

| \$101C        | Bit 15 | 14    | 13    | 12    | 11     | 10    | 9     | Bit 8 | TOC4 (High)   |

| \$101D        | Bit 7  | 6     | 5     | 4     | 3      | 2     | 1     | Bit 0 | TOC4 (Low)    |

| \$101E        | Bit 15 | 14    | 13    | 12    | 11     | 10    | 9     | Bit 8 | TI4/O5 (High) |

| \$101F        | Bit 7  | 6     | 5     | 4     | 3      | 2     | 1     | Bit 0 | TI4/O5 (Low)  |

| \$1020        | OM2    | OL2   | OM3   | OL3   | OM4    | OL4   | OM5   | OL5   | TCTL1         |

| \$1021        | EDG4B  | EDG4A | EDG1B | EDG1A | EDG2B  | EDG2A | EDG3B | EDG3A | TCTL2         |

| \$1022        | OC1I   | OC2I  | OC3I  | OC4I  | I4/O5I | IC1I  | IC2I  | IC3I  | TMSK1         |

| \$1023        | OC1F   | OC2F  | OC3F  | OC4F  | 14/O5F | IC1F  | IC2F  | IC3F  | TFLG1         |

| \$1024        | TOI    | RTII  | PAOVI | PAII  | 0      | 0     | PR1   | PR0   | TMSK2         |

| \$1025        | TOF    | RTIF  | PAOVF | PAIF  | 0      | 0     | 0     | 0     | TFLG2         |

|               |        |       | ·     |       |        |       |       | ·     | _             |

# Table 6 MC68HC11FC0 Register and Control Bit Assignments (Continued)

|              | Bit 7 | 6     | 5     | 4     | 3     | 2      | 1     | Bit 0 |                   |

|--------------|-------|-------|-------|-------|-------|--------|-------|-------|-------------------|

| \$1026       | 0     | PAEN  | PAMOD | PEDGE | 0     | 14/05  | RTR1  | RTR0  | PACTL             |

| \$1027       | Bit 7 | 6     | 5     | 4     | 3     | 2      | 1     | Bit 0 | PACNT             |

| \$1028       | SPIE  | SPE   | DWOM  | MSTR  | CPOL  | СРНА   | SPR1  | SPR0  | SPCR              |

| \$1029       | SPIF  | WCOL  | 0     | MODF  | 0     | 0      | 0     | 0     | SPSR              |

| \$102A       | Bit 7 | 6     | 5     | 4     | 3     | 2      | 1     | Bit 0 | SPDR              |

| \$102B       | TCLR  | SCP2  | SCP1  | SCP0  | RCKB  | SCR2   | SCR1  | SCR0  | BAUD              |

| \$102C       | R8    | Т8    | 0     | М     | WAKE  | 0      | 0     | 0     | SCCR1             |

| \$102D       | TIE   | TCIE  | RIE   | ILIE  | TE    | RE     | RWU   | SBK   | SCCR2             |

| \$102E       | TDRE  | TC    | RDRF  | IDLE  | OR    | NF     | FE    | 0     | SCSR              |

| \$102F       | Bit 7 | 6     | 5     | 4     | 3     | 2      | 1     | Bit 0 | SCDR              |

| \$1030       |       |       |       |       |       |        |       |       | Reserved          |

| to<br>\$1037 |       |       |       |       |       |        |       |       | Reserved          |

| \$1038       | GWOM  | CWOM  | CLK4X | LIRDV | 0     | SPRBYP | 0     | 0     | OPT2              |

| \$1039       | 0     | 0     | IRQE  | DLY   | CME   | FCME   | CR1   | CR0   | OPTION            |

| \$103A       | Bit 7 | 6     | 5     | 4     | 3     | 2      | 1     | Bit 0 | COPRST            |

| \$103B       | Dit 7 |       |       | 7     |       |        | '     | Dit 0 | Reserved          |

| \$103C       | RBOOT | SMOD  | MDA   | IRV   | PSEL3 | PSEL2  | PSEL1 | PSEL0 | HPRIO             |

| \$103D       | RAM5  | RAM4  | RAM3  | RAM2  | RAM1  | RAM0   | REG1  | REG0  | ]III KIO<br>]INIT |

| \$103E       | TILOP | 0     | OCCR  | CBYP  | DISR  | FCM    | FCOP  | 0     | J''N''<br>]TEST1  |

| \$103E       | 0     | 0     | 0     | 0     | 0     | NOCOP  | 0     | 0     | CONFIG            |

| \$1040       | 0     | 0     | 0     | U     | 0     | NOCOF  | 0     |       |                   |

| φ1040<br>to  |       |       |       |       |       |        |       |       | Reserved          |

| \$105B       |       |       |       |       |       |        |       |       | Reserved          |

| \$105C       | I01SA | I01SB | I02SA | I02SB | GSTHA | GSTGB  | PSTHA | PSTHB | CSSTRH            |

| \$105D       | I01EN | I01PL | I02EN | I02PL | GCSPR | PCSEN  | PSIZA | PSIZB | CSCTL             |

| \$105E       | GA15  | GA14  | GA13  | GA12  | GA11  | GA10   | 0     | 0     | CSGADR            |

| \$105F       | I01AV | I02AV | 0     | GNPOL | GAVLD | GSIZA  | GSIZB | GSIZC | CSGSIZ            |

### 4 Operating Modes and System Initialization

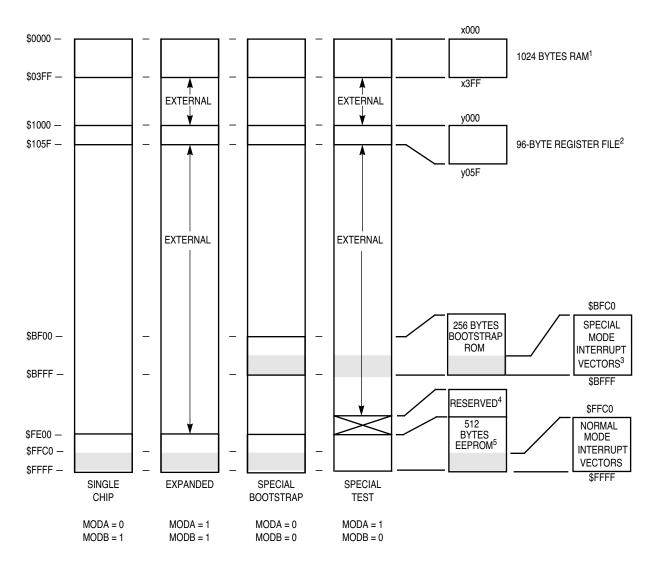

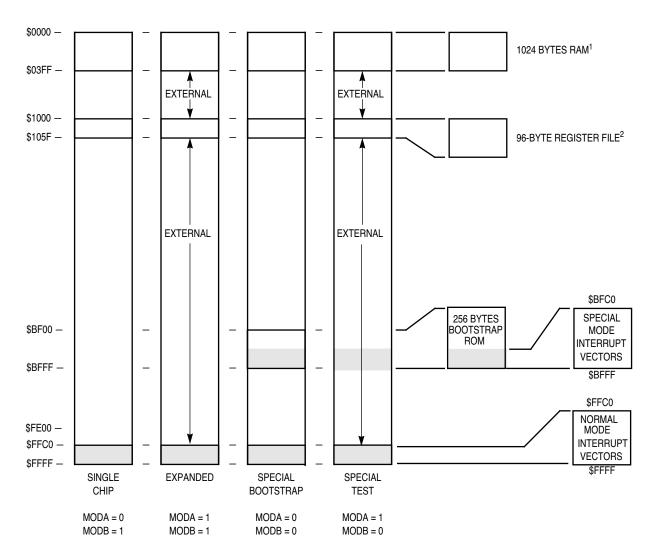

The 16-bit address bus can access 64 Kbytes of memory. Because the MC68HC11F1 and MC68HC11FC0 are intended to operate principally in expanded mode, there is no internal ROM and the address bus is non-multiplexed. Both devices include 1 Kbyte of static RAM, a 96-byte control register block, and 256 bytes of bootstrap ROM. The MC68HC11F1 also includes 512 bytes of EEPROM.

RAM and registers can be remapped on both the MC68HC11F1 and the MC68HC11FC0. On both the MC68HC11F1 and the MC68HC11FC0, out of reset RAM resides at \$0000 to \$03FF and registers reside at \$1000 to \$105F. On the MC68HC11F1, RAM and registers can both be remapped to any 4-Kbyte boundary. On the MC68HC11FC0, RAM can be remapped to any 1-Kbyte boundary, and registers can be remapped to any 4-Kbyte boundary in the first 16 Kbytes of address space.

RAM and control register locations are defined by the INIT register, which can be written only once within the first 64 E-clock cycles after a reset in normal modes. It becomes a read-only register thereafter. If RAM and the control register block are mapped to the same boundary, the register block has priority of the first 96 bytes.

In expanded and special test modes in the MC68HC11F1, EEPROM is located from \$xE00 to \$xFFF, where x represents the value of the four high-order bits of the CONFIG register. EEPROM is enabled by the EEON bit of the CONFIG register. In single-chip and bootstrap modes, the EEPROM is located from \$FE00 to \$FFFF.

### 4.1 Operating Modes

Bootstrap ROM resides at addresses \$BF00-\$BFFF, and is only available when the MCU operates in special bootstrap operating mode. Operating modes are determined by the logic levels applied to the MODB and MODA pins at reset.

In single-chip mode, the MCU functions as a self-contained microcontroller and has no external address or data bus. Ports B, C and F are available for general-purpose I/O (GPIO). Ports B and F are outputs only; each of the port C pins can be configured as input or output.

#### CAUTION

The MC68HC11FC0 must not be configured to boot in single-chip mode because it has no internal ROM or EEPROM. Operation of the device in single-chip mode will result in erratic behavior.

In expanded mode, the MCU can access external memory. Ports B and F provide the address bus, and port C is the data bus.

Special bootstrap mode is a variation of single chip mode that provides access to the internal bootstrap ROM. In this mode, the user can download a program into on-chip RAM through the serial communication interface (SCI).

Special test mode, a variation of expanded mode, is primarily used during Motorola's internal production testing, but can support emulation and debugging during program development.

**Table 7** shows a summary of operating modes, mode select pins, and control bits in the HPRIO register.

Control Bits in HPRIO (Latched at Reset) **Input Pins Mode Description** MODB SMOD **MODA RBOOT MDA** 1 0 Single Chip 0 0 0 0 0 1 1 1 Expanded 0 0 Special Bootstrap 1 1 0 0 1 Special Test 0 1 1

**Table 7 Hardware Mode Select Summary**

### 4.2 Memory Maps

#### NOTES:

- 1. RAM can be remapped to any 4-Kbyte boundary (\$x000). "x" represents the value contained in RAM[3:0] in the INIT register.

- 2. The register block can be remapped to any 4-Kbyte boundary (\$y000). "y" represents the value contained in REG[3:0] in the INIT register.

- 3. Special test mode vectors are externally addressed.

- 4. In special test mode the address locations \$zD00—\$zDFF are not externally addressable. "z" represents the value of bits EE[3:0] in the CONFIG register.

- 5. EEPROM can be remapped to any 4-Kbyte boundary (\$z000). "z" represents the value contained in EE[3:0] in the CONFIG register.

Figure 7 MC68HC11F1 Memory Map

#### NOTES:

- 1. RAM can be remapped to any 1-Kbyte boundary, depending on the value contained in the RAM field in the INIT register.

- 2. The register block can be remapped to \$0000, \$2000, or \$3000, depending on the value contained in REG[1:0] in the INIT register.

## Figure 8 MC68HC11FC0 Memory Map

### 4.3 System Initialization Registers

**HPRIO** — Highest Priority Interrupt and Miscellaneous

\$x03C

|        | Bit 7 | 6    | 5   | 4   | 3     | 2     | 1     | Bit 0 |              |

|--------|-------|------|-----|-----|-------|-------|-------|-------|--------------|

|        | RBOOT | SMOD | MDA | IRV | PSEL3 | PSEL2 | PSEL1 | PSEL0 |              |

| RESET: | 0     | 0    | 0   | 0   | 0     | 1     | 0     | 1     | Single-Chip  |

|        | 0     | 0    | 1   | 0   | 0     | 1     | 0     | 1     | Expanded     |

|        | 1     | 1    | 0   | 1   | 0     | 1     | 0     | 1     | Bootstrap    |

|        | 0     | 1    | 1   | 1   | 0     | 1     | 0     | 1     | Special Test |

#### RBOOT — Read Bootstrap ROM

RBOOT is valid only when SMOD is set to one (special bootstrap or special test mode). RBOOT can only be written in special modes but can be read anytime.

- 0 = Boot loader ROM disabled and not in memory map

- 1 = Boot loader ROM enabled and in memory map at \$BF00-\$BFFF

### SMOD and MDA — Special Mode Select and Mode Select A

The initial value of SMOD is the *inverse* of the logic level present on the MODB pin at the rising edge of reset. The initial value of MDA *equals* the logic level present on the MODA pin at the rising edge of reset. These two bits can be read at any time. They can be written at any time in special modes. Neither bit can be written in normal modes. SMOD cannot be set once it has been cleared. Refer to **Table 8**.

**Table 8 Hardware Mode Select Summary**

| Input Pins |      | Mode Description  | Control Bits in HPRIO (Latched at Reset) |      |     |  |

|------------|------|-------------------|------------------------------------------|------|-----|--|

| MODB       | MODA | Mode Description  | RBOOT                                    | SMOD | MDA |  |

| 1          | 0    | Single Chip       | 0                                        | 0    | 0   |  |

| 1          | 1    | Expanded          | 0                                        | 0    | 1   |  |

| 0          | 0    | Special Bootstrap | 1                                        | 1    | 0   |  |

| 0          | 1    | Special Test      | 0                                        | 1    | 1   |  |

### IRV — Internal Read Visibility

This bit can be read at any time. It can be written at any time in special modes, but only once in normal modes. In single-chip and bootstrap modes, IRV has no meaning or effect.

- 0 = Internal reads not visible

- 1 = Data from internal reads is driven on the external data bus

### PSEL[3:0] — See **5.2 Reset and Interrupt Registers**, page 27.

### **INIT** — RAM and I/O Mapping (MC68HC11FC0 only)

\$x03D

|        | Bit 7 | 6    | 5    | 4    | 3    | 2    | 1    | Bit 0 |

|--------|-------|------|------|------|------|------|------|-------|

|        | RAM5  | RAM4 | RAM3 | RAM2 | RAM1 | RAM0 | REG1 | REG0  |

| RESET: | 0     | 0    | 0    | 0    | 0    | 0    | 0    | 1     |

The INIT register can be written only once in first 64 cycles out of reset in normal modes, or at any time in special modes.

#### NOTE

The register diagram above applies to the MC68HC11FC0 only. A diagram and bit descriptions of the INIT register in the MC68HC11F1 are provided elsewhere in this section.

### RAM[5:0] — Internal RAM Map Position

These bits determine the upper six bits of the RAM address and allow mapping of the RAM to any one-Kbyte boundary.

### REG[1:0] — Register Block Map Position

These bits determine the location of the register block, as shown in **Table 9**.

**Table 9 Register Block Location**

| REG[1:0] | Register Block Address |

|----------|------------------------|

| 0 0      | \$0000 – \$005F        |

| 0 1      | \$1000 – \$105F        |

| 1 0      | \$2000 – \$205F        |

| 1 1      | \$3000 – \$305F        |

**INIT** — RAM and I/O Mapping (**MC68HC11F1 only**)

\$x03D

|        | Bit 7 | 6    | 5    | 4    | 3    | 2    | 1    | Bit 0 |

|--------|-------|------|------|------|------|------|------|-------|

|        | RAM3  | RAM2 | RAM1 | RAM0 | REG3 | REG4 | REG1 | REG0  |

| RESET: | 0     | 0    | 0    | 0    | 0    | 0    | 0    | 1     |

The INIT register can be written only once in first 64 cycles out of reset in normal modes, or at any time in special modes.

#### NOTE

The register diagram above applies to the MC68HC11F1 only. A diagram and bit descriptions of the INIT register in the MC68HC11FC0 are provided elsewhere in this section.

RAM[3:0] — Internal RAM Map Position

These bits determine the upper four bits of the RAM address and allow mapping of the RAM to any four-Kbyte boundary. Refer to **Table 10**.

REG[3:0] — 96-Byte Register Block Map Position

These bits determine bits the upper 4 bits of the register block and allow mapping of the register block to any four-Kbyte boundary. Refer to **Table 10**.

**Table 10 RAM and Register Mapping**

| RAM[3:0] | Location      |

|----------|---------------|

| 0000     | \$0000-\$03FF |

| 0001     | \$1000-\$13FF |

| 0010     | \$2000-\$23FF |

| 0011     | \$3000-\$33FF |

| 0100     | \$4000-\$43FF |

| 0101     | \$5000-\$53FF |

| 0110     | \$6000-\$63FF |

| 0111     | \$7000-\$73FF |

| 1000     | \$8000-\$83FF |

| 1001     | \$9000-\$93FF |

| 1010     | \$A000-\$A3FF |

| 1011     | \$B000-\$B3FF |

| 1100     | \$C000-\$C3FF |

| 1101     | \$D000-\$D3FF |

| 1110     | \$E000-\$E3FF |

| 1111     | \$F000-\$F3FF |

| REG[3:0] | Location      |

|----------|---------------|

| 0000     | \$0000-\$005F |

| 0001     | \$1000-\$105F |

| 0010     | \$2000-\$205F |

| 0011     | \$3000-\$305F |

| 0100     | \$4000-\$405F |

| 0101     | \$5000-\$505F |

| 0110     | \$6000-\$605F |

| 0111     | \$7000-\$705F |

| 1000     | \$8000-\$805F |

| 1001     | \$9000-\$905F |

| 1010     | \$A000-\$A05F |

| 1011     | \$B000-\$B05F |

| 1100     | \$C000-\$C05F |

| 1101     | \$D000-\$D05F |

| 1110     | \$E000-\$E05F |

| 1111     | \$F000-\$F05F |

**OPT2** — System Configuration Option Register 2

\$x038

|       | Bit 7 | 6    | 5     | 4     | 3 | 2      | 1 | Bit 0 |

|-------|-------|------|-------|-------|---|--------|---|-------|

|       | GWOM  | CWOM | CLK4X | LIRDV | _ | SPRBYP | _ | _     |

| RESET | 0     | 0    | 1     | 0     | 0 | 0      | 0 | 0     |

GWOM — Port G Wired-OR Mode Option

Refer to 7.8 Parallel I/O Registers, page 36.

CWOM — Port C Wired-OR Mode Option

Refer to 7.8 Parallel I/O Registers, page 37.

CLK4X — 4XCLK Output Enable

This bit can only be written once after reset in all modes.

0 = 4XOUT clock output is disabled

1 = Buffered oscillator is driven on the 4XOUT clock output

LIRDV — Load Instruction Register Driven

In order to detect consecutive instructions in a high-speed application,  $\overline{LIR}$  can be driven high for one quarter of an E-clock cycle during each instruction fetch.

$0 = \overline{\text{LIR}}$  signal is not driven high.

$1 = \overline{LIR}$  signal is driven high.

Bits 3, 1, 0 — Not implemented. Reads always return zero and writes have no effect.

SPRBYP — See 10.2 SPI Registers, page 52.

**OPTION** — System Configuration Options

\$x039

|        | Bit 7 | 6    | 5     | 4    | 3   | 2     | 1    | Bit 0 |

|--------|-------|------|-------|------|-----|-------|------|-------|

|        | ADPU  | CSEL | IRQE* | DLY* | CME | FCME* | CR1* | CR0*  |

| RESET: | 0     | 0    | 0     | 1    | 0   | 0     | 0    | 0     |

<sup>\*</sup>Can be written only once in first 64 cycles out of reset in normal modes, or at any time in special modes.

ADPU — A/D Power-Up

This bit is implemented on the MC68HC11F1 only. On the MC68HC11FC0, reads always return zero and writes have no effect.

0 = A/D system disabled

1 = A/D system enabled

CSEL — Clock Select

This bit is implemented on the MC68HC11F1 only. On the MC68HC11FC0, reads always return zero and writes have no effect.

0 = A/D and EEPROM use system E clock

1 = A/D and EEPROM use internal RC clock

IRQE — IRQ Select Edge Sensitive Only

0 = Low level recognition

1 = Falling edge recognition

DLY — Enable Oscillator Start-Up Delay on Exit from STOP

0 = No stabilization delay on exit from STOP

1 = Stabilization delay of 4064 E-clock cycles is enabled on exit from STOP

CME — Clock Monitor Enable

0 = Clock monitor disabled; slow clocks can be used

1 = Slow or stopped clocks cause clock failure reset

FCME — Force Clock Monitor Enable

0 = Clock monitor circuit follows the state of the CME bit

1 = Clock monitor circuit is enabled until the next reset

In order to use both STOP and the clock monitor, the CME bit should be written to zero prior to executing a STOP instruction and rewritten to one after recovery from STOP. FCME should be kept cleared if the user intends to use the STOP instruction.

CR[1:0] — COP Timer Rate Select

Refer to **5.2 Reset and Interrupt Registers**, page 27.

#### **CONFIG** — EEPROM Mapping, COP, EEPROM Enables

\$x03F

|       | Bit 7 | 6   | 5   | 4   | 3 | 2     | 1 | Bit 0 |

|-------|-------|-----|-----|-----|---|-------|---|-------|

|       | EE3   | EE2 | EE1 | EE0 | 1 | NOCOP | 1 | EEON  |

| RESET | U     | U   | U   | U   | 1 | U     | 1 | U     |

U = Unaffected by reset

Bits 7:3 — See **6.2 EEPROM Registers**, page 30. (These bits are implemented on the MC68HC11F1 only.)

NOCOP — COP System Disable

0 = COP enabled (forces reset on time-out)

1 = COP disabled (does not force reset on time-out)

### **TEST1** — Factory Test

\$x03E

|        | Bit 7 | 6 | 5    | 4    | 3    | 2   | 1    | Bit 0 |

|--------|-------|---|------|------|------|-----|------|-------|

|        | TILOP | 0 | OCCR | CBYP | DISR | FCM | FCOP | 0     |

| RESET: | 0     | 0 | 0    | 0    | _    | 0   | 0    | 0     |

These bits can only be written in test and bootstrap modes.

### TILOP — Test Illegal Opcode

This test mode allows serial testing of all illegal opcodes without servicing an interrupt after each illegal opcode is fetched.

- 0 = Normal operation (trap on illegal opcodes)

- $1 = Inhibit \overline{LIR}$  when an illegal opcode is found

Bit 6 — Not implemented. Reads always return zero and writes have no effect.

#### OCCR — Output Condition Code Register to Timer Port

- 0 = Normal operation

- 1 = Condition code bits H, N, Z, V and C are driven on PA[7:3] to allow a test system to monitor CPU operation

### CBYP — Timer Divider Chain Bypass

- 0 = Normal operation

- 1 = The 16-bit free-running timer is divided into two 8-bit halves and the prescaler is bypassed. The system E clock drives both halves directly.

### DISR — Disable Resets from COP and Clock Monitor

In test and bootstrap modes, this bit is reset to one to inhibit clock monitor and COP resets. In normal modes, DISR is reset to zero.

- 0 = Normal operation

- 1 = COP and Clock Monitor failure do not generate a system reset

### FCM — Force Clock Monitor Failure

- 0 = Normal operation

- 1 = Generate an immediate clock monitor failure reset. Note that the CME bit in the OPTION register must also be set in order to force the reset.

### FCOP — Force COP Watchdog Failure

- 0 = Normal operation

- 1 = Generate an immediate COP failure reset. Note that the NOCOP bit in the CONFIG register must be cleared (COP enabled) in order to force the reset.

- Bit 0 Not implemented. Reads always return zero and writes have no effect.

### **5 Resets and Interrupts**

There are three sources of reset on the MC68HC11F1 and MC68HC11FC0, each having its own reset vector:

- RESET pin

- · Clock monitor failure

- Computer operating properly (COP) failure

There are 22 interrupt sources serviced by 18 interrupt vectors. (The SCI interrupt vector services five SCI interrupt sources.) Three of the interrupt vectors are non-maskable:

- Illegal opcode trap

- Software interrupt

- XIRQ pin (pseudo non-maskable interrupt)

The other 19 interrupts, generated mostly by on-chip peripheral systems, are maskable. Maskable interrupts are recognized only if the global interrupt mask bit (I) in the condition code register (CCR) is clear. Maskable interrupts have a default priority arrangement out of reset. However, any one interrupt source can be elevated to the highest maskable priority position by writing to the HPRIO register. This register can be written at any time, provided the I bit in the CCR is set.

In addition to the global I bit, all maskable interrupt sources except the external interrupt (IRQ pin) are subject to local enable bits in control registers. Each of these interrupt sources also sets a corresponding flag bit in a control register that can be polled by software.

Several of these flags are automatically cleared during the normal course of responding to the interrupt requests. For example, the RDRF flag is set when a byte has been received in the SCI. The normal response to an RDRF interrupt request is to read the SCI status register to check for receive errors, then to read the received data from the SCI data register. It is precisely these two steps that are required to clear the RDRF flag, so no further instructions are necessary.

### 5.1 Interrupt Sources

The following table summarizes the interrupt sources, vector addresses, masks, and flag bits.

**Table 11 Interrupt and Reset Vector Assignments**

| Vector Address | Interrupt Source                       | CCR Mask | Local Mask | Flag Bit |

|----------------|----------------------------------------|----------|------------|----------|

| FFC0, C1       |                                        |          |            |          |

| to<br>FFD4, D5 | Reserved                               | _        | _          | _        |

| FFD6, D7       | SCI Serial System                      |          |            |          |

|                | SCI Transmit Complete                  |          | TCIE       | TC       |

|                | SCI Transmit Data Register Empty       | I Bit    | TIE        | TDRE     |

|                | SCI Idle Line Detect                   | I DIL    | ILIE       | IDLE     |

|                | SCI Receiver Overrun                   |          | RIE        | OR       |

|                | SCI Receive Data Register Full         |          | RIE        | RDRF     |

| FFD8, D9       | SPI Serial Transfer Complete           | I Bit    | SPIE       | SPIF     |

| FFDA, DB       | Pulse Accumulator Input Edge           | I Bit    | PAII       | PAIF     |

| FFDC, DD       | Pulse Accumulator Overflow             | I Bit    | PAOVI      | PAOVF    |

| FFDE, DF       | Timer Overflow                         | I Bit    | TOI        | TOF      |

| FFE0, E1       | Timer Input Capture 4/Output Compare 5 | I Bit    | I4/O5I     | 14/O5F   |

| FFE2, E3       | Timer Output Compare 4                 | I Bit    | OC4I       | OC4F     |

| FFE4, E5       | Timer Output Compare 3                 | I Bit    | OC3I       | OC3F     |

| FFE6, E7       | Timer Output Compare 2                 | I Bit    | OC2I       | OC2F     |

| FFE8, E9       | Timer Output Compare 1                 | I Bit    | OC1I       | OC1F     |

| FFEA, EB       | Timer Input Capture 3                  | I Bit    | IC3I       | IC3F     |

| FFEC, ED       | Timer Input Capture 2                  | I Bit    | IC2I       | IC2F     |

| FFEE, EF       | Timer Input Capture 1                  | I Bit    | IC1I       | IC1F     |

| FFF0, F1       | Real-Time Interrupt                    | I Bit    | RTII       | RTIF     |

| FFF2, F3       | ĪRQ                                    | I Bit    | None       | None     |

| FFF4, F5       | XIRQ Pin                               | X Bit    | None       | None     |

| FFF6, F7       | Software Interrupt                     | None     | None       | None     |

| FFF8, F9       | Illegal Opcode Trap                    | None     | None       | None     |

| FFFA, FB       | COP Failure                            | None     | NOCOP      | None     |

| FFFC, FD       | Clock Monitor Fail                     | None     | CME        | None     |

| FFFE, FF       | RESET                                  | None     | None       | None     |

|                |                                        |          |            |          |

### 5.2 Reset and Interrupt Registers

**OPTION** — System Configuration Options

\$x039

|        | Bit 7 | 6    | 5     | 4    | 3   | 2     | 1    | Bit 0 |

|--------|-------|------|-------|------|-----|-------|------|-------|

|        | ADPU  | CSEL | IRQE* | DLY* | CME | FCME* | CR1* | CR0*  |

| RESET: | 0     | 0    | 0     | 1    | 0   | 0     | 0    | 0     |

<sup>\*</sup>Can be written only once in first 64 cycles out of reset in normal modes, or at any time in special modes.

Bits [7:6], [4:2]

Refer to 4.3 System Initialization Registers, page 23, and 11.3 A/D Registers, page 56.

IRQE — IRQ Select Edge Sensitive Only

0 = Low level recognition

1 = Falling edge recognition

CR[1:0] — COP Timer Rate Select

The COP system is driven by a constant frequency of E/2<sup>15</sup>. CR[1:0] specify an additional divide-by factor to arrive at the COP time-out rate.

**Table 12 COP Watchdog Time-Out Periods**

| Frequency | Tolerance              | CR[1:0] = 00       | CR[1:0] = 01       | CR[1:0] = 10       | CR[1:0] = 11       |

|-----------|------------------------|--------------------|--------------------|--------------------|--------------------|

| 1 MHz     | -0/+32.768 ms          | 32.768 ms          | 131.072 ms         | 524.288 ms         | 2.097 s            |

| 2 MHz     | -0/+16.384 ms          | 16.384 ms          | 65.536 ms          | 262.144 ms         | 1.049 s            |

| 3 MHz     | -0/+10.923 ms          | 10.923 ms          | 43.691 ms          | 174.763 ms         | 699.051 ms         |

| 4 MHz     | -0/+8.192 ms           | 8.192 ms           | 32.768 ms          | 131.072 ms         | 524.288 ms         |

| 5 MHz     | -0/+6.554 ms           | 6.554 ms           | 26.214 ms          | 104.858 ms         | 419.430 ms         |

| 6 MHz     | -0/+5.461 ms           | 5.461 ms           | 21.845             | 87.381 ms          | 349.525 ms         |

| Any E     | -0/+2 <sup>15</sup> /E | 2 <sup>15</sup> /E | 2 <sup>17</sup> /E | 2 <sup>19</sup> /E | 2 <sup>21</sup> /E |

**COPRST** — Arm/Reset COP Timer Circuitry

RESET:

RESET:

\$x03A

| Bit 7 | 6 | 5 | 4 | 3 | 2 | 1 | Bit 0 |

|-------|---|---|---|---|---|---|-------|

| 7     | 6 | 5 | 4 | 3 | 2 | 1 | 0     |

| 0     | 0 | 0 | 0 | 0 | 0 | 0 | 0     |

Write \$55 to COPRST to arm the COP watchdog clearing mechanism. Then write \$AA to COPRST to reset the COP timer. Performing instructions between these two steps is possible provided both steps are completed in the correct sequence before the timer times out.

**HPRIO** — Highest Priority I-Bit Interrupt and Miscellaneous

\$x03C

| Bit 7 | 6    | 5   | 4   | 3     | 2     | 1     | Bit 0 |

|-------|------|-----|-----|-------|-------|-------|-------|

| RBOOT | SMOD | MDA | IRV | PSEL3 | PSEL2 | PSEL1 | PSEL0 |

|       | •    | •   |     | 0     | 1     | 0     | 1     |

Bits [7:4] — See **4.3 System Initialization Registers**, page 20.

PSEL[3:0] — Interrupt Priority Select Bits

Can be written only while the I bit in the CCR is set (interrupts disabled). These bits select one interrupt source to have priority over other I-bit related sources.

**Table 13 Highest Priority Interrupt Selection**

| PSEL[3:0] | Interrupt Source Promoted    |

|-----------|------------------------------|

| 0000      | Timer Overflow               |

| 0001      | Pulse Accumulator Overflow   |

| 0010      | Pulse Accumulator Input Edge |

| 0011      | SPI Serial Transfer Complete |

| 0100      | SCI Serial System            |

| 0101      | Reserved (Default to IRQ)    |

| 0110      | IRQ (External Pin)           |

| 0111      | Real-Time Interrupt          |

| 1000      | Timer Input Capture 1        |

| 1001      | Timer Input Capture 2        |

| 1010      | Timer Input Capture 3        |

**Table 13 Highest Priority Interrupt Selection (Continued)**

| PSEL[3:0] | Interrupt Source Promoted              |

|-----------|----------------------------------------|

| 1011      | Timer Output Compare 1                 |

| 1100      | Timer Output Compare 2                 |

| 1101      | Timer Output Compare 3                 |

| 1110      | Timer Output Compare 4                 |

| 1111      | Timer Output Compare 5/Input Capture 4 |

### **CONFIG** — EEPROM Mapping, COP, EEPROM Enables

\$x03F

|       | Bit 7 | 6   | 5   | 4   | 3 | 2     | 1 | Bit 0 |

|-------|-------|-----|-----|-----|---|-------|---|-------|

|       | EE3   | EE2 | EE1 | EE0 | 1 | NOCOP | 1 | EEON  |

| RESET | U     | U   | U   | U   | 1 | U     | 1 | U     |

Bits 7:3, 1:0 — See **6.2 EEPROM Registers**, page 30.

NOCOP — COP System Disable

0 = COP enabled (forces reset on time-out)

1 = COP disabled (does not force reset on time-out)

### 6 Electrically Erasable Programmable ROM

The MC68HC11F1 has 512 bytes of electrically erasable programmable ROM (EEPROM). A nonvolatile, EEPROM-based configuration register (CONFIG) controls whether the EEPROM is present or absent and determines its position in the memory map. In single-chip and bootstrap modes the EEPROM is positioned at \$FE00-\$FFFF. In expanded and special test modes, the EEPROM can be repositioned to any 4-Kbyte boundary (\$xE00-\$xFFF).

# NOTE

### EEPROM is available on the MC68HC11F1 only.

### 6.1 EEPROM Operation

The EEON bit in CONFIG controls whether the EEPROM is present in the memory map. When EEON = 1, the EEPROM is enabled. When EEON = 0, the EEPROM is disabled and removed from the memory map. EEON is forced to one out of reset in single-chip and special bootstrap modes to enable EEPROM. EEON is forced to zero out of reset in special test mode to remove EEPROM from the memory map, although test software can turn it back on. In normal expanded mode, EEON is reset to the value last programmed into CONFIG.

An on-chip charge pump develops the high voltage required for programming and erasing. When the E-clock frequency is 1 MHz or above, the charge pump is driven by the E-clock. When the E-clock frequency is less than 1 MHz, select the internal RC oscillator to drive the EEPROM charge pump by writing one to the CSEL bit in the OPTION register. Refer to the discussion of the OPTION register in **4.3 System Initialization Registers**, page 23.

### 6.2 EEPROM Registers

**BPROT** — Block Protect

\$x035

|       | Bit 7 | 6 | 5 | 4     | 3     | 2     | 1     | Bit 0 |

|-------|-------|---|---|-------|-------|-------|-------|-------|

|       | 0     | 0 | 0 | PTCON | BPRT3 | BPRT2 | BPRT1 | BPRT0 |

| RESET | 0     | 0 | 0 | 1     | 1     | 1     | 1     | 1     |

Bits [7:5] — Not implemented. Reads always return zero and writes have no effect.

PTCON — Protect for CONFIG

0 = CONFIG register can be programmed or erased normally

1 = CONFIG register cannot be programmed or erased

BPRT[3:0] — Block Protect Bits for EEPROM

0 = Protection disabled

1 = Protection enabled

**Table 14 Block Protect Bits for EEPROM**

| Bit Name | Block Protected | Block Size |

|----------|-----------------|------------|

| BPRT3    | \$xEE0-xFFF     | 288 Bytes  |

| BPRT2    | \$xE60-xEDF     | 128 Bytes  |

| PBRT1    | \$xE20-xE5F     | 64 Bytes   |

| BPRT0    | \$xE00-xE1F     | 32 Bytes   |

#### **NOTE**

Block protect register bits can be written to zero (protection disabled) only once within 64 cycles of a reset in normal modes, or at any time in special modes. Block protect register bits can be written to one (protection enabled) at any time.

### **PPROG** — EEPROM Programming Control

\$x03B

|       | Bit 7 | 6    | 5 | 4    | 3   | 2     | 1     | Bit 0 |

|-------|-------|------|---|------|-----|-------|-------|-------|

|       | ODD   | EVEN | 0 | BYTE | ROW | ERASE | EELAT | EEPGM |

| RESET | 0     | 0    | 0 | 0    | 0   | 0     | 0     | 0     |

ODD — Program Odd Rows (TEST)

EVEN — Program Even Rows (TEST)

ROW and BYTE — Row Erase Select Bit and Byte Erase Select

The value of these bits determines the manner in which EEPROM is erased. Bit encodings are shown in **6.2 EEPROM Registers**, page 30.

Table 15 ROW and BYTE Encodings

| BYTE | ROW | Action                     |

|------|-----|----------------------------|

| 0    | 0   | Bulk Erase (All 512 Bytes) |

| 0    | 1   | Row Erase (16 Bytes)       |

| 1    | 0   | Byte Erase                 |

| 1    | 1   | Byte Erase                 |

ERASE — Erase/Normal Control for EEPROM

0 = Normal read or program mode

1 = Erase mode

EELAT — EEPROM Latch Control

0 = EEPROM address and data bus configured for normal reads

1 = EEPROM address and data bus configured for programming or erasing

EEPGM — EEPROM Program Command

0 = Program or erase voltage to EEPROM array switched off

1 = Program or erase voltage to EEPROM array switched on

### **CONFIG** — EEPROM Mapping, COP, EEPROM Enables

\$x03F

|       | Bit 7 | 6   | 5   | 4   | 3 | 2     | 1 | Bit 0 |

|-------|-------|-----|-----|-----|---|-------|---|-------|

|       | EE3   | EE2 | EE1 | EE0 | 1 | NOCOP | 1 | EEON  |

| RESET | U     | U   | U   | U   | 1 | U     | 1 | U     |

U = Unaffected by reset.

The CONFIG register is used to assign EEPROM a location in the memory map and to enable or disable EEPROM operation. Bits in this register are user-programmed except when forced to certain values, as noted in the following bit descriptions.

#### EE[3:0] — EEPROM Map Position

EEPROM is located at xE00 - xFFF, where x is the value represented by these four bits. In single-chip and bootstrap modes, EEPROM is forced to FE00 - FFFF, regardless of the state of these bits. On factory-fresh devices, FE[3:0] = 0.

Bit 3 — Not implemented. Reads always return one and writes have no effect.

NOCOP — COP System Disable

0 = COP enabled (forces reset on time-out)

1 = COP disabled (does not force reset on time-out)

Bit 1 — Not implemented. Reads always return one and writes have no effect.

#### EEON — EEPROM Enable

This bit is forced to one in single-chip and bootstrap modes. In test mode, EEON is forced to zero out of reset. In expanded mode, the EEPROM obeys the state of this bit.

- 0 = EEPROM is removed from the memory map.

- 1 = EEPROM is present in the memory map.

Refer to 6.4 CONFIG Register Programming for instructions on programming this register.

### 6.3 EEPROM Programming and Erasure

Programming and erasing the EEPROM is controlled by the PPROG register, subject to the block protect (BPROT) register value. To erase the EEPROM, ensure that the proper bits of the BPROT register are cleared, and then complete the following steps:

- 1. Write to PPROG with the ERASE and EELAT bits set and the BYTE and ROW bits set or cleared as appropriate.

- 2. Write to the appropriate EEPROM address with any data. Row erase (\$xE00-\$xE0F, \$xE10-\$xE1F,... \$xFF0-\$xFFF) requires a single write to any location in the row. Perform bulk erase by writing to any location in the array.

- 3. Write to PPROG with the ERASE, EELAT, and EEPGM bits set and the BYTE and ROW bits set or cleared as appropriate.

- 4. Delay for 10 ms (20 ms for low-voltage operation).

- 5. Clear the EEPGM bit in PPROG to turn off the high voltage.

- 6. Clear the PPROG register to reconfigure EEPROM address and data buses for normal operations.

To program the EEPROM, ensure that the proper bits of the BPROT register are cleared, and then complete the following steps:

- 1. Write to PPROG with the EELAT bit set.

- 2. Write data to the desired address.

- 3. Write to PPROG with the EELAT and EEPGM bits set.

- 4. Delay for 10 ms (20 ms for low-voltage operation).

- 5. Clear the EEPGM bit in PPROG to turn off the high voltage.

- 6. Clear the PPROG register to reconfigure EEPROM address and data buses for normal operations.

#### 6.3.1 Programming a Byte

The following example shows how to program an EEPROM byte. This example assumes that the appropriate bits in BPROT are cleared and that the data to be programmed is present in accumulator A.

| PROG | LDAB | #\$02  | EELAT=1, EEPGM=0                           |

|------|------|--------|--------------------------------------------|

|      | STAB | \$103B | Set EELAT bit                              |

|      | STAA | \$FE00 | Store data to EEPROM address               |

|      | LDAB | #\$03  | EELAT=1, EEPGM=1                           |

|      | STAB | \$103B | Turn on programming voltage                |

|      | JSR  | DLY10  | Delay 10 ms                                |