# Type-C CC and SBU Short to VBUS Over-Voltage and IEC ESD Protection Switch

### **General Description**

The RT1738A is an USB Type-C interface over-voltage protection IC.

The RT1738A protects the high voltage shorted to VBUS to adjacent pins of CC/SBU up to 28V due to USB Power Delivery (PD) allowing VBUS from 3.3 to 21V sourcing.

The RT1738A is integrated the protection ESDs of IEC61000-4-2 with contact discharge  $\pm 8kV$  on CON\_CC1/CON\_CC2, D1/D2 and  $\pm 6kV$  on CON\_SBU1/CON\_SBU2. The surge immunity level of CON\_CC1 /CON\_CC2 is up to  $\pm 35V$ . Besides, the ultra-fast OVP response time of 60ns can protect the system side of application IC from damage.

The RT1738A is available in a 3×3mm WQFN package.

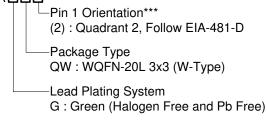

# **Ordering Information**

#### RT1738A

Note :

\*\*\*Empty means Pin1 orientation is Quadrant 1

Richtek products are :

- ► RoHS compliant and compatible with the current requirements of IPC/JEDEC J-STD-020.

- Suitable for use in SnPb or Pb-free soldering processes.

### Features

- 4-Channels of Short to VBUS Over-Voltage Protection (CON\_CC1, CON\_CC2, CON\_SBU1, CON\_SBU2)

- IEC61000-4-2 Contact Discharge Protection

► CON\_CC1/CON\_CC2 : ±8kV

- ▶ D1/D2 : ±8kV

- ► CON\_SBU1/CON\_SBU2 : ±6kV

- High Absolute Maximum Ratings = 28V of CON\_CC1, CON\_CC2, CON\_SBU1 and CON\_SBU2

- 60ns Ultra-Fast OVP Response Time of CC/SBU

- 255m $\Omega$  Ultra-Low Ron of CC Switch Typical

- 3.6Ω Low Ron of SBU Switch Typical

- 40µA Low Quiescent Current in Standby

- High Bandwidth of 1.1GHz for SBU Switch

- Dead Battery Support

- 20-Pin 3x3mm WQFN Package

### Applications

- PC/Notebook

- Smart Phone/Tablet

- TV/Monitor

- USB-C Dongle/Docking/Hubs

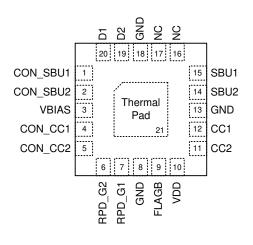

## **Pin Configuration**

(TOP VIEW)

WQFN-20L 3x3

### **Marking Information**

RS= : Product Code YMDNN : Date Code

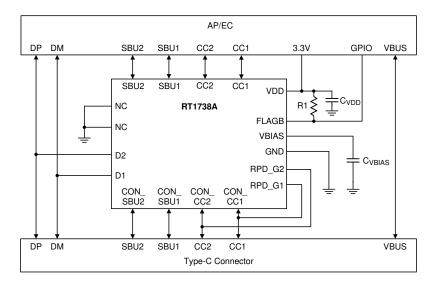

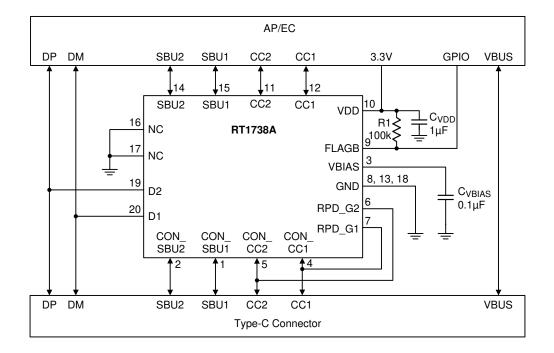

# **Simplified Application Circuit**

## **Functional Pin Description**

| Pin No.   | Pin Name | Pin Function                                                                                                                |  |  |  |

|-----------|----------|-----------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1         | CON_SBU1 | Type-C connector side SBU1 switch. Connect SBU1 pin of the USB Type-C connector.                                            |  |  |  |

| 2         | CON_SBU2 | Type-C connector side SBU2 switch. Connect SBU2 pin of the USB Type-C connector.                                            |  |  |  |

| 3         | VBIAS    | VBIAS pin connect capacitor for ESD protection. Put a $0.1\mu\text{F}$ capacitor on this pin to ground.                     |  |  |  |

| 4         | CON_CC1  | Type-C connector side CC1 switch. Connect CC1 pin of the USB Type-C connector.                                              |  |  |  |

| 5         | CON_CC2  | Type-C connector side CC2 switch. Connect CC2 pin of the USB Type-C connector.                                              |  |  |  |

| 6         | RPD_G2   | If dead battery resistors are required, short pin to CON_CC2. If dead battery resistors are not required, short pin to GND. |  |  |  |

| 7         | RPD_G1   | If dead battery resistors are required, short pin to CON_CC1. If dead battery resistors are not required, short pin to GND. |  |  |  |

| 8, 13, 18 | GND      | Ground.                                                                                                                     |  |  |  |

| 9         | FLAGB    | Open-drain output cautioning fault condition.                                                                               |  |  |  |

| 10        | VDD      | 2.5V to 5.5V power supply. Bypass VDD to GND with a $1\mu\text{F}$ capacitor.                                               |  |  |  |

| 11        | CC2      | System side of the CC2 switch. Connect to CC pin of the CC/PD controller.                                                   |  |  |  |

| 12        | CC1      | System side of the CC1 switch. Connect to CC pin of the CC/PD controller.                                                   |  |  |  |

| 14        | SBU2     | System side of the SBU2 switch. Connect to SBU pin of the SBU MUX.                                                          |  |  |  |

# **RT1738A**

| Pin No. | Pin Name    | Pin Function                                                                       |  |  |  |  |

|---------|-------------|------------------------------------------------------------------------------------|--|--|--|--|

| 15      | SBU1        | ystem side of the SBU1 switch. Connect to SBU pin of the SBU MUX.                  |  |  |  |  |

| 16, 17  | NC          | No internal connection. Connect to ground.                                         |  |  |  |  |

| 19      | D2          | USB2.0 IEC ESD protection. Connect to the USB2.0 pins of the USB Type-C connector. |  |  |  |  |

| 20      | D1          | USB2.0 IEC ESD protection. Connect to the USB2.0 pins of the USB Type-C connector. |  |  |  |  |

|         | Thermal Pad | Used as a heatsink. Thermal pad connect to PCB ground plane.                       |  |  |  |  |

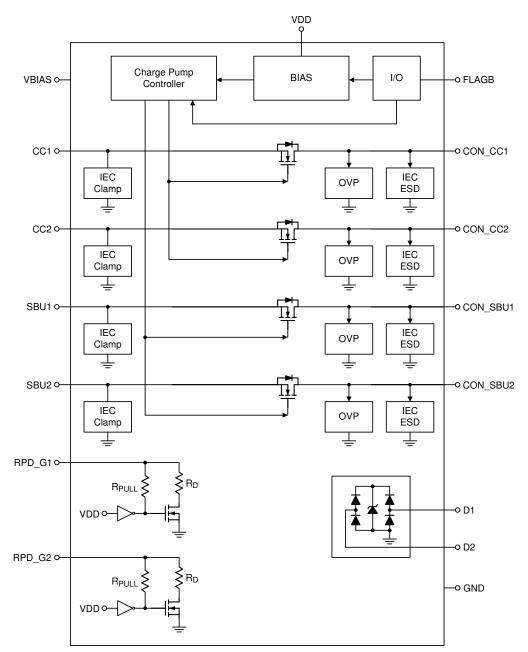

### **Functional Block Diagram**

# **RT1738A**

| Absolute Maximum Ratings (Note1)                        |                 |

|---------------------------------------------------------|-----------------|

| CON_CC1/CON_CC2/CON_SBU1/CON_SBU2                       | –0.3V to 28V    |

| VBIAS/RPD_G1/RPD_G2                                     | –0.3V to 28V    |

| CC1/CC2/SBU1/SBU2/VDD/FLAGB/D1/D2                       | –0.3V to 6V     |

| Output Current (CON_CC1/CON_CC2/CC1/CC2)                | 1.25A to 1.25A  |

| Output Current (CON_SBU1/CON_SBU2/SBU1/SBU2)            | –100mA to 100mA |

| <ul> <li>Power Dissipation, PD @ TA = 25°C</li> </ul>   |                 |

| WQFN-20L 3x3                                            | 3.33W           |

| Package Thermal Resistance (Note 2)                     |                 |

| WQFN-20L 3x3, θJA                                       | 30°C/W          |

| WQFN-20L 3x3, өјс                                       | 7.5°C/W         |

| Lead Temperature (Soldering, 10 sec.)                   | 260°C           |

| Junction Temperature                                    | 150°C           |

| Storage Temperature Range                               | –65°C to 150°C  |

| • ESD Susceptibility (Note 3)                           |                 |

| HBM (Human Body Model)                                  | ±2kV            |

| CDM                                                     | ±500V           |

| CON_CC1/CON_CC2/D1/D2 (IEC 61000-4-2 Contact Discharge) | ±8kV            |

| CON_CC1/CON_CC2/D1/D2 (IEC 61000-4-2 Air Discharge)     | ±15kV           |

| CON_SBU1/CON_SBU2 (IEC 61000-4-2 Contact Discharge)     | ±6kV            |

| CON_SBU1/CON_SBU2 (IEC 61000-4-2 Air Discharge)         | ±15kV           |

| CON_CC1/CON_CC2 (IEC 61000-4-5 Surge)                   | ±35V            |

| CON_SBU1/CON_SBU2 (IEC 61000-4-2 Air Discharge)         | ±15kV           |

### Recommended Operating Conditions (Note 4)

| Supply Input Voltage, VDD                         | 2.5V to 5.5V |

|---------------------------------------------------|--------------|

| CON_CC1/CON_CC2/CC1/CC2/RPD_G1/RPD_G2/D1/D2/FLAGB | 0V to 5.5V   |

| CON_SBU1/CON_SBU2/SBU1/SBU2                       | 0V to 4.25V  |

| Ambient Temperature Range                         |              |

| Junction Temperature Range                        |              |

|                                                   |              |

## **Electrical Characteristics**

$(V_{DD} = 3.3V, T_A = 25^{\circ}C, unless otherwise specified)$

| Parameter                 | Symbol Test Conditions |                                                                             | Min | Тур | Max  | Unit |  |

|---------------------------|------------------------|-----------------------------------------------------------------------------|-----|-----|------|------|--|

| Static Characteristics    |                        |                                                                             |     |     |      |      |  |

| VDD Under-Voltage Lockout | Vvdd_uvlo              | $V_{DD} = 1.5V$ , and the rises $V_{DD}$ until CC and SBU switches turn on. | 2   | 2.2 | 2.45 | V    |  |

| Parameter                                                    | Symbol                                 | Test Conditions                                                                                                                             | Min | Тур   | Max  | Unit |

|--------------------------------------------------------------|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|------|------|

| V <sub>DD</sub> Under-Voltage Lockout<br>Hysteresis          | VVDD_UVLO_HYS                          | $V_{DD} = 3V$ , and the lower<br>$V_{DD}$ until CC and SBU<br>switches turn off<br>measure the difference<br>between rising and<br>falling. | 95  | 165   | 260  | mV   |

| Quiescent Supply Current                                     | lq                                     | VDD = 3.3V (Typical)                                                                                                                        |     | 40    | 70   | μA   |

| Leakage Current for CC<br>Pins when Device is<br>Powered     | ICC_LEAK                               | V <sub>DD</sub> = 3.3V, V <sub>CON_CCx</sub> = 5V; CCx floating                                                                             |     |       | 3.1  | μA   |

| Leakage Current for SBU<br>Pins when Device is<br>Powered    | ISBU_LEAK                              | VDD = 3.3V, VCON_SBUx = 3.6V; SBUx floating                                                                                                 |     |       | 2    | μA   |

| Leakage Current for<br>CON_CC Pins when Device<br>is in OVP  | ICON_CC_LEAK_OVP                       | VDD = 3.3V, VCON_CCx =<br>24V; VCCx = 0V, measure<br>the current of CON_CCx                                                                 | -1  | 11.5  | 30   | μA   |

| Leakage Current for<br>CON_SBU Pins when<br>Device is in OVP | ICON_SBU_LEAK_OVP                      | $V_{DD} = 3.3V$ , $V_{CON}SBUx = 24V$ ; $V_{SBUx} = 0V$ ,<br>measure the current of CON_SBUx                                                | -1  | 7     | 20   | μA   |

| Leakage Current for CC<br>Pins when Device is in OVP         |                                        |                                                                                                                                             | -1  |       | 30   | μA   |

| Leakage Current for SBU<br>Pins when Device is in OVP        | ISBU_LEAK_OVP                          | VDD = 3.3V, VCON_SBUx =<br>24V; VSBUx = 0V,<br>measure the current into<br>SBUx                                                             | -1  |       | 1    | μA   |

| Leakage Current for Dx<br>Pins                               |                                        |                                                                                                                                             | -1  |       | 1    | μA   |

| CC Switch Characteristics                                    |                                        |                                                                                                                                             |     |       |      |      |

| Switch Turn On Resistance                                    | Ron_cc                                 | VDD = 3.3V, $VCCx = 5V$                                                                                                                     |     | 255   | 390  | mΩ   |

| Switch Turn On Resistance<br>Flatness                        | RON_CC_FLAT                            | Sweep CCx voltage between 0V and 3.6V                                                                                                       |     |       | 5    | mΩ   |

| Equivalent on Capacitance                                    | Capacitance between<br>CCx/CON_CCx and |                                                                                                                                             |     | 11.25 |      | pF   |

| Threshold Voltage of the                                     |                                        | External 80µA                                                                                                                               | 0.3 |       | 1.2  |      |

| Pull-Down Switch in Series                                   | VTH_DB                                 | External 180µA                                                                                                                              | 0.5 |       | 1.2  | V    |

| with Rd during Dead Battery                                  |                                        | External 330µA                                                                                                                              | 0.9 |       | 2.13 |      |

| OVP Threshold on CC Pins                                     | Vovpcc                                 | V <sub>DD</sub> = 3.3V, CON_CCx<br>rises from 5.5V until<br>FLAGB goes from H to L                                                          | 5.7 | 5.9   | 6.1  | V    |

| Hysteresis on CC OVP                                         | Vovpcc_hys                             | V <sub>DD</sub> = 3.3V, CON_CCx<br>falls from 6.1V until<br>FLAGB goes from L to H                                                          |     | 75    |      | mV   |

# **RT1738A**

| Parameter                                                       | Symbol                     | Test Conditions                                                                                                    | Min  | Тур | Max | Unit |  |

|-----------------------------------------------------------------|----------------------------|--------------------------------------------------------------------------------------------------------------------|------|-----|-----|------|--|

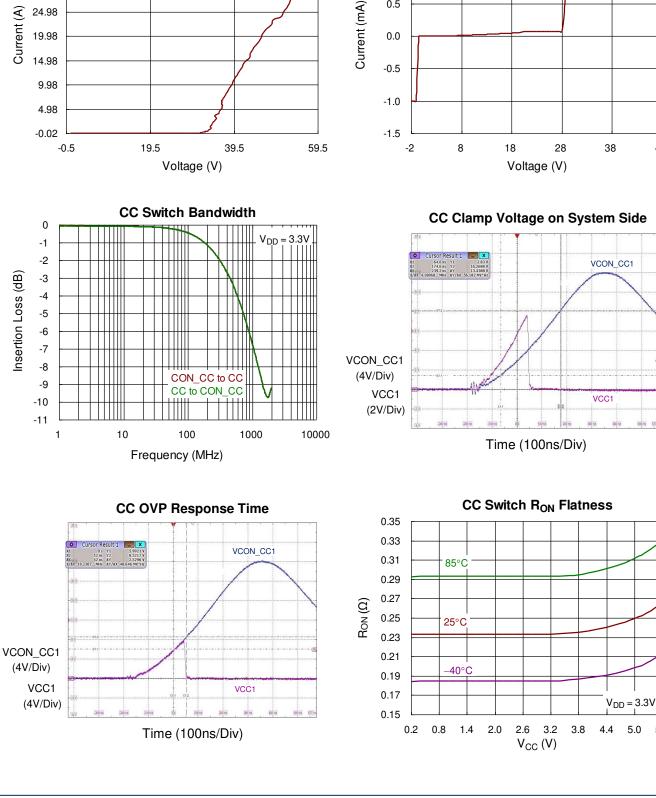

| On Bandwidth Single Ended (-3dB)                                | BWcc                       | Single ended, $50\Omega$ terminal, $V_{CCx} = 0.1V$ to 1.2V                                                        |      | 400 |     | MHz  |  |

| Clamp Voltage on System<br>Side                                 | VCLAMP                     | Hot plug voltage CON_CCx from 0V to 24V, 40V/ $\mu$ s; load 30 $\Omega$ in series to GND on CCx                    |      |     | 8   | V    |  |

| SBU Switch Characteristics                                      | SBU Switch Characteristics |                                                                                                                    |      |     |     |      |  |

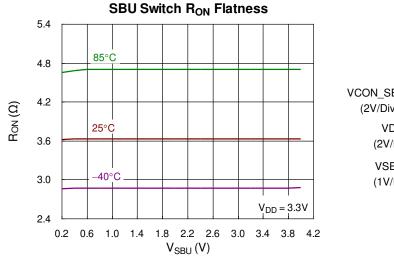

| Switch Turn on Resistance                                       | Ron_sbu                    | V <sub>DD</sub> = 3.3V, V <sub>SBUx</sub> = 3.6V                                                                   |      | 3.6 | 6.5 | Ω    |  |

| Switch Turn on Resistance<br>Flatness                           | RON_SBU_FLAT               | Sweep SBUx voltage between 0V and 3.6V                                                                             |      | 30  | 150 | mΩ   |  |

| Equivalent on Capacitance                                       | Con_sbu                    | Capacitance between<br>SBUx/CON_SBUx and<br>Ground when powered<br>on. VDD = 3.3V, VSBUx =<br>0V to 1.2V, f = 1MHz |      | 6.4 |     | pF   |  |

| OVP Threshold on SBU<br>Pins                                    | Vovpsbu                    | V <sub>DD</sub> = 3.3V, CON_SBUx<br>rises from 4.5V until<br>FLAGB goes from H to L                                | 4.35 | 4.5 | 4.7 | V    |  |

| Hysteresis on SBU OVP                                           | VOVPSBU_HYS                | V <sub>DDf</sub> = 3.3V, CON_SBUx<br>falls from 4.8V until<br>FLAGB goes from L to H                               |      | 60  |     | mV   |  |

| On Bandwidth Single Ended<br>(-3dB)                             | BWSBU                      | Single ended, $50\Omega$ terminal, V <sub>SBUx</sub> = 0.1V to 1.2V                                                |      | 1.1 |     | GHz  |  |

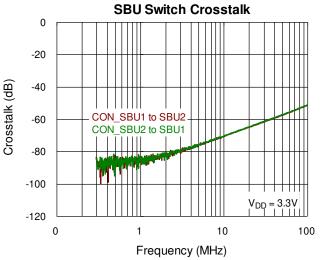

| Crosstalk                                                       | Xtalk                      | Swing 1VPP at 1MHz,<br>measure the SBU1 to<br>CON_SBU2 or SBU2 to<br>CON_SBU1 with $50\Omega$<br>terminal          |      | -80 |     | dB   |  |

| Clamp Voltage on System<br>Side                                 | VCLAMP                     | Hot plug voltage CON_SBUx from 0V to 24V, 40V/ $\mu$ s; load 100nF cap and 40 $\Omega$ in series to GND on SBUx    |      |     | 8   | V    |  |

| <b>Over-Temperature Protection</b>                              | on                         |                                                                                                                    |      |     | -   | -    |  |

| Over-Temperature<br>Protection Shutdown<br>Threshold Rising     | Tsd                        | V <sub>DD</sub> = 3.3V                                                                                             |      | 150 |     | °C   |  |

| Over-Temperature<br>Protection Shutdown<br>Threshold Hysteresis | Tsd_hys                    | VDD = 3.3V                                                                                                         |      | 20  |     | °C   |  |

| FLAGB Characteristics                                           |                            |                                                                                                                    |      |     |     |      |  |

| Low-Level Output Voltage                                        | Vol                        | IOL = 5mA                                                                                                          |      |     | 0.4 | V    |  |

| VIH High-Level Leakage<br>Current                               | Іон                        | VFLAGB = 5.5V                                                                                                      |      |     | 1   | μA   |  |

6

| <b>RT1738A</b> |  |

|----------------|--|

|----------------|--|

| Parameter                                                                                                                            | Symbol                  | Test Conditions                                                                    | Min  | Тур              | Max | Unit |

|--------------------------------------------------------------------------------------------------------------------------------------|-------------------------|------------------------------------------------------------------------------------|------|------------------|-----|------|

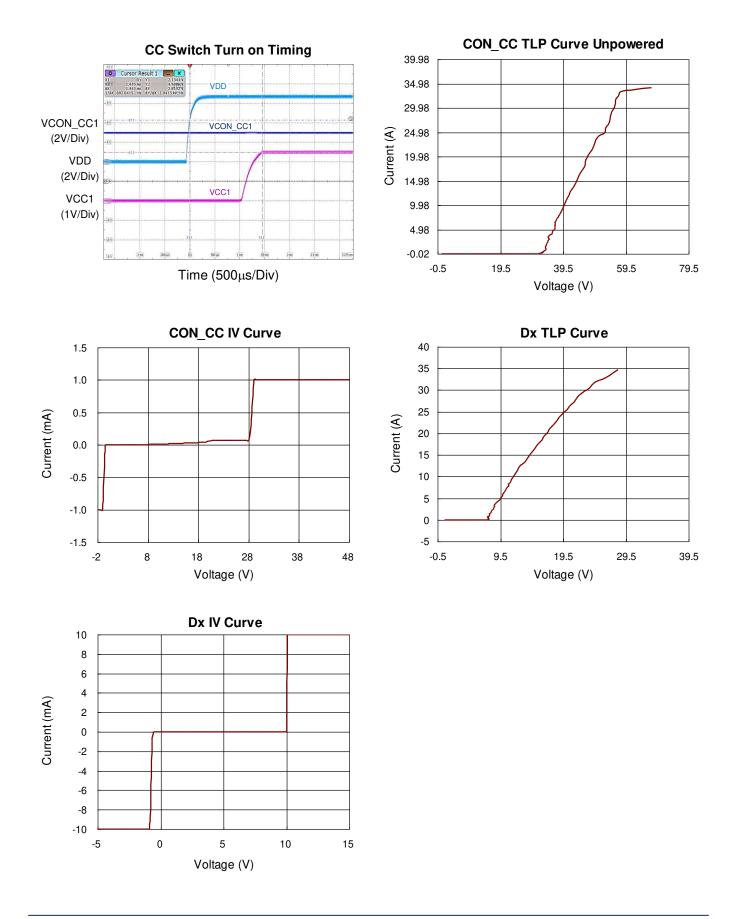

| Dx ESD Protection                                                                                                                    |                         |                                                                                    |      |                  |     |      |

| Reverse Stand-Off Voltage from Dx to GND                                                                                             | VRWM_POS                | Dx to GND. IDx ≤ 1μA                                                               |      |                  | 5.5 | V    |

| Reverse Stand-Off Voltage from GND to Dx                                                                                             | VRWM_NEG                | GND to Dx                                                                          |      |                  | 0   | V    |

| Break-Down Voltage from<br>Dx to GND                                                                                                 | VBR_POS                 | Dx to GND. IBR = 1mA                                                               | 7    |                  |     | V    |

| Break-Down Voltage from GND to Dx                                                                                                    | VBR_NEG                 | GND to Dx. IBR = 8mA                                                               | 0.6  |                  |     | V    |

| Dx to GND or GND to Dx                                                                                                               | Сю                      | f= 1MHz, VIO = 2.5V                                                                |      | D1 = 3<br>D2 = 3 |     | pF   |

| Differential Capacitance<br>between Two Dx Pins                                                                                      | ΔCΙΟ                    | f = 1MHz, VIO = 2.5V                                                               |      | 0.02             |     | pF   |

| Dynamic On-Resistance Dx<br>IEC Clamps                                                                                               | Rdyn                    | Dx to GND or GND to Dx                                                             |      | 0.45             |     | Ω    |

| Switch Dynamic Character                                                                                                             | stics                   |                                                                                    |      |                  |     |      |

| Turn-On Time, Time form<br>Rising VDD UVLO to CC<br>Switches Turn on                                                                 | ton_cc                  | V <sub>DD</sub> power-up from<br>UVLO until CCx switches<br>fully turn on          |      | 1.5              |     | ms   |

| Turn-On Time, Time from<br>Rising VDD UVLO to SBU<br>Switches Turn On                                                                | ton_sbu                 | VDD power-up from<br>UVLO until SBUx<br>switches fully turn on                     |      | 1.3              |     | ms   |

| Time from Crossing Rising<br>V <sub>DD</sub> UVLO until CC and<br>SBU Switches Turn On and<br>the Dead Battery Resistors<br>Turn Off | ton_db                  | V <sub>DD</sub> power-up from<br>UVLO until the dead<br>battery resistors turn off |      | 5                |     | ms   |

| Minimum Slew Rate<br>Allowed to Ensure CC and<br>SBU Switches Turn Off<br>during a Power Off                                         | dVDD_OFF/dt             |                                                                                    | -0.5 |                  |     | V/µs |

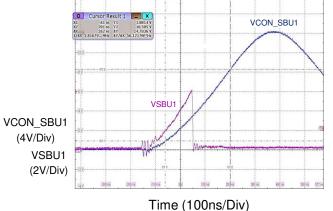

| OVP Response Time on the<br>CC Switches. Time from<br>OVP Predicated until<br>Switches Turn Off                                      | tovp_response_cc        | Time from OVP trip<br>voltage predicated to<br>switches to turn OFF                |      | 60               |     | ns   |

| OVP Response Time on the<br>SBU Switches. Time from<br>OVP Predicated until<br>Switches Turn Off                                     | tovp_response_sbu       | Time from OVP trip<br>voltage predicated to<br>switches to turn OFF                |      | 60               |     | ns   |

| OVP Recovery Time on the CCx                                                                                                         | tovp_recovery_cc        | CON_CCx OVP remove<br>until CCx switches fully<br>turn back on                     |      | 0.87             |     | ms   |

| OVP Recovery Time on the SBUx                                                                                                        | tOVP_RECOVERY_SBU       | CON_SBUx OVP remove<br>until SBUx switches fully<br>turn back on                   |      | 0.75             |     | ms   |

| OVP Recovery Time on the<br>CON_CCx's Dead Battery<br>Resistors                                                                      | tovp_recovery_cc_d<br>B | CON_CCx OVP remove<br>until the dead battery<br>resistors turn back off            |      | 5                |     | ms   |

| Parameter                                                           | Symbol                     | Test Conditions                                      | Min | Тур | Max | Unit |

|---------------------------------------------------------------------|----------------------------|------------------------------------------------------|-----|-----|-----|------|

| Time from OVP Asserted to FLAGB Assertion                           | tOVP_FLAGB_<br>ASSERTION   | Switches OVP asserted until FLAGB pull down          | 10  | 20  | 40  | μS   |

| Time from Switches Turn<br>On after an OVP to FLAGB<br>De-Assertion | tovp_flagb_<br>deassertion | Switches OVP<br>de-asserted until FLAGB<br>pull high |     | 5   |     | ms   |

| Time from OTP to FLABG<br>Assertion                                 | tOTP_FLAGB_<br>ASSERTION   | Switches OTP<br>de-asserted until FLAGB<br>pull down | 10  | 20  | 40  | μS   |

**Note 1.** Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

Note 2.  $\theta_{JA}$  is measured under natural convection (still air) at  $T_A = 25^{\circ}C$  with the component mounted on a high effective-thermal-conductivity four-layer test board on a JEDEC 51-7 thermal measurement standard.  $\theta_{JC}$  is measured at the exposed pad of the package.

Note 3. Devices are ESD sensitive. Handling precaution is recommended.

Note 4. The device is not guaranteed to function outside its operating conditions.

## **Typical Application Circuit**

Table 1. Recommended Components Information

| Reference | Q'ty | Part Number     | Description   | Package | Manufacturer |

|-----------|------|-----------------|---------------|---------|--------------|

| Cvdd      | 1    | TMK107BJ105KA-T | 1μF/X5R/25V   | 0603    | TAIYO YUDEN  |

| CVBIAS    | 1    | 0402B104K500CT  | 0.1µF/50V/X7R | 0402    | WALSIN       |

| R1        | 1    | RTT021003FTH    | 100k          | 0402    | RALEC        |

# **Typical Operating Characteristics**

**RT1738A**

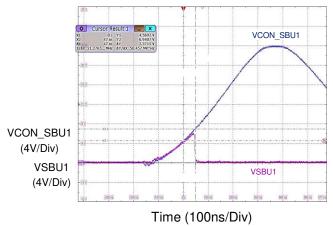

SBU Clamp Voltage on System Side

SBU Switch Turn on Timing

39.98

34.98

29.98

24.98

Current (A)

Insertion Loss (dB)

**CON SBU TLP Curve Unpowered**

Copyright © 2023 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

5.0 5.6

# **RT1738A**

48

**CON SBU IV Curve**

1.5

1.0

0.5

### **Application Information**

Richtek's component specification does not include the following information in the Application Information section. Thereby no warranty is given regarding its validity and accuracy. Customers should take responsibility to verify their own designs and to ensure the functional suitability of their components and systems.

### 6-Channels of IEC 61000-4-2 ESD Protection (CON\_CC1, CON\_CC2, CON\_SBU1, CON\_SBU2, D1 and D2)

The RT1738A provides 6-Channels of IEC 61000-4-2 system level ESD protection for the CC1, CC2, SBU1, SBU2, D1 and D2 pins. As USB Type-C interface need IEC system level ESD protection in order to provide plenty protection for the ESD events that the connector can be exposed to end users.

#### Input Over-Voltage Protection

The RT1738A has 4-channels of Short to VBUS overvoltage protection for the CC1, CC2, SBU1 and SBU2 pins of the USB Type-C receptacle via internal OVP level. When the input voltage exceeds the OVP level, the RT1738A will ultra-fast turn off internal switches around 60ns to prevent the high input voltage from damaging the end system. When the CC/SBU input voltage returns to normal operation voltage range with hysteresis 75/60mV, the will turn on the switches to turn on channel.

All switches for CC1/2 and SBU1/2 are each own OVP comparator and controlled by its comparator independently. If any one of channel voltage exceed OVP threshold, the channel switch is turned off, and the others switches are also turned off.

#### **Over-Temperature Protection (OTP)**

The RT1738A monitors its internal temperature to prevent thermal failures. The chip turns off the switches when the junction temperature reaches 150°C. The IC will resume after the junction temperature is cooled down 20°C.

#### **Dead Battery**

The RT1738A supports dead battery function. If system side haven't enough power to provide the RT1738A work, short the RPD\_G1 pin to the CON\_CC1 pin, and short the RPD\_G2 pin to the CON\_CC2 pin. When it is connected to a Source, DRP or Sourcing Device, the system will receive the default VBUS.

If dead battery function is not required in application, connect the RPD\_G1 and RPD\_G2 pins to ground.

#### **FLAGB** Pin Operation

The FLAGB operation for fault reporting. When OVP or OTP event occurred, FLAGB pin will pull low until fault event assert. Time from OVP or OTP to FLAGB pull down is around  $20\mu$ s, then time from OVP asserted to FLAGB assertion is around 5ms.

#### How to Connect Unused Pins

If the RPD\_Gx pins, the Dx pins and the NC pin 16, 17 are unused in a design, they must be connected to GND.

#### **Device Functional Modes**

The RT1738A all functional modes.

|                                   | MODE                                   | VDD    | RPD_Gx                | TJ   | FLAGB  | CC<br>Switches | SBU<br>Switches |

|-----------------------------------|----------------------------------------|--------|-----------------------|------|--------|----------------|-----------------|

| Normal<br>Operating<br>Conditions | Powered Off<br>No Dead Battery Support | < UVLO | Grounded              |      | High-Z | OFF            | OFF             |

|                                   | Powered Off<br>Dead Battery Support    | < UVLO | Shorted to<br>CON_CCx |      | High-Z | OFF            | OFF             |

|                                   | Powered On                             | > UVLO | Forced OFF            | < 0T | High-Z | ON             | ON              |

|                                   | Thermal shutdown                       | > UVLO | Forced OFF            | > OT | Low    | OFF            | OFF             |

| Fault<br>Conditions               | CC Over-Voltage Condition              | > UVLO | Forced OFF            | < 0T | Low    | OFF            | OFF             |

|                                   | SBU Over-Voltage<br>Condition          | > UVLO | Forced OFF            | < 0T | Low    | OFF            | OFF             |

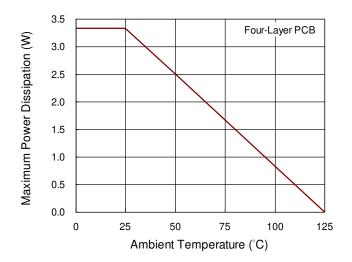

#### **Thermal Considerations**

The junction temperature should never exceed the absolute maximum junction temperature  $T_{J(MAX)}$ , listed under Absolute Maximum Ratings, to avoid permanent damage to the device. The maximum allowable power dissipation depends on the thermal resistance of the IC package, the PCB layout, the rate of surrounding airflow, and the difference between the junction and ambient temperatures. The maximum power dissipation can be calculated using the following formula :

$\mathsf{P}_{\mathsf{D}(\mathsf{MAX})} = (\mathsf{T}_{\mathsf{J}(\mathsf{MAX})} - \mathsf{T}_{\mathsf{A}}) / \theta_{\mathsf{J}\mathsf{A}}$

where  $T_{J(MAX)}$  is the maximum junction temperature, TA is the ambient temperature, and  $\theta_{JA}$  is the junction-to-ambient thermal resistance.

For continuous operation, the maximum operating junction temperature indicated under Recommended Conditions 125°C. The Operating is junction-to-ambient thermal resistance,  $\theta_{JA}$ , is highly package dependent. For a WQFN-20L 3x3 package, the thermal resistance,  $\theta_{JA}$ , is 30°C/W on a standard JEDEC 51-7 high effective-thermal-conductivity four-layer test board. The maximum power dissipation at TA = 25°C can be calculated as below :

$\mathsf{PD}(\mathsf{MAX})$  = (125°C - 25°C) / (30°C/W) = 3.33W for a WQFN-20L 3x3 package.

The maximum power dissipation depends on the operating ambient temperature for the fixed  $T_{J}(MAX)$  and the thermal resistance,  $\theta_{JA}$ . The derating curves in Figure 1 allows the designer to see the effect of rising ambient temperature on the maximum power dissipation.

Figure 1. Derating Curve of Maximum Power Dissipation

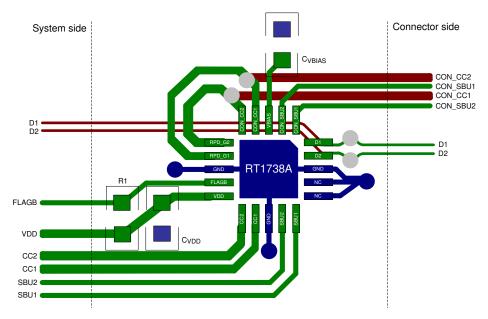

#### Layout Considerations

Appropriate routing and placement is significant to maintain the signal integrity the USB2.0, SBU, CC signals. The following guidelines apply to the RT1738A: Place the bypass capacitors close to the VDD pin, and ESD protection capacitor close to the VBIAS pin. Capacitors must be attached to a solid ground. This minimizes voltage disturbances during such as short to VBUS and ESD event. The USB2.0 and SBU trace need to be routed straight and sharp bends must be minimized.

Standard ESD suggestion apply to the CON\_CC1, CON \_CC2, CON \_SBU1, CON \_SBU2, D1, and D2 pins as well :

The optimum placement for the device is as close to the connector as possible. The PCB designer must be keeping out unprotected traces away from the protected traces which are between the RT1738A and the connector.

Route the protected path as straight as possible. Reduce any sharp corners on the protected traces between the connector by using rounded corners with the largest radii possible. Suggest to reduce Dx pin via up to another layer and to continue that trace on that same layer.

Figure 2. RT1738A Layout Guide

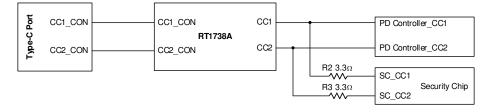

#### CC1 and CC2 Add Series Resistor with Security Chip

The RT1738A is applied with the factory customization's security chip platform that need CC1 and CC2 add series resistor with security chip. The security chip CC AMR is lower than 6V that but RT1738A CC AMR is 6V. That will have a system IEC61000-4-2 ESD test fail issue and cause to security chip damage. Add a series  $3.3\Omega$  resistor with security chip can be avoided ESD fail, that will system IEC61000-4-2 ESD contact discharge ±8kV pass. Then if RT1738A's application with factory customization's security chip, the proposal schematic is as shown below :

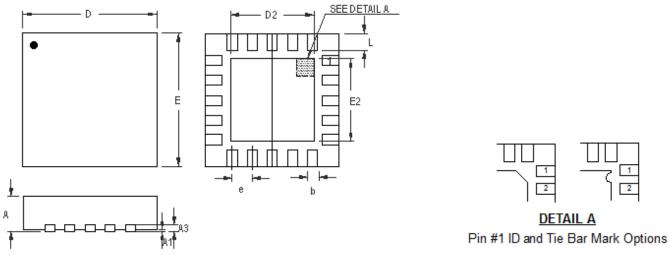

# **Outline Dimension**

Note : The configuration of the Pin #1 identifier is optional, but must be located within the zone indicated.

| Cumhal | Dimensions I | n Millimeters | <b>Dimensions In Inches</b> |       |  |  |

|--------|--------------|---------------|-----------------------------|-------|--|--|

| Symbol | Min          | Max           | Min                         | Max   |  |  |

| А      | 0.700        | 0.800         | 0.028                       | 0.031 |  |  |

| A1     | 0.000        | 0.050         | 0.000                       | 0.002 |  |  |

| A3     | 0.175        | 0.250         | 0.007                       | 0.010 |  |  |

| b      | 0.150        | 0.250         | 0.006                       | 0.010 |  |  |

| D      | 2.900        | 3.100         | 0.114                       | 0.122 |  |  |

| D2     | 1.650        | 1.750         | 0.065                       | 0.069 |  |  |

| E      | 2.900        | 3.100         | 0.114                       | 0.122 |  |  |

| E2     | 1.650        | 1.750         | 0.065                       | 0.069 |  |  |

| е      | 0.4          | 00            | 0.016                       |       |  |  |

| L      | 0.350        | 0.450         | 0.014                       | 0.018 |  |  |

W-Type 20L QFN 3x3 Package

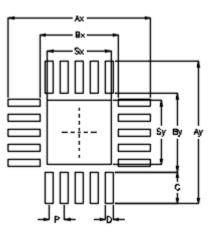

# **Footprint Information**

|                  | Number of |      | Footprint Dimension (mm) |      |      |      |      |      |      |      | Telerence |

|------------------|-----------|------|--------------------------|------|------|------|------|------|------|------|-----------|

| Package          | Pin       | Р    | Ax                       | Ау   | Bx   | Ву   | С    | D    | Sx   | Sy   | Tolerance |

| V/W/U/XQFN3*3-20 | 20        | 0.40 | 3.80                     | 3.80 | 2.10 | 2.10 | 0.85 | 0.20 | 1.70 | 1.70 | ±0.05     |

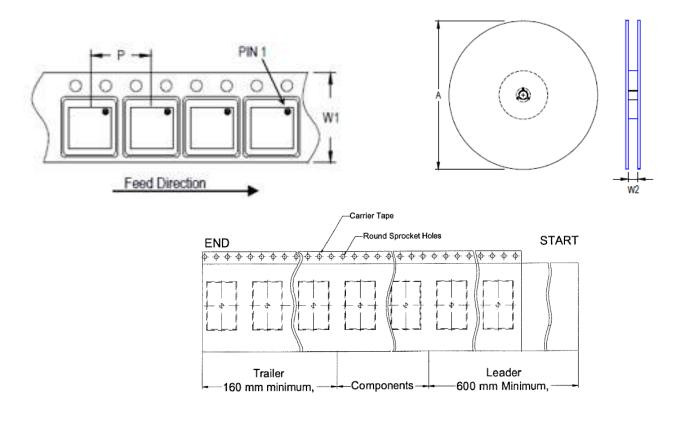

### **Packing Information**

### Tape and Reel Data

| Package Type   | Tape Size | Pocket Pitch | Reel Si | ze (A) | Units    | Trailer | Leader | Reel Width (W2) |

|----------------|-----------|--------------|---------|--------|----------|---------|--------|-----------------|

|                | (W1) (mm) | (P) (mm)     | (mm)    | (in)   | per Reel | (mm)    | (mm)   | Min./Max. (mm)  |

| QFN/DFN<br>3x3 | 12        | 8            | 180     | 7      | 1,500    | 160     | 600    | 12.4/14.4       |

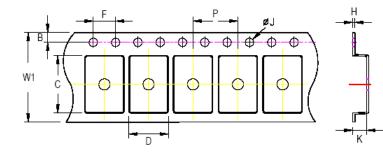

C, D and K are determined by component size. The clearance between the components and the cavity is as follows:

- For 12mm carrier tape: 0.5mm max.

| Tape Size | W1     | Р     |       | В      |        | F     |       | ØJ    |       | Н     |

|-----------|--------|-------|-------|--------|--------|-------|-------|-------|-------|-------|

| Tape Size | Max.   | Min.  | Max.  | Min.   | Max.   | Min.  | Max.  | Min.  | Max.  | Max.  |

| 12mm      | 12.3mm | 7.9mm | 8.1mm | 1.65mm | 1.85mm | 3.9mm | 4.1mm | 1.5mm | 1.6mm | 0.6mm |

#### **Tape and Reel Packing**

| Step | Photo/Description                      | Step | Photo/Description                  |

|------|----------------------------------------|------|------------------------------------|

| 1    |                                        | 4    |                                    |

|      | Reel 7"                                |      | 3 reels per inner box <b>Box A</b> |

| 2    |                                        | 5    |                                    |

|      | HIC & Desiccant (1 Unit) inside        |      | 12 inner boxes per outer box       |

| 3    |                                        | 6    | RIGHTER<br>MARINE<br>BERTAR        |

|      | Caution label is on backside of Al bag |      | Outer box Carton A                 |

| Container   | F    | leel  |       | Box           | Box   |       |          | Carton            |               |        |

|-------------|------|-------|-------|---------------|-------|-------|----------|-------------------|---------------|--------|

| Package     | Size | Units | Item  | Size(cm)      | Reels | Units | Item     | Size(cm)          | Boxes         | Unit   |

|             | 7"   | 1 500 | Box A | 18.3*18.3*8.0 | 3     | 4,500 | Carton A | 38.3*27.2*38.3    | 12            | 54,000 |

| QFN/DFN 3x3 | 1    | 1,500 | Box E | 18.6*18.6*3.5 | 1     | 1,500 |          | For Combined or F | Partial Reel. |        |

#### Packing Material Anti-ESD Property

| Surface<br>Resistance | Aluminum Bag                        | Reel                                | Cover tape                          | Carrier tape                        | Tube                                | Protection Band                     |

|-----------------------|-------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|

| $\Omega/cm^2$         | 10 <sup>4</sup> to 10 <sup>11</sup> |

### **Richtek Technology Corporation**

14F, No. 8, Tai Yuen 1<sup>st</sup> Street, Chupei City Hsinchu, Taiwan, R.O.C. Tel: (8863)5526789

RICHTEK

Richtek products are sold by description only. Richtek reserves the right to change the circuitry and/or specifications without notice at any time. Customers should obtain the latest relevant information and data sheets before placing orders and should verify that such information is current and complete. Richtek cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Richtek product. Information furnished by Richtek is believed to be accurate and reliable. However, no responsibility is assumed by Richtek or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Richtek or its subsidiaries.

Copyright © 2023 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

www.richtek.com

### **Datasheet Revision History**

| Version | Date     | Description | Item                                                                     |

|---------|----------|-------------|--------------------------------------------------------------------------|

| 01      | 2023/3/2 | Modify      | Application Information on P13, 15<br>Packing Information on P18, 19, 20 |