| <b>Discontinued Product</b>                                                                                                                 |  |  |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| These parts are no longer in production The device should not be<br>purchased for new design applications. Samples are no longer available. |  |  |  |  |  |  |  |

| Date of status change: May 3, 2010                                                                                                          |  |  |  |  |  |  |  |

| <b>Recommended Substitutions:</b>                                                                                                           |  |  |  |  |  |  |  |

| For existing customer transition, and for new customers or new appli-<br>cations, refer to your Allegro sales representative.               |  |  |  |  |  |  |  |

|                                                                                                                                             |  |  |  |  |  |  |  |

|                                                                                                                                             |  |  |  |  |  |  |  |

|                                                                                                                                             |  |  |  |  |  |  |  |

|                                                                                                                                             |  |  |  |  |  |  |  |

| NOTE: For detailed information on purchasing options, contact your local Allegro field applications engineer or sales representative.       |  |  |  |  |  |  |  |

Allegro MicroSystems, Inc. reserves the right to make, from time to time, revisions to the anticipated product life cycle plan for a product to accommodate changes in production capabilities, alternative product availabilities, or market demand. The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems, Inc. assumes no responsibility for its use; nor for any infringements of patents or other rights of third parties which may result from its use.

#### **Features and Benefits**

- 50 V minimum output clamp voltage

- 250 mA output current (all outputs simultaneously)

- 1.3  $\Omega$  typical  $r_{DS(on)}$

- Low power consumption

- Replacements for TPIC6595N and TPIC6595DW

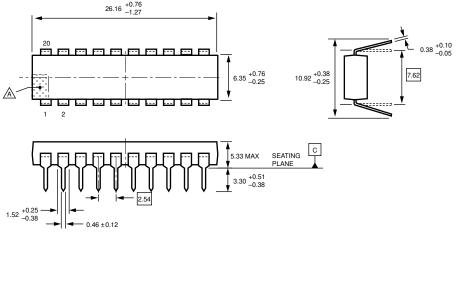

#### Package: 20-pin DIP (suffix A)

Not to scale

#### Description

The A6595 combines an 8-bit CMOS shift register and accompanying data latches, control circuitry, and DMOS power driver outputs. Power driver applications include relays, solenoids, and other medium-current or high-voltage peripheral power loads.

The serial-data input, CMOS shift register and latches allow direct interfacing with microprocessor-based systems. Serial-data input rates are over 5 MHz. Use with TTL may require appropriate pull-up resistors to ensure an input logic high.

A CMOS serial-data output enables cascade connections in applications requiring additional drive lines.

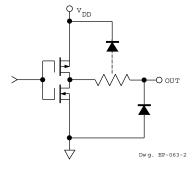

The A6595 DMOS open-drain outputs are capable of sinking up to 750 mA. All of the output drivers are disabled (the DMOS sink drivers turned off) by the OUTPUT ENABLE input high.

The A6595 is furnished in a 20-pin dual in-line plastic package that is lead (Pb) free, with 100% matte tin leadframe plating. Copper leadframe base material, reduced supply current requirements, and low on-state resistance allow the device to sink 150 mA from all outputs continuously, to ambient temperatures to 125°C.

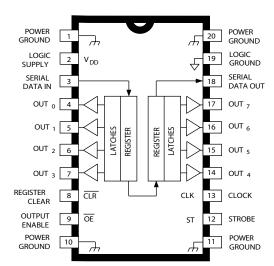

#### **Pin-out Diagram**

#### Selection Guide

| Part Number | Packing            |

|-------------|--------------------|

| A6595KA-T   | 18 pieces per tube |

#### **Absolute Maximum Ratings\***

| Characteristic                | Symbol               | Notes                                                                             | Rating      | Units |

|-------------------------------|----------------------|-----------------------------------------------------------------------------------|-------------|-------|

| Logic Supply Voltage          | V <sub>DD</sub>      |                                                                                   | 7.0         | V     |

| Input Voltage Range           | VI                   |                                                                                   | -0.3 to 7.0 | V     |

| Output Voltage                | Vo                   |                                                                                   | 50          | V     |

|                               | Ι <sub>Ο</sub>       | Continuous, each output, all outputs on                                           | 250         | mA    |

| Output Drain Current          | I <sub>OM</sub>      | Pulsed $t_w \le 100 \ \mu s$ , duty cycle $\le 2\%$ ; each output, all outputs on | 750         | mA    |

|                               |                      | Pulsed $t_w \leq 100 \ \mu s$ , duty cycle $\leq 2\%$ ;                           | 2.0         | A     |

| Single-Pulse Avalanche Energy | E <sub>AS</sub>      |                                                                                   | 75          | mJ    |

| Operating Ambient Temperature | T <sub>A</sub>       | Range K                                                                           | -40 to 125  | °C    |

| Maximum Junction Temperature  | T <sub>J</sub> (max) |                                                                                   | 150         | °C    |

| Storage Temperature           | T <sub>stg</sub>     |                                                                                   | -55 to 150  | °C    |

\*These CMOS devices have input static protection (Class 3) but are still susceptible to damage if exposed to extremely high static electrical charges.

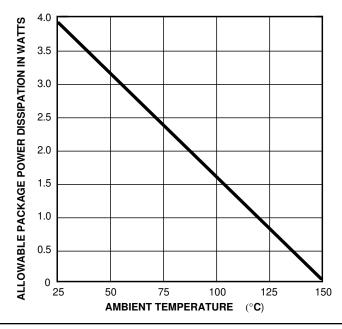

#### Thermal Characteristics may require derating at maximum conditions, see application information

| Characteristic             | Symbol          | Test Conditions*                       | Value | Units |

|----------------------------|-----------------|----------------------------------------|-------|-------|

| Package Thermal Resistance | $R_{\theta JA}$ | On 4-layer PCB based on JEDEC standard | 32    | °C/W  |

\*Additional thermal information available on the Allegro website.

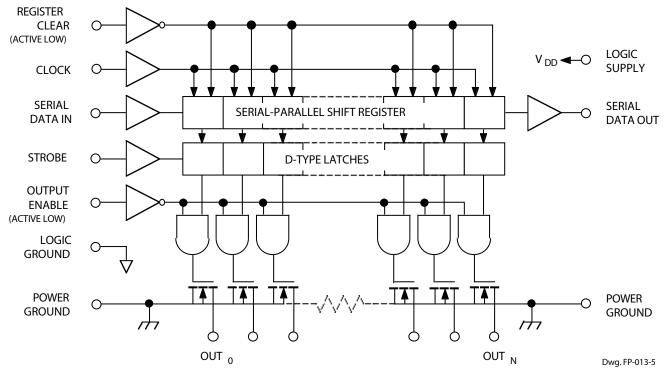

**Functional Block Diagram**

Grounds (terminals 1, 10, 11, 19, and 20) must be connected together externally.

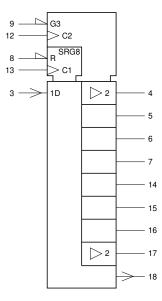

#### **Device Logic Diagram**

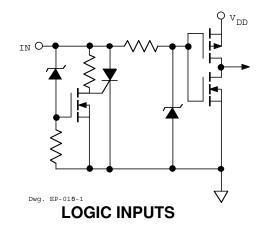

## DMOS POWER DRIVER OUTPUT

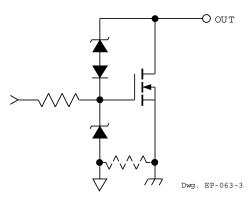

### SERIAL DATA OUT

#### **TRUTH TABLE**

| Data | Clock |                | nift F         | Regis          | ter C | ontei          | nts            | Serial<br>Data |        |                | Lat            | ch Co | onten | its            |                | Output |                | Out            | put C | Conte | ents           |                |

|------|-------|----------------|----------------|----------------|-------|----------------|----------------|----------------|--------|----------------|----------------|-------|-------|----------------|----------------|--------|----------------|----------------|-------|-------|----------------|----------------|

|      | Input | I <sub>0</sub> | I <sub>1</sub> | l <sub>2</sub> |       | I <sub>6</sub> | ۱ <sub>7</sub> | Output         | Strobe | I <sub>0</sub> | I <sub>1</sub> | $I_2$ |       | I <sub>6</sub> | I <sub>7</sub> | Enable | I <sub>0</sub> | I <sub>1</sub> | $I_2$ |       | I <sub>6</sub> | I <sub>7</sub> |

| н    | Г     | Н              | $R_0$          | R <sub>1</sub> |       | $R_5$          | $R_6$          | R <sub>6</sub> |        |                |                |       |       |                |                |        |                |                |       |       |                |                |

| L    | Г     | L              | R <sub>0</sub> | R <sub>1</sub> |       | $R_5$          | $R_6$          | R <sub>6</sub> |        |                |                |       |       |                |                |        |                |                |       |       |                |                |

| Х    | l     | R <sub>0</sub> | R <sub>1</sub> | $R_2$          |       | $R_6$          | R <sub>7</sub> | R <sub>7</sub> |        |                |                |       |       |                |                |        |                |                |       |       |                |                |

|      |       | х              | х              | х              |       | х              | х              | Х              | _      | R <sub>0</sub> | $R_1$          | $R_2$ |       | $R_6$          | R <sub>7</sub> |        |                |                |       |       |                |                |

|      |       | P <sub>0</sub> | Р <sub>1</sub> | $P_2$          |       | $P_6$          | P <sub>7</sub> | P <sub>7</sub> | Г      | P <sub>0</sub> | P <sub>1</sub> | $P_2$ |       | P <sub>6</sub> | P <sub>7</sub> | L      | P <sub>0</sub> | P <sub>1</sub> | $P_2$ |       | $P_6$          | P <sub>7</sub> |

|      |       |                |                |                |       |                |                |                |        | х              | Х              | Х     |       | х              | Х              | Н      | Н              | Н              | Н     |       | Н              | Н              |

L = Low Logic Level H = High Logic Level X = Irrelevant P = Present State R = Previous Stat e

4

### **RECOMMENDED OPERATING CONDITIONS**

over operating temperature range

| Logic Supply Voltage Range, V <sub>DD</sub> | 4.5 V to 5.5 V        |

|---------------------------------------------|-----------------------|

| High-Level Input Voltage, V <sub>IH</sub>   | ≥ 0.85V <sub>DD</sub> |

| Low-level input voltage, V <sub>IL</sub>    | ≤0.15V <sub>DD</sub>  |

# ELECTRICAL CHARACTERISTICS at T<sub>A</sub> = +25°C, V<sub>DD</sub> = 5 V, t<sub>ir</sub> = t<sub>if</sub> $\leq$ 10 ns (unless otherwise specified).

|                             |                       |                                                                 |      | Lin   | nits |       |

|-----------------------------|-----------------------|-----------------------------------------------------------------|------|-------|------|-------|

| Characteristic              | Symbol                | Test Conditions                                                 | Min. | Тур.  | Max. | Units |

| Output Breakdown<br>Voltage | V <sub>(BR)DSX</sub>  | I <sub>O</sub> = 1 mA                                           | 50   | —     | —    | V     |

| Off-State Output            | I <sub>DSX</sub>      | V <sub>O</sub> = 40 V                                           | _    | 0.05  | 1.0  | μA    |

| Current                     |                       | V <sub>O</sub> = 40 V, T <sub>A</sub> = 125°C                   |      | 0.15  | 5.0  | μA    |

| Static Drain-Source         | r <sub>DS(on)</sub>   | I <sub>O</sub> = 250 mA, V <sub>DD</sub> = 4.5 V                | _    | 1.3   | 2.0  | Ω     |

| On-State Resistance         |                       | $I_{\rm O}$ = 250 mA, $V_{\rm DD}$ = 4.5 V, $T_{\rm A}$ = 125°C | _    | 2.0   | 3.2  | Ω     |

|                             |                       | $I_{O}$ = 500 mA, $V_{DD}$ = 4.5 V (see note)                   | _    | 1.3   | 2.0  | Ω     |

| Nominal Output<br>Current   | I <sub>ON</sub>       | V <sub>DS(on)</sub> = 0.5 V, T <sub>A</sub> = 85°C              | —    | 250   | _    | mA    |

| Logic Input Current         | I <sub>IH</sub>       | $V_{I} = V_{DD} = 5.5 V$                                        | _    | _     | 1.0  | μA    |

|                             | I <sub>IL</sub>       | V <sub>I</sub> = 0, V <sub>DD</sub> = 5.5 V                     | _    | _     | -1.0 | μA    |

| Logic Input Hysteresis      | V <sub>I(hys)</sub>   |                                                                 | _    | 1.3   | _    | V     |

| SERIAL-DATA                 | V <sub>OH</sub>       | I <sub>OH</sub> = -20 μA, V <sub>DD</sub> = 4.5 V               | 4.4  | 4.49  | _    | V     |

| Output Voltage              |                       | I <sub>OH</sub> = -4 mA, V <sub>DD</sub> = 4.5 V                | 4.1  | 4.3   | —    | V     |

|                             | V <sub>OL</sub>       | $I_{OL}$ = 20 µA, $V_{DD}$ = 4.5 V                              | _    | 0.002 | 0.1  | V     |

|                             |                       | I <sub>OL</sub> = 4 mA, V <sub>DD</sub> = 4.5 V                 | _    | 0.2   | 0.4  | V     |

| Prop. Delay Time            | t <sub>PLH</sub>      | I <sub>O</sub> = 250 mA, C <sub>L</sub> = 30 pF                 | _    | 650   | _    | ns    |

|                             | t <sub>PHL</sub>      | I <sub>O</sub> = 250 mA, C <sub>L</sub> = 30 pF                 | _    | 150   | _    | ns    |

| Output Rise Time            | t <sub>r</sub>        | I <sub>O</sub> = 250 mA, C <sub>L</sub> = 30 pF                 | _    | 7500  | _    | ns    |

| Output Fall Time            | t <sub>f</sub>        | I <sub>O</sub> = 250 mA, C <sub>L</sub> = 30 pF                 | _    | 425   | _    | ns    |

| Supply Current              | I <sub>DD(OFF)</sub>  | All inputs low                                                  | _    | 15    | 100  | μA    |

|                             | I <sub>DD(ON)</sub>   | $V_{DD}$ = 5.5 V, Outputs on                                    | _    | 150   | 300  | μA    |

|                             | I <sub>DD(fclk)</sub> | $f_{clk}$ = 5 MHz, $C_L$ = 30 pF, Outputs off                   | _    | 0.6   | 5.0  | mA    |

Typical Data is at VDD = 5 V and is for design information only. NOTE — Pulse test, duration  $\leq 100 \ \mu$ s, duty cycle  $\leq 2\%$ .

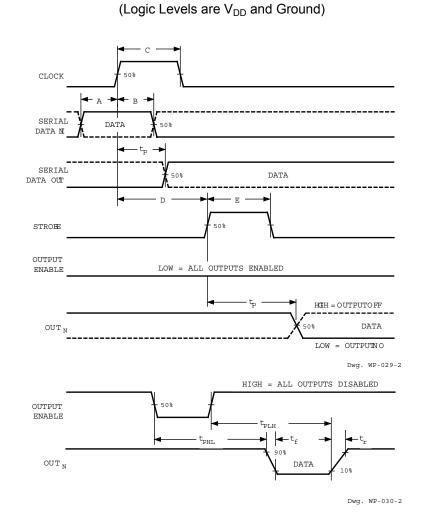

#### TIMING REQUIREMENTS and SPECIFICATIONS

| A. Data Active Time Before Clock Pulse<br>(Data Set-Up Time), t <sub>su(D)</sub>      | 10 ns         |

|---------------------------------------------------------------------------------------|---------------|

| <b>B.</b> Data Active Time After Clock Pulse                                          |               |

| (Data Hold Time), t <sub>h(D)</sub>                                                   |               |

| C. Clock Pulse Width, t <sub>w(CLK)</sub>                                             | 20 ns         |

| <b>D.</b> Time Between Clock Activation                                               |               |

| and Strobe, t <sub>su(ST)</sub>                                                       | 50 ns         |

| E. Strobe Pulse Width, t <sub>w(ST)</sub>                                             | 50 ns         |

| <b>F.</b> Output Enable Pulse Width, $t_{w(OE)}$                                      | <b>4.5 µs</b> |

| NOTE – Timing is representative of a 12.5 MHz clock.<br>Higher speeds are attainable. |               |

Serial data present at the input is transferred to the shift register on the rising edge of the CLOCK input pulse. On succeeding CLOCK pulses, the registers shift data information towards the SERIAL DATA OUTPUT.

Information present at any register is transferred to the respective latch on the rising edge of the STROBE input pulse (serial-to-parallel conversion).

When the OUTPUT ENABLE input is high, the output source drivers are disabled (OFF). The information stored in the latches is not affected by the OUTPUT ENABLE input. With the OUTPUT ENABLE input low, the outputs are controlled by the state of their respective latches.

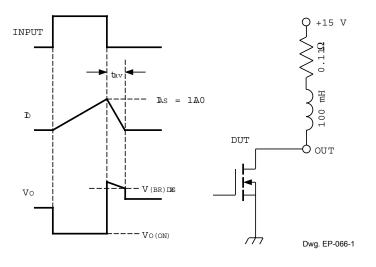

## **TEST CIRCUITS**

$E_{AS} = I_{AS} \times V_{(BR)DSX} \times t_{AV}/2$

#### Single-Pulse Avalanche Energy Test Circuit and Waveforms

## **TERMINAL DESCRIPTIONS**

| Terminal No. | Terminal Name      | Function                                                                                                   |

|--------------|--------------------|------------------------------------------------------------------------------------------------------------|

| 1            | POWER GROUND       | Reference terminal for output voltage measurements (OUT <sub>0.3</sub> ).                                  |

| 2            | LOGIC SUPPLY       | (V <sub>DD</sub> ) The logic supply voltage (typically 5 V).                                               |

| 3            | SERIAL DATA IN     | Serial-data input to the shift-register.                                                                   |

| 4-7          | OUT <sub>0-3</sub> | Current-sinking, open-drain DMOS output terminals.                                                         |

| 8            | CLEAR              | When (active) low, the registers are cleared (set low).                                                    |

| 9            | OUTPUT ENABLE      | When (active) low, the output drivers are enabled; when high, all output drivers are turned OFF (blanked). |

| 10           | POWER GROUND       | Reference terminal for output voltage measurements (OUT <sub>0.3</sub> ).                                  |

| 11           | POWER GROUND       | Reference terminal for output voltage measurements (OUT <sub>0.7</sub> ).                                  |

| 12           | STROBE             | Data strobe input terminal; shift register data is latched on rising edge.                                 |

| 13           | CLOCK              | Clock input terminal for data shift on rising edge.                                                        |

| 14-17        | OUT <sub>4-7</sub> | Current-sinking, open-drain DMOS output terminals.                                                         |

| 18           | SERIAL DATA OUT    | CMOS serial-data output to the following shift register.                                                   |

| 19           | LOGIC GROUND       | Reference terminal for input voltage measurements.                                                         |

| 20           | POWER GROUND       | Reference terminal for output voltage measurements (OUT <sub>4-7</sub> ).                                  |

NOTE — Grounds (terminals 1, 10, 11, 19, and 20) must be connected together externally.

### Package A, 20-Pin DIP

Preliminary dimensions, for reference only Dimensions in inches Metric dimensions (mm) in brackets, for reference only (reference JEDEC MS-001 AD) Dimensions exclusive of mold flash, gate burrs, and dambar protrusions Exact case and lead configuration at supplier discretion within limits shown Terminal #1 mark area

Copyright ©2000-2008, Allegro MicroSystems, Inc.

The products described here are manufactured under one or more U.S. patents or U.S. patents pending.

Allegro MicroSystems, Inc. reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the performance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon is current.

Allegro's products are not to be used in life support devices or systems, if a failure of an Allegro product can reasonably be expected to cause the failure of that life support device or system, or to affect the safety or effectiveness of that device or system.

The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems, Inc. assumes no responsibility for its use; nor for any infringement of patents or other rights of third parties which may result from its use.

For the latest version of this document, visit our website:

www.allegromicro.com