# 4-Channel, 12-/10-/8-Bit ADC with I<sup>2</sup>C-Compatible Interface in 8-Lead SOT-23

**Data Sheet**

AD7991/AD7995/AD7999

#### **FEATURES**

12-/10-/8-bit ADCs with fast conversion time: 1 µs typical 4 analog input channels/3 analog input channels with reference input Specified for V<sub>DD</sub> of 2.7 V to 5.5 V **Sequencer operation** Temperature range: -40°C to +125°C I<sup>2</sup>C-compatible serial interface supports standard, fast, and high speed modes 2 versions allow 2 I<sup>2</sup>C addresses Low power consumption Shutdown mode: 1 µA maximum 8-lead SOT-23 package

### **Qualified for automotive applications APPLICATIONS**

System monitoring **Battery-powered systems Data acquisition Medical instruments**

#### **GENERAL DESCRIPTION**

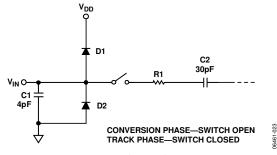

The AD7991/AD7995/AD7999 are 12-/10-/8-bit, low power, successive approximation ADCs with an I<sup>2</sup>C\*-compatible interface. Each part operates from a single 2.7 V to 5.5 V power supply and features a 1 µs conversion time. The track-and-hold amplifier allows each part to handle input frequencies of up to 14 MHz, and a multiplexer allows taking samples from four channels.

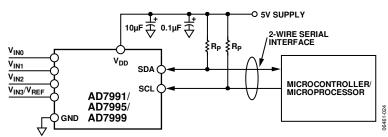

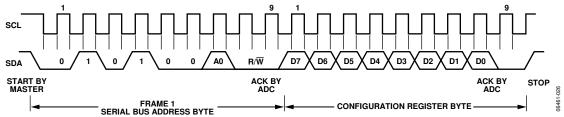

Each AD7991/AD7995/AD7999 provides a 2-wire serial interface compatible with I2C interfaces. The AD7991 and AD7995 come in two versions and each version has an individual I<sup>2</sup>C address. This allows two of the same devices to be connected to the same I<sup>2</sup>C bus. Both versions support standard, fast, and high speed I<sup>2</sup>C interface modes. The AD7999 comes in one version.

The AD7991/AD7995/AD7999 normally remain in a shutdown state, powering up only for conversions. The conversion process is controlled by a command mode, during which each I2C read operation initiates a conversion and returns the result over the I2C bus.

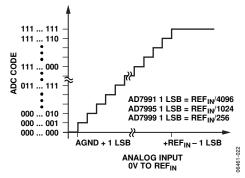

When four channels are used as analog inputs, the reference for the part is taken from V<sub>DD</sub>; this allows the widest dynamic input range to the ADC. Therefore, the analog input range to the

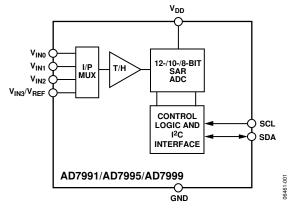

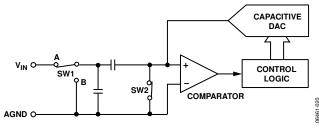

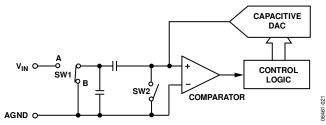

#### **FUNCTIONAL BLOCK DIAGRAM**

Figure 1.

ADC is 0 V to V<sub>DD</sub>. An external reference, applied through the V<sub>IN3</sub>/V<sub>REF</sub> input, can also be used with this part.

#### PRODUCT HIGHLIGHTS

- Four single-ended analog input channels, or three singleended analog input channels and one reference input channel.

- I<sup>2</sup>C-compatible serial interface. Standard, fast, and high speed modes.

- Automatic shutdown.

- Reference derived from the power supply or external

- 8-lead SOT-23 package.

Table 1. Related Devices

| Device | Resolution | Input Channels |

|--------|------------|----------------|

| AD7998 | 12         | 8              |

| AD7997 | 10         | 8              |

| AD7994 | 12         | 4              |

| AD7993 | 10         | 4              |

| AD7992 | 12         | 2              |

## AD7991/AD7995/AD7999

## **Data Sheet**

## **TABLE OF CONTENTS**

| Features                                                      | 1  |

|---------------------------------------------------------------|----|

| Applications                                                  | 1  |

| Functional Block Diagram                                      | 1  |

| General Description                                           | 1  |

| Product Highlights                                            | 1  |

| Revision History                                              |    |

| Specifications                                                | 3  |

| AD7991                                                        |    |

| AD7995                                                        | 5  |

| AD7999                                                        |    |

| I <sup>2</sup> C Timing Specifications                        |    |

| Absolute Maximum Ratings                                      |    |

| ESD Caution                                                   |    |

| Pin Configuration and Function Descriptions                   |    |

| -                                                             |    |

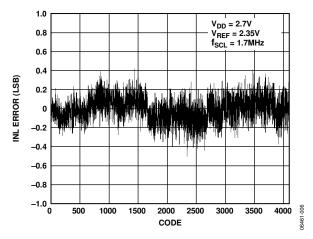

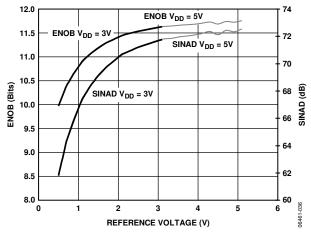

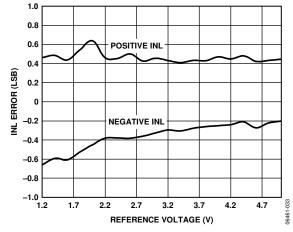

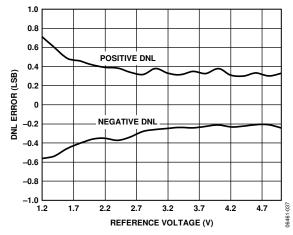

| Typical Performance Characteristics                           |    |

| Terminology                                                   |    |

| Theory of Operation                                           | 17 |

| REVISION HISTORY                                              |    |

| 7/2018—Rev. B to Rev. C                                       |    |

| Changes to Features Section                                   | 1  |

| Changes to Table 4                                            |    |

| Changes to Ordering Guide                                     |    |

| Added Automotive Products Section                             | 27 |

| 10/2010—Rev. A to Rev. B                                      |    |

| Changes to Max Offset Error Parameter in Table 2              | 3  |

| Changes to Max Offset Error Parameter (Y Version) in Table 3. |    |

| Changes to Max Offset Error Parameter (Y Version) in Table 4. | 7  |

| Changes to Ordering Guide                                     | 27 |

| 10/2009—Rev. 0 to Rev. A                                      |    |

| Changes to Table 3                                            | 5  |

| Changes to Table 4                                            |    |

| Undated Ordering Guide                                        |    |

| Converter Operation                        | 1  |

|--------------------------------------------|----|

| Typical Connection Diagram                 | 18 |

| Analog Input                               | 18 |

| Internal Register Structure                | 20 |

| Configuration Register                     | 20 |

| Sample Delay and Bit Trial Delay           | 2  |

| Conversion Result Register                 | 2  |

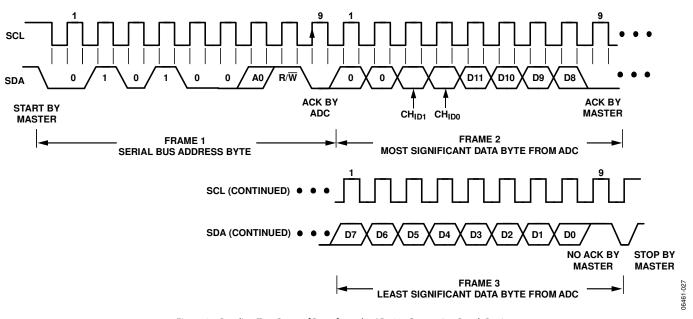

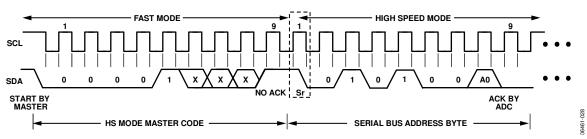

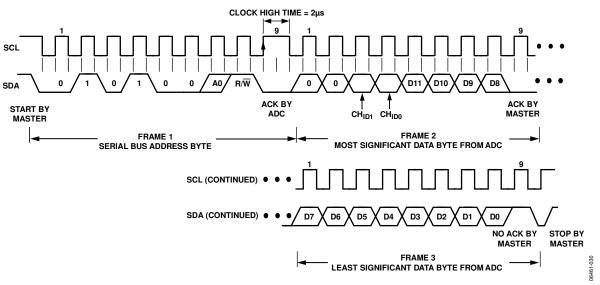

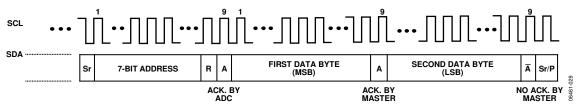

| Serial Interface                           | 22 |

| Serial Bus Address                         | 22 |

| Writing to the AD7991/AD7995/AD7999        | 23 |

| Reading from the AD7991/AD7995/AD7999      | 2  |

| Placing the AD7991/AD7995/AD7999 into High |    |

| Speed Mode                                 | 2  |

| Mode of Operation                          | 20 |

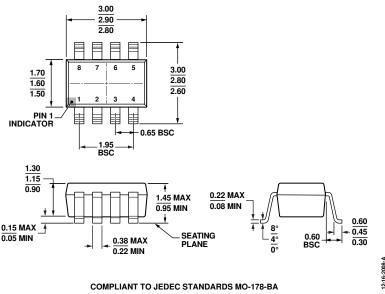

| Outline Dimensions                         | 27 |

| Ordering Guide                             | 2" |

## **SPECIFICATIONS**

### AD79911

The temperature range of the Y version is -40 °C to +125 °C. Unless otherwise noted,  $V_{DD} = 2.7$  V to 5.5 V,  $V_{REF} = 2.5$  V,  $f_{SCL} = 3.4$  MHz, and  $T_A = T_{MIN}$  to  $T_{MAX}$ .

Table 2.

|                                                     | 1    | Y Versi | on           |        |                                                                                                                                           |

|-----------------------------------------------------|------|---------|--------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------|

| Parameter                                           | Min  | Тур     | Max          | Unit   | Test Conditions/Comments                                                                                                                  |

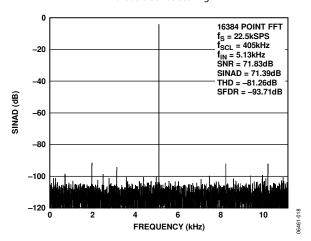

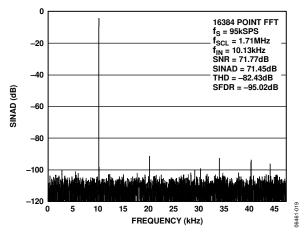

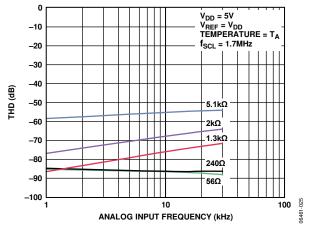

| DYNAMIC PERFORMANCE <sup>2, 3</sup>                 |      |         |              |        | See the Sample Delay and Bit Trial Delay section, $f_{\text{IN}} = 10 \text{ kHz}$ sine wave for $f_{\text{SCL}}$ from 1.7 MHz to 3.4 MHz |

|                                                     |      |         |              |        | $f_{IN} = 1$ kHz sine wave for $f_{SCL}$ up to 400 kHz                                                                                    |

| Signal-to-Noise and Distortion (SINAD) <sup>4</sup> | 69.5 | 70      |              | dB     |                                                                                                                                           |

| Signal-to-Noise Ratio (SNR) <sup>4</sup>            | 70   | 71      |              | dB     |                                                                                                                                           |

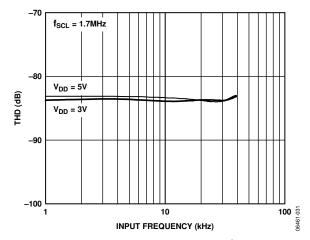

| Total Harmonic Distortion (THD) <sup>4</sup>        |      |         | -75.5        | dB     |                                                                                                                                           |

| Peak Harmonic or Spurious Noise (SFDR) <sup>4</sup> |      |         | <b>−77.5</b> | dB     |                                                                                                                                           |

| Intermodulation Distortion (IMD) <sup>4</sup>       |      |         |              |        | fa = 11 kHz, fb = 9 kHz for f <sub>SCL</sub> from<br>1.7 MHz to 3.4 MHz                                                                   |

|                                                     |      |         |              |        | $fa = 5.4 \text{ kHz}$ , $fb = 4.6 \text{ kHz}$ for $f_{SCL}$ up to $400 \text{ kHz}$                                                     |

| Second-Order Terms                                  | 1    | -92     |              | dB     |                                                                                                                                           |

| Third-Order Terms                                   |      | -88     |              | dB     |                                                                                                                                           |

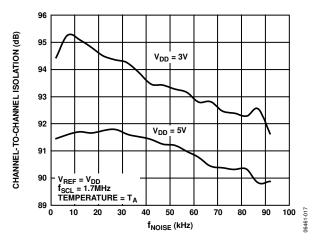

| Channel-to-Channel Isolation <sup>4</sup>           |      | -90     |              | dB     | $f_{IN} = 10 \text{ kHz}$                                                                                                                 |

| Full-Power Bandwidth <sup>4</sup>                   |      | 14      |              | MHz    | @ 3 dB                                                                                                                                    |

|                                                     |      | 1.5     |              | MHz    | @ 0.1 dB                                                                                                                                  |

| DC ACCURACY <sup>2, 5</sup>                         |      |         |              |        |                                                                                                                                           |

| Resolution                                          | 12   |         |              | Bits   |                                                                                                                                           |

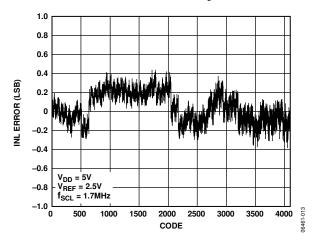

| Integral Nonlinearity <sup>4</sup>                  |      |         | ±1           | LSB    |                                                                                                                                           |

|                                                     |      | ±0.5    |              | LSB    |                                                                                                                                           |

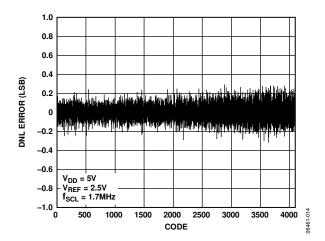

| Differential Nonlinearity <sup>4</sup>              |      |         | ±0.9         | LSB    | Guaranteed no missed codes to 12 bits                                                                                                     |

|                                                     |      | ±0.5    |              | LSB    |                                                                                                                                           |

| Offset Error <sup>4</sup>                           |      | ±1      | ±7           | LSB    |                                                                                                                                           |

| Offset Error Matching                               |      |         | ±0.5         | LSB    |                                                                                                                                           |

| Offset Temperature Drift                            |      | 4.43    |              | ppm/°C |                                                                                                                                           |

| Gain Error <sup>4</sup>                             |      |         | ±2           | LSB    |                                                                                                                                           |

| Gain Error Matching                                 |      |         | ±0.7         | LSB    |                                                                                                                                           |

| Gain Temperature Drift                              |      | 0.69    |              | ppm/°C |                                                                                                                                           |

| ANALOG INPUT                                        |      |         |              |        |                                                                                                                                           |

| Input Voltage Range                                 | 0    |         | $V_{REF}$    | V      | $V_{REF} = V_{IN3}/V_{REF}$ or $V_{DD}$                                                                                                   |

| DC Leakage Current                                  |      |         | ±1           | μΑ     |                                                                                                                                           |

| Input Capacitance                                   |      | 34      |              | pF     | Channel 0 to Channel 2—during acquisition phase                                                                                           |

|                                                     |      | 4       |              | pF     | Channel 0 to Channel 2—outside acquisition phase                                                                                          |

|                                                     | 1    | 35      |              | pF     | Channel 3—during acquisition phase                                                                                                        |

|                                                     |      | 5       |              | pF     | Channel 3—outside acquisition phase                                                                                                       |

| REFERENCE INPUT                                     | 1    |         |              |        |                                                                                                                                           |

| V <sub>REF</sub> Input Voltage Range                | 1.2  |         | $V_{DD}$     | V      |                                                                                                                                           |

| DC Leakage Current                                  | 1    |         | ±1           | μΑ     |                                                                                                                                           |

| V <sub>REF</sub> Input Capacitance                  |      | 5       |              | pF     | Outside conversion phase                                                                                                                  |

|                                                     | 1    | 35      |              | pF     | During conversion phase                                                                                                                   |

| Input Impedance                                     |      | 69      |              | kΩ     |                                                                                                                                           |

|                                                        |                        | Y Versi    | on                                  |      |                                                                               |

|--------------------------------------------------------|------------------------|------------|-------------------------------------|------|-------------------------------------------------------------------------------|

| Parameter                                              | Min                    | Тур        | Max                                 | Unit | Test Conditions/Comments                                                      |

| LOGIC INPUTS (SDA, SCL)                                |                        |            |                                     |      |                                                                               |

| Input High Voltage, V <sub>INH</sub>                   | 0.7 (V <sub>DD</sub> ) |            |                                     | V    | $V_{DD} = 2.7 \text{ V to } 5.5 \text{ V}$                                    |

|                                                        | 0.9 (V <sub>DD</sub> ) |            |                                     | V    | $V_{DD} = 2.35 \text{ V to } 2.7 \text{ V}$                                   |

| Input Low Voltage, V <sub>INL</sub>                    |                        |            | 0.3 (V <sub>DD</sub> )              | V    | $V_{DD} = 2.7 \text{ V to } 5.5 \text{ V}$                                    |

|                                                        |                        |            | 0.1 (V <sub>DD</sub> )              | V    | $V_{DD} = 2.35 \text{ V to } 2.7 \text{ V}$                                   |

| Input Leakage Current, I <sub>IN</sub>                 |                        |            | ±1                                  | μΑ   | $V_{IN} = 0 V \text{ or } V_{DD}$                                             |

| Input Capacitance, C <sub>IN</sub> 6                   |                        |            | 10                                  | рF   |                                                                               |

| Input Hysteresis, V <sub>HYST</sub>                    | 0.1 (V <sub>DD</sub> ) |            |                                     | V    |                                                                               |

| LOGIC OUTPUTS (OPEN DRAIN)                             |                        |            |                                     |      |                                                                               |

| Output Low Voltage, Vol                                |                        |            | 0.4                                 | V    | I <sub>SINK</sub> = 3 mA                                                      |

|                                                        |                        |            | 0.6                                 | V    | I <sub>SINK</sub> = 6 mA                                                      |

| Floating-State Leakage Current                         |                        |            | ±1                                  | μΑ   |                                                                               |

| Floating-State Output Capacitance <sup>6</sup>         |                        |            | 10                                  | рF   |                                                                               |

| Output Coding                                          | Stra                   | ight (natu | ral) binary                         |      |                                                                               |

| THROUGHPUT RATE                                        |                        |            | 18 × (1/f <sub>SCL</sub> )          |      | f <sub>SCL</sub> ≤ 1.7 MHz; see the Serial Interface section                  |

|                                                        |                        |            | $17.5 \times (1/f_{SCL}) + 2 \mu s$ |      | f <sub>SCL</sub> > 1.7 MHz; see the Serial Interface section                  |

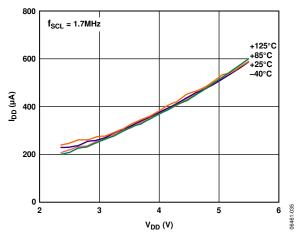

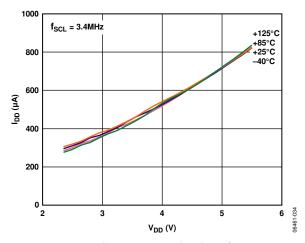

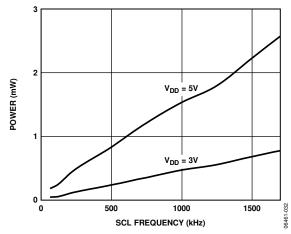

| POWER REQUIREMENTS <sup>2</sup>                        |                        |            |                                     |      | $V_{REF} = V_{DD}$ ; for $f_{SCL} = 3.4$ MHz, clock stretching is implemented |

| $V_{DD}$                                               | 2.7                    |            | 5.5                                 | V    |                                                                               |

| $I_{DD}$                                               |                        |            |                                     |      | Digital inputs = 0 V or V <sub>DD</sub>                                       |

| ADC Operating, Interface Active<br>(Fully Operational) |                        |            | 0.09/0.25                           | mA   | $V_{DD} = 3.3 \text{ V}/5.5 \text{ V}, 400 \text{ kHz f}_{SCL}$               |

|                                                        |                        |            | 0.25/0.8                            | mA   | $V_{DD} = 3.3 \text{ V}/5.5 \text{ V}, 3.4 \text{ MHz f}_{SCL}$               |

| Power-Down, Interface Active <sup>7</sup>              |                        |            | 0.07/0.16                           | mA   | $V_{DD} = 3.3 \text{ V}/5.5 \text{ V}, 400 \text{ kHz } f_{SCL}$              |

|                                                        |                        |            | 0.26/0.85                           | mA   | $V_{DD} = 3.3 \text{ V}/5.5 \text{ V}, 3.4 \text{ MHz f}_{SCL}$               |

| Power-Down, Interface Inactive <sup>7</sup>            |                        |            | 1/1.6                               | μΑ   | $V_{DD} = 3.3 \text{ V}/5.5 \text{ V}$                                        |

| Power Dissipation                                      |                        |            |                                     |      |                                                                               |

| ADC Operating, Interface Active<br>(Fully Operational) |                        |            | 0.3/1.38                            | mW   | $V_{DD} = 3.3 \text{ V}/5.5 \text{ V}, 400 \text{ kHz f}_{SCL}$               |

|                                                        |                        |            | 0.83/4.4                            | mW   | $V_{DD} = 3.3 \text{ V}/5.5 \text{ V}, 3.4 \text{ MHz f}_{SCL}$               |

| Power-Down, Interface Active <sup>7</sup>              |                        |            | 0.24/0.88                           | mW   | $V_{DD} = 3.3 \text{ V}/5.5 \text{ V}, 400 \text{ kHz f}_{SCL}$               |

|                                                        |                        |            | 0.86/4.68                           | mW   | $V_{DD} = 3.3 \text{ V}/5.5 \text{ V}, 3.4 \text{ MHz f}_{SCL}$               |

| Power-Down, Interface Inactive <sup>7</sup>            |                        |            | 3.3/8.8                             | μW   | $V_{DD} = 3.3 \text{ V}/5.5 \text{ V}$                                        |

<sup>&</sup>lt;sup>1</sup> Functional from  $V_{DD} = 2.35 \text{ V}$ .

<sup>&</sup>lt;sup>1</sup> Functional from  $V_{DD} = 2.35$  V.

<sup>2</sup> Sample delay and bit trial delay enabled,  $t_1 = t_2 = 0.5/f_{SGL}$ .

<sup>3</sup> For  $f_{SCL}$  up to 400 kHz, clock stretching is not implemented. Above  $f_{SGL} = 400$  kHz, clock stretching is implemented.

<sup>4</sup> See the Terminology section.

<sup>5</sup> For  $f_{SCL} \le 1.7$  MHz, clock stretching is not implemented; for  $f_{SCL} > 1.7$  MHz, clock stretching is implemented.

<sup>6</sup> Guaranteed by initial characterization.

<sup>7</sup> See the Reading from the AD7991/AD7995/AD7999 section.

## **Data Sheet**

### AD79951

The temperature range for the Y version is  $-40^{\circ}$ C to  $+125^{\circ}$ C. Unless otherwise noted,  $V_{DD} = 2.7$  V to 5.5 V,  $V_{REF} = 2.5$  V,  $f_{SCL} = 3.4$  MHz, and  $T_A = T_{MIN}$  to  $T_{MAX}$ .

Table 3.

|                                                        |     | A Ver | sion <sup>2</sup> |     | Y Ve | rsion           |        |                                                                                                                                           |

|--------------------------------------------------------|-----|-------|-------------------|-----|------|-----------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------|

| Parameter                                              | Min | Тур   | Max               | Min | Тур  | Max             | Unit   | Test Conditions/Comments                                                                                                                  |

| DYNAMIC PERFORMANCE <sup>3,4</sup>                     |     |       |                   |     |      |                 |        | See the Sample Delay and Bit Trial Delay section, $f_{\text{IN}} = 10 \text{ kHz}$ sine wave for $f_{\text{SCL}}$ from 1.7 MHz to 3.4 MHz |

| Signal-to-Noise and                                    |     | 61.5  |                   | 61  |      |                 | dB     | $f_{IN} = 1$ kHz sine wave for $f_{SCL}$ up to 400 kHz                                                                                    |

| Distortion (SINAD) <sup>5</sup>                        |     |       |                   |     |      |                 |        |                                                                                                                                           |

| Total Harmonic Distortion<br>(THD)⁵                    |     | -85   |                   |     |      | <del>-</del> 75 | dB     |                                                                                                                                           |

| Peak Harmonic or Spurious<br>Noise (SFDR) <sup>5</sup> |     | -85   |                   |     |      | -76             | dB     |                                                                                                                                           |

| Intermodulation<br>Distortion (IMD) <sup>5</sup>       |     |       |                   |     |      |                 |        | $fa = 11 \text{ kHz}$ , $fb = 9 \text{ kHz}$ for $f_{SCL}$ from 1.7 MHz to 3.4 MHz                                                        |

|                                                        |     |       |                   |     |      |                 |        | $fa = 5.4 \text{ kHz}$ , $fb = 4.6 \text{ kHz}$ for $f_{SCL}$ up to 400 kHz                                                               |

| Second-Order Terms                                     |     | -90   |                   |     | -90  |                 | dB     |                                                                                                                                           |

| Third-Order Terms                                      |     | -86   |                   |     | -86  |                 | dB     |                                                                                                                                           |

| Channel-to-Channel<br>Isolation⁵                       |     | -90   |                   |     | -90  |                 | dB     | $f_{IN} = 10 \text{ kHz}$                                                                                                                 |

| Full-Power Bandwidth <sup>5</sup>                      |     | 14    |                   |     | 14   |                 | MHz    | @ 3 dB                                                                                                                                    |

|                                                        |     | 1.5   |                   |     | 1.5  |                 | MHz    | @ 0.1 dB                                                                                                                                  |

| DC ACCURACY <sup>3, 6</sup>                            |     |       |                   |     |      |                 |        |                                                                                                                                           |

| Resolution                                             | 10  |       |                   | 10  |      |                 | Bits   |                                                                                                                                           |

| Integral Nonlinearity⁵                                 |     |       | ±0.4              |     |      | ±0.4            | LSB    |                                                                                                                                           |

| Differential Nonlinearity <sup>5</sup>                 |     |       | ±0.4              |     |      | ±0.4            | LSB    | Guaranteed no missed codes to 10 bits                                                                                                     |

| Offset Error⁵                                          |     | ±1    |                   |     |      | ±2.25           | LSB    |                                                                                                                                           |

| Offset Error Matching                                  |     | ±0.04 |                   |     |      | ±0.2            | LSB    |                                                                                                                                           |

| Offset Temperature Drift                               |     | 4.13  |                   |     | 4.13 |                 | ppm/°C |                                                                                                                                           |

| Gain Error <sup>5</sup>                                |     | ±0.15 |                   |     |      | ±0.5            | LSB    |                                                                                                                                           |

| Gain Error Matching                                    |     | ±0.06 |                   |     |      | ±0.25           | LSB    |                                                                                                                                           |

| Gain Temperature Drift                                 |     | 0.50  |                   |     | 0.50 |                 | ppm/°C |                                                                                                                                           |

| ANALOG INPUT                                           |     |       |                   |     |      |                 |        |                                                                                                                                           |

| Input Voltage Range                                    | 0   |       | $V_{REF}$         | 0   |      | $V_{REF}$       | V      | $V_{REF} = V_{IN3}/V_{REF}$ or $V_{DD}$                                                                                                   |

| DC Leakage Current                                     |     |       | ±1                |     |      | ±1              | μΑ     |                                                                                                                                           |

| Input Capacitance                                      |     | 34    |                   |     | 34   |                 | pF     | Channel 0 to Channel 2—during acquisition phase                                                                                           |

|                                                        |     | 4     |                   |     | 4    |                 | pF     | Channel 0 to Channel 2—outside acquisition phase                                                                                          |

|                                                        |     | 35    |                   |     | 35   |                 | pF     | Channel 3—during acquisition phase                                                                                                        |

|                                                        |     | 5     |                   |     | 5    |                 | pF     | Channel 3—outside acquisition phase                                                                                                       |

| REFERENCE INPUT                                        |     |       |                   |     |      |                 |        |                                                                                                                                           |

| V <sub>REF</sub> Input Voltage Range                   | 1.2 |       | $V_{\text{DD}}$   | 1.2 |      | $V_{\text{DD}}$ | V      |                                                                                                                                           |

| DC Leakage Current                                     |     |       | ±1                |     |      | ±1              | μΑ     |                                                                                                                                           |

| V <sub>REF</sub> Input Capacitance                     |     | 5     |                   |     | 5    |                 | pF     | Outside conversion phase                                                                                                                  |

|                                                        |     | 35    |                   |     | 35   |                 | pF     | During conversion phase                                                                                                                   |

| Input Impedance                                        |     | 69    |                   |     | 69   |                 | kΩ     |                                                                                                                                           |

|                                                   | A Version <sup>2</sup> |                |                             |                        | ΥVe    | rsion                       |      |                                                                               |

|---------------------------------------------------|------------------------|----------------|-----------------------------|------------------------|--------|-----------------------------|------|-------------------------------------------------------------------------------|

| Parameter                                         | Min                    | Тур            | Max                         | Min                    | Тур    | Max                         | Unit | Test Conditions/Comments                                                      |

| LOGIC INPUTS (SDA, SCL)                           |                        |                |                             |                        |        |                             |      |                                                                               |

| Input High Voltage, VINH                          | 0.7 (V <sub>DE</sub>   | o)             |                             | 0.7 (V <sub>DD</sub> ) |        |                             | V    | $V_{DD} = 2.7 \text{ V to } 5.5 \text{ V}$                                    |

|                                                   |                        |                |                             | 0.9 (V <sub>DD</sub> ) |        |                             | V    | $V_{DD} = 2.35 \text{ V to } 2.7 \text{ V}$                                   |

| Input Low Voltage, VINL                           |                        |                | 0.3 (V <sub>DD</sub> )      |                        |        | 0.3 (V <sub>DD</sub> )      | V    | $V_{DD} = 2.7 \text{ V to } 5.5 \text{ V}$                                    |

|                                                   |                        |                |                             |                        |        | 0.1 (V <sub>DD</sub> )      | V    | $V_{DD} = 2.35 \text{ V to } 2.7 \text{ V}$                                   |

| Input Leakage Current, I <sub>™</sub>             |                        |                | ±1                          |                        |        | ±1                          | μΑ   | $V_{IN} = 0 \text{ V or } V_{DD}$                                             |

| Input Capacitance, C <sub>IN</sub> <sup>7</sup>   |                        |                | 10                          |                        |        | 10                          | pF   |                                                                               |

| Input Hysteresis, V <sub>HYST</sub>               | 0.1 (V <sub>DD</sub>   | <sub>o</sub> ) |                             | 0.1 (V <sub>DD</sub> ) |        |                             | V    |                                                                               |

| LOGIC OUTPUTS (OPEN DRAIN)                        |                        |                |                             |                        |        |                             |      |                                                                               |

| Output Low Voltage, Vol                           |                        |                | 0.4                         |                        |        | 0.4                         | V    | I <sub>SINK</sub> = 3 mA                                                      |

|                                                   |                        |                | 0.6                         |                        |        | 0.6                         | V    | $I_{SINK} = 6 \text{ mA}$                                                     |

| Floating-State Leakage<br>Current                 |                        |                | ±1                          |                        |        | ±1                          | μΑ   |                                                                               |

| Floating-State Output<br>Capacitance <sup>7</sup> |                        |                | 10                          |                        |        | 10                          | pF   |                                                                               |

| Output Coding                                     | Straigh                | t (natura      | al) binary                  | Straight               | (natur | al) binary                  |      |                                                                               |

| THROUGHPUT RATE                                   |                        |                | $18 \times (1/f_{SCL})$     |                        |        | 18 × (1/f <sub>SCL</sub> )  |      | $f_{SCL} \le 1.7$ MHz; see the Serial Interface section                       |

|                                                   |                        |                | $17.5 \times (1/f_{SCL}) +$ |                        |        | $17.5 \times (1/f_{SCL}) +$ |      | f <sub>SCL</sub> > 1.7 MHz; see the Serial Interface section                  |

|                                                   |                        |                | 2 μs                        |                        |        | 2 μs                        |      |                                                                               |

| POWER REQUIREMENTS <sup>3</sup>                   |                        |                |                             |                        |        |                             |      | $V_{REF} = V_{DD}$ ; for $f_{SCL} = 3.4$ MHz, clock stretching is implemented |

| $V_{DD}$                                          | 2.7                    |                | 5.5                         | 2.7                    |        | 5.5                         | V    |                                                                               |

| $I_{DD}$                                          |                        |                |                             |                        |        |                             |      | Digital inputs = $0 \text{ V or V}_{DD}$                                      |

| ADC Operating,<br>Interface Active                |                        |                |                             |                        |        | 0.09/0.25                   | mA   | $V_{DD} = 3.3 \text{ V}/5.5 \text{ V}, 400 \text{ kHz } f_{SCL}$              |

| (Fully Operational)                               |                        |                | 0.25                        |                        |        | 0.25/0.8                    | mA   | $V_{DD} = 3.3 \text{ V}/5.5 \text{ V}, 3.4 \text{ MHz f}_{SCL}$               |

| Power-Down, Interface                             |                        |                |                             |                        |        | 0.07/0.16                   | mA   | $V_{DD} = 3.3 \text{ V}/5.5 \text{ V}, 400 \text{ kHz f}_{SCL}$               |

| Active <sup>8</sup>                               |                        |                | 0.26                        |                        |        | 0.26/0.85                   | mA   | $V_{DD} = 3.3 \text{ V}/5.5 \text{ V}, 3.4 \text{ MHz } f_{SCL}$              |

| Power-Down, Interface<br>Inactive <sup>8</sup>    |                        |                | 1                           |                        |        | 1/1.6                       | μΑ   | $V_{DD} = 3.3 \text{ V}/5.5 \text{ V}$                                        |

| Power Dissipation                                 |                        |                |                             |                        |        |                             |      |                                                                               |

| ADC Operating,                                    |                        |                |                             |                        |        | 0.3/1.38                    | mW   | $V_{DD} = 3.3 \text{ V}/5.5 \text{ V}, 400 \text{ kHz } f_{SCL}$              |

| Interface Active<br>(Fully Operational)           |                        |                | 0.83                        |                        |        | 0.83/4.4                    | mW   | $V_{DD} = 3.3 \text{ V}/5.5 \text{ V}, 3.4 \text{ MHz } f_{SCL}$              |

| Power-Down, Interface                             |                        |                |                             |                        |        | 0.24/0.88                   | mW   | $V_{DD} = 3.3 \text{ V}/5.5 \text{ V}, 400 \text{ kHz } f_{SCL}$              |

| Active <sup>8</sup>                               |                        |                | 0.86                        |                        |        | 0.86/4.68                   | mW   | $V_{DD} = 3.3 \text{ V}/5.5 \text{ V}, 3.4 \text{ MHz f}_{SCL}$               |

| Power-Down, Interface<br>Inactive <sup>8</sup>    |                        |                | 3.3                         |                        |        | 3.3/8.8                     | μW   | $V_{DD} = 3.3 \text{ V}/5.5 \text{ V}$                                        |

$<sup>^1</sup>$  Functional from  $V_{DD}=2.35$  V.  $^2$  A Version tested at  $V_{DD}=3.3$  V and  $f_{SCL}=3.4$  MHz. Functionality tested at  $f_{SCL}=400$  kHz.  $^3$  Sample delay and bit trial delay enabled,  $t_1=t_2=0.5/f_{SCL}$ .

$<sup>^4</sup>$  For  $f_{SCL}$  up to 400 kHz, clock stretching is not implemented. Above  $f_{SCL} = 400$  kHz, clock stretching is implemented.

For f<sub>SCL</sub> up to 400 kHz, clock stretching is not implemented. Above f<sub>SCL</sub> = 400 kHz, clock stretching is implemented.

See the Terminology section.

For f<sub>SCL</sub> ≤ 1.7 MHz, clock stretching is not implemented; for f<sub>SCL</sub> > 1.7 MHz, clock stretching is implemented.

Guaranteed by initial characterization.

See the Reading from the AD7991/AD7995/AD7999 section.

## **Data Sheet**

### AD79991

The temperature range for the Y version is  $-40^{\circ}$ C to  $+125^{\circ}$ C. Unless otherwise noted,  $V_{DD} = 2.7 \text{ V}$  to 5.5 V,  $V_{REF} = 2.5 \text{ V}$ ,  $f_{SCL} = 3.4 \text{ MHz}$ , and  $T_A = T_{MIN}$  to  $T_{MAX}$ .

Table 4.

|                                                        | Y Version |          |                  | W Ver | sion     |                  |          |                                                                                                                                                                                                        |

|--------------------------------------------------------|-----------|----------|------------------|-------|----------|------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Parameter                                              | Min       | Тур      | Max              | Min   | Тур      | Max              | Unit     | Test Conditions/Comments                                                                                                                                                                               |

| DYNAMIC PERFORMANCE <sup>2,3</sup>                     |           |          |                  |       |          |                  |          | See the Sample Delay and Bit Trial Delay section, $f_{IN} = 10 \text{ kHz}$ sine wave for $f_{SCL}$ from 1.7 MH                                                                                        |

|                                                        |           |          |                  |       |          |                  |          | to 3.4 MHz                                                                                                                                                                                             |

|                                                        |           |          |                  |       |          |                  |          | $f_{IN} = 1$ kHz sine wave for $f_{SCL}$ up to 400 kH                                                                                                                                                  |

| Signal-to-Noise and Distortion (SINAD) <sup>4</sup>    | 49.5      |          |                  | 49.5  |          |                  | dB       |                                                                                                                                                                                                        |

| Total Harmonic Distortion (THD) <sup>5</sup>           |           |          | -65              |       |          | -65              | dB       |                                                                                                                                                                                                        |

| Peak Harmonic or Spurious Noise<br>(SFDR) <sup>5</sup> |           |          | <b>–65</b>       |       |          | <b>–65</b>       | dB       |                                                                                                                                                                                                        |

| Intermodulation Distortion (IMD) <sup>5</sup>          |           |          |                  |       |          |                  |          | $fa = 11 \text{ kHz, fb} = 9 \text{ kHz for } f_{SCL} \text{ from} \\ 1.7 \text{ MHz to } 3.4 \text{ MHz} \\ fa = 5.4 \text{ kHz, fb} = 4.6 \text{ kHz for } f_{SCL} \text{ up to} \\ 400 \text{ kHz}$ |

| Second-Order Terms                                     |           | -83      |                  |       | -83      |                  | dB       |                                                                                                                                                                                                        |

| Third-Order Terms                                      |           | -75      |                  |       | -75      |                  | dB       |                                                                                                                                                                                                        |

| Channel-to-Channel Isolation <sup>5</sup>              |           | -90      |                  |       | -90      |                  | dB       | $f_{IN} = 10 \text{ kHz}$                                                                                                                                                                              |

| Full-Power Bandwidth <sup>5</sup>                      |           | 14       |                  |       | 14       |                  | MHz      | @ 3 dB                                                                                                                                                                                                 |

|                                                        |           | 1.5      |                  |       | 1.5      |                  | MHz      | @ 0.1 dB                                                                                                                                                                                               |

| DC ACCURACY <sup>3,5</sup>                             |           |          |                  |       |          |                  |          |                                                                                                                                                                                                        |

| Resolution                                             | 8         |          |                  | 8     |          |                  | Bits     |                                                                                                                                                                                                        |

| Integral Nonlinearity <sup>5</sup>                     |           |          | ±0.1             |       |          | ±0.15            | LSB      |                                                                                                                                                                                                        |

| Differential Nonlinearity <sup>5</sup>                 |           |          | ±0.1             |       |          | ±0.13            | LSB      | Guaranteed no missed codes to eight bits                                                                                                                                                               |

| Offset Error <sup>5</sup>                              |           |          | ±0.5             |       |          | ±0.65            | LSB      |                                                                                                                                                                                                        |

| Offset Error Matching                                  |           |          | ±0.05            |       |          | ±0.07            | LSB      |                                                                                                                                                                                                        |

| Offset Temperature Drift                               |           | 4.26     |                  |       | 4.26     |                  | ppm/°C   |                                                                                                                                                                                                        |

| Gain Error <sup>5</sup>                                |           |          | ±0.175           |       |          | ±0.175           | LSB      |                                                                                                                                                                                                        |

| Gain Error Matching                                    |           |          | ±0.06            |       |          | ±0.07            | LSB      |                                                                                                                                                                                                        |

| Gain Temperature Drift                                 |           | 0.59     |                  |       | 0.59     |                  | ppm/°C   |                                                                                                                                                                                                        |

| ANALOG INPUT                                           |           |          |                  |       |          |                  |          |                                                                                                                                                                                                        |

| Input Voltage Range                                    | 0         |          | V <sub>REF</sub> | 0     |          | V <sub>REF</sub> | V        | $V_{REF} = V_{IN3}/V_{REF}$ or $V_{DD}$                                                                                                                                                                |

| DC Leakage Current                                     |           | 2.4      | ±1               |       | 2.4      | ±1               | μΑ       | Channel Ota Channel 2 during                                                                                                                                                                           |

| Input Capacitance                                      |           | 34       |                  |       | 34       |                  | pF       | Channel 0 to Channel 2 during acquisition phase                                                                                                                                                        |

|                                                        |           | 4        |                  |       | 4        |                  | pF       | Channel 0 to Channel 2 outside acquisition phase                                                                                                                                                       |

|                                                        |           | 35       |                  |       | 35       |                  | pF       | Channel 3 during acquisition phase                                                                                                                                                                     |

| DEFENSAL INDUST                                        |           | 5        |                  |       | 5        |                  | pF       | Channel 3 outside acquisition phase                                                                                                                                                                    |

| REFERENCE INPUT                                        | 1.2       |          | V                | 1.2   |          | W                | .,       |                                                                                                                                                                                                        |

| V <sub>REF</sub> Input Voltage Range                   | 1.2       |          | V <sub>DD</sub>  | 1.2   |          | V <sub>DD</sub>  | V        |                                                                                                                                                                                                        |

| DC Leakage Current VREF Input Capacitance              |           | 5        | ±1               |       | 5        | ±1               | μA       | Outside conversion phase                                                                                                                                                                               |

| v <sub>REF</sub> iriput Capacitance                    |           | 5<br>35  |                  |       | 5<br>35  |                  | pF<br>pF | During conversion phase                                                                                                                                                                                |

| Input Impedance                                        |           | 55<br>69 |                  |       | 55<br>69 |                  | kΩ       | Daining conversion phase                                                                                                                                                                               |

| input impedance                                        | 1         | Už       |                  |       | υž       |                  | 1/7 7    |                                                                                                                                                                                                        |

|                                                         | Y Version                |              |                            |                          | W Ver       | sion                  |                          |                                                                  |

|---------------------------------------------------------|--------------------------|--------------|----------------------------|--------------------------|-------------|-----------------------|--------------------------|------------------------------------------------------------------|

| Parameter                                               | Min Typ Max              |              | Min Typ Max                |                          |             | Unit                  | Test Conditions/Comments |                                                                  |

| LOGIC INPUTS (SDA, SCL)                                 |                          |              |                            |                          |             |                       |                          |                                                                  |

| Input High Voltage, V <sub>INH</sub>                    | 0.7×                     |              |                            | 0.7 ×                    |             |                       | V                        | $V_{DD} = 2.7 \text{ V to } 5.5 \text{ V}$                       |

|                                                         | $V_{DD}$                 |              |                            | $V_{DD}$                 |             |                       |                          |                                                                  |

|                                                         | 0.9 ×                    |              |                            | 0.9 ×                    |             |                       | V                        | $V_{DD} = 2.35 \text{ V to } 2.7 \text{ V}$                      |

|                                                         | $V_{DD}$                 |              |                            | $V_{DD}$                 |             |                       | l                        |                                                                  |

| Input Low Voltage, V <sub>INL</sub>                     |                          |              | $0.3 \times V_{DD}$        |                          |             | $0.3 \times V_{DD}$   | V                        | $V_{DD} = 2.7 \text{ V to } 5.5 \text{ V}$                       |

|                                                         |                          |              | $0.1 \times V_{DD}$        |                          |             | $0.1 \times V_{DD}$   | V                        | $V_{DD} = 2.35 \text{ V to } 2.7 \text{ V}$                      |

| Input Leakage Current, I <sub>IN</sub>                  |                          |              | ±1                         |                          |             | ±1                    | μA                       | $V_{IN} = 0 \text{ V or } V_{DD}$                                |

| Input Capacitance, C <sub>IN</sub> <sup>6</sup>         |                          |              | 10                         |                          |             | 10                    | pF                       |                                                                  |

| Input Hysteresis, V <sub>HYST</sub>                     | 0.1 ×<br>V <sub>DD</sub> |              |                            | 0.1 ×<br>V <sub>DD</sub> |             |                       |                          |                                                                  |

| LOGIC OUTPUTS (OPEN DRAIN)                              | <b>V</b> DD              |              |                            | VDD                      |             |                       |                          |                                                                  |

| Output Low Voltage, Vol                                 |                          |              | 0.4                        |                          |             | 0.4                   | V                        | Isink = 3 mA                                                     |

| Output Low Voltage, Vol                                 |                          |              | 0.4                        |                          |             | 0.4                   | V                        | Isink = 3 mA                                                     |

| Floating State Leakage Current                          |                          |              | 0.6<br>±1                  |                          |             | 0.6<br>±1             |                          | ISINK = 6 MA                                                     |

| Floating-State Leakage Current<br>Floating-State Output |                          |              |                            |                          |             | ±1<br>10              | μA                       |                                                                  |

| Capacitance <sup>7</sup>                                |                          |              | 10                         |                          |             | 10                    | pF                       |                                                                  |

| Output Coding                                           | Stra                     | aight (na    | tural) binary              | Strai                    | aht (nati   | ural) binary          |                          |                                                                  |

| THROUGHPUT RATE                                         | 300                      | ilgilit (lla | 18 × (1/f <sub>SCL</sub> ) | Juan                     | giit (iiatt | 18×                   |                          | f <sub>SCL</sub> ≤ 1.7 MHz; see the Serial Interface             |

| THROUGHFUT NATE                                         |                          |              | 10 X (1/15CL)              |                          |             | (1/f <sub>scl</sub> ) |                          | section                                                          |

|                                                         |                          |              | $17.5 \times (1/f_{SCL})$  |                          |             | 17.5×                 |                          | f <sub>SCL</sub> > 1.7 MHz; see the Serial Interface             |

|                                                         |                          |              | + 2 µs                     |                          |             | $(1/f_{SCL})$ +       |                          | section                                                          |

|                                                         |                          |              |                            |                          |             | 2 μs                  |                          |                                                                  |

| POWER REQUIREMENTS <sup>3</sup>                         |                          |              |                            |                          |             |                       |                          | $V_{REF} = V_{DD}$ ; for $f_{SCL} = 3.4$ MHz, clock              |

|                                                         |                          |              |                            |                          |             |                       |                          | stretching is implemented                                        |

| $V_{DD}$                                                | 2.7                      |              | 5.5                        | 2.7                      |             | 5.5                   | V                        |                                                                  |

| I <sub>DD</sub>                                         |                          |              |                            |                          |             |                       |                          | Digital inputs = $0 \text{ V or V}_{DD}$                         |

| ADC Operating, Interface<br>Active (Fully Operational)  |                          |              | 0.09/0.25                  |                          |             | 0.1/0.25              | mA                       | $V_{DD} = 3.3 \text{ V}/5.5 \text{ V}, 400 \text{ kHz } f_{SCL}$ |

|                                                         |                          |              | 0.25/0.8                   |                          |             | 0.28/0.88             | mA                       | $V_{DD} = 3.3 \text{ V}/5.5 \text{ V}, 3.4 \text{ MHz } f_{SCL}$ |

| Power-Down, Interface Active <sup>7</sup>               |                          |              | 0.07/0.16                  |                          |             | 0.07/0.18             | mA                       | $V_{DD} = 3.3 \text{ V}/5.5 \text{ V}, 400 \text{ kHz } f_{SCL}$ |

|                                                         |                          |              | 0.26/0.85                  |                          |             | 0.3/0.96              | mA                       | $V_{DD} = 3.3 \text{ V}/5.5 \text{ V}, 3.4 \text{ MHz } f_{SCL}$ |

| Power-Down, Interface<br>Inactive <sup>8</sup>          |                          |              | 1/1.6                      |                          |             | 1/2                   | μΑ                       | V <sub>DD</sub> = 3.3 V/5.5 V                                    |

| Power Dissipation                                       |                          |              | 0.3/1.38                   |                          |             | 0.33/1.38             | mW                       | $V_{DD} = 3.3 \text{ V}/5.5 \text{ V}, 400 \text{ kHz } f_{SCL}$ |

| ADC Operating Interface Active (Fully Operational)      |                          |              | 0.83/4.4                   |                          |             | 0.924/4.84            | mW                       | $V_{DD} = 3.3 \text{ V}/5.5 \text{ V}, 3.4 \text{ MHz } f_{SCL}$ |

| Power-Down, Interface Active <sup>8</sup>               |                          |              | 0.24/0.88                  |                          |             | 0.24/0.99             | mW                       | $V_{DD} = 3.3 \text{ V}/5.5 \text{ V}, 400 \text{ kHz } f_{SCL}$ |

| ,                                                       |                          |              | 0.86/4.68                  |                          |             | 0.99/5.28             | mW                       | $V_{DD} = 3.3 \text{ V}/5.5 \text{ V}, 3.4 \text{ MHz } f_{SCL}$ |

| Power-Down, Interface                                   |                          |              | 3.3/8.8                    |                          |             | 3.3/11                | μW                       | $V_{DD} = 3.3 \text{ V/5.5 V}$                                   |

| Inactive <sup>8</sup>                                   |                          |              |                            |                          |             |                       |                          |                                                                  |

$<sup>^1</sup>$  Functional from V<sub>DD</sub> = 2.35 V.  $^2$  Sample delay and bit trial delay enabled,  $t_1=t_2=0.5/f_{SCL}$ .  $^3$  For  $f_{SCL}$  up to 400 kHz, clock stretching is not implemented. Above  $f_{SCL}=400$  kHz, clock stretching is implemented.

<sup>4</sup> See the Terminology section.

5 For  $f_{SCL} \le 1.7$  MHz, clock stretching is not implemented; for  $f_{SCL} > 1.7$  MHz, clock stretching is implemented.

6 Guaranteed by initial characterization.

7 See the Reading from the AD7991/AD7995/AD7999 section.

## **Data Sheet**

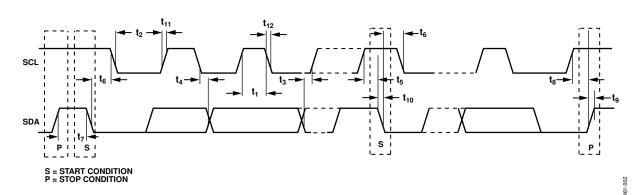

#### I<sup>2</sup>C TIMING SPECIFICATIONS

Guaranteed by initial characterization. All values were measured with the input filtering enabled.  $C_B$  refers to the capacitive load on the bus line, with  $t_r$  and  $t_f$  measured between 0.3  $V_{DD}$  and 0.7  $V_{DD}$  (see Figure 2). Unless otherwise noted,  $V_{DD} = 2.7$  V to 5.5 V and  $T_A = T_{MIN}$  to  $T_{MAX}$ .

Table 5.

|                                |                                 |                         | Limit at t <sub>MIN</sub> , t <sub>MAX</sub> |                 |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

|--------------------------------|---------------------------------|-------------------------|----------------------------------------------|-----------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Parameter                      | Conditions                      | Min                     | Тур                                          | Max             | Unit | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |