Original Page

Page URL: http://www.altera.com/products/devkits/altera/kit-cyc3-dsp.html

# **DSP Development Kit, Cyclone III Edition**

#### from Altera Corporation

The DSP Development Kit, Cyclone<sup>®</sup> III Edition is RoHS compliant and delivers a complete digital signal processing (DSP) development environment for design engineers. The kit facilitates the entire design process from design conception through hardware implementation. The DSP Development Kit, Cyclone III Edition includes the Cyclone III development board, the Data Conversion high-speed mezzanine card (HSMC), the DSP Builder development tool, Quartus<sup>®</sup> II development software, MATLAB/Simulink evaluation software, evaluation intellectual property (IP) cores, design examples, power supplies, cables, and documentation.

- Ordering Information

- Development Kit Contents

## **Ordering Information**

Table 1 provides the ordering code and pricing information for the DSP Development Kit, Cyclone III Edition.

| Table 1. DSP Development Kit, Cyclone III Edition Ordering Code and Pricing Information |         |                                                                                                            |

|-----------------------------------------------------------------------------------------|---------|------------------------------------------------------------------------------------------------------------|

| Ordering Code                                                                           | Price   | Ordering Information                                                                                       |

| DK-DSP-3C120N                                                                           | \$1,895 | In North America, call 1-888-800-0631.<br>For international sales, contact your <u>local distributor</u> . |

### **Development Kit Contents**

The DSP Development Kit, Cyclone III Edition features:

- Cyclone III Development Board

- Featured Device

- Cyclone III EP3C120F780 FPGA

- O Display and general user input/output

- 128 x 64 graphics LCD

- 2-line x 16-character LCD

- Buttons, dip-switches, LEDs, 7-segment display, speaker header

- Memory

- 256 Mbytes of dual-channel DDR2 SDRAM with ECC

- 8 Mbytes of synchronous SRAM

- 64 Mbytes of flash

- Components and interfaces

- 10/100/1000 Ethernet (RGMII)

- USB 2.0 (Type B)

- Two high-speed mezzanine (HSMC) connectors

- Data Conversion HSMC

- O Dual 14-bit, 150-MSPS A/D converter

- O Dual 14-bit, 250-MSPS D/A converter

- Audio in/out/mic

- Cyclone III FPGA Development Kit, CD-ROM

- O Design examples for the Cyclone III FPGA development board

- o Complete documentation

- User guide

- Reference manual

- Board schematic and layout

- Bill of materials

- Product and partner information

- MATLAB/Simulink evaluation software

- Altera<sup>®</sup> Complete Design Suite DVD

- Quartus II design software

- Subscription Edition (optional feature, available for purchase)

- Web Edition (no charge, Windows only)

- O ModelSim®-Altera® software

- Altera Edition (optional feature, available for purchase)

- Web Edition (no charge, Windows only)

- MegaCore<sup>®</sup> IP Library including Nios II processor OpenCore Plus evaluation

- O Nios® II Embedded Design Suite, Evaluation Edition (free)

- o DSP Builder

- Video demos of Quartus II software and the Nios® II processor

- System reference designs and labs

- DSP Builder filtering design

- Nios II processor reference designs

#### **HSMC** Interface

Altera developed the specification for the HSMC, which is based on the <u>Samtec mechanical connector</u>, to define and standardize the interface between optional daughtercards and host boards. This specification outlines both the electrical and mechanical properties of the interface between daughtercard and host. You can also create your own HSMC interface compatible daughtercards.

• Request a copy of the HSMC specification

Figure 1 shows the Cyclone III development board.

Figure 1. Cyclone III FPGA Development Board

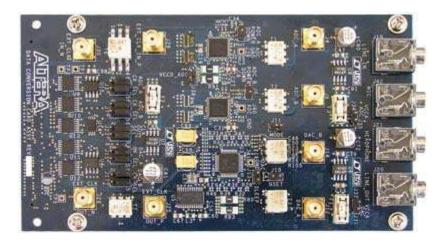

Figure 2 shows the data conversion HSMC.

Figure 2. Cyclone III Data Conversion HSMC

## **Related Links**

- Other Cyclone III-based development kits

- AN 466: Design Guidelines for Cyclone III FPGAs (PDF)

- Quartus II design software

- Literature for low-cost Cyclone III FPGAs

- Nios II 32-bit embedded processor solutions

- <u>Digital signal processing (DSP) in Cyclone III FPGAs</u>

- Power Management Center for Altera devices

Copyright © 1995 - 2008 Altera Corporation, 101 Innovation Drive, San Jose, California 95134, USA.