# ML65244/ML65L244\*

# **High Speed Dual Quad Buffer/Line Drivers**

#### GENERAL DESCRIPTION

The ML65244 and ML65L244 are non-inverting dual quad buffer/line drivers. The high operating frequency (50MHz driving a 50pF load) and low propagation delay (ML65244 – 1.7ns, ML65L244 – 2ns) make them ideal for very high speed applications such as processor bus buffering and cache and main memory control.

These buffers use a unique analog implementation to eliminate the delays inherent in traditional digital designs. Schottky clamps reduce under and overshoot, and special output driver circuits limit ground bounce. The ML65244 and ML65L244 conform to the pinout and functionality of the industry standard FCT244 and are intended for applications where propagation delay is critical to the system design.

Note: This part was previously numbered ML6582.

#### **FEATURES**

- Low propagation delay 1.7ns ML65244 2.0ns ML65L244

- Fast Dual 4-bit TTL level buffer/line driver with tri-state capability on the output (two 4-bit sections)

- TTL compatible input and output levels

- Schottky diode clamps on all inputs to handle undershoot and overshoot

- Onboard schottky diodes minimize noise

- Reduced output swing of 0-4.1 volts

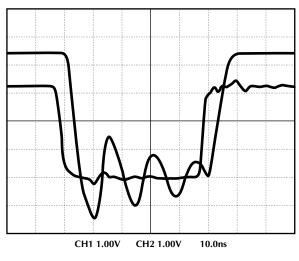

- Ground bounce controlled outputs, typically less than 400mV

- Industry standard FCT244 type pinout

- Applications include high speed cache memory, main memory, processor bus buffering, and graphics cards

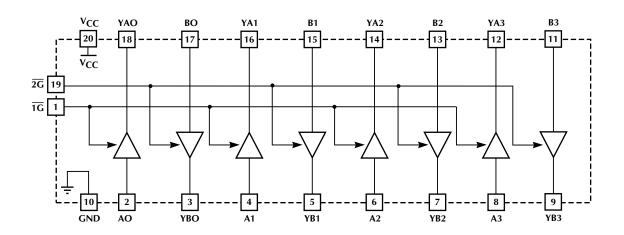

#### **BLOCK DIAGRAM**

\*This Part Is Obsolete

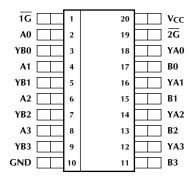

# **PIN CONFIGURATION**

# 20-Pin SOIC, QSOP

**TOP VIEW**

# **PIN DESCRIPTION**

| NAME            | I/O | DESCRIPTION                  |

|-----------------|-----|------------------------------|

| Ai              | I   | Data Bus A                   |

| YAi             | 0   | Data Bus A                   |

| Bi              | I   | Data Bus B                   |

| YBi             | 0   | Data Bus B                   |

| <del>1</del> G  | I   | Output Enable for data bus A |

| $\overline{2G}$ | I   | Output Enable for data bus B |

| GND             | I   | Signal Ground                |

| $V_{CC}$        | I   | + 5V supply                  |

|                 |     |                              |

# **FUNCTION TABLE**

| 1G/2G | Ai/Bi | YAi/YBi |

|-------|-------|---------|

| Н     | X     | Z       |

| L     | L     | L       |

| L     | Н     | Н       |

L = Logic Low

# **ABSOLUTE MAXIMUM RATINGS**

| V <sub>CC</sub>               |                                |

|-------------------------------|--------------------------------|

| DC Input voltage              | –0.3 to V <sub>CC</sub> + 0.3V |

| AC Input voltage (< 20ns)     |                                |

| DC Output voltage             |                                |

| Output sink current (per pin) | 120mA                          |

| Storage temperature           | –65°C to 150°C                 |

| Junction temperature          | 150°C                          |

| Thermal Impedance (θ,μ)       |                                |

| SOIC                          | 96°C/W                         |

| QSOP                          | 100°C/W                        |

H = Logic High

X = Don't Care

Z = High Impedance

# **ELECTRICAL CHARACTERISTICS**

Unless otherwise stated, these specifications apply for:  $V_{CC}$  = 5.0  $\pm$  5%V,  $T_{A}$  = 0°C to 70°C (Note 1).

| SYMBOL                              | PARAMETER                                     | CONDITIONS                                                        |          | MIN | TYP  | MAX  | UNITS |

|-------------------------------------|-----------------------------------------------|-------------------------------------------------------------------|----------|-----|------|------|-------|

| AC ELECTR                           | ICAL CHARACTERISTICS                          | $(C_{LOAD} = 50pF, R_{LOAD} = 500\Omega)$                         |          |     |      |      |       |

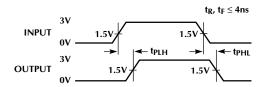

| t <sub>PLH</sub> , t <sub>PHL</sub> | Propagation delay                             | Ai to YAi, Bi to YBi (Note 2)                                     | ML65244  |     | 1.4  | 1.7  | ns    |

|                                     |                                               |                                                                   | ML65L244 |     | 1.6  | 2.0  | ns    |

| t <sub>OE</sub>                     | Output enable time 1G, 2G to YAi/YBi          |                                                                   |          |     | 10   | 15   | ns    |

| t <sub>OD</sub>                     | Output disable time 1G, 2G to YAi/YBi         |                                                                   |          |     |      | 10   | ns    |

| C <sub>IN</sub>                     | Input capacitance                             |                                                                   |          |     | 8    |      | pF    |

| DC ELECTR                           | ICAL CHARACTERISTICS                          | $(C_{LOAD} = 50pF, R_{LOAD} = \infty)$                            |          |     |      |      |       |

| V <sub>IH</sub>                     | Input high voltage                            | Logic HIGH                                                        |          | 2.0 |      |      | V     |

| V <sub>IL</sub>                     | Input low voltage                             | Logic LOW                                                         |          |     |      | 0.8  | V     |

| I <sub>IH</sub>                     | Input high current                            | Per pin, V <sub>IN</sub> = 3V                                     | ML65244  |     | 0.5  | 1.5  | mA    |

|                                     |                                               |                                                                   | ML65L244 |     | 0.3  | 0.5  | mA    |

| I <sub>IL</sub>                     | Input low current                             | Per pin, V <sub>IN</sub> = 0                                      | ML65244  |     | 2.4  | 3.5  | mA    |

|                                     |                                               |                                                                   | ML65L244 |     | 0.8  | 1.0  | mA    |

| I <sub>HI-Z</sub>                   | Three-state output current                    | V <sub>CC</sub> = 5.25V, 0 < V <sub>IN</sub> < V <sub>CC</sub>    |          |     |      | 5    | μΑ    |

| los                                 | Short circuit current                         | V <sub>CC</sub> = 5.25V, V <sub>O</sub> = GND (Note 3)            |          | -60 |      | -225 | mA    |

| V <sub>IC</sub>                     | Input clamp voltage                           | V <sub>CC</sub> = 4.75V, I <sub>IN</sub> = 18mA                   |          |     | -0.7 | -1.2 | V     |

| V <sub>OH</sub>                     | Output high voltage                           | V <sub>CC</sub> = 4.75V, I <sub>OH</sub> = 100μA<br>(Notes 4 & 5) |          | 2.4 |      |      | V     |

| V <sub>OL</sub>                     | Output low voltage                            | V <sub>CC</sub> = 4.75V, I <sub>OL</sub> = 25mA<br>(Notes 4 & 5)  |          |     |      | 0.6  | V     |

| V <sub>OFF</sub>                    | V <sub>IN</sub> – V <sub>OUT</sub> per buffer | V <sub>CC</sub> = 4.75V (Note 4)                                  | ML65244  | 0   | 100  | 200  | mV    |

|                                     |                                               |                                                                   | ML65L244 | 0   | 200  | 300  | mV    |

| I <sub>CC</sub>                     | Quiescent Power<br>Supply Current             | V <sub>CC</sub> = 5.25V, Freq = 0Hz,<br>Inputs/outputs open       | ,        |     | 55   | 80   | mA    |

Note 1: Limits are guaranteed by 100% testing, sampling or correlation with worst case test conditions.

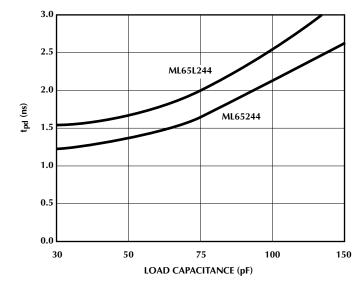

Note 2: One line switching, see Figure 3,  $t_{PLH}$ ,  $t_{PHL}$  versus  $C_L$ .

Note 3: Not more than one output should be shorted for more than a second.

Note 4: This is a true analog buffer. In the linear region, the output tracks the input with an offset  $(V_{OFF})$ . For  $V_{OH}$ ,  $V_{IN} = 2.7V$ .

$V_{OH\ MIN}$  includes  $V_{OFF}$ . For  $V_{OL}$ ,  $V_{IN}$  = 0V,  $V_{OL\ MAX}$  includes  $V_{OFF}$

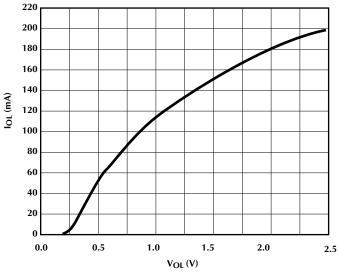

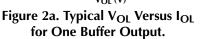

Note 5: See Figure 2 for  $I_{\mbox{\scriptsize OH}}$  versus  $V_{\mbox{\scriptsize OH}}$  and  $I_{\mbox{\scriptsize OL}}$  versus  $V_{\mbox{\scriptsize OL}}$  data.

74FCT244 ML65244

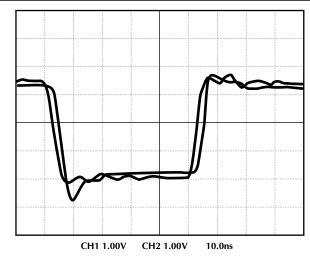

Figure 1. Ground Bounce Comparison, Four Outputs Switching into 50pF Loads.

Figure 2b. Typical V<sub>OH</sub> Versus I<sub>OH</sub> for One Buffer Output.

Figure 3. Propagation Delay (t<sub>PLH</sub>, t<sub>PHL</sub>) Versus Load Capacitance, One Output Switching.

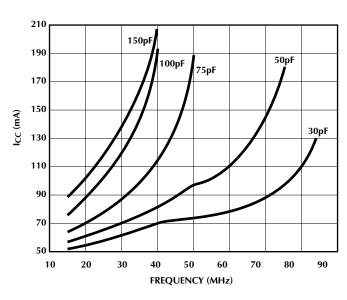

Figure 4. I<sub>CC</sub> Versus Frequency for Various Load Capacitances, Four Outputs Switching.

#### **FUNCTIONAL DESCRIPTION**

The ML65244 and ML65L244 are very high speed noninverting buffer/line drivers with three-state outputs which are ideally suited for bus-oriented applications. They provide a low propagation delay by using an analog design approach (a high speed unity gain buffer), as compared to conventional digital approaches. The ML65244 and ML65L244 follow the pinout and functionality of the industry standard FCT244 series of buffer/line drivers and are intended to replace them in designs where the propagation delay is a critical part of the system design considerations. The ML65244 and ML65L244 are capable of driving load capacitances several times larger than their input capacitance. They are configured so that the Ai inputs go to the YAi outputs, with the A side output enable controlled by  $\overline{1G}$ . Smilarly,  $\overline{2G}$ controls the Bi inputs which go to the YBi outputs.

These unity gain analog buffers achieve low propagation delays by having the output follow the input with a small offset. The output rise and fall times will closely match those of the input waveform. All inputs and outputs have Schottky clamp diodes to handle undershoot or overshoot noise suppression in unterminated applications. All outputs have ground bounce suppression (typically < 400mV), high drive output capability with almost immediate response to the input signal, and low output skew.

The I<sub>OL</sub> current drive capability of a buffer/line driver is often interpreted as a measure of its ability to sink current in a dynamic sense. This may be true for CMOS buffer/

line drivers, but it is not true for the ML65244 and ML65L244. This is because their sink and source current capability depends on the voltage difference between the output and the input. The ML65244 can sink or source more than 100mA to a load when the load is switching due to the fact that during the transition, the difference between the input and output is large.  $I_{OL}$  is only significant as a DC specification, and is 25mA.

#### ARCHITECTURAL DESCRIPTION

Until now, buffer/line drivers have been implemented in CMOSlogic and made to be TTL compatible by sizing the input devices appropriately. In order to buffer large capacitances with CMOS logic, it is necessary to cascade an even number of inverters, each successive inverter larger than the preceding, eventually leading to an inverter that will drive the required load capacitance at the required frequency. Each inverter stage represents an additional delay in the gating process because in order for a single gate to switch, the input must slew more than half of the supply voltage. The best of these CMOS buffers has managed to drive a 50pF load capacitance with a delay of 3.2ns. Micro Linear has produced a dual quad buffer/line driver with a delay less than 1.7ns by using a unique circuit architecture that does not require cascaded logic gates. The ML65244 uses a feedback technique to produce an output that follows the input. If the output voltage is not close to the input, then the feedback circuitry will source or sink enough current to the load capacitance to correct the discrepancy.

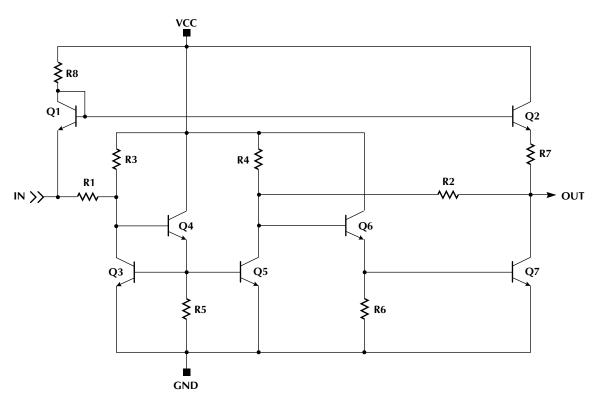

Figure 5. One buffer cell of the ML65244

# ML65244/ML65L244

The basic architecture of the ML65244 is shown in Figure 5. It is implemented on a 1.5 $\mu$ m BiCMOS process. However, in this particular circuit, all of the active devices are NPNs — the fastest devices available in the process.

In this circuit, there are two paths to the output. One path sources current to the load capacitance when the signal is asserted, and the other path sinks current from the output when the signal is negated.

The assertion path is the emitter follower path consisting of the level shift transistor Q1, the output transistor Q2, and the bias resistor R8. It sources current to the output through the 75 $\Omega$  resistor R7 which is bypassed by another NPN (not shown) during fast input transients. The negation path is a current differencing op amp connected in a follower configuration. The active components in this amplifier are transistors Q3–Q7. R3–R6 are bias resistors, and R1 and R2 are the feedback resistors. The key to understanding the operation of the current differencing op amp is to know that the currents in transistors Q3 and Q5 are the same at all times and that the voltages at the bases of Q4 and Q6 are roughly the same. If the output is higher than the input, then an error current will flow through R2. This error current will flow into the base of Q6 and be multiplied by  $\beta$  squared to the collector of Q7, closing the loop. The larger the discrepancy between the output and input, the larger the feedback current, and the harder Q7 sinks current from the load capacitor.

A number of MOSFETs are not shown in Figure 5. These MOSFETs are used to three-state dormant buffers. For instance, the feedback resistors R1 and R2 were implemented as resistive transmission gates to ensure that disabled buffers do not load the lines they are connected to. Smilarly, there is a PMOS in series with R8 that is normally on but shuts off for disable. Other MOSFETs have been included to ensure that disabled buffers consume no power.

#### **TERMINATION**

R7 in Figure 5 also acts as a termination resistor. This  $75\Omega$  resistor is in series with the output and therefore helps suppress noise caused by transmission line effects such as reflections from mismatched impedances. System designers using CMOS transceivers commonly have to use external resistors in series with each transceiver output to suppress this noise. Systems using the ML65244 or ML65L244 may not have to use these external resistors.

#### APPLICATIONS

There are a wide variety of needs for extremely fast buffers in high speed processor system designs like Pentium, PowerPC, Mips, Sparc, Alpha and other RISC processors. These applications are either in the cache memory area or the main memory (DRAM) area. In addition, fast buffers find applications in high speed graphics and multimedia applications. The high capacitive loading due to multiplexed address lines on the system bus demand external buffers to take up the excess drive current. The needed current to skew the transitions between rise and fall times must be done without adding excessive propagation delay. The ML65244 and ML65L244 are equipped with Schottky diodes to clean up ringing from overshoot and undershoot caused by reflections in unterminated board traces.

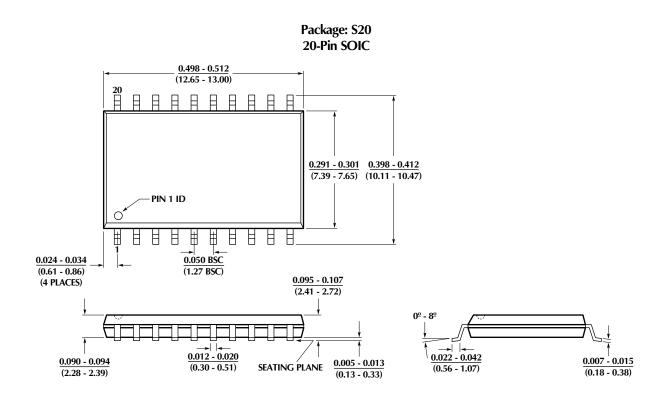

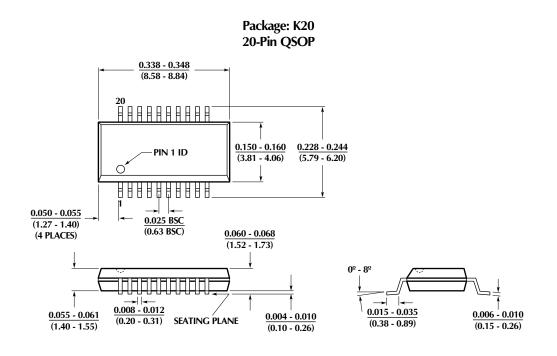

# PHYSICAL DIMENSIONS inches (millimeters)

#### ORDERING INFORMATION

| PART NUMBER | SPEED | TEMPERATURE RANGE | PACKAGE                      |

|-------------|-------|-------------------|------------------------------|

| ML65244CK   | 1.7ns | 0°C to 70°C       | 20-Pin QSOP (K20)            |

| ML65244CS   | 1.7ns | 0°C to 70°C       | 20-Pin SOIC (S20)            |

| ML65L244CK  | 2.0ns | 0°C to 70°C       | 20-Pin QSOP (K20) (Obsolete) |

| ML65L244CS  | 2.0ns | 0°C to 70°C       | 20-Pin SOIC (S20) (Obsolete) |

Intel, Pentium, PCI are registered trademarks of Intel Corporation. Mips, Alpha and Sparc are registered trademarks of Slicon Graphics, DEC and Sun Microsystems respectively.

© Micro Linear 1997 Micro Linear is a registered trademark of Micro Linear Corporation

Products described in this document may be covered by one or more of the following patents, U.S.: 4,897,611; 4,964,026; 5,027,116; 5,281,862; 5,283,483; 5,418,502; 5,508,570; 5,510,727; 5,523,940; 5,546,017; 5,559,470; 5,565,761; 5,592,128; 5,594,376; Japan: 2598946; 2619299. Other patents are pending.

Micro Linear reserves the right to make changes to any product herein to improve reliability, function or design. Micro Linear does not assume any liability arising out of the application or use of any product described herein, neither does it convey any license under its patent right nor the rights of others. The circuits contained in this data sheet are offered as possible applications only. Micro Linear makes no warranties or representations as to whether the illustrated circuits infringe any intellectual property rights of others, and will accept no responsibility or liability for use of any application herein. The customer is urged to consult with appropriate legal counsel before deciding on a particular application.

2092 Concourse Drive San Jose, CA 95131 Tel: 408/433-5200 Fax: 408/432-0295