## **Technical Specification**

PMM 8000 series PoL Regulators 2/28701-BMR 651 Rev. A November 2017 Input 8-14 V, Output 50 A / 275 W © Flex

## **Key Features**

- 50A output current

- 8-14V input voltage range

- Output voltages from 0.8V up to 5.5V

- Industry standard POLA<sup>TM</sup> compatible

52 x 26.7x 9.07 mm (2.05 x 1.05 x 0.357 in.)

- High efficiency, up to. 96%

- Auto Track<sup>TM</sup> sequencing pin

- Differential output voltage sense

- More than 1.27 million hours MTBF

#### **General Characteristics**

- Operating temperature: -40°C to 85°C

- Start up into a pre-biased output safe

- Output short-circuit protection

- Over temperature protection

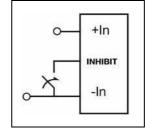

- On/Off inhibit control

- · Margin up/down control

- · Highly automated manufacturing ensures quality

- ISO 9001/14001 certified supplier

**Safety Approvals**

#### **Design for Environment**

Meets requirements in hightemperature lead-free soldering processes.

#### **Contents**

| General Information<br>Safety Specification<br>Absolute Maximum Ratings |                        |

|-------------------------------------------------------------------------|------------------------|

| Product Program<br>0.8-5.5 V/50 A                                       | Ordering No. PMM 8218T |

| 1.0 V/50 A Electrical Specification                                     | 5                      |

| 1.2 V/50 A Electrical Specification                                     | 8                      |

| 1.5 V/50 A Electrical Specification                                     | 11                     |

| 1.8 V/50 A Electrical Specification                                     | 14                     |

| 2.5 V/50 A Electrical Specification                                     |                        |

| 3.3 V/50 A Electrical Specification                                     | 20                     |

| 5.0 V/50 A Electrical Specification                                     | 23                     |

| EMC Specification                                                       | 26                     |

| Operating Information                                                   | 26                     |

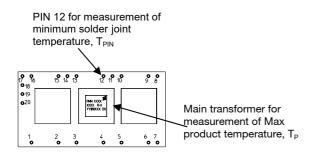

| Thermal Consideration                                                   | 28                     |

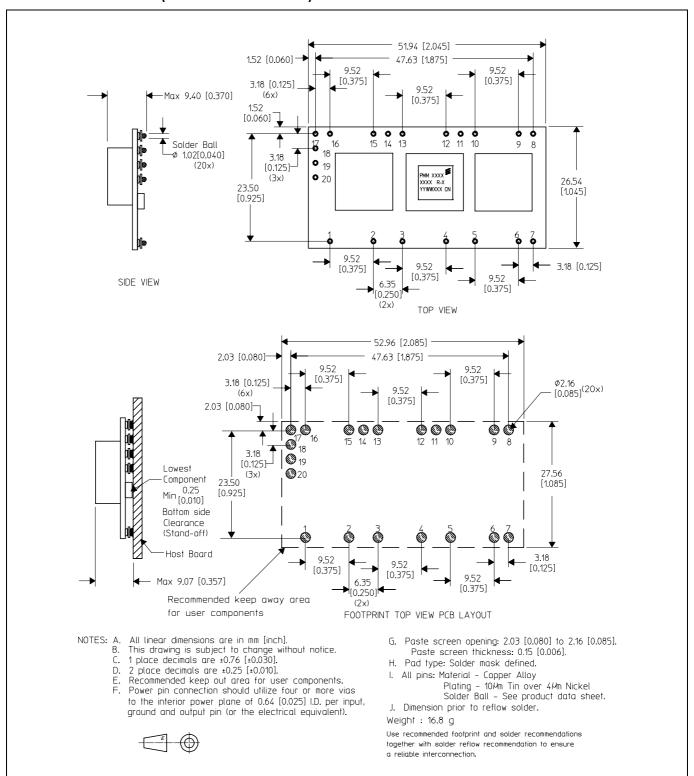

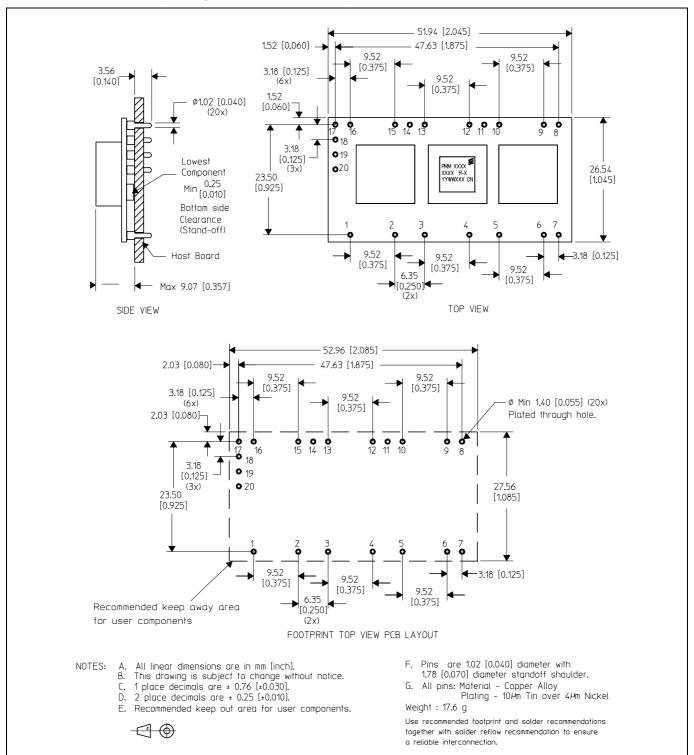

| Connections                                                             | 29                     |

| Mechanical Information                                                  | 30                     |

| Soldering Information                                                   | 32                     |

| Delivery Information                                                    | 33                     |

| Product Qualification Specification                                     | 34                     |

| PMM 8000 series PoL Regulators    | 2/ 28701- BMR 651 Rev. A | November 2017 |

|-----------------------------------|--------------------------|---------------|

| Input 8-14 V, Output 50 A / 275 W | © Flex                   |               |

#### **General Information**

#### **Ordering Information**

See Contents for individual product ordering numbers.

| Option                                       | Suffix | Ordering No. |

|----------------------------------------------|--------|--------------|

| Through hole pin                             | Р      | PMM 8218T P  |

| SMD pin, leadfree reflow temperature capable | SR     | PMM 8218T SR |

#### Reliability

The Mean Time Between Failure (MTBF) is calculated at full output power and an operating ambient temperature ( $T_A$ ) of +40°C, which is a typical condition in Information and Communication Technology (ICT) equipment. Different methods could be used to calculate the predicted MTBF and failure rate which may give different results. Flex currently uses Telcordia SR332.

Predicted MTBF for the series is:

1.27 million hours according to Telcordia SR332, issue

1, Black box technique.

Telcordia SR332 is a commonly used standard method intended for reliability calculations in ICT equipment. The parts count procedure used in this method was originally modelled on the methods from MIL-HDBK-217F, Reliability Predictions of Electronic Equipment. It assumes that no reliability data is available on the actual units and devices for which the predictions are to be made, i.e. all predictions are based on generic reliability parameters.

#### Compatibility with RoHS requirements

The products are compatible with the relevant clauses and requirements of the RoHS directive 2011/65/EU and have a maximum concentration value of 0.1% by weight in homogeneous materials for lead, mercury, hexavalent chromium, PBB and PBDE and of 0.01% by weight in homogeneous materials for cadmium.

Exemptions in the RoHS directive utilized in Flex products are found in the Statement of Compliance document.

Flex fulfills and will continuously fulfill all its obligations under regulation (EC) No 1907/2006 concerning the registration, evaluation, authorization, and restriction of chemicals (REACH) as they enter into force and is through product materials declarations preparing for the obligations to communicate information on substances in the products.

#### **Quality Statement**

The products are designed and manufactured in an industrial environment where quality systems and methods like ISO 9000,  $6\sigma$  (sigma), and SPC are intensively in use to boost the continuous improvements strategy. Infant mortality or early failures in the products are screened out and they are subjected to an ATE-based final test. Conservative design rules, design reviews and product qualifications, plus the high competence of an engaged work force, contribute to the high quality of our products.

#### Warranty

Warranty period and conditions are defined in Flex General Terms and Conditions of Sale.

#### **Limitation of Liability**

Flex does not make any other warranties, expressed or implied including any warranty of merchantability or fitness for a particular purpose (including, but not limited to, use in life support

(including, but not limited to, use in life support applications, where malfunctions of product can cause injury to a person's health or life).

#### © Flex 2017

The information and specifications in this technical specification is believed to be correct at the time of publication. However, no liability is accepted for inaccuracies, printing errors or for any consequences thereof. Flex reserves the right to change the contents of this technical specification at any time without prior notice.

| PMM 8000 series PoL Regulators    | 2/ 28701- BMR 651 Rev. A | November 2017 |

|-----------------------------------|--------------------------|---------------|

| Input 8-14 V, Output 50 A / 275 W | © Flex                   |               |

#### **Safety Specification**

#### **General information**

Flex DC/DC converters and DC/DC regulators are designed in accordance with safety standards IEC/EN/UL60950, Safety of Information Technology Equipment.

IEC/EN/UL60950 contains requirements to prevent injury or damage due to the following hazards:

- Electrical shock

- Energy hazards

- Fire

- Mechanical and heat hazards

- Radiation hazards

- Chemical hazards

On-board DC-DC converters are defined as component power supplies. As components they cannot fully comply with the provisions of any Safety requirements without "Conditions of Acceptability". It is the responsibility of the installer to ensure that the final product housing these components complies with the requirements of all applicable Safety standards and Directives for the final product.

Component power supplies for general use should comply with the requirements in IEC60950, EN60950 and UL60950 "Safety of information technology equipment".

There are other more product related standards, e.g. IEEE802.3af "Ethernet LAN/MAN Data terminal equipment power", and ETS300132-2 "Power supply interface at the input to telecommunications equipment; part 2: DC", but all of these standards are based on IEC/EN/UL60950 with regards to safety.

Flex DC/DC converters and DC/DC regulators are UL60950 recognized and certified in accordance with EN60950.

The flammability rating for all construction parts of the products meets requirements for V-0 class material according to IEC 60695-11-10.

The products should be installed in the end-use equipment, in accordance with the requirements of the ultimate application. Normally the output of the DC/DC converter is considered as SELV (Safety Extra Low Voltage) and the input source must be isolated by minimum Double or Reinforced Insulation from the primary circuit (AC mains) in accordance with IEC/EN/UL60950.

#### Isolated DC/DC converters

It is recommended that a slow blow fuse with a rating twice the maximum input current per selected product be used at the input of each DC/DC converter. If an input filter is used in the circuit the fuse should be placed in front of the input filter.

In the rare event of a component problem in the input filter or in the DC/DC converter that imposes a short circuit on the input source, this fuse will provide the following functions:

- Isolate the faulty DC/DC converter from the input power source so as not to affect the operation of other parts of the system.

- Protect the distribution wiring from excessive current and power loss thus preventing hazardous overheating.

The galvanic isolation is verified in an electric strength test. The test voltage ( $V_{\rm iso}$ ) between input and output is 1500 Vdc or 2250 Vdc for 60 seconds (refer to product specification).

Leakage current is less than 1 µA at nominal input voltage.

#### 24 V DC systems

The input voltage to the DC/DC converter is SELV (Safety Extra Low Voltage) and the output remains SELV under normal and abnormal operating conditions.

#### 48 and 60 V DC systems

If the input voltage to Flex DC/DC converter is 75 Vdc or less, then the output remains SELV (Safety Extra Low Voltage) under normal and abnormal operating conditions.

Single fault testing in the input power supply circuit should be performed with the DC/DC converter connected to demonstrate that the input voltage does not exceed 75 Vdc.

If the input power source circuit is a DC power system, the source may be treated as a TNV2 circuit and testing has demonstrated compliance with SELV limits and isolation requirements equivalent to Basic Insulation in accordance with IEC/EN/UL60950.

#### Non-isolated DC/DC regulators

The input voltage to the DC/DC regulator is SELV (Safety Extra Low Voltage) and the output remains SELV under normal and abnormal operating conditions.

| PMM 8000 series PoL Regulators    | 2/ 28701- BMR 651 Rev. A | November 2017 |

|-----------------------------------|--------------------------|---------------|

| Input 8-14 V, Output 50 A / 275 W | © Flex                   |               |

## **Absolute Maximum Ratings**

| Characteristics  |                                                                            |                       | min | typ  | max  | Unit |

|------------------|----------------------------------------------------------------------------|-----------------------|-----|------|------|------|

| $T_{amb}$        | T <sub>amb</sub> Operating Temperature (see Thermal Consideration section) |                       | -40 |      | 85   | °C   |

| Ts               | Storage temperature                                                        |                       | -40 |      | 125  | °C   |

| Vı               | V <sub>I</sub> Input voltage                                               |                       | 8.0 | 12.0 | 14.0 | V    |

| \/               | Inhibit On/Off pin voltage                                                 | Positive logic option | 2.5 |      | Open | V    |

| V <sub>inh</sub> | V <sub>inh</sub> (see Operating Information section)                       | Negative logic option | N/A |      | N/A  | V    |

Stress in excess of Absolute Maximum Ratings may cause permanent damage. Absolute Maximum Ratings, sometimes referred to as no destruction limits, are normally tested with one parameter at a time exceeding the limits of Output data or Electrical Characteristics. If exposed to stress above these limits, function and performance may degrade in an unspecified manner.

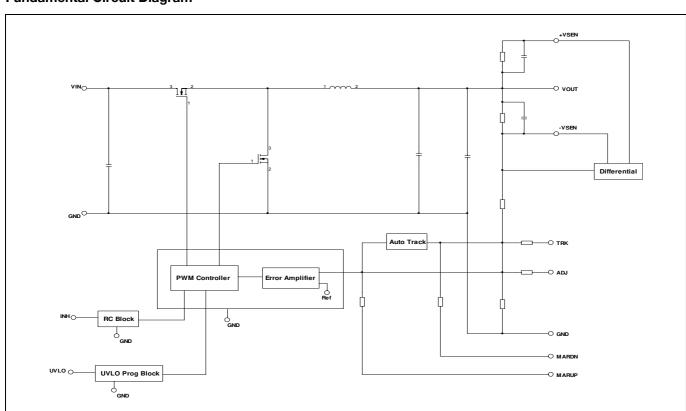

## **Fundamental Circuit Diagram**

| PMM 8000 series PoL Regulators    | 2/ 28701- BMR 651 Rev. A | November 2017 |

|-----------------------------------|--------------------------|---------------|

| Input 8-14 V, Output 50 A / 275 W | © Flex                   |               |

## 1.0 V/50 A Electrical Specification

**PMM 8218T**

$T_{ref}$  = -40 to +85°C,  $V_l$  = 8.0 to 14.0 V,  $R_{adj}$  = 38.3 kΩ, unless otherwise specified under Conditions. Typical values given at:  $T_{ref}$  = +25°C,  $V_l$ = 12.0 V, max  $I_O$ , unless otherwise specified under Conditions. Additional  $C_{in}$ = 1000μF and  $C_{out}$ = 660μF. See Operating Information section for selection of capacitor types. Connect the sense pin, where available, to the output pin.

| Charac           | teristics                  | Conditions                                  |                                                   | min | typ  | max  | Unit |  |

|------------------|----------------------------|---------------------------------------------|---------------------------------------------------|-----|------|------|------|--|

| V <sub>I</sub>   | Input voltage range        |                                             |                                                   | 8.0 |      | 14.0 | V    |  |

| UVLO             | Undervoltage lockout       | Pin 8 open                                  | On-threshold                                      |     | 7.5  |      | V    |  |

| UVLO             | Officer voltage lockout    | Fill 6 Open                                 | Hysterisis                                        |     | 1    | •    | v    |  |

| Cı               | Internal input capacitance |                                             |                                                   |     | 80   |      | μF   |  |

| Po               | Output power               |                                             |                                                   | 0   |      | 50   | W    |  |

| η Efficiency     |                            | 50 % of max I <sub>o</sub>                  | 50 % of max I <sub>O</sub>                        |     | 85.9 |      | %    |  |

|                  |                            | max I <sub>o</sub>                          | max I <sub>O</sub>                                |     | 82.5 |      | 70   |  |

| $P_d$            | Power Dissipation          | max I <sub>o</sub>                          | max I <sub>O</sub>                                |     | 10.6 |      | W    |  |

| P <sub>li</sub>  | Input idling power         | $I_0 = 0, V_1 = 12.0 \text{ V}$             |                                                   |     | 1360 |      | mW   |  |

| P <sub>inh</sub> | Input standby power        | V <sub>I</sub> = 12.0 V (turned             | V <sub>I</sub> = 12.0 V (turned off with INHIBIT) |     | 420  |      | mW   |  |

| Is               | Static Input current       | V <sub>I</sub> = 12.0 V, max I <sub>O</sub> |                                                   |     | 5.1  |      | Α    |  |

| f <sub>s</sub>   | Switching frequency        | 0-100 % of max I                            | 0                                                 | 900 | 1050 | 1200 | kHz  |  |

| $V_{Oi}$         | Output voltage initial setting and accuracy                              | $T_{ref} = +25^{\circ}C, V_{I} = 12.0 \text{ V, max } I_{O}$                           | 0.980 | 1.000 | 1.020 | V     |

|------------------|--------------------------------------------------------------------------|----------------------------------------------------------------------------------------|-------|-------|-------|-------|

|                  | Output voltage tolerance band                                            | 10-100 % of max I <sub>o</sub>                                                         | 0.970 |       | 1.030 | V     |

| \/               | Idling voltage                                                           | $I_{O} = 0$                                                                            |       | 0.998 |       | V     |

| Vo               | Line regulation                                                          | max I <sub>O</sub>                                                                     |       | ±5    |       | mV    |

|                  | Load regulation                                                          | $V_{I} = 12.0 \text{ V}, 0-100 \text{ % of max } I_{O}$                                |       | ±5    |       | mV    |

| V <sub>tr</sub>  | Load transient voltage deviation                                         | V <sub>I</sub> = 12.0 V, Load step 50-100-50 % of max I <sub>O</sub> , di/dt = 1 A/μs, |       | ±75   |       | mV    |

| t <sub>tr</sub>  | Load transient recovery time                                             | see Note 1                                                                             |       | 100   |       | μs    |

| t <sub>r</sub>   | Ramp-up time<br>(from 10–90 % of V <sub>oi</sub> )                       | max I <sub>0</sub>                                                                     |       | 2.2   |       | ms    |

| t <sub>s</sub>   | Start-up time (from V <sub>i</sub> connection to 90% of V <sub>o</sub> ) | 111dX 1 <sub>0</sub>                                                                   |       | 6.4   |       | ms    |

| +                | Ramp-down time                                                           | Max I <sub>O</sub>                                                                     |       | 10    |       | μs    |

| t <sub>f</sub>   | (from 90–10 % of V <sub>Oi</sub> )                                       | I <sub>O</sub> = 0.1 A                                                                 | 25.1  |       |       | ms    |

|                  | INHIBIT start-up time                                                    | Max I <sub>O</sub>                                                                     |       | 5.6   |       | ms    |

| t <sub>Inh</sub> | INHIBIT shutdown fall time                                               | Max I <sub>O</sub>                                                                     |       | 30    |       | μs    |

|                  | (From INHIBIT off to 10% of V <sub>o</sub> )                             | I <sub>O</sub> = 0.1 A                                                                 |       | 3.8   |       | ms    |

| Io               | Output current                                                           |                                                                                        | 0     |       | 50    | Α     |

| I <sub>lim</sub> | Current limit threshold                                                  | $T_{ref} < max T_{ref,}$                                                               |       | 95    |       | Α     |

| V <sub>Oac</sub> | Output ripple & noise                                                    | See ripple & noise section, max I <sub>o</sub> , V <sub>oi</sub>                       |       | 15    |       | mVp-p |

Note 1: Output filter according to Ripple & Noise section

|                                   | <u> </u>                 |               |

|-----------------------------------|--------------------------|---------------|

| PMM 8000 series PoL Regulators    | 2/ 28701- BMR 651 Rev. A | November 2017 |

| Input 8-14 V, Output 50 A / 275 W | © Flex                   |               |

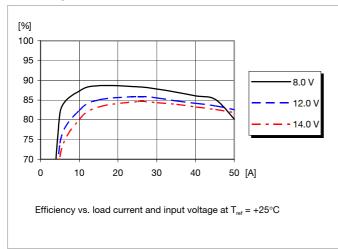

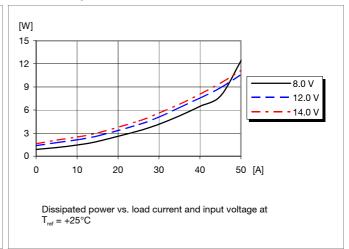

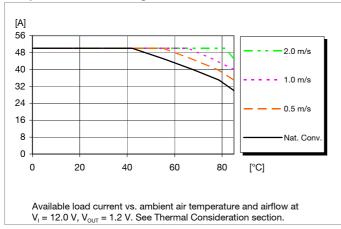

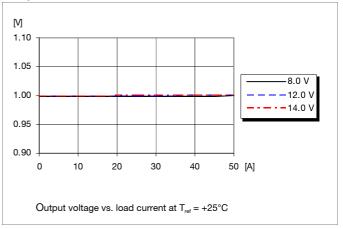

## 1.0 V/50 A Typical Characteristics

#### **PMM 8218T**

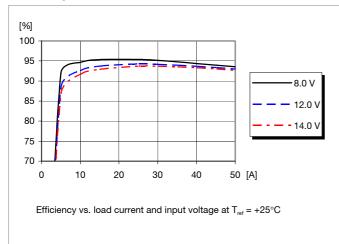

#### **Efficiency**

#### **Power Dissipation**

#### **Output Current Derating**

**Technical Specification**

| 2/ 28701- BMR 651 Rev. A | November 2017 |

|--------------------------|---------------|

| © Flex                   |               |

## **PMM 8000 series** PoL Regulators Input 8-14 V, Output 50 A / 275 W

## 1.0 V/50 A Typical Characteristics

#### **PMM 8218T**

7

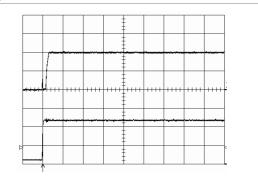

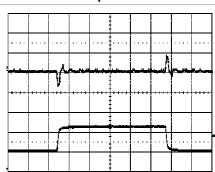

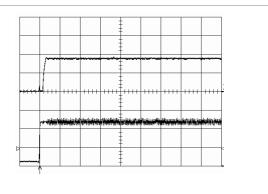

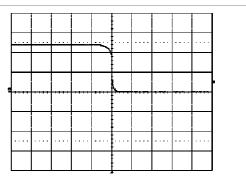

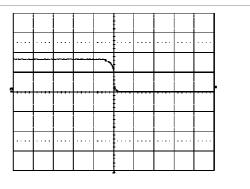

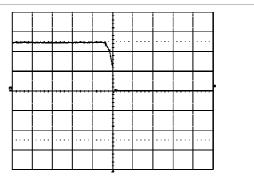

#### Start-up

Start-up enabled by connecting V<sub>I</sub> at:  $T_{ref} = +25^{\circ}C$ ,  $I_{O} = 50$  A resistive load,  $V_{I} = 12.0$  V.

Top trace: output voltage (0.5 V/div.). Bottom trace: input voltage (5 V/div.). Time scale: 20 ms/div.

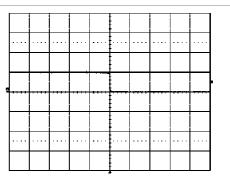

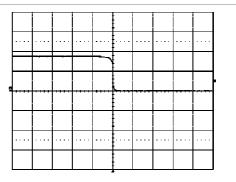

#### Shut-down

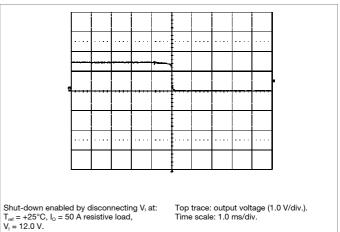

Shut-down enabled by disconnecting  $V_{l}$  at:  $T_{\rm ref} = +25^{\circ}\text{C}$ ,  $I_{o} = 50$  A resistive load,  $V_{l} = 12.0$  V.

Top trace: output voltage (1.0 V/div.). Time scale: 1.0 ms/div.

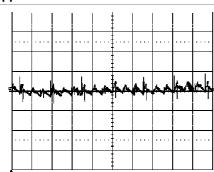

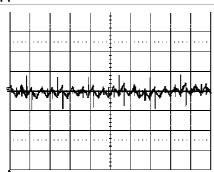

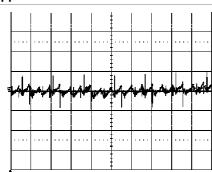

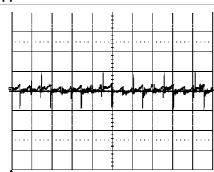

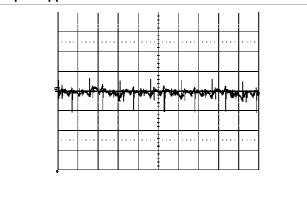

#### **Output Ripple & Noise**

Output voltage ripple (20 mV/div.) at:  $T_{\rm ref} = +25^{\circ}C$ ,  $I_{0} = 50$  A resistive load,  $V_{1} = 12.0$  V. Time scale: 2  $\mu$ s/div.

See the filter in the Output ripple and noise section (EMC Specification).

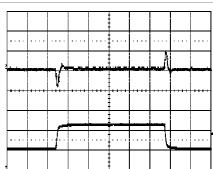

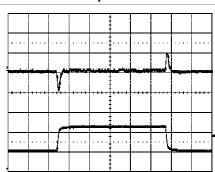

#### **Output Load Transient Response**

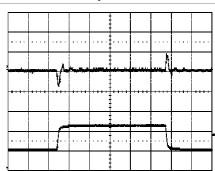

Output voltage response to load current step-change (25-50-25 A) at:  $T_{\rm ref}$  =+25°C,  $V_{\rm l}$  = 12.0 V.

Top trace: output voltage (100 mV/div.). Bottom trace: load current (20 A/div.). Time scale: 0.2 ms/div.

7.5

1

15

Characteristics

**UVLO**

| PMM 8000 series PoL Regulators    | 2/ 28701- BMR 651 Rev. A | November 2017 |

|-----------------------------------|--------------------------|---------------|

| Input 8-14 V, Output 50 A / 275 W | © Flex                   |               |

On-threshold

Hysterisis

8.0

## 1.2 V/50 A Electrical Specification

Input voltage range

Undervoltage lockout

**PMM 8218T**

٧

٧

mVp-p

14.0

$T_{ref}$  = -40 to +85°C,  $V_l$  = 8.0 to 14.0 V,  $R_{adj}$  = 18.2 kΩ, unless otherwise specified under Conditions. Typical values given at:  $T_{ref}$  = +25°C,  $V_l$ = 12.0 V, max  $I_O$ , unless otherwise specified under Conditions. Additional  $C_{in}$ = 1000μF and  $C_{out}$ = 660μF. See Operating Information section for selection of capacitor types. Connect the sense pin, where available, to the output pin.

Conditions

Pin 8 open

max I<sub>O</sub>, V<sub>Oi</sub>

| $C_{l}$          | Internal input capacitance                                               |                                                                                        |       | 80    |       | μF    |  |

|------------------|--------------------------------------------------------------------------|----------------------------------------------------------------------------------------|-------|-------|-------|-------|--|

| Po               | Output power                                                             |                                                                                        | 0 60  |       | W     |       |  |

| n                | Efficiency                                                               | 50 % of max I <sub>O</sub>                                                             | 87.9  |       | %     |       |  |

| η                | Linciency                                                                | max I <sub>O</sub>                                                                     | 84.9  |       |       | 70    |  |

| $P_d$            | Power Dissipation                                                        | max I <sub>0</sub>                                                                     | 10.7  |       | W     |       |  |

| P <sub>li</sub>  | Input idling power                                                       | I <sub>O</sub> = 0, V <sub>I</sub> = 12.0 V                                            |       | 1400  |       | mW    |  |

| P <sub>inh</sub> | Input standby power                                                      | V <sub>I</sub> = 12.0 V (turned off with INHIBIT)                                      |       | 420   |       | mW    |  |

| Is               | Static Input current                                                     | V <sub>I</sub> = 12.0 V, max I <sub>O</sub>                                            |       | 5.9   |       | Α     |  |

| fs               | Switching frequency                                                      | 0-100 % of max I <sub>O</sub>                                                          | 900   | 1050  | 1200  | kHz   |  |

|                  | •                                                                        |                                                                                        |       |       |       | •     |  |

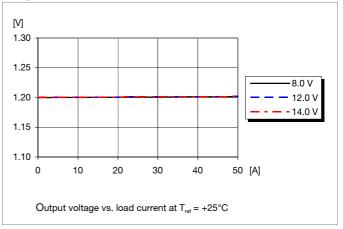

| V <sub>Oi</sub>  | Output voltage initial setting and accuracy                              | $T_{ref} = +25^{\circ}C, V_{I} = 12.0 \text{ V, max } I_{O}$                           | 1.176 | 1.200 | 1.224 | V     |  |

|                  | Output voltage tolerance band                                            | 10-100 % of max I <sub>O</sub>                                                         | 1.164 |       | 1.236 | V     |  |

| .,               | Idling voltage                                                           | I <sub>O</sub> = 0                                                                     |       | 1.200 |       | V     |  |

| $V_{O}$          | Line regulation                                                          | max I <sub>O</sub>                                                                     |       | ±5    |       | mV    |  |

|                  | Load regulation                                                          | V <sub>I</sub> = 12.0 V, 0-100% of max I <sub>O</sub>                                  |       | ±5    |       | mV    |  |

| $V_{tr}$         | Load transient voltage deviation                                         | V <sub>I</sub> = 12.0 V, Load step 50-100-50 % of max I <sub>O</sub> , di/dt = 1 A/μs, | ±80   |       | mV    |       |  |

| t <sub>tr</sub>  | Load transient recovery time                                             | see Note 1                                                                             |       | 100   |       | μs    |  |

| t <sub>r</sub>   | Ramp-up time<br>(from 10–90 % of V <sub>oi</sub> )                       | max I <sub>O</sub>                                                                     | 2.2   |       |       | ms    |  |

| t <sub>s</sub>   | Start-up time (from V <sub>1</sub> connection to 90% of V <sub>0</sub> ) | max 1 <sub>0</sub>                                                                     |       | 6.3   |       | ms    |  |

| t <sub>f</sub>   | Ramp-down time                                                           | Max I <sub>O</sub>                                                                     |       | 60    |       | μs    |  |

| Lf               | (from 90–10 % of V <sub>oi</sub> )                                       | I <sub>O</sub> = 0.1 A                                                                 |       | 29.9  |       | ms    |  |

|                  | INHIBIT start-up time                                                    | Max I <sub>O</sub>                                                                     |       | 5.6   |       | ms    |  |

| $t_{Inh}$        | INHIBIT shutdown fall time                                               | Max I <sub>O</sub>                                                                     |       | 30    |       | μs    |  |

|                  | (From INHIBIT off to 10% of V <sub>o</sub> )                             | I <sub>O</sub> = 0.1 A                                                                 |       | 4.5   |       | ms    |  |

| Io               | Output current                                                           |                                                                                        | 0     |       | 50    | Α     |  |

| l <sub>lim</sub> | Current limit threshold                                                  | T <sub>ref</sub> < max T <sub>ref,</sub>                                               |       | 95    |       | Α     |  |

| Voac             | Output ripple & noise                                                    | See ripple & noise section,                                                            |       | 15    |       | mVp-p |  |

Note 1: Output filter according to Ripple & Noise section

Output ripple & noise

| PMM 8000 series PoL Regulators    | 2/ 28701- BMR 651 Rev. A | November 2017 |

|-----------------------------------|--------------------------|---------------|

| Input 8-14 V, Output 50 A / 275 W | © Flex                   |               |

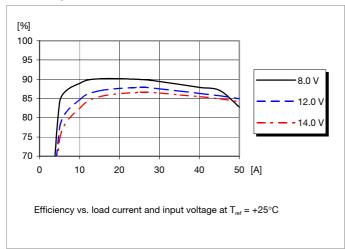

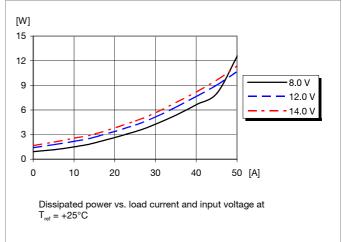

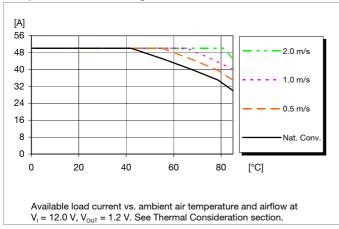

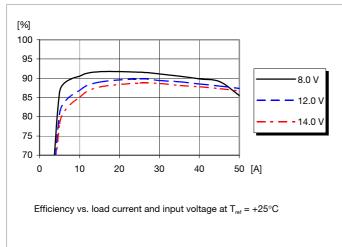

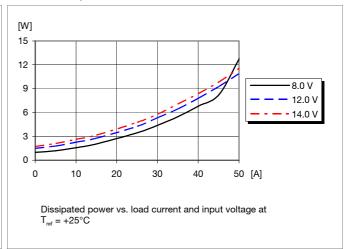

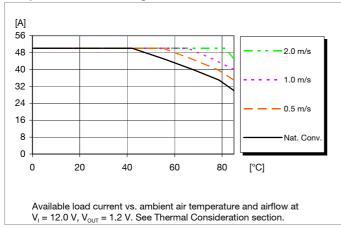

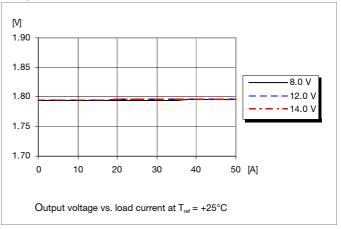

## 1.2 V/50 A Typical Characteristics

#### **PMM 8218T**

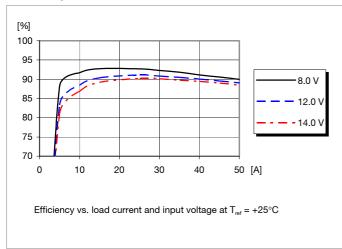

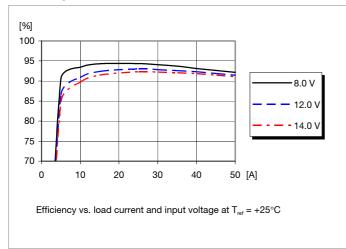

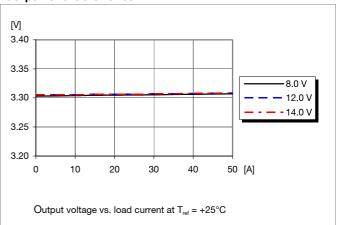

#### **Efficiency**

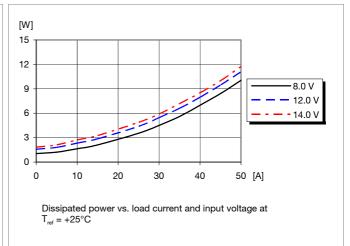

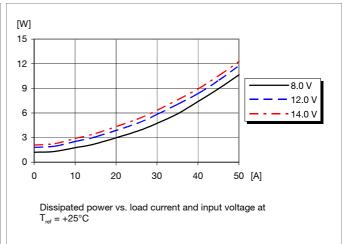

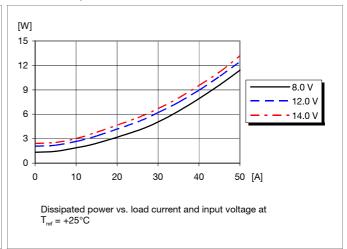

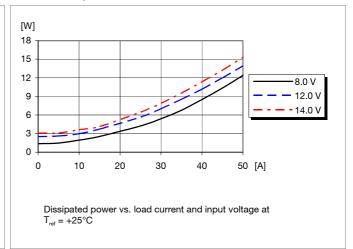

#### **Power Dissipation**

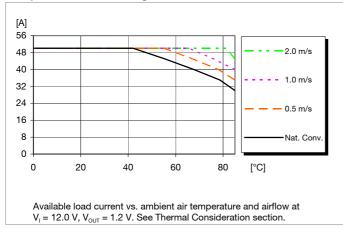

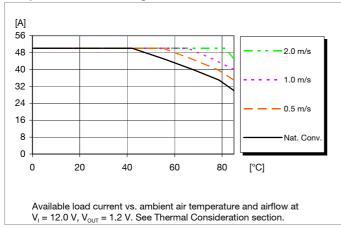

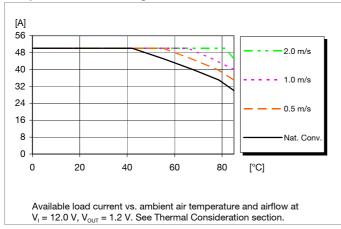

#### **Output Current Derating**

| PMM 8000 series PoL Regulators    | 2/ 28701- BMR 651 Rev. A | November 2017 |

|-----------------------------------|--------------------------|---------------|

| Input 8-14 V, Output 50 A / 275 W | © Flex                   |               |

## 1.2 V/50 A Typical Characteristics

#### **PMM 8218T**

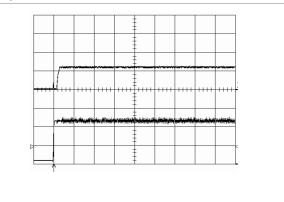

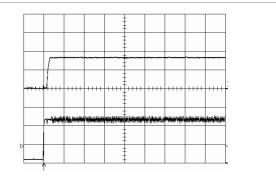

#### Start-up

Start-up enabled by connecting V<sub>I</sub> at:  $T_{ref} = +25^{\circ}C$ ,  $I_{O} = 50$  A resistive load,  $V_{I} = 12.0$  V.

Top trace: output voltage (1.0 V/div.). Bottom trace: input voltage (5 V/div.). Time scale: 20 ms/div.

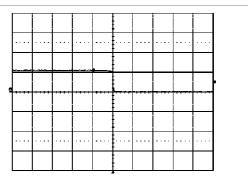

#### Shut-down

Shut-down enabled by disconnecting V<sub>I</sub> at:  $T_{\rm ref} = +25\,^{\circ}\text{C}$ , I<sub>O</sub> = 50 A resistive load, V<sub>I</sub> = 12.0 V.

Top trace: output voltage (1.0 V/div.). Time scale: 1.0 ms/div.

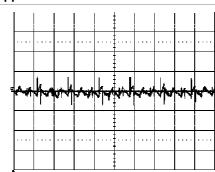

#### **Output Ripple & Noise**

Output voltage ripple (20 mV/div.) at:  $T_{\text{ref}} = +25^{\circ}\text{C}$ ,  $I_{\text{o}} = 50$  A resistive load,  $V_{\text{i}} = 12.0$  V. Time scale: 2  $\mu\text{s}/\text{div}$ .

See the filter in the Output ripple and noise section (EMC Specification).

#### **Output Load Transient Response**

Output voltage response to load current step-change (25-50-25 A) at: Bottom trace: output voltage (100 mV/div.). Bottom trace: load current (20 A/div.).  $T_{ref} = +25^{\circ}\text{C}, \ V_i = 12.0 \ \text{V}.$  Time scale: 0.2 ms/div.

| PMM 8000 series PoL Regulators    | 2/ 28701- BMR 651 Rev. A | November 2017 |

|-----------------------------------|--------------------------|---------------|

| Input 8-14 V, Output 50 A / 275 W | © Flex                   |               |

## 1.5 V/50 A Electrical Specification

**PMM 8218T**

$T_{ref}$  = -40 to +85°C,  $V_l$  = 8.0 to 14.0 V,  $R_{adj}$  = 9.76 kΩ, unless otherwise specified under Conditions. Typical values given at:  $T_{ref}$  = +25°C,  $V_l$ = 12.0 V, max  $I_O$ , unless otherwise specified under Conditions. Additional  $C_{in}$ = 1000μF and  $C_{out}$ = 660μF. See Operating Information section for selection of capacitor types. Connect the sense pin, where available, to the output pin.

| Characteristics  |                                             | Conditions                          |                            | min   | typ   | max   | Unit |  |

|------------------|---------------------------------------------|-------------------------------------|----------------------------|-------|-------|-------|------|--|

| V <sub>I</sub>   | Input voltage range                         |                                     |                            | 8.0   |       | 14.0  | V    |  |

| UVLO             | Undervoltage lockout                        | Pin 8 open                          | On-threshold               |       | 7.5   |       | V    |  |

| OVLO             | Orider voltage lockout                      | Fill 6 Open                         | Hysterisis                 |       | 1     |       | V    |  |

| Cı               | Internal input capacitance                  |                                     |                            |       | 80    |       | μF   |  |

| Po               | Output power                                |                                     |                            | 0     |       | 75    | W    |  |

| n                | Efficiency                                  | 50 % of max I <sub>o</sub>          |                            |       | 89.8  |       | %    |  |

| Ч                | Efficiency                                  | max I <sub>O</sub>                  |                            |       | 87.3  |       | 70   |  |

| $P_d$            | Power Dissipation                           | max I <sub>O</sub>                  |                            |       | 10.9  |       | W    |  |

| P <sub>li</sub>  | Input idling power                          | $I_0 = 0, V_1 = 12.0 V$             |                            |       | 1490  |       | mW   |  |

| P <sub>inh</sub> | Input standby power                         | V <sub>I</sub> = 12.0 V (turned     | off with INHIBIT)          |       | 420   |       | mW   |  |

| Is               | Static Input current                        | $V_1 = 12.0 \text{ V, max } I_C$    | )                          |       | 7.2   |       | Α    |  |

| f <sub>s</sub>   | Switching frequency                         | 0-100% of max I <sub>0</sub>        |                            | 900   | 1050  | 1200  | kHz  |  |

|                  |                                             |                                     |                            |       |       |       |      |  |

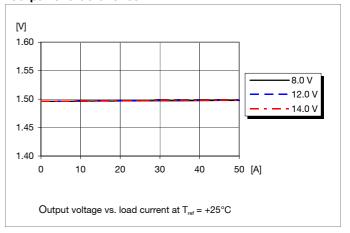

| V <sub>Oi</sub>  | Output voltage initial setting and accuracy | $T_{ref} = +25^{\circ}C, V_{I} = 1$ | 12.0 V, max I <sub>0</sub> | 1.470 | 1.500 | 1.530 | V    |  |

|                  | Output voltage tolerance band               | 10-100% of max I                    | 0                          | 1.455 |       | 1.545 | V    |  |

|                  | Idling valtage                              | 1 0                                 |                            |       | 1 407 |       | W    |  |

| V <sub>Oi</sub>  | Output voltage initial setting and accuracy                               | $T_{ref} = +25^{\circ}C, V_{I} = 12.0 \text{ V, max } I_{O}$                           | 1.470 | 1.500 | 1.530 | V     |

|------------------|---------------------------------------------------------------------------|----------------------------------------------------------------------------------------|-------|-------|-------|-------|

|                  | Output voltage tolerance band                                             | 10-100% of max I <sub>O</sub>                                                          | 1.455 |       | 1.545 | V     |

| .,               | Idling voltage                                                            | I <sub>O</sub> = 0                                                                     |       | 1.497 |       | V     |

| Vo               | Line regulation                                                           | max I <sub>O</sub>                                                                     |       | ±5    |       | mV    |

|                  | Load regulation                                                           | $V_{\rm I}$ = 12.0 V, 0-100% of max $I_{\rm O}$                                        |       | ±5    |       | mV    |

| $V_{tr}$         | Load transient voltage deviation                                          | V <sub>I</sub> = 12.0 V, Load step 50-100-50 % of max I <sub>O</sub> , di/dt = 1 A/μs, | ±80   |       | mV    |       |

| t <sub>tr</sub>  | Load transient recovery time                                              | see Note 1                                                                             |       | 100   |       | μs    |

| t <sub>r</sub>   | Ramp-up time<br>(from 10–90 % of V <sub>oi</sub> )                        | max I <sub>0</sub>                                                                     |       | 2.4   |       | ms    |

| t <sub>s</sub>   | Start-up time (from V <sub>1</sub> connection to 90% of V <sub>01</sub> ) | 111ax 1 <sub>0</sub>                                                                   |       | 6.3   |       | ms    |

| +                | Ramp-down time                                                            | Max I <sub>O</sub>                                                                     |       | 100   |       | μs    |

| t <sub>f</sub>   | (from 90–10 % of V <sub>Oi</sub> )                                        | I <sub>O</sub> = 0.1 A                                                                 |       | 36.2  |       | ms    |

|                  | INHIBIT start-up time                                                     | Max I <sub>O</sub>                                                                     |       | 5.6   |       | ms    |

| t <sub>Inh</sub> | INHIBIT shutdown fall time                                                | Max I <sub>O</sub>                                                                     |       | 70    |       | μs    |

|                  | (From INHIBIT off to 10% of $V_0$ )                                       | I <sub>O</sub> = 0.1 A                                                                 |       | 5.6   |       | ms    |

| Io               | Output current                                                            |                                                                                        | 0     |       | 50    | Α     |

| I <sub>lim</sub> | Current limit threshold                                                   | T <sub>ref</sub> < max T <sub>ref,</sub>                                               |       | 95    |       | Α     |

| V <sub>Oac</sub> | Output ripple & noise                                                     | See ripple & noise section, max I <sub>o</sub> , V <sub>oi</sub>                       |       | 15    |       | mVp-p |

Note 1: Output filter according to Ripple & Noise section

| PMM 8000 series PoL Regulators    | 2/ 28701- BMR 651 Rev. A | November 2017 |

|-----------------------------------|--------------------------|---------------|

| Input 8-14 V, Output 50 A / 275 W | © Flex                   |               |

## 1.5 V/50 A Typical Characteristics

#### **PMM 8218T**

## **Efficiency**

#### **Power Dissipation**

#### **Output Current Derating**

|                                   | •                        |               |

|-----------------------------------|--------------------------|---------------|

| PMM 8000 series PoL Regulators    | 2/ 28701- BMR 651 Rev. A | November 2017 |

| Input 8-14 V, Output 50 A / 275 W | © Flex                   |               |

## 1.5 V/50 A Typical Characteristics

#### **PMM 8218T**

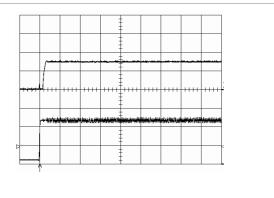

#### Start-up

#### Shut-down

Start-up enabled by connecting V<sub>I</sub> at:  $T_{ref} = +25^{\circ}C$ ,  $I_{O} = 50$  A resistive load,  $V_{I} = 12.0$  V.

Top trace: output voltage (1.0 V/div.). Bottom trace: input voltage (5 V/div.). Time scale: 20 ms/div..

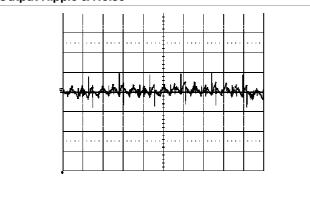

#### **Output Ripple & Noise**

Output voltage ripple (20 mV/div.) at:  $T_{\text{ref}} = +25^{\circ}\text{C}$ ,  $I_{\text{o}} = 50$  A resistive load,  $V_{\text{i}} = 12.0$  V. Time scale: 2  $\mu\text{s}/\text{div}$ .

See the filter in the Output ripple and noise section (EMC Specification).

#### **Output Load Transient Response**

Output voltage response to load current step-change (25-50-25 A) at: Bottom trace: output voltage (100 mV/div.). Bottom trace: load current (20 A/div.).  $T_{ref} = +25^{\circ}\text{C}, \ V_i = 12.0 \ \text{V}.$  Time scale: 0.2 ms/div.

| PMM 8000 series PoL Regulators    | 2/ 28701- BMR 651 Rev. A | November 2017 |

|-----------------------------------|--------------------------|---------------|

| Input 8-14 V, Output 50 A / 275 W | © Flex                   |               |

#### 1.8 V/50 A Electrical Specification

**PMM 8218T**

$T_{ref}$  = -40 to +85°C,  $V_l$  = 8.0 to 14.0 V,  $R_{adj}$  = 6.34 kΩ, unless otherwise specified under Conditions. Typical values given at:  $T_{ref}$  = +25°C,  $V_l$ = 12.0 V, max  $I_O$ , unless otherwise specified under Conditions. Additional  $C_{in}$ = 1000μF and  $C_{out}$ = 660μF. See Operating Information section for selection of capacitor types. Connect the sense pin, where available, to the output pin.

| Charac           | Characteristics Conditions |                                                   | min                     | typ  | max  | Unit |      |

|------------------|----------------------------|---------------------------------------------------|-------------------------|------|------|------|------|

| V <sub>I</sub>   | Input voltage range        |                                                   |                         | 8.0  |      | 14.0 | V    |

| UVLO             | Undervoltage lockout       | Pin 8 open                                        | On-threshold            |      | 7.5  |      | V    |

| UVLO             | Officer voltage lockout    | Fill 6 Open                                       | Hysterisis              |      | 1    |      | v    |

| Cı               | Internal input capacitance |                                                   |                         |      | 80   |      | μF   |

| Po               | Output power               |                                                   |                         | 0    |      | 90   | W    |

| n                | Efficiency 50 % of         |                                                   | % of max I <sub>o</sub> |      | 91.1 |      | %    |

| ''               | Linciency                  | max I <sub>0</sub>                                |                         | 89.0 |      |      | ] /0 |

| P <sub>d</sub>   | Power Dissipation          | max I <sub>O</sub>                                |                         |      | 11.1 |      | W    |

| P <sub>li</sub>  | Input idling power         | $I_0 = 0, V_1 = 12.0 V$                           |                         |      | 1580 |      | mW   |

| P <sub>inh</sub> | Input standby power        | V <sub>I</sub> = 12.0 V (turned off with INHIBIT) |                         |      | 420  |      | mW   |

| Is               | Static Input current       | V <sub>I</sub> = 12.0 V, max I <sub>O</sub>       |                         |      | 8.4  |      | Α    |

| f <sub>s</sub>   | Switching frequency        | 0-100 % of max I <sub>O</sub>                     |                         | 900  | 1050 | 1200 | kHz  |

| .,               | Output voltage initial setting and                                        |                                                                                        | . =0. |       |       | .,    |

|------------------|---------------------------------------------------------------------------|----------------------------------------------------------------------------------------|-------|-------|-------|-------|

| $V_{Oi}$         | accuracy                                                                  | $T_{ref} = +25^{\circ}C, V_{I} = 12.0 \text{ V, max } I_{O}$                           | 1.764 | 1.800 | 1.836 | V     |

|                  | Output voltage tolerance band                                             | 10-100 % of max I <sub>O</sub>                                                         | 1.746 |       | 1.854 | V     |

|                  | Idling voltage                                                            | $I_{O} = 0$                                                                            |       | 1.794 |       | V     |

| Vo               | Line regulation                                                           | max I <sub>O</sub>                                                                     |       | ±5    |       | mV    |

|                  | Load regulation                                                           | $V_{\rm I}$ = 12.0 V, 0-100% of max $I_{\rm O}$                                        |       | ±5    |       | mV    |

| V <sub>tr</sub>  | Load transient voltage deviation                                          | V <sub>I</sub> = 12.0 V, Load step 50-100-50 % of max I <sub>O</sub> , di/dt = 1 A/μs, |       | ±90   |       | mV    |

| t <sub>tr</sub>  | Load transient recovery time                                              | see Note 1                                                                             |       | 100   |       | μs    |

| t <sub>r</sub>   | Ramp-up time<br>(from 10–90 % of V <sub>oi</sub> )                        | max I <sub>0</sub>                                                                     |       | 2.3   |       | ms    |

| t <sub>s</sub>   | Start-up time (from V <sub>i</sub> connection to 90% of V <sub>oi</sub> ) | max 1 <sub>0</sub>                                                                     |       | 6.3   |       | ms    |

| +                | Ramp-down time                                                            | Max I <sub>O</sub>                                                                     |       | 140   |       | μs    |

| t <sub>f</sub>   | (from 90–10 % of V <sub>oi</sub> )                                        | I <sub>O</sub> = 0.1 A                                                                 |       | 42.1  |       | ms    |

|                  | INHIBIT start-up time                                                     | Max I <sub>O</sub>                                                                     |       | 5.6   |       | ms    |

| t <sub>Inh</sub> | INHIBIT shutdown fall time                                                | Max I <sub>O</sub>                                                                     |       | 190   |       | μs    |

|                  | (From INHIBIT off to 10% of V <sub>o</sub> )                              | I <sub>O</sub> = 0.1 A                                                                 |       | 6.8   |       | ms    |

| Io               | Output current                                                            |                                                                                        | 0     |       | 50    | Α     |

| I <sub>lim</sub> | Current limit threshold                                                   | T <sub>ref</sub> < max T <sub>ref,</sub>                                               |       | 95    |       | Α     |

| V <sub>Oac</sub> | Output ripple & noise                                                     | See ripple & noise section, max I <sub>o</sub> , V <sub>oi</sub>                       |       | 15    |       | mVp-p |

Note 1: Output filter according to Ripple & Noise section

| PMM 8000 series PoL Regulators    | 2/ 28701- BMR 651 Rev. A | November 2017 |

|-----------------------------------|--------------------------|---------------|

| Input 8-14 V, Output 50 A / 275 W | © Flex                   |               |

## 1.8 V/50 A Typical Characteristics

#### **PMM 8218T**

#### **Efficiency**

#### **Power Dissipation**

#### **Output Current Derating**

| PMM 8000 series PoL Regulators    | 2/ 28701- BMR 651 Rev. A | November 2017 |

|-----------------------------------|--------------------------|---------------|

| Input 8-14 V, Output 50 A / 275 W | © Flex                   |               |

## 1.8 V/50 A Typical Characteristics

#### **PMM 8218T**

#### Start-up

Start-up enabled by connecting V<sub>I</sub> at:  $T_{ref} = +25^{\circ}C$ ,  $I_{O} = 50$  A resistive load,  $V_{I} = 12.0$  V.

Top trace: output voltage (1.0 V/div.). Bottom trace: input voltage (5 V/div.). Time scale: 20 ms/div.

#### Shut-down

Shut-down enabled by disconnecting V<sub>I</sub> at:  $T_{\rm ref} = +25\,^{\circ}\text{C}$ , I<sub>O</sub> = 50 A resistive load, V<sub>I</sub> = 12.0 V.

Top trace: output voltage (1.0 V/div.). Time scale: 1.0 ms/div.

#### **Output Ripple & Noise**

Output voltage ripple (20 mV/div.) at:  $T_{\text{ref}} = +25^{\circ}\text{C}$ ,  $I_{\text{o}} = 50$  A resistive load,  $V_{\text{i}} = 12.0$  V. Time scale: 2  $\mu\text{s}/\text{div}$ .

See the filter in the Output ripple and noise section (EMC Specification).

#### **Output Load Transient Response**

Output voltage response to load current step-change (25-50-25 A) at: Bottom trace: output voltage (100 mV/div.). Bottom trace: load current (20 A/div.).  $T_{ref} = +25^{\circ}\text{C}, \ V_i = 12.0 \ \text{V}.$  Time scale: 0.2 ms/div.

| PMM 8000 series PoL Regulators    | 2/ 28701- BMR 651 Rev. A | November 2017 |

|-----------------------------------|--------------------------|---------------|

| Input 8-14 V, Output 50 A / 275 W | © Flex                   |               |

#### 2.5 V/50 A Electrical Specification

**PMM 8218T**

$T_{ref}$  = -40 to +85°C,  $V_l$  = 8.0 to 14.0 V,  $R_{adj}$  = 3.01 kΩ, unless otherwise specified under Conditions. Typical values given at:  $T_{ref}$  = +25°C,  $V_l$ = 12.0 V, max  $I_O$ , unless otherwise specified under Conditions. Additional  $C_{in}$ = 1000μF and  $C_{out}$ = 660μF. See Operating Information section for selection of capacitor types. Connect the sense pin, where available, to the output pin.

| Charac           | teristics                                   | Conditions                           |                            | min   | typ   | max   | Unit |

|------------------|---------------------------------------------|--------------------------------------|----------------------------|-------|-------|-------|------|

| Vı               | Input voltage range                         |                                      |                            |       |       | 14.0  | V    |

| UVLO             | Undervoltage lockout                        | Pin 8 open                           | On-threshold               |       | 7.5   |       | V    |

| OVLO             | Ondervoltage lockout                        | Fill 6 Open                          | Hysterisis                 |       | 1     |       | V    |

| Cı               | Internal input capacitance                  |                                      |                            |       | 80    |       | μF   |

| Po               | Output power                                |                                      |                            | 0     |       | 125   | W    |

| n                | Efficiency                                  | 50 % of max I <sub>O</sub>           |                            |       | 93.0  |       | %    |

| ''               | Efficiency                                  | max I <sub>o</sub>                   |                            |       | 91.4  |       |      |

| P <sub>d</sub>   | Power Dissipation                           | max I <sub>o</sub>                   | max I <sub>O</sub>         |       | 11.7  |       | W    |

| P <sub>li</sub>  | Input idling power                          | $I_0 = 0, V_1 = 12.0 \text{ V}$      |                            |       | 1820  |       | mW   |

| P <sub>inh</sub> | Input standby power                         | $V_i = 12.0 \text{ V (turned)}$      | off with INHIBIT)          |       | 420   |       | mW   |

| Is               | Static Input current                        | $V_{I} = 12.0 \text{ V, max } I_{C}$ | )                          |       | 11.4  |       | Α    |

| f <sub>s</sub>   | Switching frequency                         | 0-100 % of max I <sub>0</sub>        |                            | 900   | 1050  | 1200  | kHz  |

|                  | ·                                           | •                                    |                            |       |       |       | •    |

| V <sub>Oi</sub>  | Output voltage initial setting and accuracy | $T_{ref} = +25^{\circ}C, V_{I} = 1$  | 12.0 V, max I <sub>0</sub> | 2.450 | 2.500 | 2.550 | V    |

| $V_{Oi}$         | Output voltage initial setting and accuracy                               | $T_{ref} = +25^{\circ}C$ , $V_{I} = 12.0 \text{ V, max } I_{O}$                        | 2.450 | 2.500 | 2.550 | V     |

|------------------|---------------------------------------------------------------------------|----------------------------------------------------------------------------------------|-------|-------|-------|-------|

|                  | Output voltage tolerance band                                             | 10-100 % of max I <sub>o</sub>                                                         | 2.425 |       | 2.575 | V     |

| \/               | Idling voltage                                                            | $I_{O} = 0$                                                                            |       | 2.500 |       | V     |

| Vo               | Line regulation                                                           | max I <sub>O</sub>                                                                     |       | ±5    |       | mV    |

|                  | Load regulation                                                           | $V_{I} = 12.0 \text{ V}, 0-100 \text{ % of max } I_{O}$                                |       | ±5    |       | mV    |

| $V_{tr}$         | Load transient voltage deviation                                          | V <sub>I</sub> = 12.0 V, Load step 50-100-50 % of max I <sub>O</sub> , di/dt = 1 A/μs, |       | ±95   |       | mV    |

| t <sub>tr</sub>  | Load transient recovery time                                              | see Note 1                                                                             |       | 100   |       | μs    |

| t <sub>r</sub>   | Ramp-up time<br>(from 10–90 % of V <sub>oi</sub> )                        | max I <sub>0</sub>                                                                     |       | 2.4   |       | ms    |

| t <sub>s</sub>   | Start-up time (from V <sub>i</sub> connection to 90% of V <sub>oi</sub> ) | 111ax 1 <sub>0</sub>                                                                   |       | 6.2   |       | ms    |

| +                | Ramp-down time                                                            | Max I <sub>O</sub>                                                                     |       | 150   |       | μs    |

| t <sub>f</sub>   | (from 90–10 % of V <sub>Oi</sub> )                                        | I <sub>O</sub> = 0.1 A                                                                 |       | 53.6  |       | ms    |

|                  | INHIBIT start-up time                                                     | Max I <sub>O</sub>                                                                     |       | 5.6   |       | ms    |

| t <sub>Inh</sub> | INHIBIT shutdown fall time                                                | Max I <sub>O</sub>                                                                     |       | 120   |       | μs    |

|                  | (From INHIBIT off to 10% of V <sub>o</sub> )                              | I <sub>O</sub> = 0.1 A                                                                 |       | 9.1   |       | ms    |

| Io               | Output current                                                            |                                                                                        | 0     |       | 50    | Α     |

| I <sub>lim</sub> | Current limit threshold                                                   | T <sub>ref</sub> < max T <sub>ref,</sub>                                               |       | 95    |       | Α     |

| V <sub>Oac</sub> | Output ripple & noise                                                     | See ripple & noise section, max I <sub>o</sub> , V <sub>oi</sub>                       |       | 15    |       | mVp-p |

Note 1: Output filter according to Ripple & Noise section

| PMM 8000 series PoL Regulators    | 2/ 28701- BMR 651 Rev. A | November 2017 |

|-----------------------------------|--------------------------|---------------|

| Input 8-14 V, Output 50 A / 275 W | © Flex                   |               |

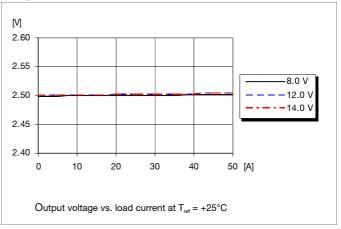

## 2.5 V/50 A Typical Characteristics

#### **PMM 8218T**

#### **Efficiency**

#### **Power Dissipation**

#### **Output Current Derating**

| PMM 8000 series PoL Regulators    | 2/ 28701- BMR 651 Rev. A | November 2017 |

|-----------------------------------|--------------------------|---------------|

| Input 8-14 V, Output 50 A / 275 W | © Flex                   |               |

## 2.5 V/50 A Typical Characteristics

#### **PMM 8218T**

#### Start-up

Start-up enabled by connecting V<sub>I</sub> at:  $T_{ref} = +25^{\circ}C$ ,  $I_{O} = 50$  A resistive load,  $V_{I} = 12.0$  V.

Top trace: output voltage (2.0 V/div.). Bottom trace: input voltage (5 V/div.). Time scale: 20 ms/div.

#### Shut-down

Shut-down enabled by disconnecting V<sub>I</sub> at:  $T_{\rm ref} = +25\,^{\circ}\text{C}$ , I<sub>O</sub> = 50 A resistive load, V<sub>I</sub> = 12.0 V.

Top trace: output voltage (1.0 V/div.). Time scale: 1.0 ms/div.

#### **Output Ripple & Noise**

Output voltage ripple (20 mV/div.) at:  $T_{\text{ref}} = +25^{\circ}\text{C}$ ,  $I_{\text{o}} = 50$  A resistive load,  $V_{\text{i}} = 12.0$  V. Time scale: 2  $\mu\text{s}/\text{div}$ .

See the filter in the Output ripple and noise section (EMC Specification).

#### **Output Load Transient Response**

Output voltage response to load current step-change (25-50-25 A) at: Bottom trace: output voltage (100 mV/div.). Bottom trace: load current (20 A/div.).  $T_{ref} = +25^{\circ}\text{C}, \ V_i = 12.0 \ \text{V}.$  Time scale: 0.2 ms/div.

| PMM 8000 series PoL Regulators    | 2/ 28701- BMR 651 Rev. A | November 2017 |

|-----------------------------------|--------------------------|---------------|

| Input 8-14 V, Output 50 A / 275 W | © Flex                   |               |

## 3.3 V/50 A Electrical Specification

**PMM 8218T**

$T_{ref}$  = -40 to +85°C,  $V_{I}$  = 8.0 to 14.0 V,  $R_{adj}$  = 1.50 kΩ, unless otherwise specified under Conditions. Typical values given at:  $T_{ref}$  = +25°C,  $V_{I}$  = 12.0 V, max  $I_{O}$ , unless otherwise specified under Conditions. Additional  $C_{in}$ = 1000μF and  $C_{out}$ = 660μF. See Operating Information section for selection of capacitor types. Connect the sense pin, where available, to the output pin.

| Charac           | teristics                                   | Conditions                        |                            | min   | typ   | max   | Unit |  |

|------------------|---------------------------------------------|-----------------------------------|----------------------------|-------|-------|-------|------|--|

| V <sub>I</sub>   | Input voltage range                         |                                   |                            | 8.0   |       | 14.0  | V    |  |

| UVLO             | Undervoltage lockout                        | Pin 8 open                        | On-threshold               |       | 7.5   |       | V    |  |

| UVLO             | Ondervoltage lockout                        | Fill 6 Open                       | Hysterisis                 |       | 1     |       | •    |  |

| Cı               | Internal input capacitance                  |                                   |                            |       | 80    |       | μF   |  |

| Po               | Output power                                |                                   |                            | 0     |       | 165   | W    |  |

| n                | Efficiency                                  | 50 % of max I <sub>O</sub>        |                            |       | 94.3  |       | %    |  |

| η                | Eniciency                                   | max I <sub>O</sub>                |                            |       | 93.0  |       | 70   |  |

| $P_d$            | Power Dissipation                           | max I <sub>O</sub>                | max I <sub>o</sub>         |       | 12.4  |       | W    |  |

| P <sub>li</sub>  | Input idling power                          | $I_0 = 0, V_1 = 12.0 \text{ V}$   |                            |       | 2070  |       | mW   |  |

| P <sub>inh</sub> | Input standby power                         | V <sub>I</sub> = 12.0 V (turned   | d off with INHIBIT)        |       | 420   |       | mW   |  |

| ls               | Static Input current                        | V <sub>I</sub> = 12.0 V, max I    | 0                          |       | 14.9  |       | А    |  |

| f <sub>s</sub>   | Switching frequency                         | 0-100 % of max I                  | 0                          | 900   | 1050  | 1200  | kHz  |  |

|                  |                                             |                                   |                            |       |       |       |      |  |

| $V_{Oi}$         | Output voltage initial setting and accuracy | $T_{ref} = +25^{\circ}C, V_{I} =$ | 12.0 V, max I <sub>0</sub> | 3.234 | 3.300 | 3.366 | V    |  |

|                  | Output voltage tolerance band               | 10-100 % of max                   | Io                         | 3.201 |       | 3.399 | V    |  |

| $V_{Oi}$         | Output voltage initial setting and accuracy                               | $T_{ref} = +25^{\circ}C$ , $V_{I} = 12.0 \text{ V, max } I_{O}$                        | 3.234 | 3.300 | 3.366 | V     |

|------------------|---------------------------------------------------------------------------|----------------------------------------------------------------------------------------|-------|-------|-------|-------|

|                  | Output voltage tolerance band                                             | 10-100 % of max I <sub>o</sub>                                                         | 3.201 |       | 3.399 | V     |

| \/               | Idling voltage                                                            | $I_{O} = 0$                                                                            |       | 3.305 |       | V     |

| Vo               | Line regulation                                                           | max I <sub>O</sub>                                                                     |       | ±5    |       | mV    |

|                  | Load regulation                                                           | $V_{I} = 12.0 \text{ V}, 0-100 \text{ % of max } I_{O}$                                |       | ±5    |       | mV    |

| $V_{tr}$         | Load transient voltage deviation                                          | V <sub>I</sub> = 12.0 V, Load step 50-100-50 % of max I <sub>O</sub> , di/dt = 1 A/μs, |       |       |       | mV    |

| t <sub>tr</sub>  | Load transient recovery time                                              | see Note 1                                                                             |       | 150   |       | μs    |

| t <sub>r</sub>   | Ramp-up time<br>(from 10–90 % of V <sub>oi</sub> )                        | max I <sub>0</sub>                                                                     |       | 2.3   |       | ms    |

| t <sub>s</sub>   | Start-up time (from V <sub>i</sub> connection to 90% of V <sub>oi</sub> ) | 111dX 1 <sub>0</sub>                                                                   |       | 6.3   |       | ms    |

| +                | Ramp-down time                                                            | Max I <sub>O</sub>                                                                     |       | 200   |       | μs    |

| t <sub>f</sub>   | (from 90–10 % of V <sub>oi</sub> )                                        | I <sub>O</sub> = 0.1 A                                                                 |       | 66.5  |       | ms    |

|                  | INHIBIT start-up time                                                     | Max I <sub>O</sub>                                                                     |       | 5.6   |       | ms    |

| t <sub>Inh</sub> | INHIBIT shutdown fall time                                                | Max I <sub>O</sub>                                                                     |       | 130   |       | μs    |

|                  | (From INHIBIT off to 10% of V <sub>o</sub> )                              | I <sub>O</sub> = 0.1 A                                                                 |       | 11.7  |       | ms    |

| Io               | Output current                                                            |                                                                                        | 0     |       | 50    | Α     |

| I <sub>lim</sub> | Current limit threshold                                                   | T <sub>ref</sub> < max T <sub>ref,</sub>                                               |       | 95    |       | Α     |

| V <sub>Oac</sub> | Output ripple & noise                                                     | See ripple & noise section, max I <sub>o</sub> , V <sub>oi</sub>                       |       | 15    |       | mVp-p |

Note 1: Output filter according to Ripple & Noise section

| PMM 8000 series PoL Regulators    | 2/ 28701- BMR 651 Rev. A | November 2017 |

|-----------------------------------|--------------------------|---------------|

| Input 8-14 V, Output 50 A / 275 W | © Flex                   |               |

## 3.3 V/50 A Typical Characteristics

#### **PMM 8218T**

#### **Efficiency**

#### **Power Dissipation**

#### **Output Current Derating**

| PMM 8000 series PoL Regulators    | 2/ 28701- BMR 651 Rev. A | November 2017 |

|-----------------------------------|--------------------------|---------------|

| Input 8-14 V, Output 50 A / 275 W | © Flex                   |               |

## 3.3 V/50 A Typical Characteristics

#### **PMM 8218T**

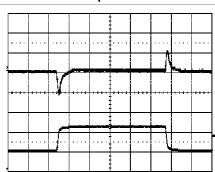

#### Start-up

Start-up enabled by connecting V<sub>I</sub> at:  $T_{ref} = +25^{\circ}C$ ,  $I_{O} = 50$  A resistive load,  $V_{I} = 12.0$  V.

Top trace: output voltage (2.0 V/div.). Bottom trace: input voltage (5 V/div.). Time scale: 20 ms/div.

#### Shut-down

Shut-down enabled by disconnecting V<sub>I</sub> at:  $T_{\rm ref} = +25\,^{\circ}\text{C}$ , I<sub>O</sub> = 50 A resistive load, V<sub>I</sub> = 12.0 V.

Top trace: output voltage (2.0 V/div.). Time scale: 1.0 ms/div.

#### **Output Ripple & Noise**

Output voltage ripple (20 mV/div.) at:  $T_{\text{ref}} = +25^{\circ}\text{C}$ ,  $I_{\text{o}} = 50$  A resistive load,  $V_{\text{i}} = 12.0$  V. Time scale: 2  $\mu\text{s}/\text{div}$ .

See the filter in the Output ripple and noise section (EMC Specification).

#### **Output Load Transient Response**

Output voltage response to load current step-change (25-50-25 A) at: Bottom trace: output voltage (100 mV/div.). Bottom trace: load current (20 A/div.).  $T_{ref} = +25^{\circ}\text{C}, \ V_i = 12.0 \ \text{V}.$  Time scale: 0.2 ms/div.

| PMM 8000 series PoL Regulators    | 2/ 28701- BMR 651 Rev. A | November 2017 |

|-----------------------------------|--------------------------|---------------|

| Input 8-14 V, Output 50 A / 275 W | © Flex                   |               |

#### 5.0 V/50 A Electrical Specification

**PMM 8218T**

$T_{ref}$  = -40 to +85°C,  $V_l$  = 8.0 to 14.0 V,  $R_{adj}$  = 205  $\Omega$ , unless otherwise specified under Conditions. Typical values given at:  $T_{ref}$  = +25°C,  $V_l$ = 12.0 V, max  $I_O$ , unless otherwise specified under Conditions. Additional  $C_{in}$ = 1000μF and  $C_{out}$ = 660μF. See Operating Information section for selection of capacitor types. Connect the sense pin, where available, to the output pin.

| Characteristics  |                            | Conditions                                        | Conditions                 |     | typ  | max  | Unit |

|------------------|----------------------------|---------------------------------------------------|----------------------------|-----|------|------|------|

| Vı               | Input voltage range        |                                                   |                            | 8.0 |      | 14.0 | V    |

| UVLO             | Undervoltage lockout       | Pin 8 open                                        | On-threshold               |     | 7.5  |      | V    |

| UVLO             | Undervoltage lockout       | Fill 6 Open                                       | Hysterisis                 |     | 1    | •    | V    |

| Cı               | Internal input capacitance |                                                   |                            |     | 80   |      | μF   |

| Po               | Output power               |                                                   |                            | 0   |      | 250  | W    |

| n                | Efficiency                 | 50 % of max I <sub>o</sub>                        | 50 % of max I <sub>0</sub> |     | 95.7 |      | %    |

| η                |                            | max I <sub>O</sub>                                | max I <sub>o</sub>         |     | 94.8 |      |      |

| P <sub>d</sub>   | Power Dissipation          | max I <sub>o</sub>                                |                            |     | 13.9 |      | W    |

| P <sub>li</sub>  | Input idling power         | $I_0 = 0, V_1 = 12.0 V$                           |                            |     | 2510 |      | mW   |

| P <sub>inh</sub> | Input standby power        | V <sub>I</sub> = 12.0 V (turned off with INHIBIT) |                            |     | 420  |      | mW   |

| Is               | Static Input current       | V <sub>I</sub> = 12.0 V, max I <sub>O</sub>       |                            |     | 22.1 |      | Α    |

| f <sub>s</sub>   | Switching frequency        | 0-100 % of max                                    | l <sub>o</sub>             | 900 | 1050 | 1200 | kHz  |

| $V_{Oi}$                              | Output voltage initial setting and accuracy                              | $T_{ref} = +25^{\circ}C, V_{I} = 12.0 \text{ V, max } I_{O}$                             | 4.900 | 5.000 | 5.100 | V     |

|---------------------------------------|--------------------------------------------------------------------------|------------------------------------------------------------------------------------------|-------|-------|-------|-------|

|                                       | Output voltage tolerance band                                            | 10-100 % of max I <sub>o</sub>                                                           | 4.850 |       | 5.150 | V     |

| \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ | Idling voltage                                                           | I <sub>O</sub> = 0                                                                       |       | 5.018 |       | V     |

| Vo                                    | Line regulation                                                          | max I <sub>O</sub>                                                                       |       | ±5    |       | mV    |

|                                       | Load regulation                                                          | V <sub>I</sub> = 12.0 V, 0-100 % of max I <sub>O</sub>                                   |       | ±5    |       | mV    |

| V <sub>tr</sub>                       | Load transient voltage deviation                                         | V <sub>I</sub> = 12.0 V, Load step 50-100-50 % of max I <sub>O</sub> , di/dt = 1 A/ μ s, |       | ±140  |       | mV    |

| t <sub>tr</sub>                       | Load transient recovery time                                             | see Note 1                                                                               |       | 150   |       | μs    |

| t <sub>r</sub>                        | Ramp-up time<br>(from 10–90 % of V <sub>oi</sub> )                       | max I <sub>0</sub>                                                                       |       | 2.4   |       | ms    |

| t <sub>s</sub>                        | Start-up time (from V <sub>i</sub> connection to 90% of V <sub>o</sub> ) | 111ax 1 <sub>0</sub>                                                                     |       | 6.3   |       | ms    |

| +                                     | Ramp-down time                                                           | Max I <sub>O</sub>                                                                       |       | 260   |       | μs    |

| t <sub>f</sub>                        | (from 90–10 % of V <sub>oi</sub> )                                       | I <sub>O</sub> = 0.1 A                                                                   |       | 91.9  |       | ms    |

|                                       | INHIBIT start-up time                                                    | Max I <sub>O</sub>                                                                       |       | 5.6   |       | ms    |

| t <sub>Inh</sub>                      | INHIBIT shutdown fall time                                               | Max I <sub>O</sub>                                                                       |       | 220   |       | μs    |

|                                       | (From INHIBIT off to 10% of $V_0$ )                                      | I <sub>O</sub> = 0.1 A                                                                   |       | 16.7  |       | ms    |

| Io                                    | Output current                                                           |                                                                                          | 0     |       | 50    | Α     |

| I <sub>lim</sub>                      | Current limit threshold                                                  | T <sub>ref</sub> < max T <sub>ref,</sub>                                                 |       | 95    |       | Α     |

| V <sub>Oac</sub>                      | Output ripple & noise                                                    | See ripple & noise section, max I <sub>o</sub> , V <sub>oi</sub>                         |       | 15    |       | mVp-p |

Note 1: Output filter according to Ripple & Noise section

| PMM 8000 series PoL Regulators    | 2/ 28701- BMR 651 Rev. A | November 2017 |

|-----------------------------------|--------------------------|---------------|

| Input 8-14 V, Output 50 A / 275 W | © Flex                   |               |

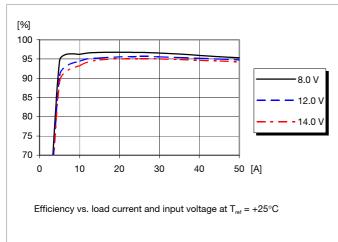

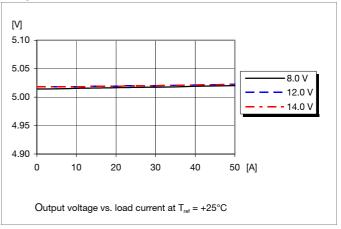

## 5.0 V/50 A Typical Characteristics

#### **PMM 8218T**

## **Efficiency**

#### **Power Dissipation**

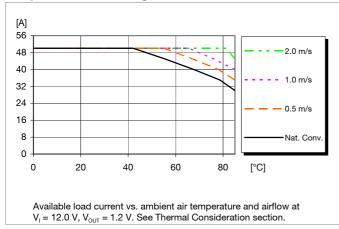

#### **Output Current Derating**

| PMM 8000 series PoL Regulators    | 2/ 28701- BMR 651 Rev. A | November 2017 |

|-----------------------------------|--------------------------|---------------|

| Input 8-14 V, Output 50 A / 275 W | © Flex                   |               |

## 5.0 V/50 A Typical Characteristics

#### **PMM 8218T**

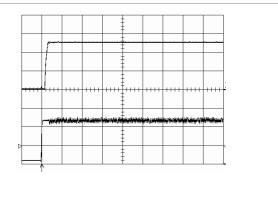

#### Start-up

Start-up enabled by connecting V<sub>I</sub> at:  $T_{ref} = +25^{\circ}C$ ,  $I_{O} = 50$  A resistive load,  $V_{I} = 12.0$  V.

Top trace: output voltage (2.0 V/div.). Bottom trace: input voltage (5 V/div.). Time scale: 20 ms/div.

#### Shut-down

Shut-down enabled by disconnecting V<sub>I</sub> at:  $T_{\rm ref} = +25\,^{\circ}\text{C}$ , I<sub>O</sub> = 50 A resistive load, V<sub>I</sub> = 12.0 V.

Top trace: output voltage (2.0 V/div.). Time scale: 1.0 ms/div.

#### **Output Ripple & Noise**

Output voltage ripple (20 mV/div.) at:  $T_{\text{ref}} = +25^{\circ}\text{C}$ ,  $I_{\text{o}} = 50$  A resistive load,  $V_{\text{i}} = 12.0$  V. Time scale: 2  $\mu\text{s}/\text{div}$ .

See the filter in the Output ripple and noise section (EMC Specification).

#### **Output Load Transient Response**

Output voltage response to load current step-change (25-50-25 A) at: Bottom trace: output voltage (100 mV/div.). Bottom trace: load current (20 A/div.).  $T_{ref} = +25^{\circ}\text{C}, \ V_i = 12.0 \ \text{V}.$  Time scale: 0.2 ms/div.

| PMM 8000 series PoL Regulators    | 2/ 28701- BMR 651 Rev. A | November 2017 |

|-----------------------------------|--------------------------|---------------|

| Input 8-14 V, Output 50 A / 275 W | © Flex                   |               |

#### **EMC Specification**

Conducted EMI measured according to test set-up. The fundamental switching frequency is 1050 kHz for PMM 8218T @  $V_I$  = 12 V, max  $I_O$ .

Conducted EMI Input terminal value (typ)

EMI without filter

Test set-up

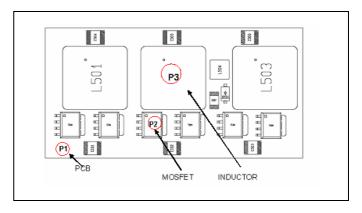

#### Layout recommendation

The radiated EMI performance of the POL regulator will depend on the PCB layout and ground layer design. It is also important to consider the stand-off of the POL regulator.

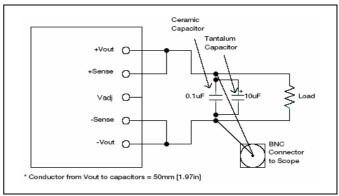

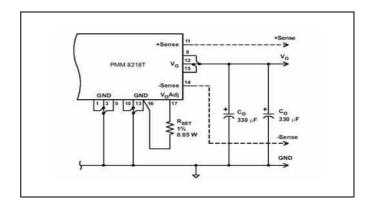

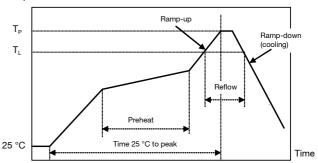

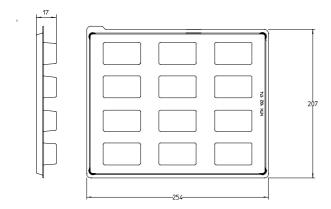

If a ground layer is used, it should be connected to the output of the POL regulator and the equipment ground or chassis.