IA700

# Ultra-Low Power Audio Edge Processor

The IA700 is an AiSonic<sup>TM</sup> Ultra-Low Power Audio Edge Processor featuring Voice Wake and Voice ID keyword detectors and a two-second buffer<sup>1</sup> in a 24-pin QFN package. The IA700 offers flexibility by supporting the most relevant audio and data interfaces. The Audio DSP with 248 Kbytes of RAM is available for customer and third party algorithms, enabling unlimited creativity. The solution pushes system performance to ultra-low power with its custom core design and accelerates time to market with its highly integrated combination of hardware, software, and firmware.

#### **Product Features**

- Audio optimized Xtensa 64-bit two-way floating-point Single Instruction Multiple Data (SIMD) DSP core.

- 64 KB on-chip ROM.

- 248 KB on-chip RAM that includes at least 168 KB of user accessible memory for code and data.

- A TDM/I2S Master/Slave port.

# **Typical Applications**

- Remote controls

- Smart home devices

- Headsets and true wireless earbuds

- Near field voice activated controls

- Up to two digital microphone (PDM) input channels and a stereo PDM output.

- Machine learning capability and Tensor Flow Lite (TFLu) support.

- Increased flexibility with I2C/UART/SPI interfaces.

- 24-pin QFN, 0.4mm pitch, 3.5 x 3.5 x 0.75 mm.

- Internet of Things (IoT) Devices

- Edge ML processor

<sup>&</sup>lt;sup>1</sup> Buffer size varies based on the use-case and algorithm.

# **Specification Summary**

### **Absolute Maximum Ratings**

| Parameter               | Absolute Maximum Ratings | Units |

|-------------------------|--------------------------|-------|

| VDD_IO to Ground        | -0.3, +3.3               | V     |

| VDD_LDOD/A to Ground    | -0.3, +1.5               | V     |

| Digital Input to Ground | -0.3, VDD_IO+0.3         | V     |

| Input Current (any pin) | ±5                       | mA    |

| Storage Temperature     | -55 to +150              | ōС    |

Note: Stresses exceeding these Absolute Maximum Ratings can cause permanent damage to the device. These are stress ratings only.

Functional operation at these or any other conditions beyond those indicated under Specifications and Electrical Characteristics is not implied.

Exposure beyond those indicated under Specifications and Electrical Characteristics for extended periods can affect device reliability.

### **Specifications**

Test Conditions: VDD\_IO = 1.8V, VDD\_LDOD/A = 1.1V at TA =25 °C, PDM + SPI mode, 3.072 MHz clock, unless otherwise specified.

| Parameter                             | Symbol         | Conditions                                     | Min  | Typical | Max  | Units |

|---------------------------------------|----------------|------------------------------------------------|------|---------|------|-------|

|                                       | VDD_IO         | -                                              | 1.71 | 1.8     | 1.98 | V     |

| Supply Voltage                        | VDD_LDOD       | -                                              | 1.05 | 1.1     | 1.15 | V     |

|                                       | VDD_LDOA       | -                                              | 1.05 | 1.1     | 1.15 | V     |

|                                       |                | Retention Sleep<br>Mode                        | -    | TBD     | -    |       |

|                                       |                | Voice Wake AAD<br>Mode (stage 0)               | -    | TBD     | -    |       |

| Supply Current                        | -              | Voice Wake<br>Keyword Detect<br>Mode (stage 1) | -    | TBD     | -    | -     |

|                                       |                | Voice Wake<br>Burst Mode<br>(stage 2)          | -    | TBD     | -    |       |

| Operational<br>Ambient<br>Temperature | T <sub>A</sub> | -                                              | -20  | 25      | 85   | ōC    |

# Table of Contents

| Chapter 1: | Product Description                      | 5        |

|------------|------------------------------------------|----------|

|            | 1.1 Overview                             | 5        |

|            | 1.2 Key Features                         | 5        |

|            | 1.3 AuViD Firmware Build Tool            | <i>6</i> |

|            | 1.4 Typical Application Block Diagrams   | 6        |

| Chapter 2: | Chip Description                         | g        |

|            | 2.1 DSP Subsystem                        | 10       |

|            | 2.1.1 Hemi Delta Processor               | 10       |

|            | 2.1.2 Digital Filters                    |          |

|            | 2.1.3 Audio Fabric                       |          |

|            | 2.1.5 Memory<br>2.1.6 Audio Interfaces   |          |

|            | 2.1.7 Host Interfaces                    |          |

|            | 2.2 Control Subsystem                    |          |

|            | 2.2.1 Boot Control                       |          |

|            | 2.2.2 Reset Control                      | 14       |

|            | 2.2.4 Power Management                   |          |

|            | 2.3 Clock Subsystem                      |          |

|            | 2.3.1 CLK_IN                             |          |

|            | 2.3.2 PLL2.3.3 Internal Oscillators      |          |

|            | 2.4 Interrupts                           |          |

| Charter 2  |                                          |          |

| Chapter 3: | Operating Modes                          |          |

|            | 3.2 OpenDSP                              |          |

|            | 3.3 Software Pass-Through                |          |

|            | 3.4 Hardware Pass-Through                |          |

|            | 3.5 Retention Sleep/Use Case Sleep Mode  |          |

|            | 3.3 Retention Sleep/ Ose case sleep Mode | 10       |

| Chapter 4: | Design Considerations                    | 17       |

|            | 4.1 Latch-On Reset Configuration Pins    | 17       |

|            | 4.1.1 Boot clock selection               |          |

|            | 4.1.2 I2C Address Pins                   |          |

|            | 4.2 Start-Up Sequencing                  |          |

|            | 4.3 Sleep and Wake-up Sequence           |          |

|            | 4.4 State Diagram                        | 19       |

| Chapter 5: | Pin Descriptions                         | 20       |

|            | 5.1 Pinout Diagram                       | 20       |

|            | 5.3 Pinout Table                         | 21       |

| Chapter 6: | Electrical Characteristics                                                                       | 22 |

|------------|--------------------------------------------------------------------------------------------------|----|

| _          | 6.1 General Electrical Characteristics                                                           | 22 |

|            | 6.2 PLL Characteristics                                                                          | 22 |

|            | 6.3 Oscillator Characteristics                                                                   | 23 |

|            | 6.4 Audio Port Interface Characteristics                                                         | 23 |

|            | 6.4.1 I <sup>2</sup> S/TDM Interface Slave Timing                                                |    |

|            | 6.4.3 I <sup>2</sup> S/TDM Interface Master Timing6.4.4 Audio Port PDM Interface Characteristics |    |

|            | 6.5 I <sup>2</sup> C Slave Interface Characteristics                                             | 25 |

|            | 6.6 SPI Interface Specifications                                                                 | 25 |

| Chapter 7: | PCB Design and Layout Guidelines                                                                 | 27 |

|            | 7.1 Power Planes                                                                                 | 27 |

|            | 7.2 Digital Signal Routing                                                                       | 27 |

| Chapter 8: | Mechanical Specifications                                                                        | 28 |

|            | 8.1 IA700CQ QFN24 Package Dimension                                                              | 28 |

| Chapter 9: | Packaging and Marking Details                                                                    | 29 |

|            | 9.1 Reel                                                                                         | 29 |

|            | 9.2 Tape                                                                                         | 29 |

|            | 9.3 Packing Details                                                                              | 30 |

| Chapter 10 | : Recommended Reflow Profile                                                                     | 32 |

|            | 10.1 Additional Notes                                                                            | 32 |

# **Chapter 1: Product Description**

#### 1.1 Overview

The Knowles IA700 Audio Edge Processor is a flexible, ultra-low power, and highly integrated voice and audio processor for battery-powered applications. The IA700 includes the following:

- An advanced, Knowles audio-optimized DSP subsystem that:

- Runs compute-intensive audio processing algorithms with very low power consumption

- Provides an efficient interface between custom software and the digital audio stream data.

- A System Control Unit (SCU) that handles booting, resetting, and power management states such as deep-sleep mode, stage 0 and stage 1 Voice Wake activity.

- A flexible internal clock generation and routing system.

- Integrated interfaces for PDM and I<sup>2</sup>S/TDM digital audio data.

- A variety of control interfaces, including UART, SPI slave, or I<sup>2</sup>C slave. All have a control messaging and audio streaming capability.

Optimize IA700 for low power operation in a wide array of applications, including IoT devices.

The IA700 includes a set of reference drivers for common operating systems and platforms, allowing for easy integration and quick time-to-market. It allows communication/data transmission through the system interfaces listed in Table 1.

| Table 1 | System | <b>Interfaces</b> |

|---------|--------|-------------------|

|         |        |                   |

| Control<br>Messages | Audio Ports | Audio Upload |

|---------------------|-------------|--------------|

| I2C                 | I2S         | I2S          |

| UART                | I2S         | I2S          |

| SPI                 | PDM         | SPI          |

| UART                | PDM         | UART         |

| I2C                 | PDM         | I2C          |

Note: A user can only use one control interface at a time. For more information, see Chapter 5:.

# 1.2 Key Features

- Voice Wake

- Ultra-low power.

- Always listening in keyword detection mode.

- Detection of either programmed (OEM) or user-trained keyword (Voice ID).

- Continuous Voice Wake (CVQ) for a seamless transition from Voice Wake to the command phrase that follows.

- SPI Slave interface for fast code download and control.

- OpenDSP (ODSP): Low power operation, DSP clock rate up to 100 MHz, 248 kB total on-chip RAM, 168 kB RAM available for algorithms.

- Support for up to two PDM microphones for dual-mic processing such as beamforming.

### 1.3 AuViD Firmware Build Tool

Knowles offers AuViD, a comprehensive tool for firmware development and testing, as well as IA700 system configuration.

Engineers can use AuViD to configure, debug, and design. The system capabilities include audio streaming, system and route configuration; which performs either of the following:

- Offline sysconfig configuration and audio stream decoding.

- Connected to the host directly for run-time debugging using a host interface (I2C, UART, or SPI)

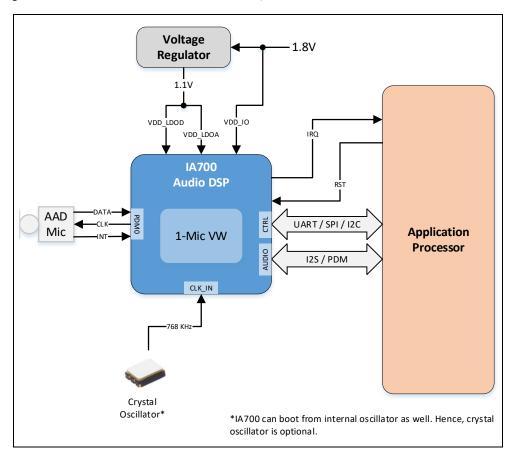

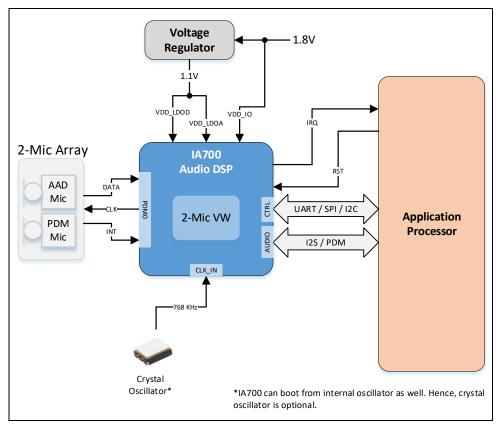

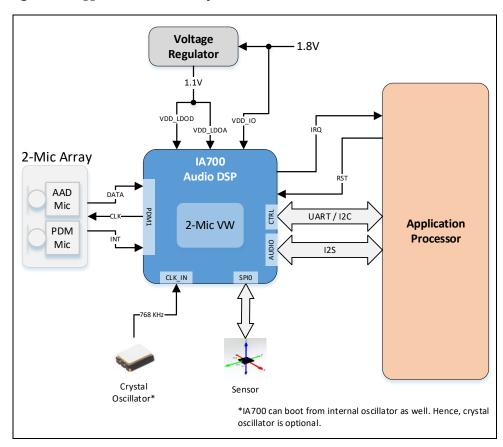

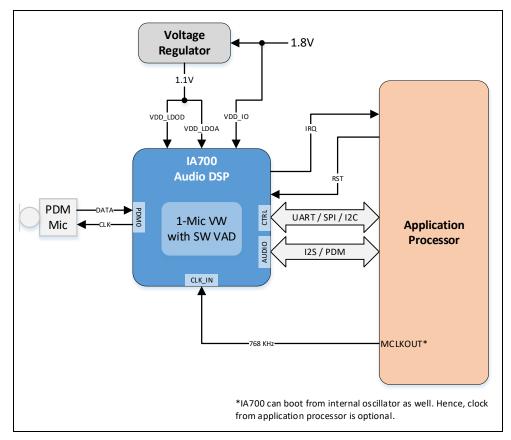

# 1.4 Typical Application Block Diagrams

Figure 1 and Figure 2 shows typical block diagrams for a host system using the IA700. (For pin configuration per boot mode, see Table 9 and Table 1.)

Figure 1 Application Schematic for a 1-mic Voice Wake with HW AAD (e.g. Remote Control)

Figure 2 Application Schematic for a 2-mic Voice Wake with HW AAD

Figure 3 Application Schematic for a 2-mic Voice Wake with a Sensor

Figure 4 Application Schematic for a 1-mic Voice Wake with SW VAD, CLK\_IN from AP

# Chapter 2: Chip Description

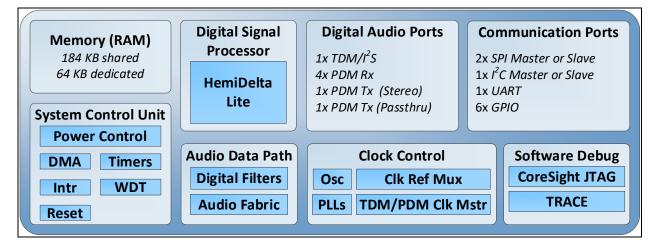

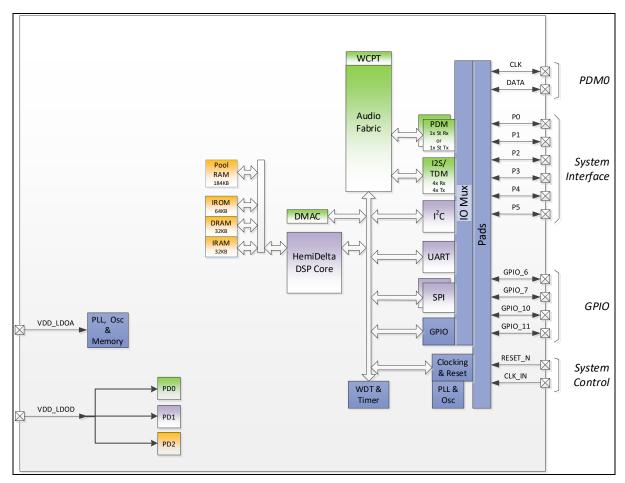

The following are the major modules of the IA700 as shown in Figure 5:

- Ultra-low power and high-performance DSP sub-system.

- A Digital Audio Interface module that provides configurable serial digital audio ports capable of streaming a wide variety of data formats such as PDM, I2S, or TDM.

- SPI, UART, and I<sup>2</sup>C Host Interfaces that includes:

- Communication with the host.

- A channel for high-speed firmware downloads.

- Audio data bursting for Voice Wake or diagnostic purposes.

- The System Control Unit (SCU) that handles booting, resetting, and power management states such as deep-sleep mode.

- An internal clock control module that generates internal clock signals and masters output clocks; it also locks internal time bases to externally provided clocks.

- System interrupt module, which provides:

- Interrupt to host for keyword detection events.

- Event handling to IA700 for host wakeup.

Figure 5 IA700 Block Diagram

### 2.1 DSP Subsystem

The DSP subsystem consists of the following:

- 1. A Hemi Delta (HMD) processor

- 2. Digital filter

- 3. Audio fabric

- 4. Memory

#### 2.1.1 Hemi Delta Processor

The HMD is a low power DSP with frame-based processing capabilities, and includes the following features:

- 64-bit instruction memory access (maximum instruction size is 64 bits).

- 64-bit data memory access (maximum register width is 64 bits).

- Main data type: 32-bit float (AFLOAT).

- Main vector register file: 16 vector registers (two 32-bit lanes each).

- Permutation registers to support load/store, permute, and arithmetic instructions.

- Dual issue instruction bundles.

- Vector and scalar instructions.

- Four MACs (real and complex arithmetic support).

- Nonlinear functions: arc tangent, cosine, sine, log, exponential, inverse, inverse square root, and sigmoid (exponential approximation).

- Added acceleration

- FFT

- Peak finding

- DNNs (eight 8-bit x 8-bit fixed-point MACs)

- TFLu (Tensor flow light for Microcontroller)

### 2.1.2 Digital Filters

The IA700 digital filters allow the use of Pulse Density Modulation (PDM) audio data. There are four receive decimation filter chains, and two transmit interpolation filter chains. The decimation filters support one-bit PDM input oversampled audio data from digital microphones and codec interfaces. The interpolation filters generate oversampled one-bit PDM output audio data that routes to a speaker or codec.

#### 2.1.3 Audio Fabric

The Audio Fabric is a memory-mapped interface that allows the processor to access data efficiently from the various audio interfaces supported by the chip, such as I<sup>2</sup>S/TDM, or PDM. Each audio interface converts input data into a common 32-bit integer format that synchronizes into the processor clock domain from the native audio clock before multiplexing into generic N-channel logical streams of audio data in the Audio Fabric. Similarly, each audio interface can convert 32-bit integer format data into the encoding required for transmission. The audio fabric supports a low-latency path and connects to the wall clock/presentation timer's unit to capture timestamps of audio data.

#### 2.1.5 Memory

The IA700 has 248 kB of RAM, which is divided as following:

- 32 kB dedicated IRAM.

- 32 kB dedicated DRAM.

- 184 kB memory pool, consisting of five 32 kB blocks, one 16 kB block, and one 8 kB block.

- 168 kB of the total 248 kB memory is reserved for custom algorithm use.

Figure 6 Memory Pool Structure

#### 2.1.6 Audio Interfaces

The IA700 audio processor supports the following audio data transfers:

- Four PDM input channels

- Two PDM output channels

- Master/Slave I2S/TDM

### 2.1.6.1 Digital Microphone PDM Input Interface

The user can configure IA700 to support Pulse Density Modulation (PDM) digital microphone interface to receive audio data from external PDM microphone(s). Depending on the configuration, IA700 can be either a PDM Master or a PDM Slave.

- PDM Master IA700 generates PDM clock by internal audio PLL.

- PDM Slave IA700 receives PDM clock by external codec or other source.

The user can configure PDM\_CLK signal either as input or as output; it supports up to 4.8 MHz frequencies.

The IA700 can support up to two digital microphones in a stereo configuration.

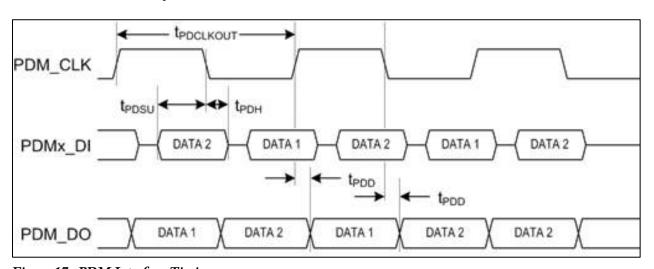

The dual channel PDM carries encoded data, therefore, the IA700 PDMx\_DI input clocks the left channel data at the falling edge of PDM\_CLK and the right channel data at the rising edge of PDM\_CLK. After driving the data input signal (PDMx\_DI) high or low in the appropriate half frame of the PDM\_CLK signal, the input device must tristate the signal. In this way, two microphones, one set to the left channel and the other to the right, can drive a single DATA line.

### 2.1.6.2 Digital Microphone PDM Output Interface

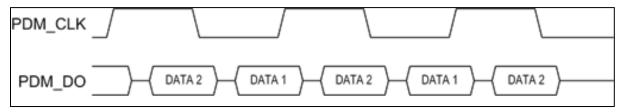

The IA700 has a single PDM output signal used to transmit two audio channels. Each clock edge transmits data for one of the two audio channels, as shown in Figure 7. The clock can be set to input (slave) or output (master) in PDM output mode. Table 2 lists the supported frequency ranges, if the user programs frequency ranges as an input. When the clock is set to output, the default output frequency is 3.072 MHz. For more information on flexibility of using PDM clock as an output, see *IA700 API Guide*.

Figure 7 PDM Two-Channel Output Timing

Table 2 Supported PDM Clock Rates

| PDM Clock (KHz) | Recommended Max<br>Bandwidth of Audio<br>Signal (KHz) |

|-----------------|-------------------------------------------------------|

| 512             | 8                                                     |

| 768             | 8                                                     |

| 1024            | 10.66                                                 |

| 1536            | 16                                                    |

| 2048            | 21.33                                                 |

| 2400            | 25                                                    |

| 3072            | 32                                                    |

| 4608            | 48                                                    |

| 4800            | 50                                                    |

### 2.1.6.3 I<sup>2</sup>S/TDM Digital Audio Port

When in  $I^2S + I^2C$  or  $I^2S + UART$  mode, the IA700 can transfer audio data through  $I^2S$  or TDM protocol with an external host or codec device. (Table 9 and Table 1 lists the pin configuration in these modes.) The user can configure IA700 to operate either in slave or master mode using API commands.

I<sup>2</sup>S transfers have the following features.

- Bit clock (I2S\_CLK) up to 24.576 MHz.

- Sampling clock (I2S\_WS) up to 192 KHz.

- There must be exactly two slots, Left (I2S\_WS low) and Right (I2S\_WS high).

- There must be an equal number of I2S\_CLK periods in each half I2S\_WS period.

- Support for 8 to 32 audio data bits per slot (channel).

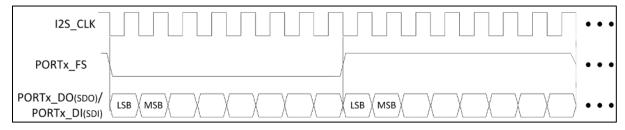

Figure 8 shows an example of I<sup>2</sup>S mode.

Figure 8 l'S Mode

TDM transfers have the following features:

- Bit clock (I2S\_CLK) up to 24.576 MHz.

- Sampling rates of up to 192 KHz.

- Frame Sync pulse (I2S\_WS) must be at least one-bit clock wide.

- Support for up to four active slots (channels) out of 32. Slots do not have to be consecutive. In master mode, the master clock generator supports up to 256 clocks per frame, however slave TDM operation supports up to 32 slots with 32 data bits per slot and is not limited by clocks per frame.

- Support for 8 to 32 audio data bits per slot (channel).

- Support for output transmission on either the rising or falling bit clock edge.

- Support for input sampling on either the rising or falling bit clock edge.

- The transmitting and sampling edges must be of opposite polarity.

- Support for both MSB-first and LSB-first transmission modes.

Figure 9 shows an example of TDM mode.

Figure 9 TDM Mode

### 2.1.7 Host Interfaces

### 2.1.7.1 Firmware download, Command and Control

The IA700 audio processor supports command and control over SPI, UART, and I2C interfaces. It also supports firmware download on all three interfaces selected at boot time by a Host.

Table 3 Supported interface speed

| Control Interfaces | Firmware download Interface Speed with<br>Internal Oscillator | Firmware download Interface Speed with external CLK_IN |

|--------------------|---------------------------------------------------------------|--------------------------------------------------------|

| SPI                | 4.5 MHz                                                       | 13 MHz                                                 |

| UART 1.152 Mbps    |                                                               | 2.048 Mbps                                             |

| 12C                | 1 MHz                                                         | 1 MHz                                                  |

#### 2.1.7.2 SPI

The IA700 supports a four-wire Serial Peripheral Interface (SPI) protocol with a frequency range of up to 13 MHz. The user can download a firmware image and send API control and data to the IA700 through the SPI slave port.

#### 2.1.7.3 UART

The IA700 supports a two-wire UART (UART\_TX, UART\_RX). The UART is required to download a firmware image onto the IA700, and a UART connection to the host is required for streaming as an alternative to ID tapping. The interface can detect the baud rate automatically up to 115 KHz; it also supports baud rates of 0.4608, 0.9216, 1.000, 1.024, 1.152, 2.000, and 2.048 MHz as configured by the host using the Bootloader UART baud rate change API command or by the firmware after the binary file download.

#### $2.1.7.4 I^2C$

The IA700 supports a Slave I<sup>2</sup>C bus as the host interface with a 7-bit address range. The I<sup>2</sup>C address can be set through the data output Latch-On Reset (LOR) configuration pin, as described in Section 4.1. A firmware image is downloaded to the IA700 using the I<sup>2</sup>C interface.

### 2.1.7.5 Debug

The SPI, UART, and I<sup>2</sup>C interfaces all support the collection of diagnostic data streams. This requires the ability to collect synchronized input/output streams using any of the interfaces.

Debug is supported either by a virtual connection over ADB to an Android Proxy running on the host processor, or by a direct physical connection to test-points on the system PCB, with no-load resistors connected to the SPI, UART, I2C I/O pins for the IA700.

### 2.2 Control Subsystem

#### 2.2.1 Boot Control

When the user turns on the VDD, the IA700 goes through a power-up initialization process. During this time, the IA700 does not respond to host requests. The IA700 then enters a control interfaces auto-detect mode to determine which pin configuration to use for operation. For more information on the start-up sequence, see Section 4.2 and for more information on the auto-detect sequence, refer *IA700 API Guide*.

#### 2.2.2 Reset Control

There are two types of Resets:

- 1. External Hard Reset

- 2. Soft Reset

#### 2.2.2.1 External Hard Reset

The System Reset Input pin (RESET\_N) is an active low asynchronous reset input that provides a global reset for the IA700. When reset asserts, the digital output pins are tri-stated, or pulled-up or pulled-down by internal resistors, and the default values for all the internal registers are restored. RESET\_N must drive high from the system printed circuit board.

**Note:** Do not share the RESET\_N pin of IA700 with any other reset pin on printed circuit board.

#### 2.2.2.2 Soft Reset

The one watchdog timer of the IA700 resets the processor when it expires.

### 2.2.4 Power Management

Figure 5 shows a color-coded block diagram of the IA700's different power domains. There are two primary power domains: one to supply the core analog signal path circuitry and one to supply the core DSP subsystem. The DSP core subsystem has three subordinate power domains; controlled independently to optimize power in various use cases. This section provides further details around the primary ASIC power domains.

Table 4 Power Supply Pins

| Name       | Voltage | Max Current | Power Direction | Comment     |

|------------|---------|-------------|-----------------|-------------|

| GND        | 0 V     | 25mA        | -               |             |

| VDD_IO     | 1.8V    | 25mA        | Input           | IO supply   |

| VDD_LDOD/A | 1.1V    | 23mA        | Input           | Core supply |

#### Where:

- GND is the common ground pin for all IA700.

- VDD\_IO supply provides power to all I/Os.

- VDD\_LDOD/A supply provides power to the DSP subsystem, including the processor, memory, Audio Fabric, and core logic.

IA700 supports various sleep modes to save power. For more details, refer <u>Section 3.5</u>.

## 2.3 Clock Subsystem

### 2.3.1 CLK\_IN

The IA700 has an option to receive clock from extern source on CLK\_IN pin. The supported frequencies for CLK\_IN are 0.768MHz and 1.536MHz.

#### 2.3.2 PLL

The IA700 has an integrated, high-performance Phase Lock Loop (PLL) that provides clocks for the processors, memory, and related circuits as well as oversampling clocks that drive the serial control communications interfaces. Table 11 details the performance of PLL.

#### 2.3.3 Internal Oscillators

The IA700 has an integrated non-calibrated silicon oscillator optimized for accuracy and system flexibility. The host can calibrate this internal oscillator by providing a reference clock with a factor of 43.008MHz and running appropriate commands. After calibration, the internal oscillator output frequency is set to 43.008MHz. This output frequency divides within the IA700 for use by various internal modules, or as a master output clock. For more information on the performance of the oscillator, see Section 6.3.

# 2.4 Interrupts

The IA700 provides an interrupt request to the host for a keyword detection event through the HOST\_IRQ function, as well as a wakeup event from the host through the WAKE function.

Based on the configuration, the HOST\_IRQ and WAKE function map to a specific pin. For more information, see Table 9, Table 1, and IA700 API Guide.

# **Chapter 3: Operating Modes**

The IA700 can operate in one of the following modes:

- **Bootloader Auto-Detect Mode:** After power up, the IA700 detects the host control interface and waits for firmware download.

- **Software Pass-Through Mode:** The IA700 supports software pass-through mode for PDM-to-PCM/I2S.

- Hardware Pass-Through Mode: The IA700 supports hardware pass-through PDM-to-PDM.

- **Retention Sleep Mode:** The IA700 is in low power mode retaining memory.

### 3.1 Bootloader Mode (SBL)

Upon system power-up, or after deep-sleep mode, the IA700 is in Bootloader Mode and waits for either an API command to determine the host control interface, or a PDM clock to enter HW Bypass Mode. Once the control interface is determined, download firmware and configure IA700 to operate in one of the other modes listed. For more information on auto-detecting the control interface, firmware download, and mode switching, refer *IA700 API Guide*.

### 3.2 OpenDSP

248 KB of total on-chip RAM enables third-party algorithms, with dynamic audio filtering and keyword detection as examples. Knowles provides a Software Development Kit (SDK) to enable third-party developers to create DSP algorithms on the IA700 Audio Processor platform.

Contact Knowles to obtain access to the SDK and associated Developer's Guide.

# 3.3 Software Pass-Through

Host can configure the IA700 to run in software pass-through mode. In this mode, PDM0 is an input port and PCM/I2S is an output port. The Software Pass-Through mode supports only after firmware download.

# 3.4 Hardware Pass-Through

The Hardware Pass-Through mode allows the host to put the IA700 into a low power digital audio pass-through mode to bypass processing. In this mode, the IA700 reads data from external microphone connected to PDM0 and sends it to the Host on PDM00 port.

## 3.5 Retention Sleep/Use Case Sleep Mode

IA700 can enter into a retention sleep mode after the firmware download. The chip enters into normal sleep mode retaining the memory content. A wakeup signal from retention sleep mode is required to bring the chip into firmware mode. A firmware download is not required after waking up from retention sleep mode. Exiting retention sleep mode restarts any internal hardware blocks that were off due to the sleep command.

Similar to retention sleep mode, IA700 can enter into use-case sleep mode after sending appropriate sleep command depends on the use-case.

# **Chapter 4: Design Considerations**

### 4.1 Latch-On Reset Configuration Pins

#### 4.1.1 Boot clock selection

The IA700 has a Latch-On Reset (LOR) P1 pin to select the boot time clock source. The pin is in latched state when the power is on and stable. An internal pull-down resistor pulls this pin low (0) when not connected. To set this pin to the logical value of 1, connect the pin to the same power supply that powers the IA700 with an external  $10 \text{ k}\Omega$  pull-up resistor.

Table 5 Latch on reset configuration for boot clock

| LOR_1 (P1 pin) | Description                   |

|----------------|-------------------------------|

| 0              | Boot from CLK_IN              |

| 1              | Boot from internal oscillator |

#### 4.1.2 I2C Address Pins

The IA700 contains two Latch-On Reset (LOR) address pins (P2 and P3 pins) that set the I<sup>2</sup>C slave address when in I<sup>2</sup>C mode. The address pins are in latched state when the power is on and stable. An internal pull-down resistor pulls the address pins low (0) when not connected. To set the address pin to a logical value of 1, connect the LOR pin to the same power supply that powers the IA700 with an external 10 k $\Omega$  pull-up resistor.

Table 6 shows the configuration of the address pins and the resulting I<sup>2</sup>C address.

Table 6 Latch On Reset Configuration for PC Address

| ADDR1 (P2 pin) | ADDR2 (P3 pin) | Description         |

|----------------|----------------|---------------------|

| 0              | 0              | 7 bit, address 0x3E |

|                |                | (default)           |

| 0              | 1              | 7 bit, address 0x38 |

| 1              | 0              | 7 bit, address 0x3F |

| 1              | 1              | 7 bit, address 0x39 |

# 4.2 Start-Up Sequencing

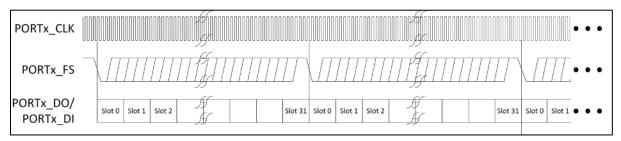

Figure 10 shows a complete start-up sequence, including system power and the host bus.

After LOR, the IA700 wakes up in the Auto-detect state, where it determines the control interface and awaits command communication or firmware download from the host.

**Note:** The host interface pins must be floating or driven to ground during VDD power up so that they are never exceed VDD+0.3 V.

Figure 10 Start-up Sequence

The host must follow a defined sequence to download program code into the IA700. The program code download sequences over the various interfaces are described in detail in the IA700 API Guide describes

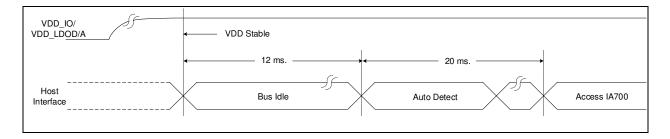

### 4.3 Sleep and Wake-up Sequence

The IA700 can be set to an ultra-low-power sleep state to minimize power consumption. During sleep, the host can continue to access other devices connected to the host interface buses.

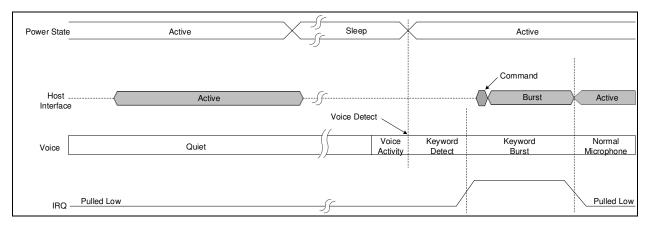

Figure 11, Figure 12, and Error! Reference source not found. provide a general overview of the sleep and wake-up process and their timings. The *IA700 API Guide* provides a detailed description of the sleep and wake-up sequences.

Figure 11 Sleep and Wake-Up Sequence for Waking Up the IA700 Using the WAKEUP Input

Figure 12 Sleep and Wake-up Sequence for Voice Wake mode with external AAD enabled microphone

Table 7 Sleep and Wake-up Sequence Timings

| Parameter                                          | Symbol           | Min | Typical | Max | Units |

|----------------------------------------------------|------------------|-----|---------|-----|-------|

| Time from WAKEUP deasserted to SLEEP command write | t <sub>ws</sub>  | 30  | 1       | 1   | ms    |

| Time from WAKEUP asserted to SYNC command write    | t <sub>was</sub> | 30  | 1       | -   | ms    |

| Time from SYNC _ACK read to WAKEUP deasserted      | t <sub>sw</sub>  | 0   | -       | -   | ms    |

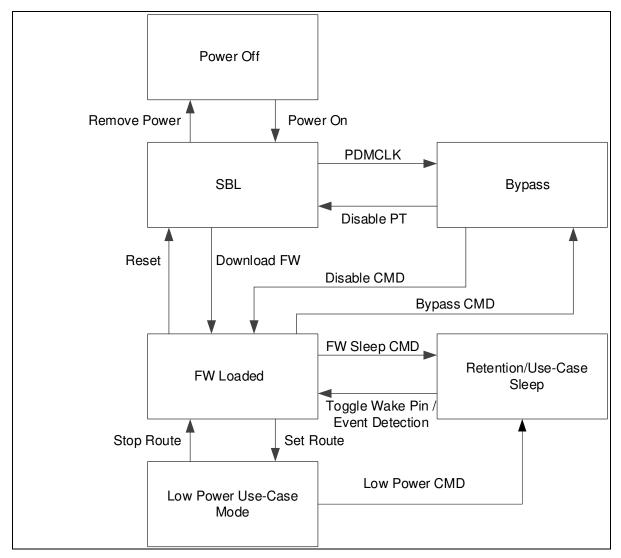

# 4.4 State Diagram

Figure 13 shows the IA700 state diagram.

Figure 13 IA700 State Diagram

# **Chapter 5: Pin Descriptions**

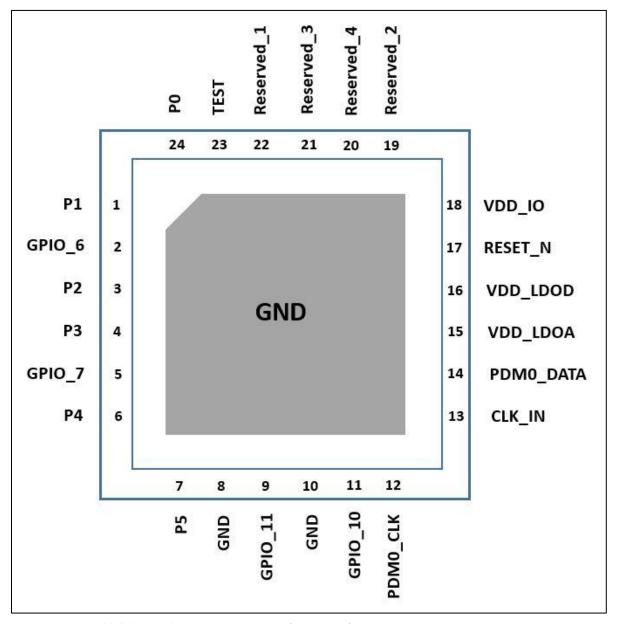

# 5.1 Pinout Diagram

Figure 14 shows the pinouts for the IA700CQ QFN24 package.

Figure 14 IA700CQ QFN24 Pin Assignments (Top View)

### 5.3 Pinout Table

Table 8 shows a list of the IA700 pins and the signals associated with them. In active mode, the firmware sets the pin state depending on the mode. Firmware can configure a pin to be an input or an output, and enables internal pull-ups or pull-downs if they are available.

Table 8 Pin Descriptions

| Pin# | Name       | Туре           | Description                            |

|------|------------|----------------|----------------------------------------|

| 1    | P1         | Digital I/O    | P1 I/O                                 |

| 2    | GPIO_6     | Digital I/O    | General purpose I/O                    |

| 3    | P2         | Digital I/O    | P2 I/O                                 |

| 4    | P3         | Digital I/O    | P3 I/O                                 |

| 5    | GPIO_7     | Digital I/O    | General purpose I/O                    |

| 6    | P4         | Digital I/O    | P4 I/O                                 |

| 7    | P5         | Digital I/O    | P5 I/O                                 |

| 8    | GND        | Power          | Ground                                 |

| 9    | GPIO_11    | Digital I/O    | General purpose I/O                    |

| 10   | GND        | Power          | Ground                                 |

| 11   | GPIO_10    | Digital I/O    | General purpose I/O                    |

| 12   | PDM0_CLK   | Digital I/O    | PDM microphone clock                   |

| 13   | CLK_IN     | Digital I/O    | Clock input                            |

| 14   | PDM0_DATA  | Digital I/O    | PDM microphone data                    |

| 15   | VDD_LDOA   | Power          | Power supply for core                  |

| 16   | VDD_LDOD   | Power          | Power supply for core                  |

| 17   | RESET_N    | Input          | Reset, Active Low                      |

| 18   | VDD_IO     | Power          | Power supply for IO                    |

| 19   | RESERVED_2 | Not Applicable | Reserved pin – No connect              |

| 20   | RESERVED_4 | Not Applicable | Reserved pin – No connect              |

| 21   | RESERVED_3 | Not Applicable | Reserved pin – No connect              |

| 22   | RESERVED_1 | Not Applicable | Reserved pin – No connect              |

| 23   | TEST       | Not Applicable | Test pin. Must connect it with Ground. |

| 24   | P0         | Digital I/O    | P0 I/O                                 |

| 25   | GND        | Power          | Ground paddle (TAB)                    |

Table 9 Pin Configuration Per Boot Mode

| Mode                                | P0      | P1      | P2                   | P3                   | P4       | P5       |

|-------------------------------------|---------|---------|----------------------|----------------------|----------|----------|

| PDM + I <sup>2</sup> C              | PDM_CLK | PDM_SDO | I2C_ADDR1            | I2C_ADDR2            | I2C_SCLK | I2C_SDA  |

| PDM +<br>UART                       | PDM_CLK | PDM_SDO | NA                   | IRQ                  | UART_RX  | UART_TX  |

| PDM + SPI                           | PDM_CLK | PDM_SDO | SPI_SCLK             | SPI_MISO             | SPI_SS   | SPI_MOSI |

| I <sup>2</sup> S + I <sup>2</sup> C | I2S_WS  | I2S_CLK | I2S_SDI<br>I2C_ADDR1 | I2S_SDO<br>I2C_ADDR2 | I2C_SCLK | I2C_SDA  |

| I <sup>2</sup> S + UART             | I2S_WS  | I2S_CLK | I2S_SDI              | I2S_SDO              | UART_RX  | UART_TX  |

# Chapter 6: Electrical Characteristics

#### 6.1 General Electrical Characteristics

Table 10 Electrical Characteristics

Test conditions: VDD\_IO = 1.8V at T<sub>A</sub> =25°C, unless otherwise specified.

| Parameter                                              | Symbol          | Min           | Typical | Max              | Units |

|--------------------------------------------------------|-----------------|---------------|---------|------------------|-------|

| Digital Input High-Level Voltage                       | V <sub>IH</sub> | 0.65 * VDD_IO |         |                  | V     |

| Digital Input Low-Level Voltage                        | V <sub>IL</sub> | -0.2          |         | 0.35 *<br>VDD_IO | V     |

| Digital Output High-Level Voltage                      | V <sub>OH</sub> | 0.65 * VDD_IO |         |                  | V     |

| Digital Output Low-Level Voltage                       | V <sub>OL</sub> |               |         | 0.35 *<br>VDD_IO | V     |

| Programmable Digital Input Internal Pull-Down Resistor | R <sub>PD</sub> | 35            | 61      | 114              | kΩ    |

| Programmable Digital Input Internal Pull-Up Resistor   | R <sub>PU</sub> | 39            | 71      | 138              | kΩ    |

| I/O drive strength                                     |                 | 2             |         | 12               | mA    |

| Capacitance To Ground of I/O Pins                      | С               | 9             |         | 18               | pF    |

#### Note:

- 1. The maximum output current source or sink drive by any I/O pin is programmable in four steps. The default is 4 mA nominal. For more information and settings, refer IA700 API Guide.

- 2. External I/O loading and drive strength have a direct effect on voltage V<sub>IH</sub> and V<sub>IL</sub> transition times. For timing critical signals, adjust the values of any external R and C components connected to the I/O pins based on the application.

### 6.2 PLL Characteristics

Table 11 lists the PLL operation parameters. The PLL has two frequency ranges of operation, set through the software API. The Phase-Frequency Detector (PFD) on the PLL receives a divided-down version of the reference clock.

Table 11 PLL Characteristics

Test conditions: VDD = 1.8V at  $T_A = 25^{\circ} C$ , unless otherwise specified.

| Parameter                                    | Symbol                  | Conditions | Min   | Typical         | Max             | Units              |

|----------------------------------------------|-------------------------|------------|-------|-----------------|-----------------|--------------------|

| Reference Frequency                          | f <sub>PLL_IN</sub>     |            | 0.768 | -               | 24.576          | MHz                |

| DED Fraguency                                | f                       | Low Range  | 0.768 | -               | 35 <sup>1</sup> | MHz                |

| PFD Frequency                                | f <sub>PLL_PFD</sub>    | High Range | 0.768 | -               | 75 <sup>2</sup> | MHz                |

| VCO Fraguency                                | fru voo                 | Low Range  | 28    | -               | 140             | MHz                |

| VCO Frequency                                | f <sub>PLL_</sub> vco   | High Range | 120   | -               | 600             | MHz                |

| Output Frequency                             | f <sub>PLL_OUT</sub>    | -          | 0.11  | -               | 98.304          | MHz                |

| Lock Time                                    | tpll_lock               | -          |       | 500             | 1000            | PFD cycles         |

| Feedback Divider                             | n <sub>PLL_FBDIV</sub>  | -          | 4     | -               | 781             | integer            |

| Loop Bandwidth                               | f <sub>PLL_BW</sub>     | -          |       | fPLL_PFD/<br>25 |                 | MHz                |

| Period Jitter (random) <sup>3</sup>          | tpll_jit_rnd            | -          | 1.73  | -               | 239.38          | pS (RMS)           |

| Period Jitter Power Supply Noise Sensitivity | t <sub>PLL_JIT_PS</sub> | -          |       | 1.5             | -               | pS/mV              |

| Period Jitter from reference spur            | tpll_JIT_REF            | -          |       | 1%              | -               | Output clock cycle |

| Integrated Long-Term Jitter <sup>4</sup>     | tPLL_JIT_LT             | -          | 14.37 | -               | 657.38          | pS (RMS)           |

For Low Range Maximum PFD Frequency f<sub>PLL\_PFD</sub> = f<sub>PLL\_VCO</sub>÷4

$<sup>^2</sup>$ For High Range Maximum PFD Frequency  $f_{PLL\_PFD} = f_{PLL\_VCO} \div 8$

$<sup>^3</sup>$ Formula to calculate Period Jitter (random)  $t_{PLL\_JIT\_RND} = 0.7 \text{ pS} \times \text{sqrt} (600 \text{ MHz} \div f_{PLL\_VCO}) \times \text{sqrt} (600 \text{ MHz} \div f_{PLL\_OUT})$

Formula to calculate Integrated Long-Term Jitter tell JIT LT = 100 pS × sqrt (6 MHz ÷ fell PFD) × sqrt (128 MHz ÷ fell VCO)

### 6.3 Oscillator Characteristics

The non-calibrated on-chip silicon oscillator has the characteristics listed in Table 12. The following frequency ranges are after oscillator calibration. There are two operational ranges, set by an internal register through the software API.

Table 12 Oscillator Characteristics

Test conditions: VDD = 1.8V at TA =25 o C, unless otherwise specified.

| Parameter                               | Symbol                  | Conditions    | Min | Typical | Max | Units     |

|-----------------------------------------|-------------------------|---------------|-----|---------|-----|-----------|

| Output Fraguency                        | f                       | Low Range     | -   | 43.008  | ı   | MHz       |

| Output Frequency                        | t <sub>osc_out</sub>    | High Range    | -   | 172.032 | -   | MHz       |

| Output Frequency Temperature Dependence | $\Delta_{OSC\_T}$       | -10°C to 80°C | -   | 340     | 535 | ppm/°C    |

| Dariad litter (random)                  |                         | Low Range     | -   | -       | 44  | mc (DNAC) |

| Period Jitter (random)                  | tosc_jit_rnd            | High Range    | -   | -       | 22  | pS (RMS)  |

| Period Jitter Power Supply Noise        |                         | Low Range     |     | 0.0     | 2.2 | C / \     |

| Sensitivity                             | t <sub>OSC_JIT_PS</sub> | High Range    | -   | 0.9     | 2.2 | pS/mV     |

### 6.4 Audio Port Interface Characteristics

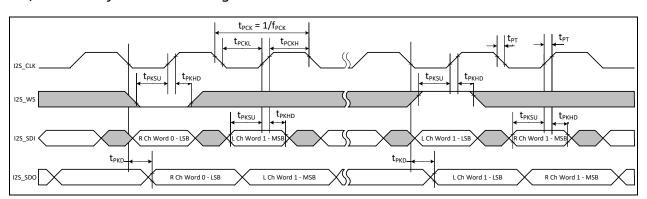

### 6.4.1 I<sup>2</sup>S/TDM Interface Slave Timing

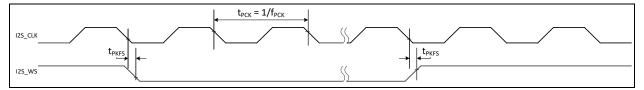

Figure 15 I<sup>2</sup>S/TDM Interface Slave Timing

In Slave Mode, I2S\_CLK and I2S\_WS are inputs.

Table 13 I'S/TDM Slave Timing

Test Conditions: VDD = 1.8V, 10pF Load, at  $T_A$  =25° C, unless otherwise specified. Measurement levels on waveforms are  $V_{lH}$  and  $V_{lL}$ .

| Parameter                                                  | Symbol            | Min | Typical            | Max    | Units              |

|------------------------------------------------------------|-------------------|-----|--------------------|--------|--------------------|

| I2S_CLK Clock Frequency                                    | f <sub>PCK</sub>  | -   | 1                  | 24.576 | MHz                |

| I2S_CLK Clock Cycle Time                                   | t <sub>PCK</sub>  | -   | 1/f <sub>PCK</sub> | -      | S                  |

| I2S_CLK Clock High Pulse Width                             | t <sub>PCKH</sub> | 35  | -                  | -      | % t <sub>PCK</sub> |

| I2S_CLK Clock Low Pulse Width                              | t <sub>PCKL</sub> | 35  | ı                  | -      | % t <sub>PCK</sub> |

| I <sup>2</sup> S input transition time                     | t <sub>PT</sub>   | -   | 10                 | -      | ns                 |

| I2S_SDI and I2S_WS Input Setup Time to CLK 个 <sup>2</sup>  | t <sub>PKSU</sub> | 25  | ı                  | -      | ns                 |

| I2S_SDI and I2S_WS Input Hold Time from CLK 个 <sup>2</sup> | t <sub>PKHD</sub> | 5.1 | ı                  | -      | ns                 |

| I2S_SDO Data Output Delay from CLK $\downarrow$ $^3$       | t <sub>PKD</sub>  | 0   | =                  | 15     | ns                 |

<sup>&</sup>lt;sup>1</sup>The design ensures the timing parameters and not by the final test.

<sup>&</sup>lt;sup>2</sup>The I2S\_WS and I2S\_SDI inputs sampled at the rising edge of the I2S\_CLK.

<sup>&</sup>lt;sup>3</sup>The I2S\_SDO outputs are set to drive at the falling edge of the I2S\_CLK.

### 6.4.3 I<sup>2</sup>S/TDM Interface Master Timing

Figure 16 I<sup>2</sup>S/TDM Interface Master Timing

In Master Mode, I2S\_CLK and I2S\_WS are outputs, but I2S\_SDI and I2S\_SDO timing with respect to I2S\_CLK are identical to that in Slave mode.

Table 14 I<sup>2</sup>S/TDM Master Timing

Test Conditions: VDD = 1.8V, 10pF Load, at  $T_A$  =25° C, unless otherwise specified. Measurement levels on waveforms are  $V_{lH}$  and  $V_{lL}$ .<sup>1</sup>

| Parameter                                   | Symbol            | Min | Typical | Max | Units            |

|---------------------------------------------|-------------------|-----|---------|-----|------------------|

| I2S_WS Output Delay from CLK ↓ <sup>2</sup> | t <sub>PKFS</sub> | 0   | -       | 25% | t <sub>PCK</sub> |

<sup>&</sup>lt;sup>1</sup>The design ensures the timing parameters and not by the final test.

### 6.4.4 Audio Port PDM Interface Characteristics

Figure 17 PDM Interface Timing

### Table 15 PDM Timing<sup>1</sup>

Test Conditions: VDD = 1.8V, 10pF Load, at T<sub>A</sub> =25° C, unless otherwise specified.

| Parameter                                              | Symbol            | Min   | Тур              | Max   | Units |

|--------------------------------------------------------|-------------------|-------|------------------|-------|-------|

| PDM_CLK Output Frequency, Operating                    | fPDCLKOUT         | 0.512 | 3.072            | 4.800 | MHz   |

| PDM_CLK Output Frequency, Low-power Voice<br>Wake Mode | -                 | 0.512 | 0.768<br>Nominal | -     | MHz   |

| PDM Data Input Setup Time to Clock Edge                | t <sub>PDSU</sub> | 25    | -                | -     | ns    |

| PDM Data Input Hold Time after Clock Edge              | t <sub>PDH</sub>  | 3     | -                | -     | ns    |

| PDM Data Delay from PDM_CLK Edge <sup>2</sup>          | t <sub>PDD</sub>  | 6     | -                | -     | ns    |

<sup>&</sup>lt;sup>1</sup>The design ensures the timing parameters and not by the final test.

<sup>&</sup>lt;sup>2</sup>The I2S\_WS outputs are set to drive at the falling edge of the I2S\_CLK. Delay from CLK ↓ to I2S\_CLK is determined by an integer number of periods of an internal oversampling clock used to generate both I2S\_CLK and I2S\_WS.

<sup>&</sup>lt;sup>2</sup>The edge of the clock on which data is output is programmable.

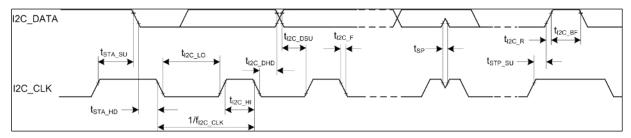

### 6.5 I<sup>2</sup>C Slave Interface Characteristics

Figure 18 I<sup>2</sup>C Slave Interface Timing

### Table 16 PC Slave Timing

Test Conditions: VDD = 1.8V, Output Load = 20pF, unless otherwise specified.

| Parameter                                       | Cymhol              | Standard Mode |      | Fast Mode |     | Fast Mode+ |      | Units |

|-------------------------------------------------|---------------------|---------------|------|-----------|-----|------------|------|-------|

| Parameter                                       | Symbol              | Min           | Max  | Min       | Max | Min        | Max  |       |

| I <sup>2</sup> C Clock Frequency                | fi2C_CLK            | 0             | 100  | 0         | 400 | 0          | 1000 | KHz   |

| I <sup>2</sup> C Clock High Period              | tı2C_HI             | 4.0           | -    | 0.6       | -   | 0.26       | -    | μs    |

| I <sup>2</sup> C Clock Low Period               | tı2C_LO             | 4.7           | -    | 1.3       | -   | 0.5        | -    | μs    |

| Start Condition Setup Time                      | tsta_su             | 4.7           | -    | 0.6       | -   | 0.26       | -    | μs    |

| Start Condition Hold Time                       | t <sub>STA_HD</sub> | 4.0           | -    | 0.6       | -   | 0.26       | -    | μs    |

| Stop Condition Setup Time                       | t <sub>STP_SU</sub> | 4.0           | -    | 0.6       | -   | 0.26       | -    | μs    |

| Bus Free Time between Stop and Start Conditions | t <sub>I2C_BF</sub> | 4.7           | -    | 1.3       | -   | 0.5        | -    | μs    |

| I <sup>2</sup> C Clock and Data Rise Time       | tı2C_R              | -             | 1000 | 20        | 300 | -          | 120  | ns    |

| I <sup>2</sup> C Clock and Data Fall Time       | t <sub>12C_F</sub>  | -             | 300  | -         | 300 | -          | 120  | ns    |

| I <sup>2</sup> C Data Setup Time                | ti2c_dsu            | 250           | -    | 100       | -   | 50         | -    | ns    |

| I <sup>2</sup> C Data Hold Time                 | ti2C_DHD            | 0             | 202  | 0         | 202 | 0          | -    | ns    |

| Spike Suppression Period                        | tsp                 | 0             | 0    | 0         | 50  | 0          | 50   | ns    |

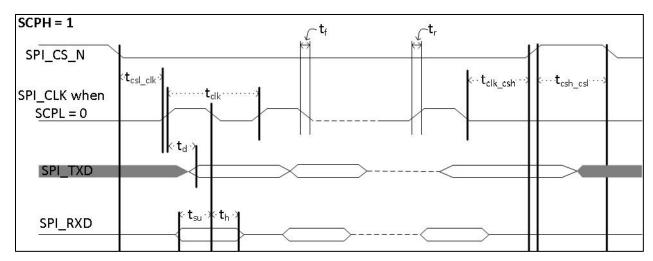

# **6.6 SPI Interface Specifications**

Figure 19 SPI Interface Timing

In bootloader auto-detect mode, the SPI clock phase is set to SCPH = 1, and the clock polarity is set to SCPL = 0 on reset. SPI is 32-bit interface. To enable the SPI interface in bootloader mode, refer IA700 API Guide.

Table 17 SPI Timing SCPH = 1

Test Conditions: VDD = 1.8V, >=6x oversampling, 10pF Load, at T<sub>A</sub> = 25° C, unless otherwise specified.

| Parameter                                   | Symbol               | Min   | Typical | Max    | Units             |

|---------------------------------------------|----------------------|-------|---------|--------|-------------------|

| SPI sample clock frequency                  | $f_{samp}$           | -     | =       | 43     | MHz <sup>1</sup>  |

| SPI sample clock period                     | $T_{samp}$           | 23.25 | =       | -      | ns                |

| SPI clock frequency                         | f <sub>clk</sub>     | -     | -       | 13     | MHz               |

| SPI clock period                            | t <sub>clk</sub>     | 76.92 | -       | -      | ns                |

| Chip select assert to clock edge            | t <sub>csl_clk</sub> | 1     | -       | -      | t <sub>clk</sub>  |

| Clock edge to chip select de-assert         | $t_{clk\_csh}$       | 1     | -       | -      | t <sub>clk</sub>  |

| Chip select de-assert to chip select assert | t <sub>csh_csl</sub> | 1     | -       | -      | t <sub>clk</sub>  |

| Tx data valid from clock edge               | t <sub>d</sub>       | -     | -       | 64.125 | ns                |

| Rx data setup time                          | t <sub>su</sub>      | 0.5   | -       | -      | t <sub>samp</sub> |

| Rx data hold time                           | t <sub>h</sub>       | 1.5   | -       | -      | t <sub>samp</sub> |

| SPI clock rise time                         | t <sub>r</sub>       | =     | -       | 10%    | t <sub>clk</sub>  |

| SPI clock fall time                         | t <sub>f</sub>       | -     | -       | 10%    | t <sub>clk</sub>  |

<sup>&</sup>lt;sup>1</sup>The maximum frequency is available only in certain modes. The internal oversampling clock is set to a minimum of 2.5 times the SPI\_CLK frequency by the software API. The values in this table vary, as the internal sampling clock changes. The higher the internal sampling clock frequency, the higher the power consumption.

# Chapter 7: PCB Design and Layout Guidelines

### 7.1 Power Planes

Use low impedance power planes with decoupling capacitors for the design of system power supply.

Place ceramic SMT bypass capacitors (1  $\mu$ F) next to the IA700 VDD\_LDOD and VDD\_LDOA power input pins, as well as IA700 VDD\_IO pin. The IA700 VDD\_LDOD and VDD\_LDOA pins can be shorted and can have a 1  $\mu$ F decoupling capacitor connected to it.

Additional decoupling capacitors (0.1  $\mu$ F) may be necessary to reduce noise on the power pin. Keep the routing traces for the decoupling capacitors as short as possible. A long trace has an antenna effect that can introduce additional noise into the power supply, which requires additional filtering.

# 7.2 Digital Signal Routing

Follow good design practices in PCB layout by keeping the digital signal traces as short as possible and away from analog and RF signals.

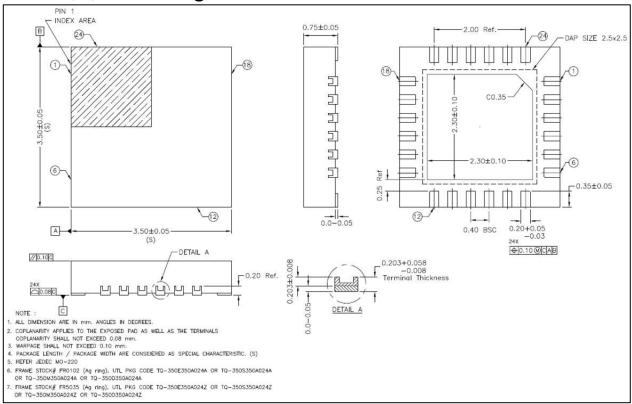

# **Chapter 8: Mechanical Specifications**

# 8.1 IA700CQ QFN24 Package Dimension

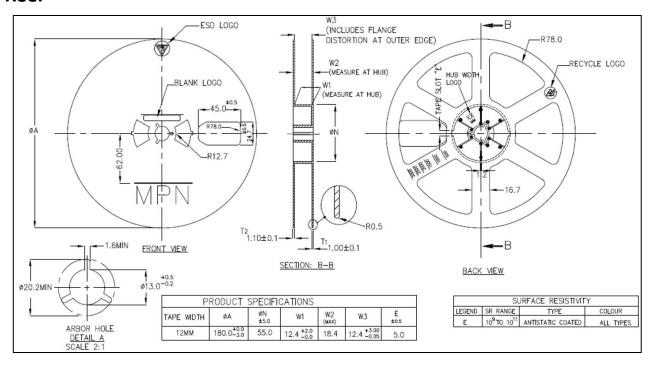

# Chapter 9: Packaging and Marking Details

### 9.1 **Reel**

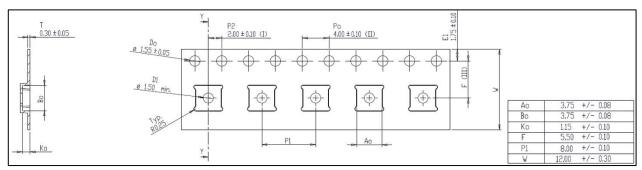

# 9.2 **Tape**

**Note:** Dimensions are in millimeters unless otherwise specified.

Table 18 Model and Part Numbers

| Model Number | Reel Diameter | Quantity Per Reel |

|--------------|---------------|-------------------|

| IA700CQ      | 13"           | 2500              |

Unit orientation in carrier tape: Pin 1 top left

| Product Customer Lot Number – U193545010.00 |                             |                                                                                   |  |  |  |  |

|---------------------------------------------|-----------------------------|-----------------------------------------------------------------------------------|--|--|--|--|

| Digit                                       | Description                 | Actual                                                                            |  |  |  |  |

| 1                                           | Vendor ID                   | U for UTAC                                                                        |  |  |  |  |

| 2-3                                         | Year – YY                   | 2 digit                                                                           |  |  |  |  |

| 4-5                                         | Workweek – WW               | 2 digit                                                                           |  |  |  |  |

| 6-9                                         | Fab lot ID                  | 1st two and last two digit of the fab lot ID                                      |  |  |  |  |

| 10                                          | Sequence #                  | One hexadecimal character (OSAT assigned running character: 0,1,29,A,BX,Y,Z,0,1,) |  |  |  |  |

| 11                                          |                             | Dot                                                                               |  |  |  |  |

| 12-13                                       | Split/Child Indicator       | 2 digit                                                                           |  |  |  |  |

| Example: Year 2019, Workw                   | eek 35, Fab lot ID UKNT4500 | 1.00                                                                              |  |  |  |  |

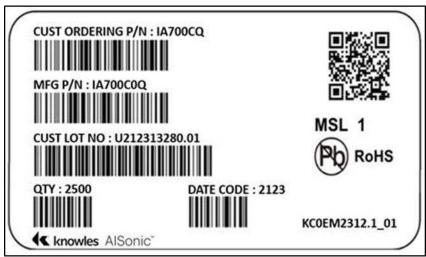

# 9.3 Packing Details

Customer Ordering PN: IA700CQ Knowles Manufacturing PN: IA700C0Q

#### **Label Content:**

• CUST ORDERING P/N = Knowles Customer Part Number

• MFG P/N = Knowles Manufacturing Part Number

• CUST LOT NO = Lot Number from supplier

• QTY = Unit quantity per reel

• DATE CODE = Manufacturing Date Code in YYWW format

• MSL = Moisture Sensitive Level

• Lead Free and RoHS symbols

• UTL label running number (unique number per label)

### Barcode type:

- 1D code 128 or 3 of 9

- 2D QR code

#### 2D barcode content:

- P+ (CUST ORDERING P/N) Q+(QTY)T+ (CUST LOT NO) S+ (RUNNING NUMBER) D+ (DATE CODE)

- 2D barcode content example based on data on the label sample:

- P+IA700CQQ+2500T+U212313280.01S+KC0EM2312.1\_01D+2123

**Note:** All barcodes in label sample are for illustration only.

# Chapter 10: Recommended Reflow Profile

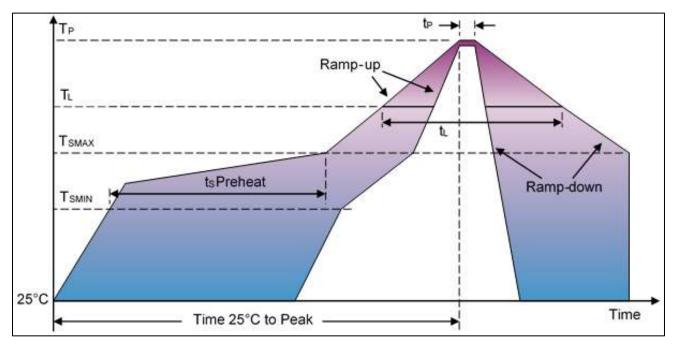

Figure 20 Recommended Reflow Profile

Table 19 Profile Specifications

| Profile Feature                                                           | Pb-Free        |  |

|---------------------------------------------------------------------------|----------------|--|

| Average Ramp-up rate (TSMAX to TP) 3°C/second m                           |                |  |

| Preheat                                                                   |                |  |

| - Temperature Min (T <sub>SMIN</sub> )                                    | 150°C          |  |

| - Temperature Max (T <sub>SMAX</sub> )                                    | 200°C          |  |

| - Time (T <sub>SMIN</sub> to T <sub>SMAX</sub> ) (t <sub>s</sub> )        | 60-180 seconds |  |

| Time maintained above:                                                    |                |  |

| - Temperature (TL)                                                        | 217°C          |  |

| - Time (tL)                                                               | 60-150 seconds |  |

| Peak Temperature (T <sub>P</sub> ) 260°C                                  |                |  |

| Time within 5°C of actual Peak Temperature (t <sub>P</sub> ) 20-40 second |                |  |

| Ramp-down rate (T <sub>P</sub> to T <sub>SMAX</sub> ) 6°C/second m        |                |  |

| Time 25°C to Peak Temperature 8 minutes max                               |                |  |

Note: Based on IPC/JDEC J-STD-020 Revision C.

All temperatures refer to topside of the package, measured on the package body surface.

### 10.1 Additional Notes

- 1. MSL (moisture sensitivity level) Class 1.

- 2. Recommending maximum of three reflow cycles.

### **Revision History**

| Revision | Description     | Date       |

|----------|-----------------|------------|

| 1.0      | Initial Release | 25-08-2021 |

Material contained in this document may not be copied, reproduced, reduced to any electronic medium or machine readable form or otherwise duplicated and the information herein may not be used, disseminated or otherwise disclosed, except with the prior written consent of an authorized representative of Knowles, Inc. Knowles is a registered trademark of Knowles Corporation. All other trademarks are the properties of their respective owners.