## FAIRCHILD

SEMICONDUCTOR

# MM74C911 4-Digit Expandable Segment Display Controller

## **General Description**

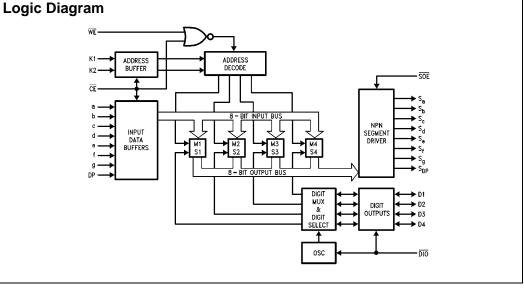

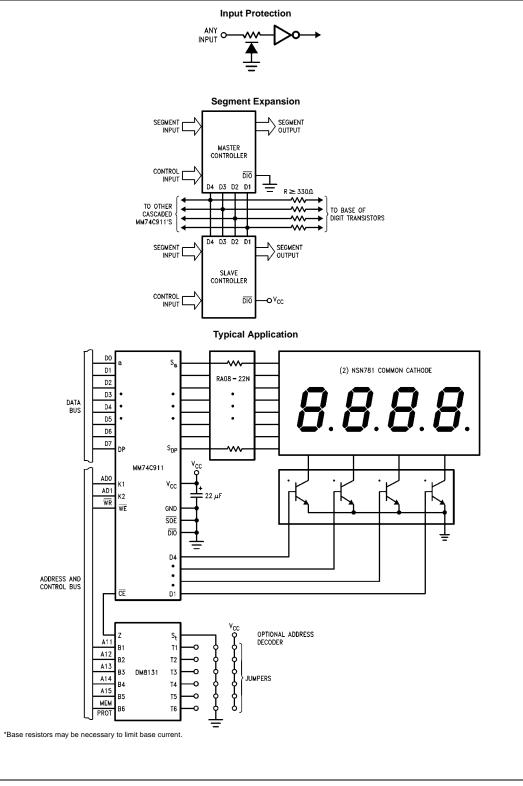

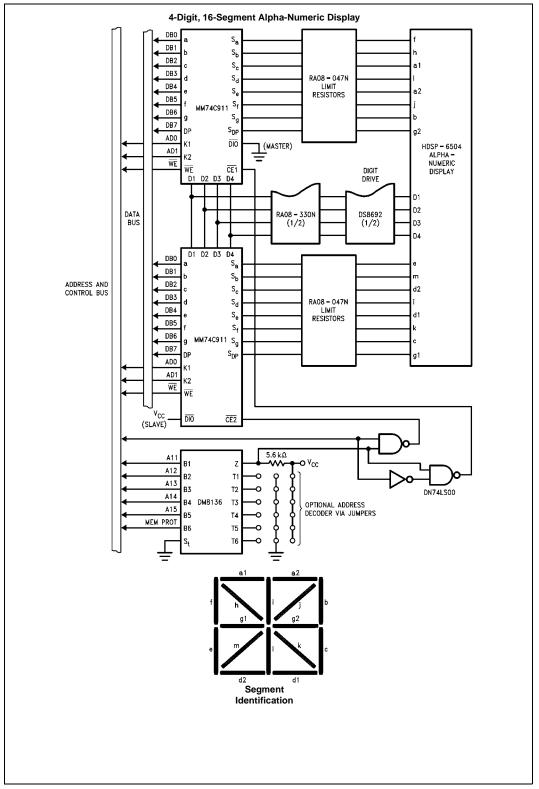

The MM74C911 display controller is an interface element with memory that drives a 4-digit, 8-segment LED display. The MM74C911 allows individual control of any segment in the 4-digit display. The number of segments per digit can be expanded without any external components. For example, two MM74C911's can be cascaded to drive a 16-segment alpha-numeric display.

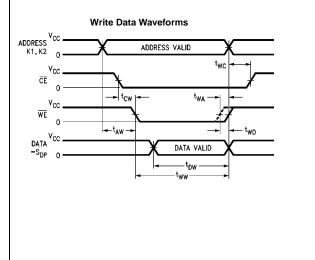

The display controllers receive data information through 8 data lines a, b...DP, and digit information through 2 address inputs K1 and K2. The input data is written into the register selected by the address information when  $\overrightarrow{CHIP}$  ENABLE,  $\overrightarrow{CE}$ , and  $\overrightarrow{WRITE}$  ENABLE,  $\overrightarrow{WE}$ , are LOW and is latched when either  $\overrightarrow{CE}$  or  $\overrightarrow{WE}$  return HIGH. Data hold time is not required.

A self-contained internal oscillator sequentially presents the stored data to high drive (100 mA typ.) 3-STATE output drivers which directly drive the LED display. The drivers are active when the control pin labeled SEGMENT OUTPUT ENABLE,  $\overline{\text{SOE}}$ , is LOW and go into 3-STATE when  $\overline{\text{SOE}}$  is HIGH. This feature allows for duty cycle brightness control, or for disabling the output drive for power conservation.

The digit outputs directly drive the base of the digit transistor when the control pin labeled  $\overrightarrow{\text{DIGIT INPUT OUTPUT}}$ ,  $\overrightarrow{\text{DIO}}$ , is LOW. When  $\overrightarrow{\text{DIO}}$  is HIGH, the digit lines turn into inputs and the internal scanning multiplexer is disabled.

When any digit line is forced HIGH by an external device, usually another MM74C911, the data information for that digit is presented to the output. In this manner, 16-segment alpha-numeric displays, 24- or 32-segment displays, or an array of discrete LED's can be controlled by the simple cascading of expandable segment display controllers. All inputs except digit inputs are TTL compatible and do not clamp input voltages above  $V_{CC}. \end{tabular}$

#### **Features**

- Direct segment drive (100 mA typ.) 3-STATE

- 4 registers addressed like RAM

- Internal oscillator and scanning circuit

- Direct base drive to digit transistor

- Segment expandability without external components

- TTL compatible inputs

- Power saver mode—5 µW (typ.)

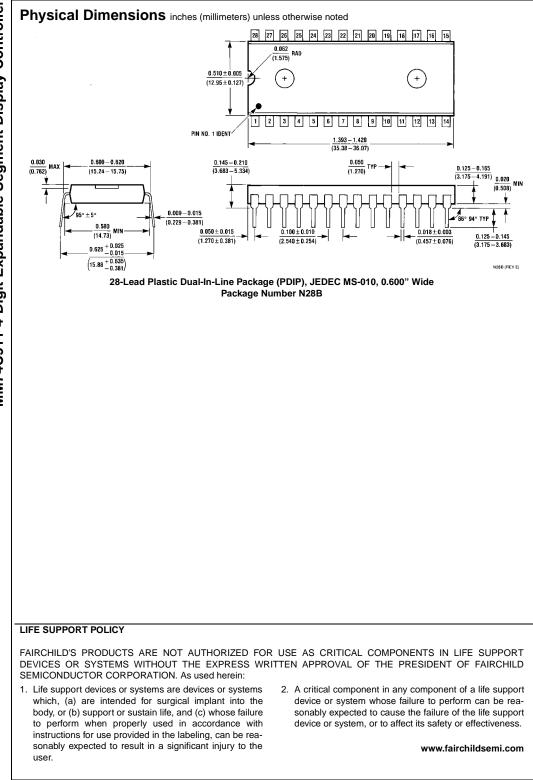

## **Ordering Code:**

| MM74C991N N28B 28-Lead Plastic Dua |                                                      |

|------------------------------------|------------------------------------------------------|

|                                    | II-In-Line Package (PDIP), JEDEC MS-010, 0.600" Wide |

## **Connection Diagram**

# MM74C911

**Truth Tables**

Input Control

| -  | r                   |    |   |                 |           |  |  |

|----|---------------------|----|---|-----------------|-----------|--|--|

| CE | Digit<br>CE Address |    | - |                 | Operation |  |  |

|    | K2                  | K1 |   | -               |           |  |  |

| 0  | 0                   | 0  | 0 | Write Digit 1   |           |  |  |

| 0  | 0                   | 0  | 1 | Latch Digit 1   |           |  |  |

| 0  | 0                   | 1  | 0 | Write Digit 2   |           |  |  |

| 0  | 0                   | 1  | 1 | Latch Digit 2   |           |  |  |

| 0  | 1                   | 0  | 0 | Write Digit 3   |           |  |  |

| 0  | 1                   | 0  | 1 | Latch Digit 3   |           |  |  |

| 0  | 1                   | 1  | 0 | Write Digit 4   |           |  |  |

| 0  | 1                   | 1  | 1 | Latch Digit 4   |           |  |  |

| 1  | Х                   | Х  | х | Disable Writing |           |  |  |

### **Functional Description**

The MM74C911 display controller is manufactured on standard metal gate CMOS technology. A single 5V 74 series TTL supply can be used for power and should be bypassed at the V<sub>CC</sub> pin to suppress current transients.

The digit outputs directly drive the base of a grounded emitter digit transistor without the need of a Darlington configuration. If an MM74C911 is driving a digit transistor and also supplying digit information to a cascaded MM74C911, base resistors are needed in the digit transistors to provide an adequate high level to the digit inputs of the cascaded MM74C911.

As seen in the Block Diagram, these display controllers contain four 8-bit registers; any one may be randomly writ-

**Output Control**

| ſ | DIO | SOE | Digit Lines |    |    | s  | Operation               |

|---|-----|-----|-------------|----|----|----|-------------------------|

|   |     |     | D4          | D3 | D2 | D1 |                         |

|   | 0   | 0   | R           | R  | R  | R  | Refresh Display         |

|   | 0   | 1   | R           | R  | R  | R  | Disable Segment Outputs |

|   | 1   | 0   | 0           | 0  | 0  | 0  | Digits Are Now Inputs   |

|   | 1   | 0   | 0           | 0  | 0  | 1  | Display Digit 1         |

|   | 1   | 0   | 0           | 0  | 1  | 0  | Display Digit 2         |

|   | 1   | 0   | 0           | 1  | 0  | 0  | Display Digit 3         |

|   | 1   | 0   | 1           | 0  | 0  | 0  | Display Digit 4         |

|   | 1   | 1   | 0           | 0  | 0  | 0  | Power Saver Mode        |

$$\label{eq:R} \begin{split} &\mathsf{R} = \mathsf{R} \mathsf{e} \mathsf{f} \mathsf{r} \mathsf{e} \mathsf{s} \mathsf{h} \; (\mathsf{digit} \; \mathsf{lines} \; \mathsf{sequentially} \; \mathsf{pulsed}) \\ &\mathsf{X} = \mathsf{D} \mathsf{on't} \; \mathsf{C} \mathsf{are} \end{split}$$

ten into. In normal operation, the internal multiplexer scans the registers and refreshes the display. In cascaded operation, 1 MM74C911 serves as a master refresh device and cascaded MM74C911's are slaved to it through digit lines operating as inputs.

The MM74C911 appears to a microprocessor as memory and to the user as a self-scan display. Since every segment is under microprocessor control, great versatility is obtained.

Low power standby operation occurs with both  $\overline{\text{SOE}}$  and  $\overline{\text{DIO}}$  inputs HIGH. This condition forces the MM74C911 to a quiescent state typically drawing less than 1  $\mu$ A of supply current with a standby supply voltage as low as 3V.

| Absolute Maximu                                                  | m Ratings(Note 1)                                                        | Operating V <sub>CC</sub> Range                                                                                                                                                                                                                    |  |  |  |

|------------------------------------------------------------------|--------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| (Note 2)                                                         | -                                                                        | Absolute Maximum V <sub>CC</sub>                                                                                                                                                                                                                   |  |  |  |

| Voltage at Any Pin<br>except Inputs                              | $-0.3 \text{V}$ to $\text{V}_{\text{CC}} + 0.3 \text{V}$                 | Lead Temperature<br>(Soldering, 10 seconds)                                                                                                                                                                                                        |  |  |  |

| Voltage at Any Input<br>except Digits<br>Operating Temperature   | -0.3V to +15V                                                            | Note 1: "Absolute Maximum Ratings" are those values be<br>safety of the device cannot be guaranteed. Except for "Op<br>they are not meant to imply that the device should be opera<br>its. The table of "Electrical Characteristics" provides cond |  |  |  |

| Range, (T <sub>A</sub> )                                         | -40°C to +85°C                                                           | device operation.                                                                                                                                                                                                                                  |  |  |  |

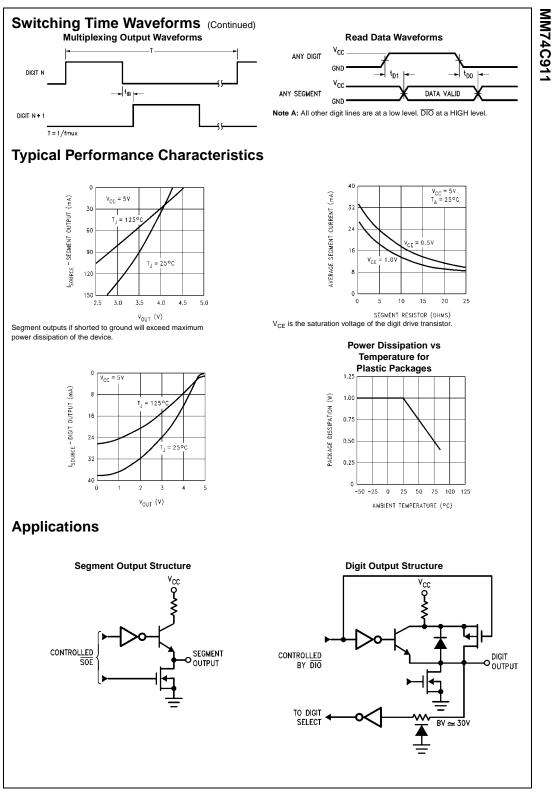

| Storage Temperature Range<br>Power Dissipation (P <sub>D</sub> ) | $-65^{\circ}C$ to $+150^{\circ}C$ Refer to $P_{D(MAX)}$ vs $T_{A}$ Graph | Note 2: All voltage reference to ground.                                                                                                                                                                                                           |  |  |  |

## 3V to 6V 6.5V 260°C

MM74C911

beyond which the Operating Range", prated at these lim-onditions for actual

## **DC Electrical Characteristics**

| Symbol              | Parameter                    | Conditions                                                                          | Min                 | Тур    | Max | Units |

|---------------------|------------------------------|-------------------------------------------------------------------------------------|---------------------|--------|-----|-------|

| V <sub>IN(1)</sub>  | Logical "1" Input Voltage    | $V_{CC} = 5V$                                                                       | 3.0                 |        |     | V     |

| V <sub>IN(0)</sub>  | Logical "0" Input Voltage    |                                                                                     |                     |        | 1.5 | V     |

| I <sub>IN(1)</sub>  | Logical "1" Input Current    | $V_{CC} = 5V, V_{IN} = 15V$                                                         |                     | 0.005  | 1.0 | μA    |

| I <sub>IN(0)</sub>  | Logical "0" Input Current    | $V_{CC} = 5V, V_{IN} = 0V$                                                          | -1.0                | -0.005 |     | μA    |

| I <sub>CC</sub>     | Supply Current (Normal)      | V <sub>CC</sub> = 5V, Outputs Open                                                  |                     | 0.50   | 2.5 | mA    |

| I <sub>CC</sub>     | Supply Current (Power Saver) | $V_{CC} = 5V$ , $\overline{SOE}$ , $\overline{DIO} = "1"$ ,<br>D1, D2, D3, D4 = "0" |                     | 1      | 600 | μΑ    |

| I <sub>OUT</sub>    | 3-STATE Output Current       | V <sub>O</sub> = 5V                                                                 |                     | 0.03   | 10  | μA    |

|                     |                              | $V_{O} = 0V$                                                                        | -10                 | -0.03  |     |       |

| CMOS/LPT            | TL INTERFACE                 |                                                                                     |                     |        |     |       |

| V <sub>IN(1)</sub>  | Logical "1" Input Voltage    | V <sub>CC</sub> = 4.75V                                                             | V <sub>CC</sub> – 2 |        |     | V     |

| V <sub>IN(0)</sub>  | Logical "0" Input Voltage    | V <sub>CC</sub> = 4.75V                                                             |                     |        | 0.8 | V     |

| OUTPUT D            | RIVE                         |                                                                                     |                     |        |     |       |

| I <sub>SH</sub>     | HIGH Level Segment Current   | $V_{CC} = 5V, V_{O} = 3.4V$                                                         |                     |        |     |       |

|                     |                              | $T_J = 25^{\circ}C$                                                                 | -60                 | -100   |     | mA    |

|                     |                              | $T_J = 100^{\circ}C$                                                                | -40                 | -60    |     | mA    |

| I <sub>DH</sub>     | HIGH Level Digit Current     | $V_{CC} = 5V, V_{O} = 3V$                                                           |                     |        |     |       |

|                     |                              | $T_J = 25^{\circ}C$                                                                 | -10                 | -20    |     | mA    |

|                     |                              | $T_J = 100^{\circ}C$                                                                | -7                  | -10    |     | mA    |

|                     |                              | $V_{CC} = 5V, V_{O} = 1V$                                                           |                     |        |     |       |

|                     |                              | $T_J = 25^{\circ}C$                                                                 | -15                 | -40    |     | mA    |

|                     |                              | $T_J = 100^{\circ}C$                                                                | -10                 | -15    |     | mA    |

| V <sub>OUT(1)</sub> | Logical "1" Output Voltage,  | $V_{CC} = 5V, I_{O} = -360 \mu A$                                                   | 4.6                 |        |     | V     |

|                     | Any Digit                    |                                                                                     |                     |        |     |       |

| V <sub>OUT(0)</sub> | Logical "0" Output Voltage,  | $V_{CC} = 5V, I_{O} = 360 \ \mu A$                                                  |                     |        | 0.4 | V     |

| . /                 | Any Output                   |                                                                                     |                     |        |     |       |

| θ,ιΑ                | Thermal Resistance           | (Note 3)                                                                            |                     | 100    |     | °C/W  |

| Symbol                            | $t_r = t_f = 20 \text{ ns}, C_L = 50 \text{ pF}$ | Conditions                                 | Min | Тур | Max  | Un |

|-----------------------------------|--------------------------------------------------|--------------------------------------------|-----|-----|------|----|

|                                   |                                                  |                                            |     |     | WIAA | _  |

| t <sub>CW</sub>                   | Chip Enable to Write Enable Set-Up Time          | $T_J = 25^{\circ}C$                        | 35  | 15  |      | n  |

|                                   |                                                  | T <sub>J</sub> = 125°C                     | 50  | 20  |      | n  |

| t <sub>AW</sub>                   | Address to Write Enable Set-Up Time              | $T_J = 25^{\circ}C$                        | 35  | 15  |      | n  |

|                                   |                                                  | $T_J = 125^{\circ}C$                       | 50  | 20  |      | n  |

| t <sub>WW</sub>                   | Write Enable Width                               | $T_J = 25^{\circ}C$                        | 400 | 225 |      | n  |

|                                   |                                                  | $T_J = 125^{\circ}C$                       | 450 | 250 |      | n  |

| t <sub>DW</sub>                   | Data to Write Enable Set-Up Time                 | $T_J = 25^{\circ}C$                        | 390 | 225 |      | n  |

|                                   |                                                  | $T_J = 125^{\circ}C$                       | 430 | 250 |      | n  |

| t <sub>WD</sub>                   | Write Enable to Data Hold Time                   | $T_J = 25^{\circ}C$                        | 0   | -10 |      | n  |

|                                   |                                                  | $T_J = 125^{\circ}C$                       | 0   | -15 |      | n  |

| t <sub>WA</sub>                   | Write Enable to Address Hold Time                | $T_J = 25^{\circ}C$                        | 0   | -10 |      | n  |

|                                   |                                                  | $T_J = 125^{\circ}C$                       | 0   | -15 |      | n  |

| t <sub>WC</sub>                   | Write Enable to Chip Enable Hold Time            | $T_J = 25^{\circ}C$                        | 55  | 30  |      | n  |

|                                   |                                                  | $T_J = 125^{\circ}C$                       | 75  | 40  |      | n  |

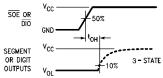

| t <sub>1H</sub> , t <sub>0H</sub> | Logical "1", Logical "0" Levels into 3-STATE     | R <sub>L</sub> =10k, C <sub>L</sub> =10 pF |     |     |      |    |

|                                   |                                                  | $T_J = 25^{\circ}C$                        |     | 275 | 500  | n  |

|                                   |                                                  | $T_J = 125^{\circ}C$                       |     | 325 | 600  | n  |

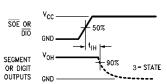

| t <sub>H1</sub> , t <sub>H0</sub> | 3-STATE to Logical "1" or                        | R <sub>L</sub> =10k, C <sub>L</sub> =10 pF |     |     |      |    |

|                                   | Logical "0" Levels                               | $T_J = 25^{\circ}C$                        |     | 325 | 600  | n  |

|                                   |                                                  | $T_J = 125^{\circ}C$                       |     | 375 | 700  | n  |

| t <sub>D1</sub> , t <sub>D0</sub> | Propagation Delay from Digit Input to            | $T_J = 25^{\circ}C$                        |     | 500 | 1000 | n  |

|                                   | Segment Output                                   | T <sub>J</sub> = 125°C                     |     | 700 | 1400 | n  |

| t <sub>IB</sub>                   | Interdigit Blanking Time                         | T <sub>J</sub> = 25°C                      | 5   | 10  | 1    | μ  |

|                                   |                                                  | T <sub>J</sub> = 125°C                     | 10  | 20  |      | μ  |

| f <sub>MUX</sub>                  | Multiplex Scan Frequency                         | T <sub>.1</sub> = 25°C                     |     | 525 | 1    | H  |

|                                   |                                                  | T <sub>1</sub> = 125°C                     |     | 375 |      | н  |

| C <sub>IN</sub>                   | Input Capacitance                                | (Note 5)                                   |     | 5   | 7.5  | p  |

| C <sub>OUT</sub>                  | 3-STATE Output Capacitance                       | (Note 5)                                   |     | 30  | 50   | p  |

Note 5: Capacitance guaranteed by periodic testing.

## Switching Time Waveforms

### 3-STATE Waveforms

5

**MM74C911**

MM74C911

Fairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications.