# DDR3 SDRAM Controller IP Core - Lattice Radiant Software

**User Guide**

FPGA-IPUG-02086-1.4

October 2020

#### Disclaimers

Lattice makes no warranty, representation, or guarantee regarding the accuracy of information contained in this document or the suitability of its products for any particular purpose. All information herein is provided AS IS and with all faults, and all risk associated with such information is entirely with Buyer. Buyer shall not rely on any data and performance specifications or parameters provided herein. Products sold by Lattice have been subject to limited testing and it is the Buyer's responsibility to independently determine the suitability of any products and to test and verify the same. No Lattice products should be used in conjunction with mission- or safety-critical or any other application in which the failure of Lattice's product could create a situation where personal injury, death, severe property or environmental damage may occur. The information provided in this document is proprietary to Lattice Semiconductor, and Lattice reserves the right to make any changes to the information in this document or to any products at any time without notice.

## Contents

| Acronyms in This Document                      | 5  |

|------------------------------------------------|----|

| 1. Introduction                                | 6  |

| 1.1. Quick Facts                               | 6  |

| 1.2. Features                                  | 6  |

| 1.3. Conventions                               | 7  |

| 1.3.1. Nomenclature                            | 7  |

| 1.3.2. Signal Names                            | 7  |

| 1.3.3. Attribute                               |    |

| 2. Functional Description                      | 8  |

| 2.1. Overview                                  | 8  |

| 2.2. Signal Description                        | 9  |

| 2.3. Attributes Summary                        | 11 |

| 2.4. Submodules Description                    | 17 |

| 2.4.1. DDR3 Memory Controller Module           | 17 |

| 2.4.2. DDR3 PHY Module                         | 17 |

| 2.5. Operations Details                        | 19 |

| 2.5.1. Initialization Control                  | 19 |

| 2.5.2. Command and Address                     | 19 |

| 2.5.3. User Commands                           | 21 |

| 2.5.4. WRITE                                   | 21 |

| 2.5.5. WRITEA                                  | 22 |

| 2.5.6. READ                                    | 22 |

| 2.5.7. READA                                   | 23 |

| 2.5.8. REFRESH Support                         | 23 |

| 2.6. Local-to-Memory Address Mapping           | 24 |

| 2.7. Mode register Programming                 | 25 |

| 3. Core Generation, Simulation, and Validation | 27 |

| 3.1. Licensing the IP                          | 27 |

| 3.2. Generation and Synthesis                  | 27 |

| 3.2.1. Required Post-Synthesis Constraints     | 30 |

| 3.3. Running Functional Simulation             | 30 |

| 3.4. Hardware Evaluation                       | 32 |

| 4. Ordering Part Number                        | 33 |

| Appendix A. Resource Utilization               | 34 |

| Appendix B. Limitation                         | 35 |

| References                                     | 36 |

| Technical Support Assistance                   | 37 |

| Revision History                               | 38 |

|                                                |    |

## Figures

| Figure 2.1. DDR3 SDRAM Controller IP Core Functional Diagram        | 8  |

|---------------------------------------------------------------------|----|

| Figure 2.2. Timing of Command and Address                           | 20 |

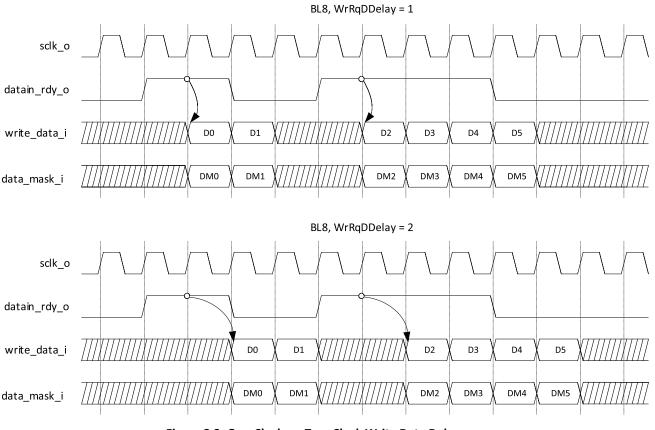

| Figure 2.3. One-Clock vs. Two-Clock Write Data Delay                | 22 |

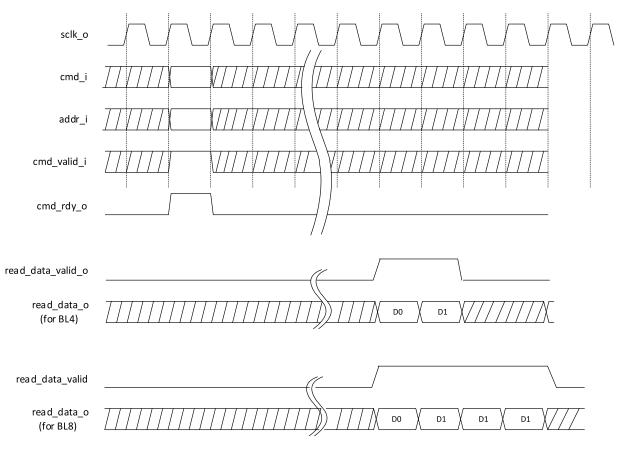

| Figure 2.4. User-Side Read Operation                                | 23 |

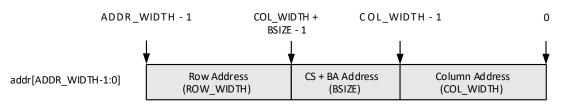

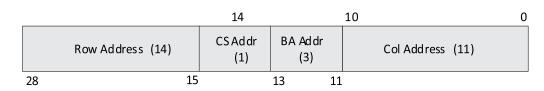

| Figure 2.5. Local-to-Memory Address Mapping for Memory Access       |    |

| Figure 2.6. Mapped Address for the Example                          | 24 |

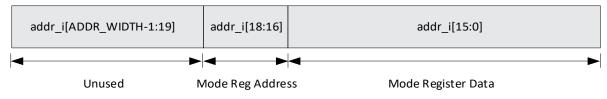

| Figure 2.7. User-to-Memory Address Mapping for MR Programming       |    |

| Figure 3.1. Module/IP Block Wizard                                  |    |

| Figure 3.2. Module/IP Block Wizard of DDR3 SDRAM Controller IP Core |    |

| Figure 3.3. Check Generating Result                                 | 29 |

| Figure 3.4. Simulation Wizard                                       | 30 |

| Figure 3.5. Adding and Reordering Source                            |    |

| Figure 3.6. Simulation Waveform                                     | 31 |

## Tables

| Table 1.1. Quick Facts                                             | 6  |

|--------------------------------------------------------------------|----|

| Table 2.1. DDR3 SDRAM Controller IP Core Signal Description        | 9  |

| Table 2.2. Attributes Table                                        | 11 |

| Table 2.3. Attributes Descriptions                                 | 14 |

| Table 2.4. Native Interface Functional Groups                      |    |

| Table 2.5. Defined User Commands                                   | 21 |

| Table 2.6. Address Mapping Example                                 | 24 |

| Table 2.7. Transmit MAC Statistics Vector                          | 25 |

| Table 2.8. Initialization Default Values for Mode Register Setting | 26 |

| Table 3.1. Generated File List                                     |    |

| Table A.1. Resource Utilization                                    | 34 |

|                                                                    |    |

## Acronyms in This Document

A list of acronyms used in this document.

| Acronym | Definition                                |

|---------|-------------------------------------------|

| DDR3    | Double Data Rate Type 3                   |

| JEDEC   | Joint Electron Device Engineering Council |

| SDRAM   | Synchronous Dynamic Random Access Memory  |

| FPGA    | Field Programmable Gate Array             |

| RTL     | Register Transfer Level                   |

## 1. Introduction

The Lattice Double Data Rate Synchronous Dynamic Random Access Memory (DDR3 SDRAM) Controller IP Core is a general-purpose memory controller that interfaces with industry standard DDR3 memory devices compliant with JESD79-3C, DDR3 SDRAM Standard. This IP provides a generic command interface to user applications.

DDR3 SDRAM Controller IP reduces the effort required to integrate the DDR3 memory controller with the user application design and minimizes the need to directly deal with the DDR3 memory interface.

This design is implemented in Verilog. It can be targeted to CrossLink<sup>™</sup>-NX and Certus<sup>™</sup>-NX FPGA devices and implemented using the Lattice Radiant<sup>®</sup> software Place and Route tool integrated with the Synplify Pro<sup>®</sup> synthesis tool.

## 1.1. Quick Facts

Table 1.1 presents a summary of the LIFCL DDR3 SDRAM Controller IP Core.

| Table | 1.1. | Quick | Facts |

|-------|------|-------|-------|

|-------|------|-------|-------|

| IP Requirements             | Supported FPGA Family    | CrossLink-NX, Certus-NX                                                          |  |  |

|-----------------------------|--------------------------|----------------------------------------------------------------------------------|--|--|

|                             | Targeted Devices         | LIFCL-40, LIFCL-17, LFD2NX-40                                                    |  |  |

| <b>Resource Utilization</b> | Supported User Interface | Native                                                                           |  |  |

|                             | Resources                | See Table A.1                                                                    |  |  |

| Design Tool Support         | Lattice Implementation   | IP Core v1.0.x – Lattice Radiant Design Suite 2.0                                |  |  |

|                             |                          | IP Core v1.1.x – Lattice Radiant Design Suite 2.1                                |  |  |

|                             | Curath a sig             | Lattice Synthesis Engine                                                         |  |  |

|                             | Synthesis                | Synopsys <sup>®</sup> Synplify Pro for Lattice                                   |  |  |

|                             | Simulation               | For a list of supported simulators, see the Lattice Radiant Software User Guide. |  |  |

## 1.2. Features

The key features of DDR3 SDRAM Controller IP Core include:

- Memory data path widths of 8, 16, 24, 32 bits

- Selectable gearing ratios: 4:1, 8:1

- x8 and x16 device configurations

- Programmable burst lengths of 8 (fixed), chopped 4 or 8 (on-the-fly), or chopped 4 (fixed)

- Programmable read and write CAS latency set

- Read burst type of nibble sequential or interleave

- Automatic DDR3 SDRAM initialization and refresh

- Automatic write levelling for each DQS

- Automatic read training for each DQS

- Power Down mode

- Dynamic On-Die Termination (ODT) controls

- Termination Data Strobe (TDQS) for x8 widths only

- I/O primitives manage read skews (read levelling equivalent)

- Automatic programmable interval refresh or user-initiated refresh

- Option for controlling memory reset outside the controller

The DDR3 SDRAM Controller IP Core supports the following devices:

- All LIFCL FPGA Family devices

- Interfaces to industry standard DDR3 SDRAM components and modules compliant with JESD79-3C, DDR3 SDRAM Standard

- Interfaces to DDR3 SDRAM at speeds up to 400 MHz/800 Mbps

## 1.3. Conventions

### 1.3.1. Nomenclature

The nomenclature used in this document is based on Verilog HDL.

### 1.3.2. Signal Names

Signal Names that end with:

- \_*n* are active low

- \_*i* are input signals

- \_*o* are output signals

- \_io are bi-directional input/output signals

#### 1.3.3. Attribute

The names of attributes in this document are formatted in title case and italicized (Attribute Name).

## 2. Functional Description

### 2.1. Overview

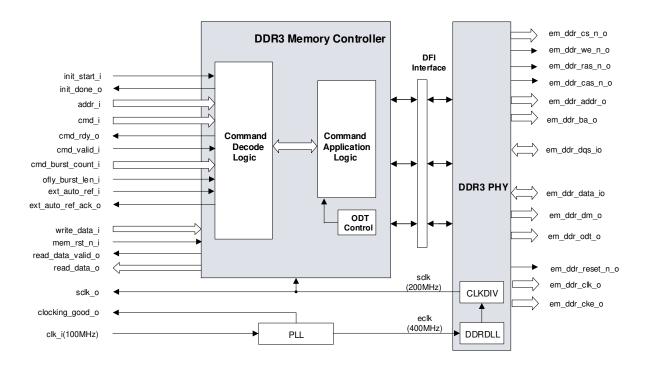

The DDR3 memory controller consists of three submodules: Memory Controller (MC) module, Physical Interface (PHY) module, and the Phase-Locked Loop (PLL) instance. The Submodules Description section briefly describes the operation of each of these submodules. Figure 2.1 provides a high-level block diagram illustrating the main functional blocks used to implement the DDR3 SDRAM Controller IP Core functions.

Figure 2.1. DDR3 SDRAM Controller IP Core Functional Diagram

## 2.2. Signal Description

Table 2.1 lists the input and output signals for DDR3 SDRAM Controller IP Core.

| Port Name           | I/O         | Width           | Description                                                                                                                                                                                                                     |  |  |

|---------------------|-------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Clock and Reset     |             |                 |                                                                                                                                                                                                                                 |  |  |

| clk_i <sup>4</sup>  | In          | 1               | Reference clock to the PLL                                                                                                                                                                                                      |  |  |

| clocking_good_o     | Out         | 1               | Signal from PLL indicating stable clock condition                                                                                                                                                                               |  |  |

| sclk_o <sup>4</sup> | Out         | 1               | System clock used by controller's core module                                                                                                                                                                                   |  |  |

|                     |             |                 | You may use this clock for DDR3 controller interface logic.                                                                                                                                                                     |  |  |

| rst_n_i             | In          | 1               | Asynchronous reset                                                                                                                                                                                                              |  |  |

|                     |             |                 | By default setting, this signal resets the entire IP core and the DDR3 memory when asserted.                                                                                                                                    |  |  |

| mem_rst_n_i         | In          | 1               | Asynchronous reset when <i>Controller Reset to Memory</i> is checked from Module/IP Block Wizard                                                                                                                                |  |  |

|                     |             |                 | Allows you to reset the memory device only. This signal does not reset the memory controller.                                                                                                                                   |  |  |

| em_ddr_reset_n_o    | Out         | 1               | Asynchronous reset signal from controller to the memory device                                                                                                                                                                  |  |  |

|                     |             |                 | Asserted by the controller for the duration of power on reset, or active<br>rst_n_i, or active mem_rst_n_i.                                                                                                                     |  |  |

| DDR3 SDRAM Memo     | ory Interfa | ce <sup>1</sup> |                                                                                                                                                                                                                                 |  |  |

| em_ddr_clk_o        | Out         | CLKO_WIDTH      | Memory clock generated by the controller                                                                                                                                                                                        |  |  |

| em_ddr_cke_o        | Out         | CKE_WIDTH       | Memory clock enable generated by the controller                                                                                                                                                                                 |  |  |

| em_ddr_addr_o       | Out         | ROW_WIDTH       | Memory address bus – multiplexed row and column address for the memory                                                                                                                                                          |  |  |

| em_ddr_ba_o         | Out         | 3               | Memory bank address                                                                                                                                                                                                             |  |  |

| em_ddr_data_io      | In/Out      | DATA_WIDTH      | Memory bi-directional data bus                                                                                                                                                                                                  |  |  |

| em_ddr_dm_o         | Out         | DATA_WIDTH/8    | DDR3 memory write data mask – to mask the byte lanes for byte-level write                                                                                                                                                       |  |  |

| em_ddr_dqs_io       | In/<br>Out  | DQS_WIDTH       | Memory bi-directional data strobe                                                                                                                                                                                               |  |  |

| em_ddr_cs_n_o       | Out         | CS_WIDTH        | Memory chip select                                                                                                                                                                                                              |  |  |

| em_ddr_cas_n_o      | Out         | 1               | Memory column address strobe                                                                                                                                                                                                    |  |  |

| em_ddr_ras_n_o      | Out         | 1               | Memory row address strobe                                                                                                                                                                                                       |  |  |

| em_ddr_we_n_o       | Out         | 1               | Memory write enabl                                                                                                                                                                                                              |  |  |

| em_ddr_odt_o        | Out         | CS_WIDTH        | High Output Memory on-die termination control                                                                                                                                                                                   |  |  |

| Native Interface    |             |                 |                                                                                                                                                                                                                                 |  |  |

| init_start_i        | In          | 1               | Initialization start request                                                                                                                                                                                                    |  |  |

|                     |             |                 | Should be asserted to initiate memory initialization either right after the power-on reset or before sending the first user command to the memory controller.                                                                   |  |  |

| init_done_o         | Out         | 1               | Initialization done output                                                                                                                                                                                                      |  |  |

|                     |             |                 | Asserted for one clock period after the core completes memory initialization<br>and write levelling. When sampled high, the input signal init_start_i must be<br>immediately deasserted at the same edge of the sampling clock. |  |  |

| cmd_valid_i         | In          | 1               | Command and address valid input<br>When asserted, the addr_i, cmd_i and cmd_burst_cnt_i inputs are                                                                                                                              |  |  |

|                     |             |                 | considered valid.                                                                                                                                                                                                               |  |  |

| cmd_rdy_o           | Out         | 1               | Command ready output                                                                                                                                                                                                            |  |  |

|                     |             |                 | When asserted, indicates that the core is ready to accept the next command<br>and the corresponding address. This signal is active for one clock period.                                                                        |  |  |

| cmd_i               | In          | 4               | User command input to the memory controller                                                                                                                                                                                     |  |  |

|                     |             |                 |                                                                                                                                                                                                                                 |  |  |

#### Table 2.1. DDR3 SDRAM Controller IP Core Signal Description

© 2019-2020 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

| Port Name                 | I/O | Width      | Description                                                                                                                                                                                                                                                                                                                                  |

|---------------------------|-----|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| cmd_burst_cnt_i           | In  | 5          | Command burst count input<br>Indicates the number of times a given read or write command is to be<br>repeated by the controller automatically. Controller also generates the<br>address for each repeated command sequentially as per the burst length of<br>the command. Burst range is from 1 to 32 and <i>0</i> indicates 32 repetitions. |

| ofly_burst_len_i          | In  | 1          | On-the-fly burst length for current command<br>0 = BC4<br>1 = BL8<br>This input is valid only if Mode Reg0 is set for on-the-fly mode. If set, this<br>input is sampled when cmd_valid_i and cmd_rdy_o are high.                                                                                                                             |

| addr_i <sup>2</sup>       | In  | ADDR_WIDTH | User read or write address input to the memory controller<br>Refer the section Local-to-Memory Address Mapping for further details.                                                                                                                                                                                                          |

| datain_rdy_o              | Out | 1          | Data ready output<br>When asserted, indicates the core is ready to receive the write data.                                                                                                                                                                                                                                                   |

| write_data_i <sup>3</sup> | In  | DSIZE      | Write data input from user logic to the memory controller<br>The user side write data width is four times the memory data bus.                                                                                                                                                                                                               |

| data_mask_i <sup>3</sup>  | In  | DSIZE/8    | Data mask input for write data<br>Each bit masks a corresponding byte of local write data.                                                                                                                                                                                                                                                   |

| read_data_o <sup>3</sup>  | Out | DSIZE      | Read data output from memory controller to the user logic.                                                                                                                                                                                                                                                                                   |

| read_data_valid_o         | Out | 1          | Read data valid output<br>When asserted, indicates the data on the read_data_o bus is valid.                                                                                                                                                                                                                                                 |

| ext_auto_ref_i            | In  | 1          | Refresh user request<br>This signal is available only when the <i>External Auto Refresh Port</i> attribute is<br>selected in the Module/IP Block Wizard.                                                                                                                                                                                     |

| ext_auto_ref_ack_o        | Out | 1          | Completion of memory refresh in response to ext_auto_ref_i signal assertion.<br>This pin is available only when the <i>External Auto Refresh Port</i> is checked in<br>the Module/IP Block Wizard.                                                                                                                                           |

| wl_err_o                  | Out | 1          | Write levelling error<br>Indicates failure in write levelling. The controller does not work properly if<br>there is a write levelling error. This signal should be checked when<br>init_done_o signal is asserted.                                                                                                                           |

| rt_err_o                  | Out | 1          | Read Training error<br>Indicates failure in Read Training process. The controller does not work<br>properly if there is a Read Training error. This signal should be checked when<br>init_done signal is asserted.                                                                                                                           |

Notes:

1. The bit width of some DDR3 SDRAM Memory Interface signals are set by the attributes. Refer to Table 2.3 for the description of these attributes.

2. The bit width of addr\_i is set by ADDR\_WIDTH which is defined in Local-to-Memory Address Mapping section.

3. The bit width of write\_data\_i, data\_mask\_i, and read\_data\_o are set by DSIZE which is 4 \* DATA\_WIDTH for 4:1 gearing ratio and 8 \* DATA\_WIDTH for 8:1 gearing ratio.

4. The clk\_i and sclk\_o signals are named clk\_in\_i and sclk\_out\_o respectively in the IP Core v1.0.1 or earlier.

© 2019-2020 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

## 2.3. Attributes Summary

The configurable attributes of the DDR3 SDRAM Controller IP Core are shown in Table 2.2 and are described in Table 2.3. The attributes can be configured through the IP Catalog's Module/IP Block Wizard of the Lattice Radiant software. The attributes are arranged into tabs and related attributes are collected into groups. The 3 tabs are as follows:

General Tab

The General tab contains the attributes for configuring the target memory device and the IP Core features. These attributes are static; they can only be set in the Module/IP Block Wizard. The DDR3 SDRAM Controller IP Core must be regenerated to change the features set by these attributes.

• Memory Device Setting Tab

The Memory Device Setting Tab contains the attributes for configuring the target memory device/module. The attributes under Mode Register Initial Setting Group are dynamic, which means, reset values are set from Module/IP Block Wizard and are dynamically changeable using LOAD\_MR user commands. Refer to JESD79-3, DDR3 SDRAM Standard, for allowed values.

• Memory Device Timing Tab

The attribute default displayed in this tab are the default values of the Micron DDR3 1Gb-25E memory module. These attributes can be modified by checking the Manual Adjust attribute. It is important that the attribute values in this tab are adjusted to the timing parameters of the memory device for the target application. The DDR3 SDRAM Controller IP Core also uses these timing parameters when generating memory commands.

| Attribute Selectable Values      |                                                                                                                                                                                                         | Default                 | Dependency on Other Attributes            |  |

|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-------------------------------------------|--|

| General Tab                      | •                                                                                                                                                                                                       |                         |                                           |  |

| Device Information Group         |                                                                                                                                                                                                         |                         |                                           |  |

| Interface Type                   | DDR3, DDR3L                                                                                                                                                                                             | DDR3                    | -                                         |  |

| Gearing Ratio                    | 4:1, 8:1                                                                                                                                                                                                | 8:1                     | -                                         |  |

| I/O Buffer Type                  | SSTL15_I, SSTL15_II                                                                                                                                                                                     | SSTL15_I                | If Interface Type == DDR3                 |  |

|                                  | SSTL135_I, SSTL135_II                                                                                                                                                                                   | SSTL135_I               | If Interface Type == DDR3L                |  |

| Select Memory                    | Micron DDR3 1Gb-25E,<br>Micron DDR3 2Gb-25E,<br>Micron DDR3 4Gb-25E,<br>Custom                                                                                                                          | Micron DDR3<br>1Gb-25E  | If Gearing Ratio == 4:1                   |  |

|                                  | Micron DDR3 1Gb-187E,<br>Micron DDR3 2Gb-187E,<br>Micron DDR3 4Gb-187E,<br>Custom                                                                                                                       | Micron DDR3<br>1Gb-187E | If Gearing Ratio == 8:1                   |  |

| Clock Settings Group             | ·                                                                                                                                                                                                       |                         |                                           |  |

| Enable PLL                       | Checked                                                                                                                                                                                                 | Checked                 | Display only                              |  |

| PLL Reference Clock from Pin     | Checked, Unchecked                                                                                                                                                                                      | Checked                 | _                                         |  |

| I/O Standard for Reference Clock | LVDS, SUBLVDS, SLVS,<br>HSTL15_I, HSTL15D_I,<br>LVTTL33, LVCMOS33,<br>LVCMOS25, LVCMOS18,<br>LVCMOS18H, HSTL15D_I,<br>LVCMOS15, LVCMOS15H,<br>LVCMOS12, LVCMOS12H,<br>LVCMOS10H, LVCMOS10,<br>LVCMOS10R | SLVS                    | _                                         |  |

| RefClock (MHz)                   | 25, 50, 75, 100, 111, 125,<br>150                                                                                                                                                                       | 100                     | -                                         |  |

| MemClock (MHz)                   | 300, 333, 400, 533                                                                                                                                                                                      | 400                     | If Gearing Ratio == 8:1, 533 is available |  |

#### Table 2.2. Attributes Table

<sup>© 2019-2020</sup> Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

| Attribute                          | Selectable Values Default                       |                    | Dependency on Other Attributes                                                                                                                                                                                                                                      |  |

|------------------------------------|-------------------------------------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Memory Configuration Group         |                                                 |                    | · ·                                                                                                                                                                                                                                                                 |  |

| Memory Type                        | On-board Memory                                 | On-board<br>Memory | -                                                                                                                                                                                                                                                                   |  |

| Memory Data Bus Size               | s Size 8, 16, 24, 32                            |                    | Selectable values may change depending on the target device.                                                                                                                                                                                                        |  |

| Configuration                      | X8, X16                                         | X8                 | x16 is available when <i>Memory Data Bus</i><br><i>Size</i> is 16 or 32                                                                                                                                                                                             |  |

| Rank Size                          | Single, Dual                                    | Single             | If <i>Memory Data Bus Size</i> == 32, fixed to<br>Single due to limited I/O resource                                                                                                                                                                                |  |

|                                    | 1, 2                                            | 1                  | If Rank Size == Single: [1, 2]                                                                                                                                                                                                                                      |  |

| Clock Width                        | [2,4]                                           | 2                  | If Rank Size == Dual: [2, 4]                                                                                                                                                                                                                                        |  |

|                                    | Calculated based on Rank                        | 1                  | If Rank Size == Single: 1                                                                                                                                                                                                                                           |  |

| CKE Width                          | Size                                            | 2                  | If Rank Size == Dual: 2                                                                                                                                                                                                                                             |  |

| Local Interface                    |                                                 |                    |                                                                                                                                                                                                                                                                     |  |

| Local Bus Type                     | Native                                          | Native             | Display only                                                                                                                                                                                                                                                        |  |

| Additional Configuration Group     |                                                 |                    |                                                                                                                                                                                                                                                                     |  |

| Data ready to Write Data delay     | 1, 2                                            | 1                  | Display only                                                                                                                                                                                                                                                        |  |

| 2T Mode                            | Checked/Unchecked                               | Unchecked          | Rank Size == 2                                                                                                                                                                                                                                                      |  |

| Write levelling                    | Checked/Unchecked                               | Checked            | _                                                                                                                                                                                                                                                                   |  |

| Controller reset to Memory         | Checked/Unchecked                               | Unchecked          | -                                                                                                                                                                                                                                                                   |  |

| Memory Device Setting Tab          |                                                 |                    |                                                                                                                                                                                                                                                                     |  |

| Address Group                      |                                                 |                    |                                                                                                                                                                                                                                                                     |  |

| Row Size                           | 13, 14, 15, 16                                  | 14                 | <ul> <li>Default value is set by Select Memory:</li> <li>Micron DDR3 1Gb-&lt;25E,187E&gt;:14</li> <li>Micron DDR3 2Gb-&lt;25E,187E&gt;:15</li> <li>Micron DDR3 4Gb-&lt;25E,187E&gt;:16</li> <li>Custom: 13</li> <li>Editable when Select Memory = Custom</li> </ul> |  |

| Column Size                        | 10, 11, 12                                      | 10                 | Editable when <i>Select Memory</i> = Custom                                                                                                                                                                                                                         |  |

| Auto Refresh Control Group         |                                                 |                    |                                                                                                                                                                                                                                                                     |  |

| Auto Refresh Burst Count           | 1, 2, 3, 4, 5, 6, 7, 8                          | 8                  | _                                                                                                                                                                                                                                                                   |  |

| External Auto Refresh Port         | Checked/Unchecked                               | Unchecked          | _                                                                                                                                                                                                                                                                   |  |

| Mode Register Initial Setting Grou |                                                 |                    |                                                                                                                                                                                                                                                                     |  |

| Burst Length                       | Fixed 4 (BC4), Fixed 8<br>(BL8), On the fly     | Fixed 8 (BL8)      | -                                                                                                                                                                                                                                                                   |  |

| CAS Latency                        | 5, 6, 7, 8                                      |                    | Selectable values and default are updated based on <i>Select Memory</i> and <i>MemClock</i> .                                                                                                                                                                       |  |

| Burst Type                         | Sequential/Interleave                           | Sequential         | -                                                                                                                                                                                                                                                                   |  |

| Write Recovery                     | 5, 6, 7, 8, 10, 12                              | 6                  | If <i>MemClock</i> == 533, minimum value and default value are both 8                                                                                                                                                                                               |  |

| DLL Control for PD                 | Slow Exit/Fast Exit                             | Slow Exit          | —                                                                                                                                                                                                                                                                   |  |

| ODI Control                        | RZQ/6, RZQ/7                                    | RZQ/6 —            |                                                                                                                                                                                                                                                                     |  |

| RTT_Nom (Ohm)                      | RZQ/2, RZQ/4, RZQ/6,<br>RZQ/8, RZQ/12, Disabled | RZQ/6              | -                                                                                                                                                                                                                                                                   |  |

| Additive Latency                   | 0, CL-1, CL-2                                   | 0                  | -                                                                                                                                                                                                                                                                   |  |

| CAS Write Latency                  | 5, 6, 7, 8, 10, 12                              | 5                  | Selectable values and default are updated based on <i>Select Memory</i> and <i>MemClock</i> .                                                                                                                                                                       |  |

|                                    | RZQ/2, RZQ/4, Off                               | RZQ/4              | _                                                                                                                                                                                                                                                                   |  |

<sup>© 2019-2020</sup> Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

| NA                               |                                    |           | Dependency on Other Attributes                                                                                                                                                                                                                  |

|----------------------------------|------------------------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Memory Device Timing Tab         |                                    |           |                                                                                                                                                                                                                                                 |

| Command and Address Timing G     | iroup                              |           |                                                                                                                                                                                                                                                 |

| Manually Adjust                  | Checked/Unchecked                  | Unchecked | _                                                                                                                                                                                                                                               |

| TRTP (tCLK)                      | 4–65536                            | 4         | Enabled when Manually Adjust is Checked                                                                                                                                                                                                         |

| TWTR (tCLK)                      | 4–65536                            | 4         | Enabled when Manually Adjust is Checked                                                                                                                                                                                                         |

| TMRD(tCLK)                       | 4–65536                            | 4         | Enabled when Manually Adjust is Checked                                                                                                                                                                                                         |

| TMOD (tCLK)                      | 12-65536                           | 12        | Enabled when Manually Adjust is Checked                                                                                                                                                                                                         |

| TRCD (tCLK)                      | 4–65536                            | 6         | Enabled when Manually Adjust is Checked                                                                                                                                                                                                         |

| TRP (tCLK)                       | 4–65536                            | 6         | Enabled when Manually Adjust is Checked                                                                                                                                                                                                         |

| TRC (tCLK)                       | 15-65536                           | 20        | Enabled when Manually Adjust is Checked                                                                                                                                                                                                         |

| TRAS (tCLK)                      | 12-65536                           | 15        | Enabled when Manually Adjust is Checked                                                                                                                                                                                                         |

| TFAW (tCLK)                      | 12-65536                           | 16        | Enabled when Manually Adjust is Checked                                                                                                                                                                                                         |

| TRRD (tCLK)                      | 4–65536                            | 4         | Enabled when Manually Adjust is Checked                                                                                                                                                                                                         |

| Calibration Timing Group         |                                    |           |                                                                                                                                                                                                                                                 |

| TZQINIT(tCLK)                    | 512-65536                          | 512       | Enabled when Manually Adjust is Checked                                                                                                                                                                                                         |

| TZQCS (tCLK)                     | 64–65536                           | 64        | Enabled when Manually Adjust is Checked                                                                                                                                                                                                         |

| TZQOPER (tCLK)                   | 256-65536                          | 256       | Enabled when Manually Adjust is Checked                                                                                                                                                                                                         |

| Refresh, Reset and Power Down    | Timing Group                       | ·         |                                                                                                                                                                                                                                                 |

| TCKE (tCLK)                      | 3–65536                            | 3         | Enabled when Manually Adjust is Checked                                                                                                                                                                                                         |

| TRFC (tCLK)                      | 44–28080                           | 44        | <ul> <li>Enabled when <i>Manually Adjust</i> is Checked</li> <li>Default value is set by <i>Select Memory</i>:</li> <li>Micron DDR3 1Gb-25E:44</li> <li>Micron DDR3 2Gb-25E:64</li> <li>Micron DDR3 4Gb-25E:104</li> <li>Custom: 140</li> </ul> |

| TCKESR (tCLK)                    | 4–65536                            | 4         | Enabled when Manually Adjust is Checked                                                                                                                                                                                                         |

| TPD (tCLK)                       | 3–65536                            | 3         | Enabled when Manually Adjust is Checked                                                                                                                                                                                                         |

| TXPDLL (tCLK)                    | 10–65536                           | 10        | Enabled when Manually Adjust is Checked                                                                                                                                                                                                         |

| TXPR (tCLK)                      | 48–65536                           | 48        | Enabled when <i>Manually Adjust</i> is Checked<br>Default value is set by <i>Select Memory</i> :<br>• Micron DDR3 1Gb-25E:48<br>• Micron DDR3 2Gb-25E:68<br>• Micron DDR3 4Gb-25E:108<br>Custom: 144                                            |

| TREFI (tCLK)                     | 44-4160                            | 3120      | Enabled when Manually Adjust is Checked                                                                                                                                                                                                         |

| Write levelling and ODT Timing ( | Group                              | ·         |                                                                                                                                                                                                                                                 |

| TWLMRD (tCLK)                    | 40–65536                           | 40        | Enabled when Manually Adjust is Checked                                                                                                                                                                                                         |

| TWLDQSEN (tCLK)                  |                                    |           | Enabled when Manually Adjust is Checked                                                                                                                                                                                                         |

| TWLO (ns)                        | 0–9 4 Enabled when Manually Adjust |           | Enabled when Manually Adjust is Checked                                                                                                                                                                                                         |

|                                  | 4 4 Display only                   |           |                                                                                                                                                                                                                                                 |

| ODTH4 (tCLK)                     | 4                                  | 4         | Display only                                                                                                                                                                                                                                    |

#### Table 2.3. Attributes Descriptions

| Attribute                            | Description                                                                                                                                                                                                                                                                                                                                                                   |

|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| General Tab                          |                                                                                                                                                                                                                                                                                                                                                                               |

| Device Information Group             |                                                                                                                                                                                                                                                                                                                                                                               |

| Interface Type                       | Specifies the DDR3 Memory interface: DDR3 or DDR3L.                                                                                                                                                                                                                                                                                                                           |

| Select Memory                        | Some attribute default values are dependent on this attribute. The Micron DDR3 1GB -25E is provided as the default DDR3 memory device, the timing parameters of this memory device are listed in the Memory Device Timing tab as default values. The other available options are: Micron DDR3 2Gb-25E and Micron DDR3 4Gb-25E.                                                |

| RefClock (MHz)                       | Specifies the reference input clock to PLL which generates the system clock (sclk_o) and memory clock (em_ddr_clk_o).                                                                                                                                                                                                                                                         |

| MemClock (MHz)                       | Specifies the frequency of the memory clock to memory device. The allowed values are 300 MHz, 333 MHz and 400 MHz. The default value is linked to the speed grade of Lattice device selected. This is the PLL output frequency which depends on the corresponding value of RefClock. For example, for MemClock value of 333 MHz the PLL RefClock should be set to 111 MHz.    |

| Memory Configuration Group           |                                                                                                                                                                                                                                                                                                                                                                               |

| Memory Type                          | This attribute is for information only. Only On-board Memory type is supported.                                                                                                                                                                                                                                                                                               |

| Memory Data Bus Size<br>(DATA_WIDTH) | Specifies the bit width of DDR3 data bus (em_ddr_data_io). If the memory module has a wider data bus than required, only the required data width should be selected.                                                                                                                                                                                                          |

| Configuration                        | Selects the device configuration of the on-board memory. The memory controller supports device configurations x8, and x16.                                                                                                                                                                                                                                                    |

| Rank Size (CS_WIDTH)                 | Select the number of Chip selects (em_ddr_cs_n_o) required - Single or Dual. This also specifies the bit width of em_ddr_odt_o.                                                                                                                                                                                                                                               |

| Clock Width (CLKO_WIDTH)             | Specifies the number of clocks signals (em_ddr_clk_o) with which the IP Core drives the memory. The clocks signals are converted to differential pair in the FPGA pins. Please note that the differential pair signals are not shown in simulation.                                                                                                                           |

| CKE Width (CKE_WIDTH)                | Specifies the number of Clock Enable (CKE) signals (em_ddr_cke_o) with which the IP Core drives the memory.                                                                                                                                                                                                                                                                   |

| Local Interface                      |                                                                                                                                                                                                                                                                                                                                                                               |

| Local Bus Type                       | Specifies the user interface in FPGA fabric side. Only Native Interface is currently supported.                                                                                                                                                                                                                                                                               |

| Additional Configuration Group       |                                                                                                                                                                                                                                                                                                                                                                               |

| Data ready to Write Data delay       | This option is for information only. User logic is allowed to send the write data to the controller after a one-clock cycle delay with respect to datain_rdy_o signal.                                                                                                                                                                                                        |

| 2T Mode                              | Enables or disables the 2T timing for command signals when <i>Rank Size</i> = 2 (Dual Rank DIMM or 2 Chip select) is selected.                                                                                                                                                                                                                                                |

| Write levelling                      | This option allows you to enable or disable the Write Leveling operation of the DDR3 SDRAM Controller IP Core.                                                                                                                                                                                                                                                                |

| Controller reset to Memory           | When this option is disabled (unchecked), the reset signals mem_rst_n_i and<br>em_ddr_reset_n_o is no longer available and external logic should take care of the DDR3<br>memory reset.<br>If the option is enabled, the IP Core responds to mem_rst_n_i signal. When it is 1'b0, it<br>asserts m_ddr_reset_n_o signal for minimum 200 µs as per the DDR3 Memory requirement. |

| Attribute                        | Description                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Memory Device Setting Tab        |                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Address Group                    |                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Row Size (ROW_WIDTH)             | Indicates the default Row Address size used in the selected memory configuration.                                                                                                                                                                                                                                                                                                                                       |

| Column Size                      | Indicates the default Column Address size used in the selected memory configuration.                                                                                                                                                                                                                                                                                                                                    |

| Auto Refresh Control Group       |                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Auto Refresh Burst Count         | Indicates the number of Auto Refresh commands that the DDR3 SDRAM Controller IP Core is set to send in a single burst. Refer to REFRESH Support for more details.                                                                                                                                                                                                                                                       |

| External Auto Refresh Port       | Specifies the generation of refresh commands to the memory.<br>If Unchecked: the controller automatically generates refresh commands to the memory at the interval defined by the <i>Auto Refresh Burst Count</i> and memory refresh timing requirement.<br>If Checked: The user logic is allowed to generate a Refresh request to the controller via ext_auto_ref_i signal. Refer to REFRESH Support for more details. |

| Mode Register Initial Setting Gr |                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Burst Length                     | Sets the Burst length value in Mode Register 0 during initialization. This value remains until you write a different value to the Mode Register.                                                                                                                                                                                                                                                                        |

| CAS Latency                      | Sets the CAS Latency value in Mode Register 0 during initialization. This value remains until you write a different value to the Mode Register.                                                                                                                                                                                                                                                                         |

| Burst Type                       | Sets the Burst Type value in Mode Register 0 during initialization. This value remains until you write a different value to the Mode Register.                                                                                                                                                                                                                                                                          |

| Write Recovery                   | Sets the Write Recovery value in Mode Register 0 during initialization. The value is in terms of Memory clock. This value remains until you write a different value to the Mode Register.                                                                                                                                                                                                                               |

| DLL Control for PD               | Sets the DLL Control for Precharge PD value in Mode Register 0 during initialization. This value remains until you write a different value to the Mode Register.                                                                                                                                                                                                                                                        |

| ODI Control                      | Sets the Output Driver Impedance Control value in Mode Register 1 during initialization. This value remains until you write a different value to the Mode Register.                                                                                                                                                                                                                                                     |

| RTT_Nom (Ohm)                    | Sets the nominal termination, Rtt_Nom, value in Mode Register 1 during initialization. This value remains until you write a different value to the Mode Register.                                                                                                                                                                                                                                                       |

| Additive Latency                 | Sets the Additive latency, AL, value in Mode Register 1 during initialization. This value remains until you write a different value to the Mode Register                                                                                                                                                                                                                                                                |

| CAS Write Latency                | Sets the CAS Write Latency, CWL, value in Mode Register 2 during initialization. This value remains until you write a different value to the Mode Register.                                                                                                                                                                                                                                                             |

| RTT_WR                           | Sets the Dynamic ODT termination, Rtt_WR, value in Mode Register 2 during initialization.<br>This value remains until you write a different value to the Mode Register.                                                                                                                                                                                                                                                 |

| Memory Device Timing Tab*        |                                                                                                                                                                                                                                                                                                                                                                                                                         |