# CLC5955 11-bit, 55MSPS Broadband Monolithic A/D Converter

## **General Description**

The CLC5955 is a monolithic 11-bit, 55MSPS analog-to-digital converter. The device has been optimized for use in IF-sampled digital receivers and other applications where high resolution, high sampling rate, wide dynamic range, low power dissipation, and compact size are required. The CLC5955 features differential analog inputs, low jitter differential universal clock inputs, a low distortion track-and-hold with 0-300MHz input bandwidth, a bandgap voltage reference, data valid clock output, TTL compatible CMOS (3.3V or 2.5V) programmable output logic, and a proprietary multistage quantizer. The CLC5955 is fabricated on the ABIC-V 0.8 micron BiCMOS process.

The CLC5955 features a 74dBc spurious free dynamic range (SFDR) and a 64dB signal to noise ratio (SNR). The wideband track-and-hold allows sampling of IF signals to greater than 250MHz. The part produces two-tone, dithered, SFDR of 83dBFS at 75MHz input frequency. The differential analog input provides excellent common mode rejection, while the differential universal clock inputs minimize jitter. The 48-pin TSSOP package provides an extremely small footprint for applications where space is a critical consideration. The CLC5955 operates from a single +5V power supply. Operation over the industrial temperature range of -40°C to +85°C is guaranteed. National Semiconductor tests each part to verify compliance with the guaranteed specifications.

## **Features**

- 55MSPS

- Wide dynamic range SFDR: 74dBc SFDR w/dither: 85dBFS SNR: 64dB

- · IF sampling capability

- Input bandwidth = 0-300MHz

- · Low power dissipation: 640mW

- · Very small package: 48-pin TSSOP

- Single +5V supply

- · Data valid clock output

- Programmable output levels: 3.3V or 2.5V

## **Applications**

- Cellular base-stations

- · Digital communications

- Infrared/CCD imaging

- IF sampling

- · Electro-optics

- Instrumentation

- Medical imaging

- · High definition video

**Actual Size**

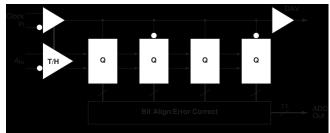

## **ADC Block Diagram**

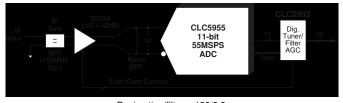

## First IF Receiver

Decimation/filter = 190/0.8 Output BW = 50M/190 X 0.8 = 210KHz

| CLC5955 Electrical Cha                                                       | aracteristics (V <sub>cc= +5</sub> )    | /, 55MSPS      | ; unless s | pecified) ( | $T_{min} = -40$ | °C, T <sub>max</sub> =                           | +85°C)                                         |

|------------------------------------------------------------------------------|-----------------------------------------|----------------|------------|-------------|-----------------|--------------------------------------------------|------------------------------------------------|

| PARAMETERS                                                                   | CONDITIONS                              | TEMP           |            | RATINGS     | <u> </u>        | UNITS                                            | NOTES                                          |

|                                                                              |                                         |                | MIN        | TYP         | MAX             |                                                  | 2                                              |

| RESOLUTION                                                                   |                                         | Full           |            | 11          |                 | Bits                                             | 1                                              |

| DIFF. INPUT VOLTAGE RANGE                                                    |                                         | Full           |            | 2.048       |                 | V                                                |                                                |

| MAXIMUM CONVERSION RATE SNR                                                  | $f_{in} = 25MHz$ , $A_{in} = -1dBFS$    | Full<br>+25°C  | 55<br>60   | 75<br>64    |                 | MSPS<br>dBFS                                     | 1 1                                            |

| SFDR                                                                         | $f_{in} = 25MHz, A_{in} = -1dBFS$       | +25°C          | 65         | 74          |                 | dBc                                              | '1                                             |

|                                                                              |                                         | 1200           |            | 1 .         |                 |                                                  | <u> </u>                                       |

| DYNAMIC PERFORMANCE large-signal bandwidth                                   | $A_{in} = -3dBFS$                       | +25°C          |            | 300         |                 | MHz                                              |                                                |

| overvoltage recovery time                                                    | A <sub>in</sub> = 1.5FS (0.01%)         | +25°C          |            | 12          |                 | ns                                               |                                                |

| effective aperture delay (Ta)                                                | - 411                                   | +25°C          |            | -0.41       |                 | ns                                               |                                                |

| aperture jitter                                                              |                                         | +25°C          |            | 0.3         |                 | ps(rms)                                          |                                                |

| NOISE AND DISTORTION                                                         |                                         |                |            |             |                 |                                                  |                                                |

| signal-to-noise ratio (w/o 50 harmonic                                       | cs)                                     | l l            |            |             |                 |                                                  |                                                |

| $f_{in} = 5.0MHz$                                                            | $A_{in} = -1dBFS$                       | Full           |            | 65          |                 | dBFS                                             |                                                |

| f <sub>in</sub> = 25MHz                                                      | $A_{in} = -1dBFS$                       | Full           | 57         | 64          |                 | dBFS                                             | 1                                              |

| f <sub>in</sub> = 75MHz                                                      | $A_{in} = -3dBFS$                       | Full           |            | 63          |                 | dBFS                                             |                                                |

| f <sub>in</sub> = 150MHz                                                     | $A_{in} = -15dBFS$                      | Full           |            | 64          |                 | dBFS                                             |                                                |

| f <sub>in</sub> = 250MHz                                                     | $A_{in} = -15dBFS$                      | Full           |            | 64          |                 | dBFS                                             |                                                |

| spurious-free dynamic range<br>f <sub>in</sub> = 5.0MHz                      | A <sub>in</sub> = -1dBFS                | Full           |            | 74          |                 | dBc                                              |                                                |

| f <sub>in</sub> = 25MHz                                                      | $A_{in} = -1 dBFS$                      | Full           | 59         | 74          |                 | dBc                                              | 1                                              |

| f <sub>in</sub> = 25WHz                                                      | $A_{in} = -1dBFS$<br>$A_{in} = -3dBFS$  | Full           | ] 39       | 72          |                 | dBc                                              | '                                              |

| $f_{in} = 750012$<br>$f_{in} = 150MHz$                                       | $A_{in} = -3dBFS$<br>$A_{in} = -15dBFS$ | Full           |            | 69          |                 | dBc                                              |                                                |

| $f_{in} = 130MHz$                                                            | $A_{in} = -15dBFS$                      | Full           |            | 65          |                 | dBc                                              |                                                |

| intermodulation distortion                                                   | A <sub>in</sub> = -13dbi 3              | l i uii        |            | 05          |                 | UDC                                              |                                                |

| f <sub>in1</sub> = 149.84MHz, f <sub>in2</sub> = 149.7MH                     | Iz A:- = -10dBFS                        | +25°C          |            | 68          |                 | dBFS                                             |                                                |

| $f_{\text{in1}} = 249.86\text{MHz}, f_{\text{in2}} = 249.69\text{M}$         | Hz A:- = -10dBFS                        | +25°C          |            | 58          |                 | dBFS                                             |                                                |

| dithered performance                                                         | TIZ TIN - TOUBTO                        | 120 0          |            |             |                 | ub. o                                            |                                                |

| spurious-free dynamic range                                                  |                                         |                |            |             |                 |                                                  |                                                |

| $f_{in} = 19MHz$                                                             | $A_{in} = -6dBFS$                       | +25°C          |            | 85          |                 | dBFS                                             |                                                |

| intermodulation distortion                                                   |                                         |                |            |             |                 |                                                  |                                                |

| $f_{in1} = 74MHz$ , $f_{in2} = 75MHz$                                        | $A_{in} = -12dBFS$                      | +25°C          |            | 83          |                 | dBFS                                             |                                                |

| DC ACCURACY AND PERFORMANCI                                                  |                                         |                |            |             |                 |                                                  |                                                |

| differential non-linearity                                                   | $f_{in} = 5MHz$ , $A_{in} = -1dBFS$     | Full           |            | ±0.8        |                 | LSB                                              |                                                |

| integral non-linearity                                                       | $f_{in} = 5MHz$ , $A_{in} = -1dBFS$     | Full           |            | ±2.0        |                 | LSB                                              |                                                |

| offset error                                                                 |                                         | Full           | -30        | 0           | 30              | mV                                               | 1                                              |

| gain error                                                                   |                                         | Full           |            | 1.2         |                 | %FS                                              |                                                |

| V <sub>ref</sub>                                                             |                                         | +25°C          | 2.2        | 2.37        | 2.6             | V                                                | 1                                              |

| ANALOG INPUTS                                                                |                                         | l l            |            |             |                 |                                                  |                                                |

| analog differential input voltage range                                      |                                         | Full           |            | 2.048       |                 | Vpp                                              |                                                |

| analog input resistance (single ended analog input resistance (differential) | )                                       | Full<br>Full   |            | 500<br>1000 |                 | $\Omega \Omega$                                  |                                                |

| analog input resistance (dinerential) analog input capacitance (single-end   | ed)                                     | Full           |            | 2           |                 | pF                                               |                                                |

| ENCODE INPUTS (Universal)                                                    | •                                       | 1              |            |             |                 | <del>                                     </del> |                                                |

| VIH                                                                          |                                         | +25°C          |            |             | 5               | V                                                | 3, 4                                           |

| VIL                                                                          |                                         | +25°C          | 0          |             |                 | V                                                | 3, 4                                           |

| differential input swing                                                     |                                         | +25°C          | 0.2        |             |                 | V                                                | 3, 4                                           |

| DIGITAL OUTPUTS                                                              | la sia LOW                              | 2502           |            | 0.01        |                 | .,                                               |                                                |

| output voltage                                                               | logic LOW                               | +25°C          | 2.0        | 0.01        | 0.4             | V                                                | <b> </b> 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 |

| OUTLEV = 1 (open)<br>OUTLEV = 0 (GND)                                        | logic HIGH<br>logic HIGH                | +25°C<br>+25°C | 3.2<br>2.4 | 3.5<br>2.7  | 3.8<br>3.0      | V<br>V                                           | 1 1                                            |

|                                                                              | logic i nari                            | T23 0          | <u> </u>   | 2.1         | 3.0             |                                                  | <b> </b> '                                     |

| POWER REQUIREMENTS                                                           |                                         | F              |            | 100         | 150             | A                                                | 4                                              |

| +5V supply current Power dissipation                                         |                                         | Full<br>Full   |            | 128<br>640  | 150<br>750      | mA<br>mW                                         | 1<br>  1                                       |

| V <sub>CC</sub> power supply rejection ratio                                 |                                         | +25°C          |            | 64          | , 30            | dB                                               | '                                              |

| 00 kg - 2 - 2 kg y - 2 y - 2 m - 1 m - 1                                     |                                         |                |            |             |                 |                                                  |                                                |

Min/max ratings are based on product characterization and simulation. Individual parameters are tested as noted. Outgoing quality levels are determined from tested parameters.

# CLC5955 Electrical Characteristics (V<sub>cc</sub>= +5V, 55MSPS; unless specified) (T<sub>min</sub> = -40°C, T<sub>max</sub> = +85°C)

| PARAMETERS                                                                                                                                                                                                                                                                                                   | CONDITIONS                       | SYMB                                                                                                           | TEMP                                                          | RATINGS                                                                      |          |                     | UNITS                                                   | NOTES                                |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|------------------------------------------------------------------------------|----------|---------------------|---------------------------------------------------------|--------------------------------------|

|                                                                                                                                                                                                                                                                                                              |                                  |                                                                                                                |                                                               | MIN                                                                          | TYP      | MAX                 |                                                         | 2                                    |

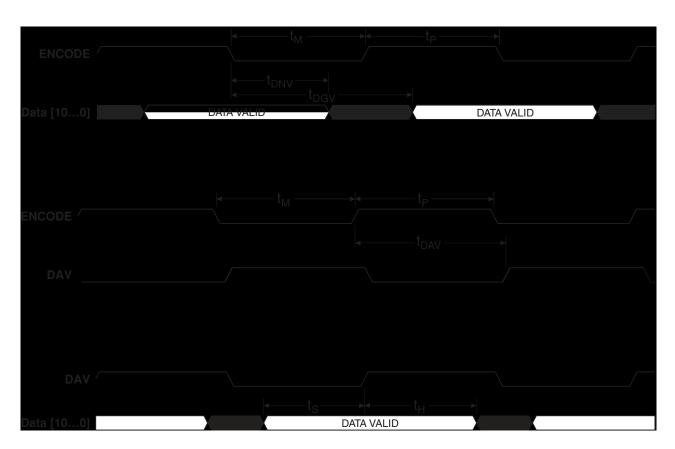

| TIMING (C <sub>L</sub> =7pF DATA; 10pF DAV) max conversion rate (ENCODE) min conversion rate (ENCODE) pulse width high (ENCODE) pulse width low (ENCODE) ENCODE falling edge to DATA not ENCODE falling edge to DATA guarising ENCODE to rising DAV delay DATA setup time before rising DAV pipeline latency | ranteed valid<br>/ 50% threshold | t <sub>P</sub> t <sub>M</sub> t <sub>DNV</sub> t <sub>DGV</sub> t <sub>DAV</sub> t <sub>S</sub> t <sub>H</sub> | Full<br>+25°C<br>Full<br>Full<br>Full<br>Full<br>Full<br>Full | 55<br>9.1<br>9.1<br>8.3<br>8.3<br>t <sub>M</sub> -2.4<br>t <sub>P</sub> -1.6 | 75<br>10 | 17.8<br>12.6<br>3.0 | MSPS<br>MSPS<br>ns<br>ns<br>ns<br>ns<br>ns<br>clk cycle | 1<br>3<br>3<br>3<br>3<br>3<br>3<br>3 |

Min/max ratings are based on product characterization and simulation. Individual parameters are tested as noted. Outgoing quality levels are determined from tested parameters.

# **Notes**

- 1) These parameters guaranteed by test.

- Typical specifications are based on the mean test values of deliverable converters from the first three diffusion lots.

- 3) Values guaranteed based on characterization and simulation.

4) See page 8, Figure 3 for ENCODE Inputs circuit.

# Absolute Maximum Ratings

positive supply voltage (V<sub>cc</sub>) -0.5V to +6V differential voltage between any two grounds <100mV analog input voltage range GND to  $V_{cc}$ -0.5V to  $+V_{cc}$ digital input voltage range output short circuit duration (one-pin to ground) infinite junction temperature 175°C storage temperature range -65°C to 150°C lead solder duration (+300°C) 10sec ESD tolerance 2000V human body model machine model 200V

Note: Absolute maximum ratings are limiting values, to be applied individually, and beyond which the serviceability of the circuit may be impaired. Functional operability under any of these conditions is not necessarily implied. Exposure to maximum ratings for extended periods may affect device reliability.

# **Recommended Operating Conditions**

positive supply voltage ( $V_{cc}$ ) +5V ±5% analog input voltage range 2.048 $V_{pp}$  diff. operating temperature range -40°C to +85°C

| Package Thermal Resistance |               |        |  |  |  |  |

|----------------------------|---------------|--------|--|--|--|--|

| Package                    | $\theta_{JA}$ | θЈС    |  |  |  |  |

| 48-pin TSSOP               | 56°C/W        | 16°C/W |  |  |  |  |

# Reliability Information

Transistor count 5000

| Ordering Information |                                     |                                 |  |  |

|----------------------|-------------------------------------|---------------------------------|--|--|

| Model                | Model Temperature Range Description |                                 |  |  |

| CLC5955MTDX          | -40°C to +85°C                      | 48-pin TSSOP (TNR 1000 pc reel) |  |  |

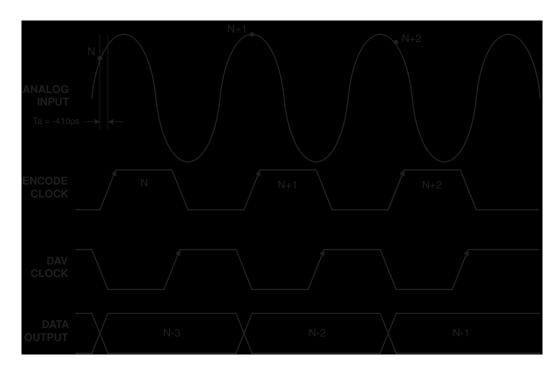

**CLC5955 Aperture Delay Diagram**

**CLC5955 DAV to Data Timing Diagram**

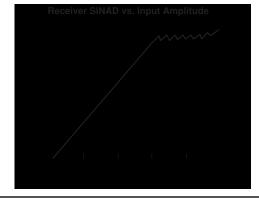

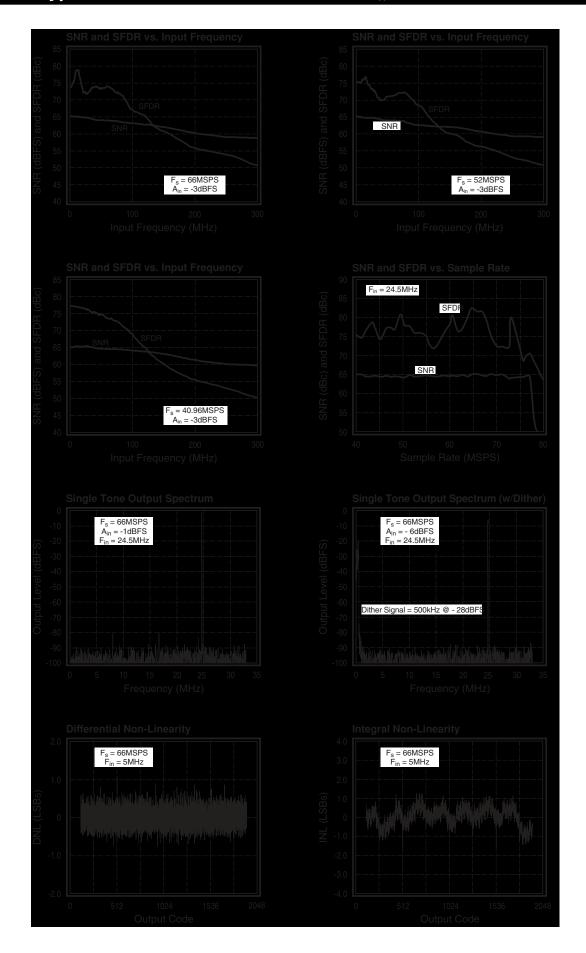

# **CLC5955 Typical Performance Characteristics** (V<sub>cc</sub> = +5V)

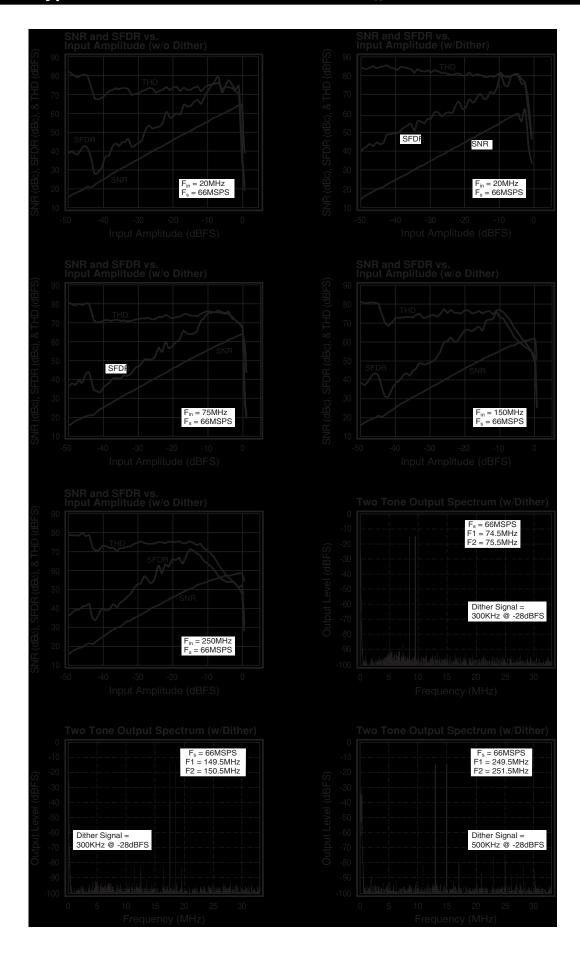

# **CLC5955 Typical Performance Characteristics** (V<sub>cc</sub> = +5V)

## **Physical Dimensions**

| Symbol | Min Max     |       | Notes |

|--------|-------------|-------|-------|

| Α      | _           | 1.10  |       |

| A1     | 0.05        | 0.15  |       |

| A2     | 0.80        | 1.05  |       |

| b      | 0.17        | 0.27  |       |

| b1     | 0.17        | 0.23  |       |

| С      | 0.09        | 0.20  |       |

| c1     | 1 0.09 0.16 |       |       |

| D      | 12.40       | 12.60 | 2     |

| Е      | 8.1 BSC     |       |       |

| E1     | 6.00        | 6.20  | 2     |

| е      | 0.50        |       |       |

| L      | 0.50 0.75   |       |       |

| L1     | 1.00        |       |       |

| R1     | 0.127       |       |       |

#### Notes:

- 1. All dimensions are in millimeters.

- 2. Dimensions D and E1 do not include mold protrusion. Allowable protrusion is 0.20mm per side.

# **CLC5955 Pin Definitions**

| GND                 | 1  |         | 48 | GND               |

|---------------------|----|---------|----|-------------------|

| GND                 | 2  |         | 47 | GND               |

| GND                 | 3  |         | 46 | +DV <sub>CC</sub> |

| GND                 | 4  |         | 45 | D10 (MSB)         |

| +AV <sub>CC</sub>   | 5  |         | 44 | D9                |

| +AVcc               | 6  |         | 43 | D8                |

| +AV <sub>CC</sub>   | 7  | CLC5955 | 42 | D7                |

| GND                 | 8  | 0203333 | 41 | D6                |

| ENCODE              | 9  |         | 40 | D5                |

| ENCODE              | 10 |         | 39 | D4                |

| GND                 | 11 |         | 38 | +DVcc             |

| GND                 | 12 |         | 37 | +DV <sub>CC</sub> |

| Ain                 | 13 |         | 36 | GND               |

| $\overline{A_{IN}}$ | 14 |         | 35 | GND               |

| GND                 | 15 |         | 34 | D3                |

| +AV <sub>CC</sub>   | 16 |         | 33 | D2                |

| +AVcc               | 17 |         | 32 | D1                |

| +AV <sub>CC</sub>   | 18 |         | 31 | D0 (LSB)          |

| GND                 | 19 |         | 30 | OGND              |

| GND                 | 20 |         | 29 | NC                |

| VcM                 | 21 |         | 28 | OUTLEV            |

| +AV <sub>CC</sub>   | 22 |         | 27 | DAV               |

| GND                 | 23 |         | 26 | GND               |

| GND                 | 24 |         | 25 | GND               |

$A_{IN}, A_{IN}$ (Pins 13, 14) Differential input with a common mode voltage of +2.4V. The ADC full scale input is 1.024Vpp

on each of the complimentary input signals. ENCODE, ENCODE (Pins 9, 10) Differential clock where ENCODE initiates a

new data conversion cycle on each rising edge. Logic for these inputs are 50% duty cycle universal differential signal (>200mV). The clock input is internally biased to V<sub>CC</sub>/2 with

a termination impedance of  $2.5k\Omega$ .

D0-D10 (Pins 31-34, 39-45) Digital data outputs are CMOS and

TTL compatible. Do is the LSB and D10 is the MSB. MSB is inverted. Output coding is two's complement.

Current limited to source/sink 2.5mA typical.

DAV (Pin 27) Data Valid Clock. Data is valid on rising edge.

Current limited to source/sink 5mA typical.

(Pin 28) Output Logic 3.3V or 2.5V option. Open = 3.3V, GND = 2.5V. **OUTLEV**

(Pin 21) Internal common mode voltage reference. Nominally V<sub>CM</sub> +2.4V. Can be used for the input common mode voltage.

This voltage is derived from an internal bandgap reference. VCM should be buffered when driving any external load. Failure to buffer this signal can cause errors in the internal

bias currents.

GND (Pins 1-4, 8, 11, 12, 15, 19, 20, 23-26, 35, 36, 47, 48)

circuit ground.

(Pins 5-7, 16-18, 22,) +5V power supply for the analog +AV<sub>CC</sub>

section. Bypass to ground with a 0.1µF capacitor.

+DV<sub>CC</sub> (Pins 37, 38, 46) +5V power supply for the digital section.

Bypass to ground with a 0.1µF capacitor.

NC (Pin 29) No connect. May be left open or grounded.

**OGND** (Pin 30) Option ground. May be tied to GND or left floating.

# **CLC5955 Applications**

## **Analog Inputs and Bias**

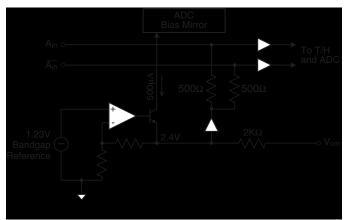

Figure 1 depicts the analog input and bias scheme. Each of the differential analog inputs are internally biased to a nominal voltage of 2.40 volts DC through a  $500\Omega$  resistor to a low impedance buffer. This enables a simple interface to a broadband RF transformer with a centertapped output winding that is decoupled to the analog ground. If the application requires the inputs to be DC coupled, the  $V_{cm}$  output can be used to establish the proper common -mode input voltage for the ADC. The  $V_{cm}$  voltage reference is generated from an internal bandgap source that is very accurate and stable.

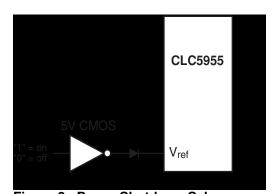

Figure 1: CLC5955 Bias Scheme

The  $V_{cm}$  output may also be used to power down the ADC. When the  $V_{cm}$  pin is pulled above 3.5V, the internal bias mirror is disabled and the total current is reduced to less than 10mA. Figure 2 depicts how this function can be used. The diode is necessary to prevent the logic gate from altering the ADC bias value.

Figure 2: Power Shutdown Scheme

## **ENCODE Clock Inputs**

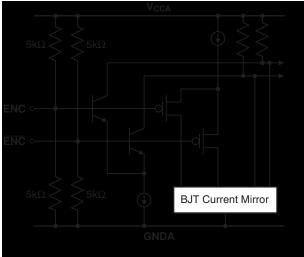

The CLC5955's differential input clock scheme is compatible with all commonly used clock sources. Although small differential and single-ended signals are adequate, for best aperture jitter performance a low noise differential clock with a high slew rate is preferred. As depicted in Figure 3, both ENCODE clock inputs are internally biased to  $V_{CC}/2$  though a pair of  $5K\Omega$  resistors. The clock input buffer operates with any common-mode voltage between the supply and ground.

Figure 3: CLC5955 ENCODE Clock Inputs

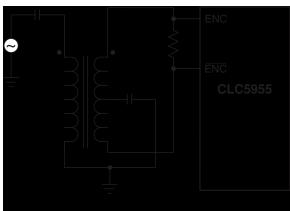

The internal bias resistors simplify the clock interface to another center-tapped transformer as depicted in Figure 4. A low phase noise, RF synthesizer of moderate amplitude  $(1 - 4V_{pp})$  can drive the ADC through this interface.

Figure 4: Transformer Coupled Clock Scheme

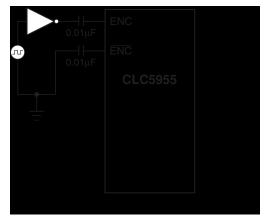

Figures 5 shows the clock interface scheme for square wave clock sources.

Figure 5: TTL, 3V or 5V CMOS Clock Scheme

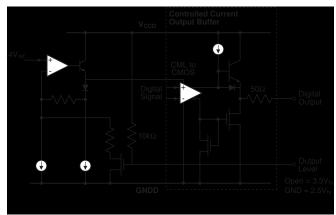

Figure 6: CLC5955 Digital Outputs

## **Digital Outputs and Level Select**

Figure 6 depicts the digital output buffer and bias used in the CLC5955. Although each of the eleven output bits uses a controlled current buffer to limit supply transients, it is recommended that parasitic loading of the outputs is minimized. Because these output transients are harmonically related to the analog input signal, excessive loading will degrade ADC performance at some frequencies.

The logic high level is slaved to the internal 2.4 voltage reference. The OUTLEV control pin selects either a 3.3V or 2.5V logic high level. An internal pullup resistor selects the 3.3 volt level as the default when the OUTLEV pin is left open. Grounding the OUTLEV pin selects the 2.5V logic high level.

To ease user interface to subsequent digital circuitry, the CLC5955 has a data valid clock output (DAV). In order to match delays over IC processing variables, this digital output also uses the same output buffer as the data bits. The DAV clock output is simply a delayed version of the ENCODE input clock. Since the ADC output data change is slaved to the falling edge of the ENCODE clock, the rising DAV clock edge occurs near the center of the data valid window (or eye) regardless of the sampling frequency.

## **Minimum Conversion Rate**

This ADC is optimized for high-speed operation. The internal bipolar track and hold circuits will cause droop errors at low sample rates. The point at which these errors cause a degradation of performance is listed on the specifications page as the minimum conversion rate. If a lower sample rate is desired, the ADC should be clocked at a higher rate, and the output data should be decimated. For example, to obtain a 10MSPS output, the ADC should be clocked at 20MHz, and every other output sample should be used. No significant power savings occurs at lower sample rates, since most of the power is used in analog circuits rather than digital circuits.

## LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, a) are intended for surgical implant into the body, or b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

## National Semiconductor Corporation

Tel: 1(800) 272-9959 Fax: 1(800) 737-7018 E-mail: support@nsc.com www.national.com

### National Semiconductor Europe

Fax: +49 (0) 1 80-530 85 86 E-mail: europe.support.nsc.com Deutsch Tel: +49 (0) 1 69 9508 6208 English Tel: +44 (0) 870 24 0 2171 Francais Tel: +33 (0) 1 41 91 8790

## National Semiconductor Asia Pacific Customer Response Group

Tel: 65-2544466 Fax: 65-2504466 E-mail: ap.support@nsc.com

### National Semiconductor Japan Ltd.

Tel: 81-3-5639-7560 Fax: 81-3-5639-7507

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications