# XS1-A16A-128-FB217 Datasheet

2015/04/14

## **Table of Contents**

| 1   | xCORE Multicore Microcontrollers         | 2 |

|-----|------------------------------------------|---|

| 2   | XS1-A16A-128-FB217 Features              | 4 |

| 3   |                                          | 5 |

| 4   | Signal Description                       | 6 |

| 5   | Example Application Diagram              | 0 |

| 6   | Product Overview                         |   |

| 7   | xCORE Tile Resources                     |   |

| 8   | Oscillator                               |   |

| 9   | Boot Procedure                           | 7 |

| 10  | Memory                                   | 9 |

| 11  | Analog-to-Digital Converter              | 0 |

| 12  | Supervisor Logic                         | 1 |

| 13  | Energy management                        |   |

| 14  | JTAG                                     |   |

| 15  | Board Integration                        | 5 |

| 16  | Example XS1-A16A-128-FB217 Board Designs |   |

| 17  | DC and Switching Characteristics         | 2 |

| 18  | Package Information                      | 7 |

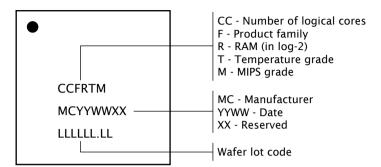

| 19  | Ordering Information                     | 8 |

| App | endices                                  | 9 |

| Α   | Configuring the device                   | 9 |

| В   | Processor Status Configuration           | 2 |

| C   | xCORE Tile Configuration                 | 1 |

| D   | Digital Node Configuration               | 9 |

| Ε   | Analogue Node Configuration              | 6 |

| F   | ADC Configuration                        | 0 |

| G   | Deep sleep memory Configuration          | 4 |

| Н   | Oscillator Configuration                 | 5 |

| 1   | Real time clock Configuration            | 7 |

| J   | Power control block Configuration        | 7 |

| K   | XMOS USB Interface                       | 0 |

| L   | Device Errata                            | 0 |

| M   | JTAG, xSCOPE and Debugging               | 1 |

| N   | Schematics Design Check List             | 3 |

| 0   | PCB Layout Design Check List             | 5 |

| P   | Associated Design Documentation          |   |

| Q   | Related Documentation                    |   |

| Ď   | Pavision History                         |   |

#### TO OUR VALUED CUSTOMERS

It is our intention to provide you with accurate and comprehensive documentation for the hardware and software components used in this product. To subscribe to receive updates, visit <a href="http://www.xmos.com/">http://www.xmos.com/</a>.

XMOS Ltd. is the owner or licensee of the information in this document and is providing it to you "AS IS" with no warranty of any kind, express or implied and shall have no liability in relation to its use. XMOS Ltd. makes no representation that the information, or any particular implementation thereof, is or will be free from any claims of infringement and again, shall have no liability in relation to any such claims.

XMOS and the XMOS logo are registered trademarks of XMOS Ltd in the United Kingdom and other countries, and may not be used without written permission. Company and product names mentioned in this document are the trademarks or registered trademarks of their respective owners.

### 1 xCORE Multicore Microcontrollers

The XS1-A Series is a comprehensive range of 32-bit multicore microcontrollers that brings the low latency and timing determinism of the xCORE architecture to mainstream embedded applications. Unlike conventional microcontrollers, xCORE multicore microcontrollers execute multiple real-time tasks simultaneously and communicate between tasks using a high speed network. Because xCORE multicore microcontrollers are completely deterministic, you can write software to implement functions that traditionally require dedicated hardware.

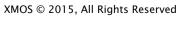

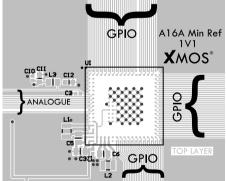

Figure 1: XS1-A Series:6-16 core devices

Key features of the XS1-A16A-128-FB217 include:

- ▶ **Tiles**: Devices consist of one or more xCORE tiles. Each tile contains between four and eight 32-bit xCOREs with highly integrated I/O and on-chip memory.

- ▶ Logical cores Each logical core can execute tasks such as computational code, DSP code, control software (including logic decisions and executing a state machine) or software that handles I/O. Section 7.1

- ➤ xTIME scheduler The xTIME scheduler performs functions similar to an RTOS, in hardware. It services and synchronizes events in a core, so there is no requirement for interrupt handler routines. The xTIME scheduler triggers cores on events generated by hardware resources such as the I/O pins, communication channels and timers. Once triggered, a core runs independently and concurrently to other cores, until it pauses to wait for more events. Section 7.2

- ▶ Channels and channel ends Tasks running on logical cores communicate using channels formed between two channel ends. Data can be passed synchronously or asynchronously between the channel ends assigned to the communicating tasks. Section 7.5

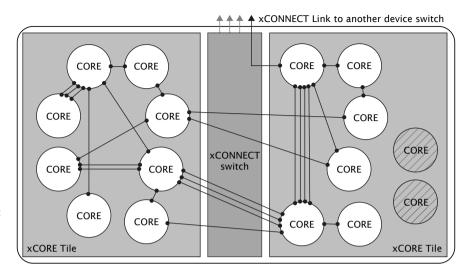

- ➤ xCONNECT Switch and Links Between tiles, channel communications are implemented over a high performance network of xCONNECT Links and routed through a hardware xCONNECT Switch. Section 7.6

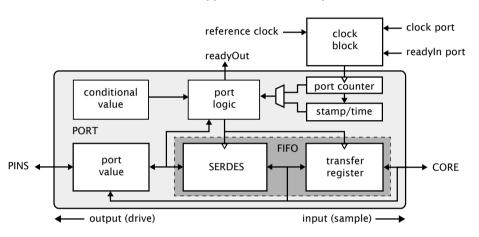

- ▶ **Ports** The I/O pins are connected to the processing cores by Hardware Response ports. The port logic can drive its pins high and low, or it can sample the value on its pins optionally waiting for a particular condition. Section 7.3

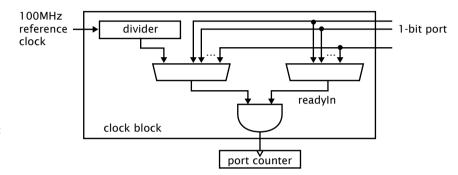

- ► Clock blocks xCORE devices include a set of programmable clock blocks that can be used to govern the rate at which ports execute. Section 7.4

- Memory Each xCORE Tile integrates a bank of SRAM for instructions and data, and a block of one-time programmable (OTP) memory that can be configured for system wide security features. Section 10

- ▶ PLL The PLL is used to create a high-speed processor clock given a low speed external oscillator. Section 8

- ▶ JTAG The JTAG module can be used for loading programs, boundary scan testing, in-circuit source-level debugging and programming the OTP memory. Section 14

#### 1.1 Software

Devices are programmed using C, C++ or xC (C with multicore extensions). XMOS provides tested and proven software libraries, which allow you to quickly add interface and processor functionality such as USB, Ethernet, PWM, graphics driver, and audio EQ to your applications.

### 1.2 xTIMEcomposer Studio

The xTIMEcomposer Studio development environment provides all the tools you need to write and debug your programs, profile your application, and write images into flash memory or OTP memory on the device. Because xCORE devices operate deterministically, they can be simulated like hardware within xTIMEcomposer: uniquely in the embedded world, xTIMEcomposer Studio therefore includes a static timing analyzer, cycle-accurate simulator, and high-speed in-circuit instrumentation.

xTIMEcomposer can be driven from either a graphical development environment, or the command line. The tools are supported on Windows, Linux and MacOS X and available at no cost from xmos.com/downloads. Information on using the tools is provided in the xTIMEcomposer User Guide, X3766.

#### 2 XS1-A16A-128-FB217 Features

#### ► Multicore Microcontroller with Advanced Multi-Core RISC Architecture

- 16 real-time logical cores on 2 xCORE tiles

- Cores share up to 1000 MIPS

- Each logical core has:

- Guaranteed throughput of between 1/4 and 1/8 of tile MIPS

- 16x32bit dedicated registers

- 159 high-density 16/32-bit instructions

- All have single clock-cycle execution (except for divide)

- 32x32→64-bit MAC instructions for DSP, arithmetic and user-definable cryptographic functions

### ▶ 12b 1MSPS 8-channel SAR Analog-to-Digital Converter

- ▶ 1 x LDO

- ▶ 2 x DC-DC converters and Power Management Unit

- ▶ Watchdog Timer

#### ▶ Onchip clocks/oscillators

- Crvstal oscillator

- 20MHz/31kHz silicon oscillators

#### ▶ Programmable I/O

- 90 general-purpose I/O pins, configurable as input or output

- Up to 32 x 1bit port, 12 x 4bit port, 8 x 8bit port, 4 x 16bit port

- 4 xCONNECT links

- Port sampling rates of up to 60 MHz with respect to an external clock

- 64 channel ends for communication with other cores, on or off-chip

#### Memory

- 128KB internal single-cycle SRAM (max 64KB per tile) for code and data storage

- 16KB internal OTP (max 8KB per tile) for application boot code

- 128 bytes Deep Sleep Memory

#### ▶ Hardware resources

- 12 clock blocks (6 per tile)

- 20 timers (10 per tile)

- 8 locks (4 per tile)

#### ▶ JTAG Module for On-Chip Debug

#### Security Features

- Programming lock disables debug and prevents read-back of memory contents

- AES bootloader ensures secrecy of IP held on external flash memory

#### ► Ambient Temperature Range

- Commercial qualification: 0°C to 70°C

- Industrial qualification: -40°C to 85°C

#### ► Speed Grade

- 10: 1000 MIPS

- 8: 800 MIPS

#### ▶ Power Consumption (typical)

- 600 mW at 500 MHz (typical)

- Sleep Mode: 500 µW

- ▶ 217-pin FBGA package 0.8 mm pitch

# 3 Pin Configuration

|   | 1          | 2           | 3     | 4     | 5      | 6            | 7       | 8     | 9     | 10    | 11    | 12    | 13    | 14             | 15    | 16    | 17    | 18    | 19             |

|---|------------|-------------|-------|-------|--------|--------------|---------|-------|-------|-------|-------|-------|-------|----------------|-------|-------|-------|-------|----------------|

| А | X0D00      | X0D02       | X0D04 | X0D06 | X0D08  | X0D10        | X0D12   | X0D14 | X0D16 | X0D18 | X0D20 | X0D22 | X0D24 | X0D25          | X0D26 | X0D28 | X0D30 | X0D32 | VDDIO_<br>OUT_ |

| В | X0D01      | X0D03       | X0D05 | X0D07 | X0D09  | X0D11        | X0D13   | X0D15 | X0D17 | X0D19 | X0D21 | X0D23 | X0D70 | ADC_<br>SAMPLE | X0D27 | X0D29 | X0D31 | X0D33 | X0D36          |

| С | TDO        | DEBUG_<br>N |       |       |        |              |         |       |       |       |       |       |       |                |       |       |       | X0D38 | X0D37          |

| D | тск        | RST_N       |       |       |        |              |         |       |       |       |       |       |       |                |       |       |       | X0D40 | X0D39          |

| E | TMS        | TDI         |       |       |        |              |         |       |       |       |       |       |       |                |       |       |       | X0D42 | X0D41          |

| F | MODE[2]    | MODE[3]     |       |       |        | GND          | GND     | GND   | GND   | GND   | GND   | GND   | GND   | GND            |       |       |       | X0D34 | X0Ö43/<br>WAKE |

| G | AVDD       | ADC7        |       |       |        | GND          | GND     | GND   | GND   | GND   | GND   | GND   | GND   | GND            |       |       |       | X1D00 | X0D35          |

| Н | ADC5       | ADC6        |       |       |        | GND          | GND     | GND   | GND   | GND   | GND   | GND   | GND   | GND            |       |       |       | X1D02 | X1D01          |

| J | ADC3       | ADC4        |       |       |        | AVSS         | GND     | GND   | GND   | GND   | GND   | GND   | GND   | GND            |       |       |       | X1D04 | X1D03          |

| К | ADC1       | ADC2        |       |       |        | MODE[0]      | MODE[1] | GND            |       |       |       | X1D06 | X1D05          |

| L | NC         | ADC0        |       |       |        | OSC<br>EXT_N | MODE[4] | GND            |       |       |       | X1D08 | X1D07          |

| М | XI/<br>CLK | NC          |       |       |        | NC           | NC      | GND            |       |       |       | X1D10 | X1D09          |

| N | хо         | NC          |       |       |        | NC           | NC      | GND            |       |       |       | X1D12 | X1D11          |

| Р | NC         | VSUP        |       |       |        | GND          | GND     | GND   | GND   | GND   | GND   | GND   | GND   | GND            |       |       |       | X1D14 | X1D13          |

| R | SW1        | SW1         |       |       |        |              |         |       |       |       |       |       |       |                |       |       |       | X1D16 | X1D15          |

| Т | SW1        | VDDCORE     |       |       |        |              |         |       |       |       |       |       |       |                |       |       |       | X1D18 | X1D17          |

| U | VDDCORE    | VDDCORE     |       |       |        |              |         |       |       |       |       |       |       |                |       |       |       | X1D20 | X1D19          |

| V | PGND       | PGND        | VDDIO | PGND  | VDD1V8 | SW2          | NC      | X1D35 | X1D43 | X1D41 | X1D39 | X1D37 | X1D33 | X1D31          | X1D29 | X1D27 | X1D25 | X1D22 | X1D21          |

| W | VSUP       | VSUP        | VDDIO | PGND  | VDD1V8 | SW2          | NG      | X1D34 | X1D42 | X1D40 | X1D38 | X1D36 | X1D32 | X1D30          | X1D28 | X1D26 | X1D24 | X1D70 | X1D23          |

## 4 Signal Description

This section lists the signals and I/O pins available on the XS1-A16A-128-FB217. The device provides a combination of 1bit, 4bit, 8bit and 16bit ports, as well as wider ports that are fully or partially (gray) bonded out. All pins of a port provide either output or input, but signals in different directions cannot be mapped onto the same port.

Pins may have one or more of the following properties:

- ▶ PD/PU: The IO pin a weak pull-down or pull-up resistor. On GPIO pins this resistor can be enabled.

- ▶ ST: The IO pin has a Schmitt Trigger on its input.

|           | Power pins (10)               |      |            |  |  |  |  |  |

|-----------|-------------------------------|------|------------|--|--|--|--|--|

| Signal    | Function                      | Type | Properties |  |  |  |  |  |

| AVSS      | Digital ground                | GND  |            |  |  |  |  |  |

| GND       | Digital ground                | GND  |            |  |  |  |  |  |

| PGND      | Power ground                  | GND  |            |  |  |  |  |  |

| SW1       | DCDC1 switched output voltage | PWR  |            |  |  |  |  |  |

| SW2       | DCDC2 switched output voltage | PWR  |            |  |  |  |  |  |

| VDD1V8    | 1v8 voltage supply            | PWR  |            |  |  |  |  |  |

| VDDCORE   | Core voltage supply           | PWR  |            |  |  |  |  |  |

| VDDIO     | Digital I/O power             | PWR  |            |  |  |  |  |  |

| VDDIO_OUT | Digital I/O power out         | PWR  |            |  |  |  |  |  |

| VSUP      | Power supply (3V3/5V0)        | PWR  |            |  |  |  |  |  |

|            | Analog pins (10)             |       |            |  |  |  |  |  |

|------------|------------------------------|-------|------------|--|--|--|--|--|

| Signal     | Function                     | Type  | Properties |  |  |  |  |  |

| ADC0       | Analog input                 | Input |            |  |  |  |  |  |

| ADC1       | Analog input                 | Input |            |  |  |  |  |  |

| ADC2       | Analog input                 | Input |            |  |  |  |  |  |

| ADC3       | Analog input                 | Input |            |  |  |  |  |  |

| ADC4       | Analog input                 | Input |            |  |  |  |  |  |

| ADC5       | Analog input                 | Input |            |  |  |  |  |  |

| ADC6       | Analog input                 | Input |            |  |  |  |  |  |

| ADC7       | Analog input                 | Input |            |  |  |  |  |  |

| ADC_SAMPLE | Sample Analog input          | I/O   |            |  |  |  |  |  |

| AVDD       | Supply and reference voltage | PWR   |            |  |  |  |  |  |

(continued)

| Signal | Function | Type | Properties |

|--------|----------|------|------------|

|--------|----------|------|------------|

| Clocks pins (4) |                                |        |            |  |  |  |  |  |

|-----------------|--------------------------------|--------|------------|--|--|--|--|--|

| Signal          | Function                       | Type   | Properties |  |  |  |  |  |

| MODE[4:0]       | Boot mode select               | Input  | PU, ST     |  |  |  |  |  |

| OSC_EXT_N       | Use Silicon Oscillator         | Input  | ST         |  |  |  |  |  |

| XI/CLK          | Crystal Oscillator/Clock Input | Input  |            |  |  |  |  |  |

| хо              | Crystal Oscillator Output      | Output |            |  |  |  |  |  |

|         | JTAG pins (5)    |        |            |

|---------|------------------|--------|------------|

| Signal  | Function         | Type   | Properties |

| DEBUG_N | Multi-chip debug | I/O    | PU         |

| TCK     | Test clock       | Input  | PU, ST     |

| TDI     | Test data input  | Input  | PU, ST     |

| TDO     | Test data output | Output | PD, OT     |

| TMS     | Test mode select | Input  | PU, ST     |

| Misc pins (1) |                    |       |            |  |  |  |  |

|---------------|--------------------|-------|------------|--|--|--|--|

| Signal        | Function           | Type  | Properties |  |  |  |  |

| RST_N         | Global reset input | Input | PU, ST     |  |  |  |  |

| I/O pins (90) |                                                                                                    |      |                                  |  |  |  |  |  |

|---------------|----------------------------------------------------------------------------------------------------|------|----------------------------------|--|--|--|--|--|

| Signal        | Function                                                                                           | Type | Properties                       |  |  |  |  |  |

| X0D00         | 1A <sup>0</sup>                                                                                    | I/O  | PD <sub>S</sub> , R <sub>S</sub> |  |  |  |  |  |

| X0D01         | XLA <sub>out</sub> 1B <sup>0</sup>                                                                 | I/O  | PD <sub>S</sub> , R <sub>S</sub> |  |  |  |  |  |

| X0D02         | XLA <sub>out</sub> 4A <sup>0</sup> 8A <sup>0</sup> 16A <sup>0</sup> 32A <sup>20</sup>              | I/O  | PD <sub>S</sub> , R <sub>U</sub> |  |  |  |  |  |

| X0D03         | XLA <sub>out</sub> 4A <sup>1</sup> 8A <sup>1</sup> 16A <sup>1</sup> 32A <sup>21</sup>              | I/O  | PD <sub>S</sub> , R <sub>U</sub> |  |  |  |  |  |

| X0D04         | XLA <sub>out</sub> 4B <sup>0</sup> 8A <sup>2</sup> 16A <sup>2</sup> 32A <sup>22</sup>              | I/O  | PD <sub>S</sub> , R <sub>U</sub> |  |  |  |  |  |

| X0D05         | XLA <sub>out</sub> 4B <sup>1</sup> 8A <sup>3</sup> 16A <sup>3</sup> 32A <sup>23</sup>              | I/O  | PD <sub>S</sub> , R <sub>U</sub> |  |  |  |  |  |

| X0D06         | XLA <sub>in</sub> 4B <sup>2</sup> 8A <sup>4</sup> 16A <sup>4</sup> 32A <sup>24</sup>               | I/O  | PD <sub>S</sub> , R <sub>U</sub> |  |  |  |  |  |

| X0D07         | XLA <sub>in</sub> 4B <sup>3</sup> 8A <sup>5</sup> 16A <sup>5</sup> 32A <sup>25</sup>               | I/O  | PD <sub>S</sub> , R <sub>U</sub> |  |  |  |  |  |

| X0D08         | XLA <sub>in</sub> 4A <sup>2</sup> 8A <sup>6</sup> 16A <sup>6</sup> 32A <sup>26</sup>               | I/O  | PD <sub>S</sub> , R <sub>U</sub> |  |  |  |  |  |

| X0D09         | XLA <sub>in</sub> 4A <sup>3</sup> 8A <sup>7</sup> 16A <sup>7</sup> 32A <sup>27</sup>               | I/O  | PD <sub>S</sub> , R <sub>U</sub> |  |  |  |  |  |

| X0D10         | XLA <sup>4</sup> <sub>in</sub> 1C <sup>0</sup>                                                     | I/O  | PD <sub>S</sub> , R <sub>S</sub> |  |  |  |  |  |

| X0D11         | 1D <sup>0</sup>                                                                                    | I/O  | PD <sub>S</sub> , R <sub>S</sub> |  |  |  |  |  |

| X0D12         | 1E <sup>0</sup>                                                                                    | I/O  | PD <sub>S</sub> , R <sub>U</sub> |  |  |  |  |  |

| X0D13         | XLB <sup>4</sup> <sub>out</sub> 1F <sup>0</sup>                                                    | I/O  | PD <sub>S</sub> , R <sub>U</sub> |  |  |  |  |  |

| X0D14         | XLB <sup>3</sup> <sub>out</sub> 4C <sup>0</sup> 8B <sup>0</sup> 16A <sup>8</sup> 32A <sup>28</sup> | I/O  | PD <sub>S</sub> , R <sub>U</sub> |  |  |  |  |  |

| X0D15         | XLB <sub>out</sub> 4C <sup>1</sup> 8B <sup>1</sup> 16A <sup>9</sup> 32A <sup>29</sup>              | I/O  | PD <sub>S</sub> , R <sub>U</sub> |  |  |  |  |  |

| X0D16         | XLB <sub>out</sub> 4D <sup>0</sup> 8B <sup>2</sup> 16A <sup>10</sup>                               | I/O  | PD <sub>S</sub> , R <sub>U</sub> |  |  |  |  |  |

(continued)

| Cianal          | Function                                                                                                                | Tyma | Duamantias                       |

|-----------------|-------------------------------------------------------------------------------------------------------------------------|------|----------------------------------|

| Signal<br>X0D17 |                                                                                                                         | Type | Properties                       |

|                 | out                                                                                                                     | 1/0  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D18           |                                                                                                                         | 1/0  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D19           |                                                                                                                         | 1/0  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D20           | 111                                                                                                                     | 1/0  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D21           | XLB <sub>in</sub> 4C <sup>3</sup> 8B <sup>7</sup> 16A <sup>15</sup> 32A <sup>31</sup> XLB <sub>in</sub> 1G <sup>0</sup> | 1/0  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D22           | XLB <sup>4</sup> <sub>in</sub> 1G <sup>0</sup>                                                                          | 1/0  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D23           | 110                                                                                                                     | 1/0  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D24           |                                                                                                                         | 1/0  | PDs                              |

| X0D25           | 1,10                                                                                                                    | 1/0  | PDs                              |

| X0D26           | 4E <sup>0</sup> 8C <sup>0</sup> 16B <sup>0</sup>                                                                        | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D27           | 4E <sup>1</sup> 8C <sup>1</sup> 16B <sup>1</sup>                                                                        | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D28           | 4F <sup>0</sup> 8C <sup>2</sup> 16B <sup>2</sup>                                                                        | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D29           | 4F <sup>1</sup> 8C <sup>3</sup> 16B <sup>3</sup>                                                                        | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D30           | 4F <sup>2</sup> 8C <sup>4</sup> 16B <sup>4</sup>                                                                        | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D31           | 4F <sup>3</sup> 8C <sup>5</sup> 16B <sup>5</sup>                                                                        | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D32           | 4E <sup>2</sup> 8C <sup>6</sup> 16B <sup>6</sup>                                                                        | I/O  | PDs, R <sub>U</sub>              |

| X0D33           | 4E <sup>3</sup> 8C <sup>7</sup> 16B <sup>7</sup>                                                                        | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D34           | 1K <sup>0</sup>                                                                                                         | I/O  | PDs                              |

| X0D35           | 1L <sup>0</sup>                                                                                                         | I/O  | PDs                              |

| X0D36           | 1M <sup>0</sup> 8D <sup>0</sup> 16B <sup>8</sup>                                                                        | I/O  | $PD_S$                           |

| X0D37           | 1N <sup>0</sup> 8D <sup>1</sup> 16B <sup>9</sup>                                                                        | I/O  | $PD_S$ , $R_U$                   |

| X0D38           | 10 <sup>0</sup> 8D <sup>2</sup> 16B <sup>10</sup>                                                                       | I/O  | $PD_S$ , $R_U$                   |

| X0D39           | 1P <sup>0</sup> 8D <sup>3</sup> 16B <sup>11</sup>                                                                       | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D40           | 8D <sup>4</sup> 16B <sup>12</sup>                                                                                       | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D41           | 8D <sup>5</sup> 16B <sup>13</sup>                                                                                       | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D42           | 8D <sup>6</sup> 16B <sup>14</sup>                                                                                       | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D43/WAKE      | 8D <sup>7</sup> 16B <sup>15</sup>                                                                                       | I/O  | PU <sub>S</sub> , R <sub>U</sub> |

| X0D70           | 32A <sup>19</sup>                                                                                                       | I/O  | PDs                              |

| X1D00           | 1A <sup>0</sup>                                                                                                         | I/O  | PD <sub>S</sub> , R <sub>S</sub> |

| X1D01           | XLA <sub>out</sub> 1B <sup>0</sup>                                                                                      | I/O  | PD <sub>S</sub> , R <sub>S</sub> |

| X1D02           | XLA <sub>out</sub> 4A <sup>0</sup> 8A <sup>0</sup> 16A <sup>0</sup> 32A <sup>20</sup>                                   | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X1D03           | XLA <sub>out</sub> 4A <sup>1</sup> 8A <sup>1</sup> 16A <sup>1</sup> 32A <sup>21</sup>                                   | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X1D04           | XLA <sub>out</sub> 4B <sup>0</sup> 8A <sup>2</sup> 16A <sup>2</sup> 32A <sup>22</sup>                                   | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X1D05           | XLA <sub>out</sub> 4B <sup>1</sup> 8A <sup>3</sup> 16A <sup>3</sup> 32A <sup>23</sup>                                   | I/O  | PDs, Ru                          |

| X1D06           | XLA <sub>in</sub> 4B <sup>2</sup> 8A <sup>4</sup> 16A <sup>4</sup> 32A <sup>24</sup>                                    | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X1D07           | XLA <sup>1</sup> <sub>in</sub> 4B <sup>3</sup> 8A <sup>5</sup> 16A <sup>5</sup> 32A <sup>25</sup>                       | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X1D08           | XLA <sub>in</sub> 4A <sup>2</sup> 8A <sup>6</sup> 16A <sup>6</sup> 32A <sup>26</sup>                                    | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X1D09           | XLA <sub>in</sub> 4A <sup>3</sup> 8A <sup>7</sup> 16A <sup>7</sup> 32A <sup>27</sup>                                    | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| XID10           | XLA <sup>4</sup> <sub>in</sub> 1C <sup>0</sup>                                                                          | I/O  | PD <sub>S</sub> , R <sub>S</sub> |

| XIDII           | 1D <sup>0</sup>                                                                                                         | 1/0  | PD <sub>S</sub> , R <sub>S</sub> |

| X1D12           | 1E <sup>0</sup>                                                                                                         | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X1D13           | XLB <sup>4</sup> <sub>out</sub> 1F <sup>0</sup>                                                                         | 1/0  | PD <sub>S</sub> , R <sub>U</sub> |

| X1D14           | XLB <sub>out</sub> 4C <sup>0</sup> 8B <sup>0</sup> 16A <sup>8</sup> 32A <sup>28</sup>                                   | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

|                 | Out 12 25 10/1 52/1                                                                                                     | ., • | - 31 - 10                        |

(continued)

| Signal | Function                                                                                           | Type | Properties                       |

|--------|----------------------------------------------------------------------------------------------------|------|----------------------------------|

| X1D15  | XLB <sub>out</sub> 4C <sup>1</sup> 8B <sup>1</sup> 16A <sup>9</sup> 32A <sup>29</sup>              | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X1D16  | XLB <sup>1</sup> <sub>out</sub> 4D <sup>0</sup> 8B <sup>2</sup> 16A <sup>10</sup>                  | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X1D17  | XLB <sup>0</sup> <sub>out</sub> 4D <sup>1</sup> 8B <sup>3</sup> 16A <sup>11</sup>                  | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X1D18  | XLB <sub>in</sub> 4D <sup>2</sup> 8B <sup>4</sup> 16A <sup>12</sup>                                | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X1D19  | XLB <sub>in</sub> 4D <sup>3</sup> 8B <sup>5</sup> 16A <sup>13</sup>                                | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X1D20  | XLB <sub>in</sub> <sup>2</sup> 4C <sup>2</sup> 8B <sup>6</sup> 16A <sup>14</sup> 32A <sup>30</sup> | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X1D21  | XLB <sup>3</sup> 4C <sup>3</sup> 8B <sup>7</sup> 16A <sup>15</sup> 32A <sup>31</sup>               | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X1D22  | XLB <sup>4</sup> <sub>in</sub> 1G <sup>0</sup>                                                     | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X1D23  | 1H <sup>0</sup>                                                                                    | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X1D24  | 110                                                                                                | I/O  | PDs                              |

| X1D25  | 1J <sup>0</sup>                                                                                    | I/O  | PDs                              |

| X1D26  | 4E <sup>0</sup> 8C <sup>0</sup> 16B <sup>0</sup>                                                   | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X1D27  | 4E <sup>1</sup> 8C <sup>1</sup> 16B <sup>1</sup>                                                   | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X1D28  | 4F <sup>0</sup> 8C <sup>2</sup> 16B <sup>2</sup>                                                   | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X1D29  | 4F <sup>1</sup> 8C <sup>3</sup> 16B <sup>3</sup>                                                   | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X1D30  | 4F <sup>2</sup> 8C <sup>4</sup> 16B <sup>4</sup>                                                   | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X1D31  | 4F <sup>3</sup> 8C <sup>5</sup> 16B <sup>5</sup>                                                   | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X1D32  | 4E <sup>2</sup> 8C <sup>6</sup> 16B <sup>6</sup>                                                   | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X1D33  | 4E <sup>3</sup> 8C <sup>7</sup> 16B <sup>7</sup>                                                   | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X1D34  | 1K <sup>0</sup>                                                                                    | I/O  | PDs                              |

| X1D35  | 1L <sup>0</sup>                                                                                    | I/O  | PDs                              |

| X1D36  | 1M <sup>0</sup> 8D <sup>0</sup> 16B <sup>8</sup>                                                   | I/O  | PDs                              |

| X1D37  | 1N <sup>0</sup> 8D <sup>1</sup> 16B <sup>9</sup>                                                   | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X1D38  | 10 <sup>0</sup> 8D <sup>2</sup> 16B <sup>10</sup>                                                  | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X1D39  | 1P <sup>0</sup> 8D <sup>3</sup> 16B <sup>11</sup>                                                  | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X1D40  | 8D <sup>4</sup> 16B <sup>12</sup>                                                                  | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X1D41  | 8D <sup>5</sup> 16B <sup>13</sup>                                                                  | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X1D42  | 8D <sup>6</sup> 16B <sup>14</sup>                                                                  | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X1D43  | 8D <sup>7</sup> 16B <sup>15</sup>                                                                  | I/O  | PU <sub>S</sub> , R <sub>U</sub> |

| X1D70  | 32A <sup>19</sup>                                                                                  | I/O  | PDs                              |

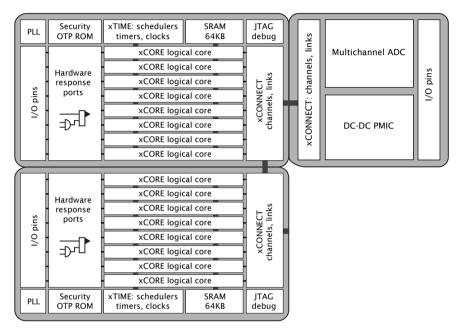

# 5 Example Application Diagram

Figure 2: Simplified Reference Schematic

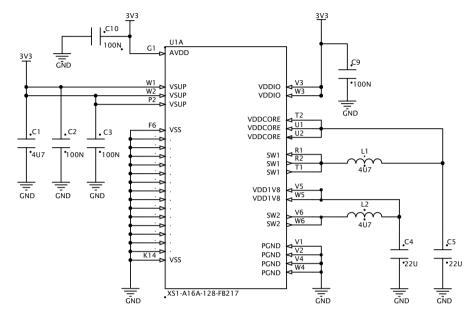

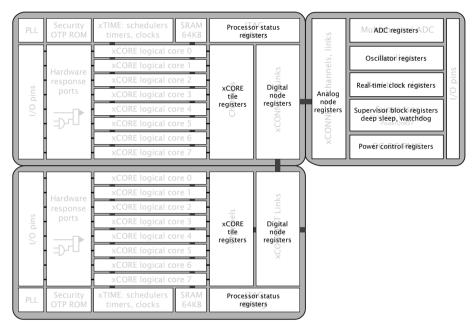

#### 6 Product Overview

The XS1-A16A-128-FB217 comprises a digital and an analog node, as shown in Figure 3. The digital node comprises an xCORE Tile, a Switch, and a PLL (Phase-locked-loop). The analog node comprises a multi-channel ADC (Analog to Digital Converter), deep sleep memory, an oscillator, a real-time counter, and power supply control.

Figure 3: Block Diagram

All communication between the digital and analog node takes place over a link that is connected to the Switch of the digital node. As such, the analog node can be controlled from any node on the system. The analog functions can be configured using a set of node configuration registers, and a set of registers for each of the peripherals.

The device can be programmed using high-level languages such as C/C++ and the XMOS-originated XC language, which provides extensions to C that simplify the control over concurrency, I/O and timing, or low-level assembler.

#### 6.1 XCore Tile

The xCORE Tile is a flexible multicore microcontroller component with tightly integrated I/O and on-chip memory. The tile contains multiple logical cores that run simultaneously, each of which is guaranteed a slice of processing power and can execute computational code, control software and I/O interfaces. The logical cores use channels to exchange data within a tile or across tiles. The tiles are connected via an integrated switch network, called xCONNECT, which uses a

proprietary physical layer protocol and can also be used to add additional resources to a design. The I/O pins are driven using intelligent ports that can serialize data, interpret strobe signals and wait for scheduled times or events, making the device ideal for real-time control applications.

#### 6.2 ADC and Power Management

Each XS1-A16A-128-FB217 device includes a set of analog components, including a 12b, 8-channel ADC, power management unit, watchdog timer, real-time counter and deep sleep memory. The device reduces the number of additional external components required and allows designs to be implemented using simple 2-layer boards.

## 7 xCORE Tile Resources

### 7.1 Logical cores

Each tile has 8 active logical cores, which issue instructions down a shared four-stage pipeline. Instructions from the active cores are issued round-robin. If up to four logical cores are active, each core is allocated a quarter of the processing cycles. If more than four logical cores are active, each core is allocated at least 1/n cycles (for n cores). Figure 4 shows the guaranteed core performance depending on the number of cores used.

Figure 4: Logical core performance

| Speed | MIPS      | Frequency | Minimum MIPS per core (for <i>n</i> cores) |     |     |     |     |    |    |    |

|-------|-----------|-----------|--------------------------------------------|-----|-----|-----|-----|----|----|----|

| grade |           |           | 1                                          | 2   | 3   | 4   | 5   | 6  | 7  | 8  |

| 8     | 800 MIPS  | 400 MHz   | 100                                        | 100 | 100 | 100 | 80  | 67 | 57 | 50 |

| 10    | 1000 MIPS | 500 MHz   | 125                                        | 125 | 125 | 125 | 100 | 83 | 71 | 63 |

There is no way that the performance of a logical core can be reduced below these predicted levels. Because cores may be delayed on I/O, however, their unused processing cycles can be taken by other cores. This means that for more than four logical cores, the performance of each core is often higher than the predicted minimum but cannot be guaranteed.

The logical cores are triggered by events instead of interrupts and run to completion. A logical core can be paused to wait for an event.

#### 7.2 xTIME scheduler

The xTIME scheduler handles the events generated by xCORE Tile resources, such as channel ends, timers and I/O pins. It ensures that all events are serviced and synchronized, without the need for an RTOS. Events that occur at the I/O pins are handled by the Hardware-Response ports and fed directly to the appropriate xCORE Tile. An xCORE Tile can also choose to wait for a specified time to elapse, or for data to become available on a channel.

Tasks do not need to be prioritised as each of them runs on their own logical xCORE. It is possible to share a set of low priority tasks on a single core using cooperative multitasking.

#### 7.3 Hardware Response Ports

Hardware Response ports connect an xCORE tile to one or more physical pins and as such define the interface between hardware attached to the XS1-A16A-128-FB217, and the software running on it. A combination of 1bit, 4bit, 8bit, 16bit and 32bit ports are available. All pins of a port provide either output or input. Signals in different directions cannot be mapped onto the same port.

Figure 5: Port block diagram

The port logic can drive its pins high or low, or it can sample the value on its pins, optionally waiting for a particular condition. Ports are accessed using dedicated instructions that are executed in a single processor cycle.

Data is transferred between the pins and core using a FIFO that comprises a SERDES and transfer register, providing options for serialization and buffered data.

Each port has a 16-bit counter that can be used to control the time at which data is transferred between the port value and transfer register. The counter values can be obtained at any time to find out when data was obtained, or used to delay I/O until some time in the future. The port counter value is automatically saved as a timestamp, that can be used to provide precise control of response times.

The ports and xCONNECT links are multiplexed onto the physical pins. If an xConnect Link is enabled, the pins of the underlying ports are disabled. If a port is enabled, it overrules ports with higher widths that share the same pins. The pins on the wider port that are not shared remain available for use when the narrower port is enabled. Ports always operate at their specified width, even if they share pins with another port.

#### 7.4 Clock blocks

xCORE devices include a set of programmable clocks called clock blocks that can be used to govern the rate at which ports execute. Each xCORE tile has six clock blocks: the first clock block provides the tile reference clock and runs at a default frequency of 100MHz; the remaining clock blocks can be set to run at different frequencies.

Figure 6: Clock block diagram

A clock block can use a 1-bit port as its clock source allowing external application clocks to be used to drive the input and output interfaces.

In many cases I/O signals are accompanied by strobing signals. The xCORE ports can input and interpret strobe (known as readyln and readyOut) signals generated by external sources, and ports can generate strobe signals to accompany output data.

On reset, each port is connected to clock block 0, which runs from the processor reference clock.

#### 7.5 Channels and Channel Ends

Logical cores communicate using point-to-point connections, formed between two channel ends. A channel-end is a resource on an xCORE tile, that is allocated by the program. Each channel-end has a unique system-wide identifier that comprises a unique number and their tile identifier. Data is transmitted to a channel-end by an output-instruction; and the other side executes an input-instruction. Data can be passed synchronously or asynchronously between the channel ends.

#### 7.6 xCONNECT Switch and Links

XMOS devices provide a scalable architecture, where multiple xCORE devices can be connected together to form one system. Each xCORE device has an xCONNECT interconnect that provides a communication infrastructure for all tasks that run on the various xCORE tiles on the system.

The interconnect relies on a collection of switches and XMOS links. Each  $\times$ CORE device has an on-chip switch that can set up circuits or route data. The switches are connected by  $\times$ Connect Links. An XMOS link provides a physical connection

Figure 7: Switch, links and channel ends

between two switches. The switch has a routing algorithm that supports many different topologies, including lines, meshes, trees, and hypercubes.

The links operate in either 2 wires per direction or 5 wires per direction mode, depending on the amount of bandwidth required. Circuit switched, streaming and packet switched data can both be supported efficiently. Streams provide the fastest possible data rates between tiles, but each stream requires a single link to be reserved between switches on two tiles. All packet communications can be multiplexed onto a single link.

Information on the supported routing topologies that can be used to connect multiple devices together can be found in the XS1-L Link Performance and Design Guide, X2999.

### 8 Oscillator

The oscillator block provides:

- ▶ An oscillator circuit. Together with an external resonator (crystal or ceramic), the oscillator circuit can provide a clock-source for both the real-time counter and the xCORE Tile. The external resonator can be chosen by the designer to have the appropriate frequency and accuracy. If desired, an external oscillator can be used on the XI/CLK input pin, this must be a 1.8 V oscillator.

- ▶ A 20 MHz silicon oscillator. This enables the device to boot and execute code without requiring an external crystal. The silicon oscillator is not as accurate as an external crystal.

▶ A 31,250 Hz oscillator. This enables the real-time counter to operate whilst the device is in low-power mode. This oscillator is not as accurate as an external crystal.

The oscillator can be controlled through package pins, a set of peripheral registers, and a digital node control register.

A package pin OSC\_EXT\_N is used to select the oscillator to use on boot. It must be grounded to select an external resonator or connected to VDDIO to select the on-chip 20 MHz oscillator. If an external resonator is used, then it must be in the range 5-100 MHz. Two more package pins, MODEO and MODE1 are used to inform the node of the frequency.

The analog node runs at the frequency provided by the oscillator. Hence, increasing the clock frequency will speed up operation of the analog node, and will speed up communicating data with the digital node. The digital node has a PLL.

The PLL creates a high-speed clock that is used for the switch, tile, and reference clock.

The PLL multiplication value is selected through the two MODE pins, and can be changed by software to speed up the tile or use less power. The MODE pins are set as shown in Figure 8:

| Figure 8:      |

|----------------|

| PLL multiplier |

| values and     |

| MODE pins      |

| Oscillator | MC | DDE | Tile           | PLL Ratio | PLL | setting | gs |

|------------|----|-----|----------------|-----------|-----|---------|----|

| Frequency  | 1  | 0   | Frequency      |           | OD  | F       | R  |

| 5-13 MHz   | 0  | 0   | 130-399.75 MHz | 30.75     | 1   | 122     | 0  |

| 13-20 MHz  | 1  | 1   | 260-400.00 MHz | 20        | 2   | 119     | 0  |

| 20-48 MHz  | 1  | 0   | 167-400.00 MHz | 8.33      | 2   | 49      | 0  |

| 48-100 MHz | 0  | 1   | 196-400.00 MHz | 4         | 2   | 23      | 0  |

Figure 8 also lists the values of OD, F and R, which are the registers that define the ratio of the tile frequency to the oscillator frequency:

$$F_{core} = F_{osc} \times \frac{F+1}{2} \times \frac{1}{R+1} \times \frac{1}{OD+1}$$

OD, F and R must be chosen so that  $0 \le R \le 63$ ,  $0 \le F \le 4095$ ,  $0 \le OD \le 7$ , and  $260MHz \le F_{osc} \times \frac{F+1}{2} \times \frac{1}{R+1} \le 1.3GHz$ . The OD, F, and R values can be modified by writing to the digital node PLL configuration register.

The MODE pins must be held at a static value during and after deassertion of the system reset.

If a different tile frequency is required (eg, 500 MHz), then the PLL must be reprogrammed after boot to provide the required tile frequency. The XMOS tools perform this operation by default. Further details on configuring the clock can be found in the XS1-L Clock Frequency Control document, X1433.

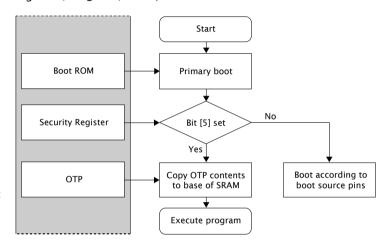

## 9 Boot Procedure

The device is kept in reset by driving RST\_N low. When in reset, all GPIO pins are high impedance. When the device is taken out of reset by releasing RST\_N the processor starts its internal reset process. After approximately 750,000 input clocks, all GPIO pins have their internal pull-resistor enabled, and the processor boots at a clock speed that depends on MODE0 and MODE1.

The processor boot procedure is illustrated in Figure 9. In normal usage, MODE[4:2] controls the boot source according to the table in Figure 10. If bit 5 of the security register (see §10.1) is set, the device boots from OTP.

Figure 9: Boot procedure

| MODE | MODE | MODE | Boot Source                                                                                              |

|------|------|------|----------------------------------------------------------------------------------------------------------|

| [4]  | [3]  | [2]  |                                                                                                          |

| Х    | 0    | 0    | None: Device waits to be booted via JTAG                                                                 |

| Х    | 0    | 1    | Reserved                                                                                                 |

| 0    | 1    | 0    | Tile0 boots from link B, Tile1 from channel end 0 via Tile0                                              |

| 0    | 1    | 1    | Tile0 boots from SPI, Tile1 from channel end 0 via Tile0                                                 |

| 1    | 1    | 0    | TileO and Tile1 independently enable link B and internal links (E, F, G, H), and boot from channel end 0 |

| 1    | 1    | 1    | TileO and Tile 1 boot from SPI independently                                                             |

Figure 10: Boot source pins

The boot image has the following format:

- ▶ A 32-bit program size *s* in words.

- ▶ Program consisting of  $s \times 4$  bytes.

- ➤ A 32-bit CRC, or the value 0x0D15AB1E to indicate that no CRC check should be performed.

The program size and CRC are stored least significant byte first. The program is loaded into the lowest memory address of RAM, and the program is started from that address. The CRC is calculated over the byte stream represented by the program size and the program itself. The polynomial used is 0xEDB88320 (IEEE 802.3); the CRC register is initialized with 0xFFFFFFFF and the residue is inverted to produce the CRC.

#### 9.1 Boot from SPI master

If set to boot from SPI master, the processor enables the four pins specified in Figure 11, and drives the SPI clock at 2.5 MHz (assuming a 400 MHz core clock). A READ command is issued with a 24-bit address 0x000000. The clock polarity and phase are 0 / 0.

Figure 11: SPI master pins

| Ī | Pin   | Signal | Description                |

|---|-------|--------|----------------------------|

| ſ | X0D00 | MISO   | Master In Slave Out (Data) |

| İ | X0D01 | SS     | Slave Select               |

|   | X0D10 | SCLK   | Clock                      |

| İ | X0D11 | MOSI   | Master Out Slave In (Data) |

The xCORE Tile expects each byte to be transferred with the *least-significant bit first*. Programmers who write bytes into an SPI interface using the most significant bit first may have to reverse the bits in each byte of the image stored in the SPI device.

If a large boot image is to be read in, it is faster to first load a small boot-loader that reads the large image using a faster SPI clock, for example 50 MHz or as fast as the flash device supports.

The pins used for SPI boot are hardcoded in the boot ROM and cannot be changed. If required, an SPI boot program can be burned into OTP that uses different pins.

#### 9.2 Boot from xConnect Link

If set to boot from an xConnect Link, the processor enables Link B around 200 ns after the boot process starts. Enabling the Link switches off the pull-down on resistors X0D16..X0D19, drives X0D16 and X0D17 low (the initial state for the Link), and monitors pins X0D18 and X0D19 for boot-traffic. X0D18 and X0D19 must be low at this stage. If the internal pull-down is too weak to drain any residual charge, external pull-downs of 10K may be required on those pins.

The boot-rom on the core will then:

- 1. Allocate channel-end 0.

- 2. Input a word on channel-end 0. It will use this word as a channel to acknowledge the boot. Provide the null-channel-end 0x0000FF02 if no acknowledgment is required.

- 3. Input the boot image specified above, including the CRC.

- 4. Input an END control token.

- 5. Output an END control token to the channel-end received in step 2.

- 6. Free channel-end 0.

- 7. Jump to the loaded code.

#### 9.3 Boot from OTP

If an xCORE tile is set to use secure boot (see Figure 9), the boot image is read from address 0 of the OTP memory in the tile's security module.

This feature can be used to implement a secure bootloader which loads an encrypted image from external flash, decrypts and CRC checks it with the processor, and discontinues the boot process if the decryption or CRC check fails. XMOS provides a default secure bootloader that can be written to the OTP along with secret decryption keys.

Each tile has its own individual OTP memory, and hence some tiles can be booted from OTP while others are booted from SPI or the channel interface. This enables systems to be partially programmed, dedicating one or more tiles to perform a particular function, leaving the other tiles user-programmable.

#### 9.4 Security register

The security register enables security features on the xCORE tile. The features shown in Figure 12 provide a strong level of protection and are sufficient for providing strong IP security.

## 10 Memory

#### 10.1 OTP

Each xCORE Tile integrates 8 KB one-time programmable (OTP) memory along with a security register that configures system wide security features. The OTP holds data in four sectors each containing 512 rows of 32 bits which can be used to implement secure bootloaders and store encryption keys. Data for the security register is loaded from the OTP on power up. All additional data in OTP is copied from the OTP to SRAM and executed first on the processor.

The OTP memory is programmed using three special I/O ports: the OTP address port is a 16-bit port with resource ID 0x100200, the OTP data is written via a 32-bit port with resource ID 0x200100, and the OTP control is on a 16-bit port with ID 0x100300. Programming is performed through libotp and xburn.

#### 10.2 SRAM

Each xCORE Tile integrates a single 64KBSRAM bank for both instructions and data. All internal memory is 32 bits wide, and instructions are either 16-bit or

| Feature              | Bit  | Description                                                                                                                                                                                                                    |

|----------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Disable JTAG         | 0    | The JTAG interface is disabled, making it impossible for the tile state or memory content to be accessed via the JTAG interface.                                                                                               |

| Disable Link access  | 1    | Other tiles are forbidden access to the processor state via the system switch. Disabling both JTAG and Link access transforms an xCORE Tile into a "secure island" with other tiles free for non-secure user application code. |

| Secure Boot          | 5    | The processor is forced to boot from address 0 of the OTP, allowing the processor boot ROM to be bypassed (see §9).                                                                                                            |

| Redundant rows       | 7    | Enables redundant rows in OTP.                                                                                                                                                                                                 |

| Sector Lock 0        | 8    | Disable programming of OTP sector 0.                                                                                                                                                                                           |

| Sector Lock 1        | 9    | Disable programming of OTP sector 1.                                                                                                                                                                                           |

| Sector Lock 2        | 10   | Disable programming of OTP sector 2.                                                                                                                                                                                           |

| Sector Lock 3        | 11   | Disable programming of OTP sector 3.                                                                                                                                                                                           |

| OTP Master Lock      | 12   | Disable OTP programming completely: disables updates to all sectors and security register.                                                                                                                                     |

| Disable JTAG-OTP     | 13   | Disable all (read & write) access from the JTAG interface to this OTP.                                                                                                                                                         |

| Disable Global Debug | 14   | Disables access to the DEBUG_N pin.                                                                                                                                                                                            |

|                      | 2115 | General purpose software accessable security register available to end-users.                                                                                                                                                  |

|                      | 3122 | General purpose user programmable JTAG UserID code extension.                                                                                                                                                                  |

Figure 12: Security register features

32-bit. Byte (8-bit), half-word (16-bit) or word (32-bit) accesses are supported and are executed within one tile clock cycle. There is no dedicated external memory interface, although data memory can be expanded through appropriate use of the ports.

### 10.3 Deep Sleep Memory

The XS1-A16A-128-FB217 device includes 128 bytes of deep sleep memory for state storage during sleep mode. Deep sleep memory is volatile and if device input power is remove, the data will be lost.

## 11 Analog-to-Digital Converter

The device has a 12-bit 1MSample/second Successive Approximation Register (SAR) Analogue to Digital Converter (ADC). It has 8 input pins which are multiplexed into the ADC. The sampling of the ADC is controlled using the ADC\_SAMPLE pin that should be wired to a GPIO pin, for example X0D24 (port 11). The sampling is triggered either by writing to the port, or by driving the pin externally. On each

rising edge of the sample pin the ADC samples, holds and converts the data value from one of the analog input pins. Each of the 8 inputs can be enabled individually. Each of the enabled analog inputs is sampled in turn, on successive rising edges of the sample pin. The data is transmitted to the channel-end that the user configures during initialization of the ADC. Data is transmitted over the channel in individual packets, or in packets that contain multiple consecutive samples. The ADC uses an external reference voltage, nominally 3V3, which represents the full range of the ADC. The ADC configuration registers are documented in Appendix F.

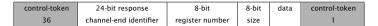

The minimum latency for reading a value from the ADC into the xCORE register is shown in Figure 13:

Figure 13:

Minimum

latency to

read sample

from ADC to

xCORE

| Sample | Tile clock frequency | Start of packet | Subsequent samples |

|--------|----------------------|-----------------|--------------------|

| 32-bit | 500 MHz              | 840 ns          | 710 ns             |

| 32-bit | 400 MHz              | 870 ns          | 740 ns             |

| 16-bit | 500 MHz              | 770 ns          | 640 ns             |

| 16-bit | 400 MHz              | 800 ns          | 670 ns             |

## 12 Supervisor Logic

An independent supervisor circuit provides power-on-reset, brown-out, and watch-dog capabilities. This facilitates the design of systems that fail gracefully, whilst keeping BOM costs down.

The reset supervisor holds the chip in reset until all power supplies are good. This provides a power-on-reset (POR). An external reset is optional and the pin RST\_N can be left not-connected.

If at any time any of the power supplies drop because of too little supply or too high a demand, the power supervisor will bring the chip into reset until the power supplies have been restored. This will reboot the system as if a cold-start has happened.

The 16-bit watchdog timer provides 1ms accuracy and runs independently of the real-time counter. It can be programmed with a time-out of between 1 ms and 65 seconds (Appendix E). If the watchdog is not set before it times out, the XS1-A16A-128-FB217 is reset. On boot, the program can read a register to test whether the reset was due to the watchdog. The watchdog timer is only enabled and clocked whilst the processor is in the AWAKE power state.

## 13 Energy management

XS1-A16A-128-FB217 devices can be powered by:

- ► An external 5v core and 3.3v I/O supply.

- ► A single 3.3v supply.

#### 13.1 DC-DC

XS1-A16A-128-FB217 devices include two DC-DC buck converters which can be configured to take input voltages between 3.3-5V power supply and output circuit voltages (nominally 1.8V and 1.0V) required by the analog peripherals and digital node.

#### 13.2 Power mode controller

The device transitions through multiple states during the power-up and powerdown process.

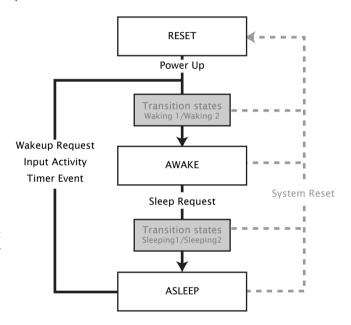

Figure 14: XS1-A16A-128-FB217 Power Up States and Transitions

The device is quiescent in the ASLEEP state, and is running in the AWAKE state. The other states allow a controlled transition between AWAKE and ASLEEP.

A transition from AWAKE state to ASLEEP state is instigated by a write to the general control register. Sleep requests must only be made in the AWAKE state.

A transition from the ASLEEP state into the AWAKE state is instigated by a wakeup request triggered by an input, or a timer. The device only responds to a wakeup stimulus in the ASLEEP state. If wakeup stimulus occurs whilst transitioning from AWAKE to ASLEEP, the appropriate response occurs when the ASLEEP state is reached.

Configuration is through a set of registers documented in Appendix J.

### 13.3 Deep Sleep Modes and Real-Time Counter

The normal mode in which the XS1-A16A-128-FB217 operates is the AWAKE mode. In this mode, all cores, memory, and peripherals operate as normal. To save power, the XS1-A16A-128-FB217 can be put into a deep sleep mode, called ASLEEP, where the digital node is powered down, and most peripherals are powered down. The XS1-A16A-128-FB217 will stay in the ASLEEP mode until one of two conditions:

- 1. An external pin is asserted or deasserted (set by the program);

- 2. The 64-bit real-time counter reaches a value set by the program; or

When the chip is awake, the real-time counter counts the number of clock ticks on the oscillator. As such, the real-time counter will run at a fixed ratio, but synchronously with the 100 MHz timers on the xCORE Tile. When asleep, the real-time counter can be automatically switched to the 31,250 Hz silicon oscillator to save power (see Appendix H). To ensure that the real-time counter increases linearly over time, a programmable value is added to the counter on every 31,250 Hz clock-tick. This means that the clock will run at a granularity of 31,250 Hz but still maintain real-time in terms of the frequency of the main oscillator. If an accurate clock is required, even whilst asleep, then an external crystal or oscillator shall be provided that is used in both AWAKE and ASLEEP state.

The designer has to make a trade-off between accuracy of clocks when asleep and awake, costs, and deep-sleep power consumption. Four example designs are shown in Figure 15.

Figure 15: Example trade-offs in oscillator selection

| Clocks         | used           | Power   | ВОМ     | Accuracy |         |  |  |

|----------------|----------------|---------|---------|----------|---------|--|--|

| Awake          | Asleep         | Asleep  | costs   | Awake    | Asleep  |  |  |

| 20 Mhz SiOsc   | 31,250 SiOsc   | lowest  | lowest  | lowest   | lowest  |  |  |

| 24 MHz Crystal | 31,250 SiOsc   | lowest  | medium  | highest  | lowest  |  |  |

| 5 MHz ext osc  | 5 MHz ext osc  | medium  | highest | highest  | highest |  |  |

| 24 MHz Crystal | 24 MHz crystal | highest | medium  | highest  | highest |  |  |

During deep-sleep, the program can store some state in 128 bytes of Deep Sleep Memory.

### 13.4 Requirements during sleep mode

Whilst in sleep mode, the device must still be powered as normal over 3V3 or 5V0 on VSUP, and 3V3 on VDDIO; however it will draw less power on both VSUP and VDDIO.

For best results (lowest power):

- ▶ The XTAL bias and XTAL oscillators should be switched off.

- ▶ The sleep register should be configured to

- ▶ Disable all power supplies except DCDC2.

- ▶ Set all power supplies to PFM mode

- Mask the clock

- Assert reset

- ▶ All GPIO and JTAG pins should be quiescent, and none should be driven against a pull-up or pull-down.

- ▶ 3V3 should be supplied as the input voltage to VSUP.

This will result in a power consumption of less than 100 uA on both VSUP and VDDIO.

If any power supply loses power-good status during the asleep-to-awake or awake-to-asleep transitions, a system reset is issued.

## 14 JTAG

The JTAG module can be used for loading programs, boundary scan testing, incircuit source-level debugging and programming the OTP memory.

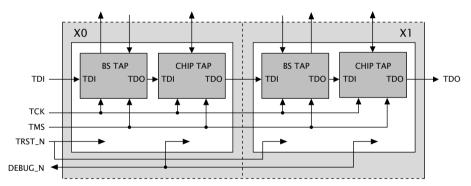

Figure 16: JTAG chain structure

The JTAG chain structure is illustrated in Figure 16. Directly after reset, three TAP controllers are present in the JTAG chain for each xCORE Tile: the debug TAP, the boundary scan TAP and the processor TAP. The debug TAP provides access into the peripherals including the ADC. The boundary scan TAP is a standard 1149.1 compliant TAP that can be used for boundary scan of the I/O pins. The processor TAP provides access into the xCORE Tile, switch and OTP for loading code and debugging.

The JTAG module can be reset by holding TMS high for five clock cycles.

The DEBUG\_N pin is used to synchronize the debugging of multiple processors. This pin can operate in both output and input mode. In output mode and when configured to do so, DEBUG\_N is driven low by the device when the processor hits a debug break point. Prior to this point the pin will be tri-stated. In input mode and when configured to do so, driving this pin low will put the processor into debug

mode. Software can set the behavior of the processor based on this pin. This pin should have an external pull up of  $4K7-47K\,\Omega$  or left not connected in single core applications.

The JTAG device identification register can be read by using the IDCODE instruction. Its contents are specified in Figure 17.

Figure 17: IDCODE return value

| Bi | t31                                       |       |  |  |  |  |   |   |   |   |     | D | evice | lde | ntifi | catio | on R                | egist | er |  |  |   |   |  |  |   |  |  | E | Bit0 |

|----|-------------------------------------------|-------|--|--|--|--|---|---|---|---|-----|---|-------|-----|-------|-------|---------------------|-------|----|--|--|---|---|--|--|---|--|--|---|------|

|    | Version Part Number Manufacturer Identity |       |  |  |  |  |   |   |   |   |     |   |       |     |       | 1     |                     |       |    |  |  |   |   |  |  |   |  |  |   |      |

| 0  | 0 0 0 0 0 0 0 0 0 0 0                     |       |  |  |  |  | 0 | 0 | 0 | 0 | 0   | 0 | 0     | 1   | 1     | 0     | 0 1 1 0 0 0 1 1 0 0 |       |    |  |  | 1 | 1 |  |  |   |  |  |   |      |

|    |                                           | 0 0 0 |  |  |  |  |   |   |   |   | 0 3 |   |       |     |       |       |                     | 6 3   |    |  |  |   |   |  |  | 3 |  |  |   |      |

The JTAG usercode register can be read by using the USERCODE instruction. Its contents are specified in Figure 18. The OTP User ID field is read from bits [22:31] of the security register on xCORE Tile 0, see §10.1 (all zero on unprogrammed devices).

Figure 18: USERCODE return value

| В                                   | it3               | 1 |   |  |  |   |   |   |   |   |   |   |   | -                             | Jser | code | Reg | giste | r  |  |  |   |   |   |   |   |  |  |   | В | it0 |

|-------------------------------------|-------------------|---|---|--|--|---|---|---|---|---|---|---|---|-------------------------------|------|------|-----|-------|----|--|--|---|---|---|---|---|--|--|---|---|-----|

| OTP User ID Unused Silicon Revision |                   |   |   |  |  |   |   |   |   |   |   |   |   |                               |      |      |     |       |    |  |  |   |   |   |   |   |  |  |   |   |     |

| 0                                   | 0 0 0 0 0 0 0 0 0 |   |   |  |  |   |   | 0 | 0 | 0 | 0 | 0 | 1 | 1 0 1 1 0 0 0 0 0 0 0 0 0 0 0 |      |      |     |       |    |  |  | 0 | 0 | 0 | 0 |   |  |  |   |   |     |

|                                     |                   | ( | ) |  |  | ( | ) |   |   | ( | 0 |   |   | :                             | 2    |      |     | (     | Ξ. |  |  | ( | ) |   | ( | ) |  |  | ( | ) |     |

## 15 Board Integration

XS1-A16A-128-FB217 devices are optimized for layout on low cost PCBs using standard design rules. Careful layout is required to maximize the device performance. XMOS therefore recommends that the guidelines in this section are followed when laying out boards using the device.

The XS1-A16A-128-FB217 includes two DC-DC buck converters that take input voltages between 3.3-5V and output the 1.8V and 1.0V circuits required by the digital core and analogue peripherals. The DC-DC converters should have a 4.7uF X5R or X7R ceramic capacitor and a 100nF X5R or X7R ceramic capacitor on the VSUP input pins W1 and W2. These capacitors must be placed as close as possible to the those pins (within a maximum of 5mm), with the routing optimized to minimize the inductance and resistance of the traces.

The SW output pin must have an LC filter on the output with a 4.7uH inductor and 22uF X5R capacitor. The capacitor must have maximum ESR value of 0.015R, and the inductor should have a maximum DCR value of 0.07R. A list of suggested inductors is in Figure 19.

Figure 19: Example 4.7  $\mu$ H inductors

|        | Part number    | Current | Max DCR      | Package      |

|--------|----------------|---------|--------------|--------------|

| Wurth  | 744043004      | 1550 mA | 70 $m\Omega$ | 4.8 x 4.8 mm |

| Murata | LQH55DN4R7M03L | 2700 mA | $57~m\Omega$ | 5750 (2220)  |

The traces from the SW output pins to the inductor and from the output capacitor back to the VDD pins must be routed to minimize the coupling between them.

The power supplies must be brought up monotonically and input voltages must not exceed specification at any time.

The VDDIO supply to the XS1-A16A-128-FB217 requires a 100nF X5R or X7R ceramic decoupling capacitor placed as close as possible to the supply pins. VDDIO\_OUT is the switched IO supply; it is only supplied when the chip is AWAKE. This pin can be used to provide extra decoupling, or it can be used to switch other devices off during sleep mode, for example a SPI flash. No more than 240 mA should be drawn on VDDIO at any time: this includes any supply sourced statically (e.g., driving a LED from a GPIO pin), any dynamic power consumption (e.g., toggling a GPIO pin at a high frequency) and any devices powered through VDDIO OUT.

If the ADC Is used, it requires a 100nF X5R or X7R ceramic decoupling capacitor placed as close as possible to the AVDD pin. Care should be taken to minimize noise on these inputs, and if necessary an extra 10uF decoupling capacitor and ferrite bead can be used to remove noise from this supply.

The crystal oscillator requires careful routing of the XI / XO nodes as these are high impedance and very noise sensitive. Hence, the traces should be as wide and short as possible, and routed over a continuous ground plane. They should not be routed near noisy supply lines or clocks. The device has a load capacitance of 18pF for the crystal. Care must be taken, so that the inductance and resistance of the ground returns from the capacitors to the ground of the device is minimized.

#### 15.1 Land patterns and solder stencils

The land pattern recommendations in this document are based on a RoHS compliant process and derived, where possible, from the nominal *Generic Requirements for Surface Mount Design and Land Pattern Standards* IPC-7351B specifications. This standard aims to achieve desired targets of heel, toe and side fillets for solderjoints.

Solder paste and ground via recommendations are based on our engineering and development kit board production. They have been found to work and optimized as appropriate to achieve a high yield. These factors should be taken into account during design and manufacturing of the PCB.

The following land patterns and solder paste contains recommendations. Final land pattern and solder paste decisions are the responsibility of the customer. These should be tuned during manufacture to suit the manufacturing process.

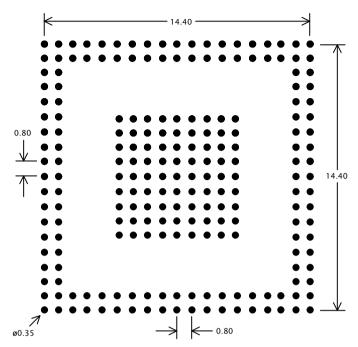

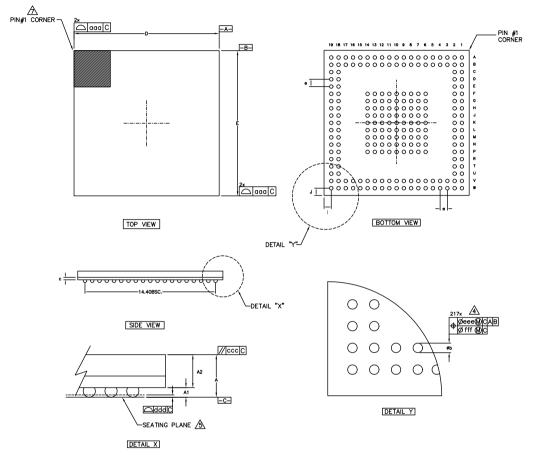

The package is a 217 pin Fine Ball Grid Array package on a 0.8mm pitch with 0.4mm balls.

An example land pattern is shown in Figure 20.

Pad widths and spacings are such that solder mask can still be applied between the pads using standard design rules. This is highly recommended to reduce solder shorts.

**Figure 20:** Example land pattern

#### 15.2 Ground and Thermal Vias

Vias next to every other ground ball into the ground plane of the PCB are recommended for a low inductance ground connection and good thermal performance. Vias with with a 0.6mm diameter annular ring and a 0.3mm drill would be suitable.

### 15.3 Moisture Sensitivity

XMOS devices are, like all semiconductor devices, susceptible to moisture absorption. When removed from the sealed packaging, the devices slowly absorb moisture from the surrounding environment. If the level of moisture present in the device is too high during reflow, damage can occur due to the increased internal vapour pressure of moisture. Example damage can include bond wire damage, die lifting, internal or external package cracks and/or delamination.

All XMOS devices are Moisture Sensitivity Level (MSL) 3 - devices have a shelf life of 168 hours between removal from the packaging and reflow, provided they are stored below 30C and 60% RH. If devices have exceeded these values or an included moisture indicator card shows excessive levels of moisture, then the parts should be baked as appropriate before use. This is based on information from *Joint IPC/JEDEC Standard For Moisture/Reflow Sensitivity Classification For Nonhermetic Solid State Surface-Mount Devices* J-STD-020 Revision D.

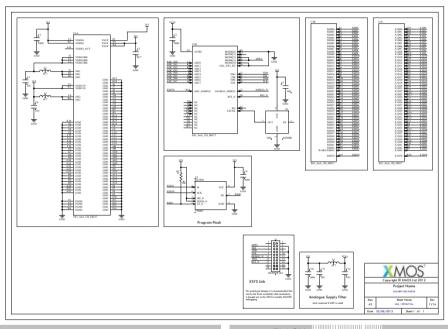

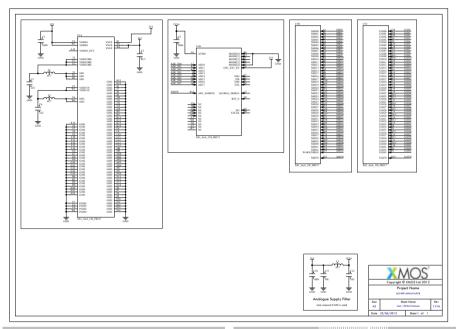

## 16 Example XS1-A16A-128-FB217 Board Designs

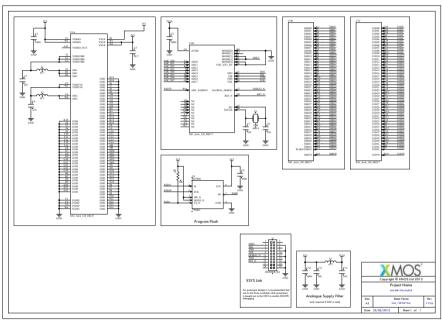

This section shows example schematics and layout for a 2-layer PCB.

- ▶ Figures 21 shows example schematics and layout. It uses a 24 MHz crystal for the clock, and an SPI flash for booting. XS1-A16A-128-FB217 is powered directly from 3V3.

- ▶ Figures 22 shows example schematics and layout for a design that uses an oscillator rather than a crystal. If required a 3V3 oscillator can be used (for example when sharing an oscillator with other parts of the design), but a resistor bridge must be included to reduce the XI/CLK input from 3V3 to 1V8.

- ▶ Figure 23 shows example schematics and layout for a design that runs off the internal 20 MHz oscillator. The XS1-A16A-128-FB217 is powered directly from 3V3.

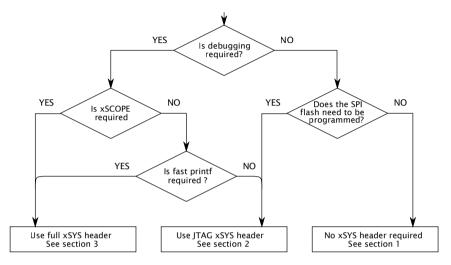

Flash, AVDD, RST, and JTAG connectivity are all optional. Flash can be removed if the processor boots from OTP. The AVDD decoupler and wiring can be removed if the ADC is not used. RST\_N and all JTAG wiring can be removed if debugging is not required (see Appendix M)

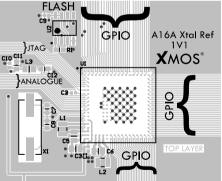

Figure 21:

Example

XTAL

schematic,

with top and

bottom

layout of a

2-layer PCB

Figure 22:

Example Oscillator schematic, with top and bottom layout of a 2-layer PCB

··· ···

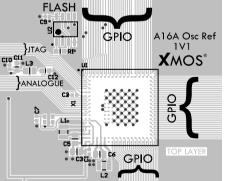

Figure 23:

Example

minimal

system

schematic,

with top and

bottom

layout of a

2-layer PCB

# 17 DC and Switching Characteristics

## 17.1 Operating Conditions

| Symbol | Parameter                                  | MIN  | TYP  | MAX  | UNITS | Notes |

|--------|--------------------------------------------|------|------|------|-------|-------|

| VSUP   | Power Supply (3.3V Mode)                   | 3.00 | 3.30 | 3.60 | V     |       |

| V 301  | Power Supply (5V Mode)                     | 4.50 | 5.00 | 5.50 | V     |       |

| VDDIO  | I/O supply voltage                         | 3.00 | 3.30 | 3.60 | V     |       |

| AVDD   | Analog Supply and Reference<br>Voltage     | 3.00 | 3.30 | 3.60 | V     |       |

| Cl     | xCORE Tile I/O load capacitance            |      |      | 25   | pF    |       |

| Та     | Ambient operating temperature (Commercial) | 0    |      | 70   | °C    |       |

|        | Ambient operating temperature (Industrial) | -40  |      | 85   | °C    |       |

| Tj     | Junction temperature                       |      |      | 125  | °C    |       |

| Tsta   | Storage temperature                        | -65  |      | 150  | °C    |       |

Figure 24: Operating conditions

## 17.2 DC1 Characteristics

| Symbol    | Parameter                           | MIN  | TYP  | MAX  | UNITS     | Notes |