# 2.5/3.3V 200 MHz High-Speed, Low-Jitter, Low-Skew, Zero-Delay Clock Buffer with 5 Outputs

#### **Features**

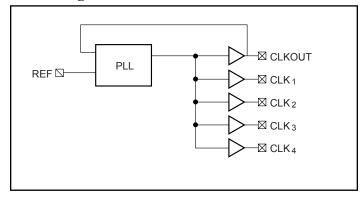

- Phase-Lock Loop Clock Distribution (Zero Input-to-Output Delay)

- Internal feedback connection

- Distributes one to one bank of five outputs

- High-Performance

- 30 MHz to 220 MHz operation frequency range

- <100ps output-to-output skew

- <100ps cycle-to-cycle jitter

- Low Power Consumption 25mA (outputs unloaded)

- Spread-spectrum capable

- Power supply

- $\pm 2.5 V \pm 5\%$

- +3.3V ±10%

- Temperature range

- -40°C to +85°C Industrial temp range

- Packaging (Pb-free & Green):

- -8-pin TSSOP (L8)

- —8-pin SOIC (W8)

### **Description**

The PI6C22405-1H is a low-jitter, low-skew, high-speed Zero-Delay Buffer with 5 outputs designed to address high-speed clock distribution applications.

The PI6C22405-1H features an internal patented Phase Lock Loop (PLL) with high drive output capability and internal feedback.

The PI6C22405-1H operates from a 2.5V±5% or 3.3V±10% supply, guaranteed over the full industrial temperature range of -40°C to +85°C. All support documentation can be found on Pericom's web site at: www.pericom.com.

Pericom can customize these devices for specific requirements.

## **Block Diagram**

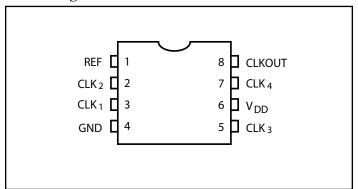

# **Pin Configuration**

#### **Pin Description**

| Pin           | Signal                     | Description                                           |  |

|---------------|----------------------------|-------------------------------------------------------|--|

| 1             | REF                        | Reference clock input with weak pull down.            |  |

| 2, 3,<br>5, 7 | CLK2, CLK1,<br>CLK3, CLK4, | Clock output. Clock outputs contain a weak pull-down. |  |

| 8             | CLKOUT                     | Clock output. Internal feedback on this pin.          |  |

| 4             | GND                        | Ground                                                |  |

| 6             | $V_{\mathrm{DD}}$          | Power                                                 |  |

# Maximum Ratings (1)

| Supply Voltage                        |                |

|---------------------------------------|----------------|

| V <sub>DD</sub>                       | 0.5V to +4.6V  |

| REF                                   | 0.5V to +4.6V  |

| Input Current                         | 50mA           |

| Output Current                        | ±50mA          |

| Lead Temperature (soldering, 10 sec.) | +260°C         |

| Storage Temperature (Ts)              | 65°C to +150°C |

| Junction Temperature                  | +150°C         |

|                                       |                |

# **Operation Ratings**<sup>(2)</sup>

| Supply Voltage                                  |

|-------------------------------------------------|

| V <sub>DD</sub> +3.0V to +3.6V                  |

| V <sub>DD</sub> +2.375V to +2.625V              |

| Operating Temperature (industrial)40°C to +85°C |

| Package Thermal Resistance (2)                  |

| θЈА                                             |

| Still-Air157°C/W                                |

| θЈВ                                             |

| Junction-to-Board42°C                           |

#### **Notes:**

- 1. Stresses greater then those listed under Maximum Ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of the this specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

- 2.  $\theta$ JA and  $\theta$ JB values are determined for a 4-layer board in still-air, unless otherwise stated.

#### **DC Electrical Characteristics**

| Parameter         | Description           | Test Conditions                    |                 |      | Max. | Units |

|-------------------|-----------------------|------------------------------------|-----------------|------|------|-------|

| 17                | Innut I OW Voltage    | $V_{DD} = 3.3V$                    |                 |      | 0.8  |       |

| $V_{ m IL}$       | Input LOW Voltage     | $V_{\mathrm{DD}} = 2.5 \mathrm{V}$ |                 |      | 0.7  | V     |

| $V_{\mathrm{IH}}$ | Innut IIICII Valta aa | $V_{DD} = 3.3V$                    |                 | 2.0  |      |       |

|                   | Input HIGH Voltage    | $V_{\rm DD} = 2.5 \mathrm{V}$      |                 | 1.7  |      |       |

| $I_{\mathrm{IL}}$ | Input LOW Current     | $V_{IN} = 0V$                      |                 |      | 10   |       |

| $I_{\mathrm{IH}}$ | Input HIGH Current    | $V_{IN} = V_{DD}$                  |                 |      | 100  | μA    |

| V <sub>OL</sub>   | Output LOW Voltage    | $I_{OL} = 12$ mA                   | $V_{DD} = 3.3V$ |      | 0.25 | V     |

|                   |                       |                                    | $V_{DD} = 2.5V$ |      | 0.35 |       |

| V <sub>OH</sub>   | Output HIGH Voltage   | $V_{DD} = 2.5V$ , $I_{OH} = -12mA$ |                 | 1.9  |      |       |

|                   |                       | $V_{DD} = 3.3V, I_{OH} = -12mA$    |                 | 2.55 |      |       |

| $I_{DD}$          | Supply Current        | Unloaded outputs 66 MHz            |                 |      | 22   | mA    |

#### **AC Electrical Characteristics**

| Parameter        | Description                                                       | Test Conditions                                        |                           | Min.                                             | Тур. | Max. | Units |

|------------------|-------------------------------------------------------------------|--------------------------------------------------------|---------------------------|--------------------------------------------------|------|------|-------|

| F <sub>O</sub>   | Output Frequency                                                  | $V_{DD} = 2.5V, C_L = 15pF$                            |                           | 10                                               |      | 200  | MHz   |

|                  |                                                                   | $V_{DD} = 3.3V, C_L = 15pF$                            |                           | 10                                               |      | 220  | MHz   |

| BW               | Bandwidth for PLL                                                 | $V_{DD} = 2.5V$                                        |                           |                                                  | 0.8  |      | MHz   |

|                  |                                                                   | $V_{DD} = 3.3V$                                        |                           |                                                  | 1.5  |      |       |

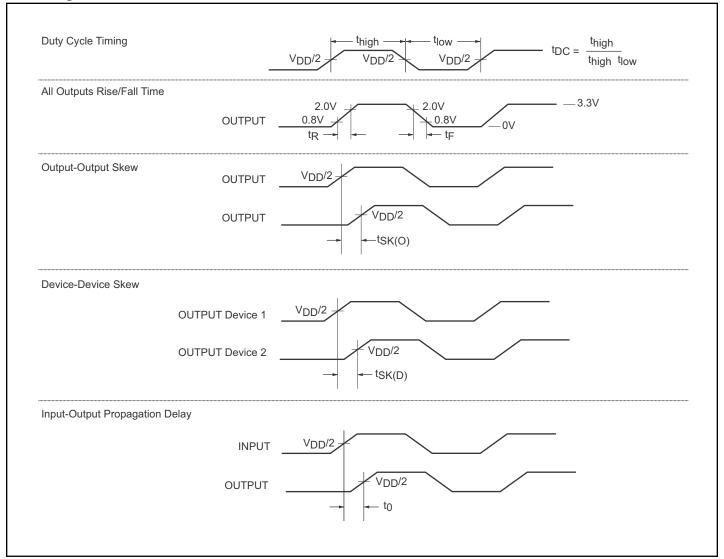

| $t_{DC}$         | Duty Cycle <sup>(1)(4)</sup>                                      | Measured at V <sub>DD</sub> /2, 10pF load              |                           | 45                                               | 50   | 55   | %     |

| to               | Rise Time <sup>(1)(4)</sup>                                       | For 3.3V: Measured between 0.8V and 2.0V @ 10pF        |                           |                                                  |      | 1    |       |

| $t_{R}$          | Kise Time ( )                                                     | For 2.5V: Measured between 0.6V and 1.8V @ 10pF        |                           |                                                  |      | 1.8  | nc    |

| to               | Fall Time <sup>(1)(4)</sup>                                       | For 3.3V: Measured bety                                | ween 0.8V and 2.0V @ 10pF |                                                  |      | 1    | ns    |

| $t_{\mathrm{F}}$ | ran rime(*)(*)                                                    | For 2.5V: Measured between 0.6V and 1.8V @ 10pF        |                           |                                                  |      | 1.8  |       |

| f 17.5           | Output to Output Skew <sup>(2)</sup>                              | All outputs equally                                    | $V_{DD} = 3.3V$           |                                                  |      | 90   |       |

| $t_{sk(o)}$      | Output to Output Skew(=)                                          | loaded                                                 | $V_{DD} = 2.5V$           |                                                  |      | 90   | ps    |

| 4                | Delay, REF Rising Edge<br>to CLKOUT Rising<br>Edge <sup>(2)</sup> | Measured at V <sub>DD</sub> /2 @ 66MHz                 | $V_{DD} = 3.3V$           | -100                                             |      | 100  |       |

| $t_0$            |                                                                   |                                                        | $V_{DD} = 2.5V$           | -200                                             |      | 200  |       |

| $t_{SK(D)}$      | Device-to-device Skew <sup>(3)</sup>                              | Measured at V <sub>DD</sub> /2 on CLKx pins of device  |                           | -300                                             |      | +300 |       |

| t <sub>JIT</sub> | Cycle-to-Cycle Jitter                                             | 15pF load, >66MHz,<br>standard drive                   | $V_{DD} = 3.3V$           |                                                  | 47   | 110  | ps    |

|                  |                                                                   |                                                        | $V_{\rm DD} = 2.5 V$      |                                                  | 42   | 90   |       |

|                  |                                                                   | 15pF load, >66MHz,<br>high drive                       | $V_{DD} = 3.3V$           |                                                  | 45   | 100  |       |

|                  |                                                                   |                                                        | $V_{DD} = 2.5V$           |                                                  | 40   | 80   |       |

|                  |                                                                   | 30pF load, >66MHz, standard drive                      | $V_{DD} = 3.3V$           |                                                  | 63   | 120  |       |

|                  |                                                                   |                                                        | $V_{DD} = 2.5V$           |                                                  | 83   | 130  |       |

|                  |                                                                   | 30pF load, >66MHz,<br>high drive                       | $V_{DD} = 3.3V$           |                                                  | 51   | 115  |       |

|                  |                                                                   |                                                        | $V_{DD} = 2.5V$           |                                                  | 66   | 115  |       |

| tрj              | Period Jitter (Peak)                                              | 15pF load, >66MHz,<br>standard drive                   | $V_{DD} = 3.3V$           |                                                  | 39   | 90   | ps    |

|                  |                                                                   |                                                        | $V_{DD} = 2.5V$           |                                                  | 28   | 60   |       |

|                  |                                                                   | 15pF load, >66MHz,<br>high drive                       | $V_{DD} = 3.3V$           |                                                  | 39   | 85   |       |

|                  |                                                                   |                                                        | $V_{DD} = 2.5V$           |                                                  | 27   | 55   |       |

|                  |                                                                   | 30pF load, >66MHz, standard drive  30pF load, >66MHz,  | $V_{DD} = 3.3V$           |                                                  | 48   | 85   |       |

|                  |                                                                   |                                                        | $V_{\rm DD} = 2.5 V$      | <del>                                     </del> | 75   | 90   |       |

|                  |                                                                   |                                                        | $V_{DD} = 3.3V$           |                                                  | 43   | 75   |       |

|                  | (1)                                                               | high drive                                             | $V_{DD} = 2.5V$           |                                                  | 60   | 80   |       |

| $t_{LOCK}$       | PLL Lock Time (1)                                                 | Stable power supply, valid clocks presented on REF pin |                           |                                                  |      | 1.0  | ms    |

#### Note:

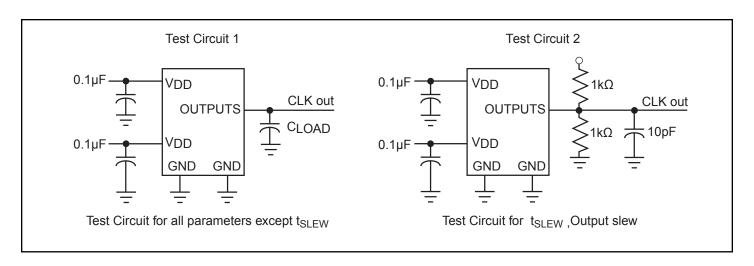

- 1. See Switching Waveforms

- 2. All clock output should have the same loading to achieve zero delay between the input and outputs and zero output-to-output skew. Since the CLKOUT pin is the internal feedback to the PLL, its relative loading can adjust the input-to-output delay. If input-to-output delay adjustments are needed, the CLKOUT load may be changed to vary the delay between the REF input to the clock outputs. Output-to-output skew includes CLK 1-4.

- 3. Specifications are guaranteed by design and not production tested.

- 4. Measured at 100MHz.

## **Switching Waveforms**

PS9029A 03/17/10 10-0137 4

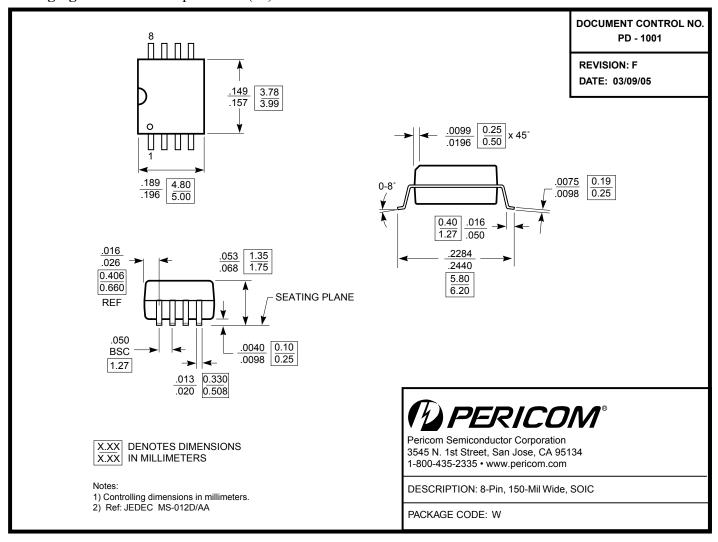

## Packaging Mechanical: 8-pin SOIC (W)

#### Note:

• For latest package info, please check: http://www.pericom.com/products/packaging/mechanicals.php

10-0137 5 PS9029A 03/17/10

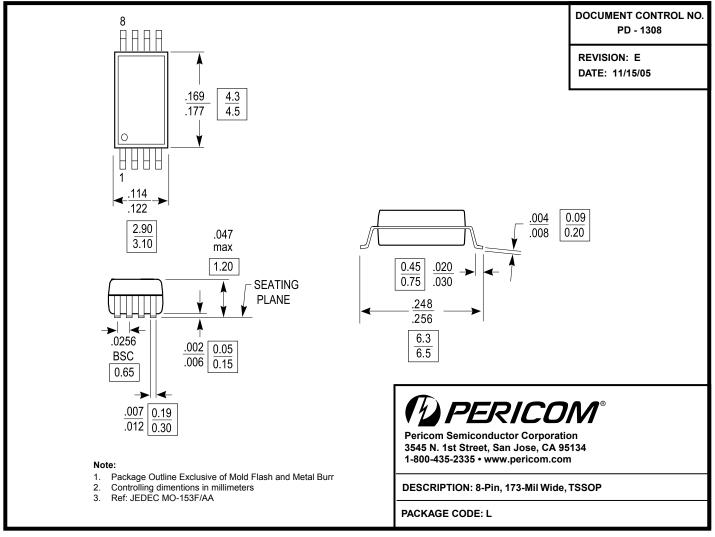

#### Packaging Mechanical: 8-pin TSSOP (L)

#### Note:

• For latest package info, please check: http://www.pericom.com/products/packaging/mechanicals.php

# Ordering Information<sup>(1,2,3)</sup>

| Ordering Code   | Package Code | Package Description                                 |

|-----------------|--------------|-----------------------------------------------------|

| PI6C22405-1HWE  | W            | Pb-free & Green, 8-pin SOIC                         |

| PI6C22405-1HWIE | W            | Pb-free & Green, 8-pin SOIC, Industrial temp range  |

| PI6C22405-1HLE  | L            | Pb-free & Green, 8-pin TSSOP                        |

| PI6C22405-1HLIE | L            | Pb-free & Green, 8-pin TSSOP, Industrial temp range |

#### **Notes:**

- 1. Latest Thermal characteristics can be found on the company web site at www.pericom.com/packaging/

- 2. E = Pb-free & Green

- 3. Adding an X suffix = Tape/Reel

Pericom Semiconductor Corporation • 1-800-435-2336 • www.pericom.com