# MC68EN302

# Integrated Multiprotocol Processor with Ethernet Reference Manual

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters can and do vary in different applications. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and expenses, and manufacture of the part. Motorola and expenses of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

#### **Literature Distribution Centers:**

USA/EUROPE: Motorola Literature Distribution; P.O. Box 20912, Arizona 85036.

JAPAN: Nippon Motorola Ltd.; 4-32-1, Nishi-Gotanda, Shinagawa-ku, Tokyo 141 Japan.

ASIA-PACIFIC: Motorola Semiconductors H.K. Ltd.; Silicon Harbour Center, No. 2 Dai King Street, Tai Po Industrial Estate,

# **Preface**

The complete documentation package for the MC68EN302 consists of MC68EN302RM/AD, the *MC68EN302 Integrated Multiprotocol Processor with Ethernet*, MC68302UM/AD, the *MC68302 Integrated Multiprotocol Processor*, MC68EN302/D, the *MC68EN302 Integrated Multiprotocol Processor with Ethernet Product Brief*, and M68000PM/AD, the *M68000 Programmer's Reference Manual*.

The MC68EN302 Integrated Multiprotocol Processor with Ethernet User's Manual describes the programming, capabilities, registers, and operation of the MC68EN302 that differs from the MC68302; the MC68302 Integrated Multiprotocol Processor describes the original MC68302, the MC68EN302 Integrated Multiprotocol Processor with Ethernet Product Brief provides a brief description of the MC68EN302 capabilities; and the M68000 Programmer's Reference Manual describes programming and the instruction set for the IMP processor.

This user's manual is organized as follows:

| Section 1 | Introduction                             |

|-----------|------------------------------------------|

| Section 2 | Module Bus Controller                    |

| Section 3 | DRAM Control Module (DCM)                |

| Section 4 | Ethernet Controller                      |

| Section 5 | Signal Description                       |

| Section 6 | Applications                             |

| Section 7 | IEEE 1149 Test Access Port (TAP)         |

| Section 8 | Electrical Specifications                |

| Section 9 | Ordering Information and Mechanical Data |

# **Applications and Technical Information**

For questions or comments pertaining to technical information, questions, and applications, please contact one of the following sales offices nearest you.

# — Sales Offices —

#### **UNITED STATES**

| ALABAMA, Huntsville ARIZONA, Tempe CALIFORNIA, Agoura Hills CALIFORNIA, Los Angeles CALIFORNIA, Irvine CALIFORNIA, Roseville CALIFORNIA, San Diego CALIFORNIA, Sunnyvale COLORADO, Colorado Springs COLORADO, Denver CONNECTICUT, Wallingford FLORIDA, Maitland FLORIDA, Pompano Beach/ Fort Lauderdal FLORIDA, Clearwater GEORGIA, Atlanta IDAHO, Boise ILLINOIS, Chicago/Hoffman Estates INDIANA, Fort Wayne INDIANA, Fort Wayne INDIANA, Kokomo IOWA, Cedar Rapids KANSAS, Kansas City/Mission MARYLAND, Columbia | (205) 464-6800<br>(602) 897-5056<br>(818) 706-1929<br>(310) 417-8848<br>(714) 753-7360<br>(916) 922-7152<br>(619) 541-2163<br>(408) 749-0510<br>(719) 599-7497<br>(303) 337-3434<br>(203) 949-4100<br>(407) 628-2636<br>(305) 486-9776<br>(813) 538-7750<br>(404) 729-7100<br>(208) 323-9413<br>(708) 490-9500<br>(219) 436-5818<br>(317) 571-0400<br>(317) 457-6634<br>(319) 373-1328<br>(913) 451-8555<br>(410) 381-1570 | MASSACHUSETTS, Marborough MASSACHUSETTS, Woburn MICHIGAN, Detroit MINNESOTA, Minnetonka MISSOURI, St. Louis NEW JERSEY, Fairfield NEW YORK, Fairport NEW YORK, Hauppauge NEW YORK, Poughkeepsie/Fishkill NORTH CAROLINA, Raleigh OHIO, Cleveland OHIO, Columbus Worthington OHIO, Dayton OKLAHOMA, Tulsa OREGON, Portland PENNSYLVANIA, Colmar Philadelphia/Horsham TENNESSEE, Knoxville TEXAS, Austin TEXAS, Houston TEXAS, Plano VIRGINIA, Richmond WASHINGTON, Bellevue Seattle Access WISCONSIN, Milwaukee/Brookfield | (508) 481-8100<br>(617) 932-9700<br>(313) 347-6800<br>(612) 932-1500<br>(314) 275-7380<br>(201) 808-2400<br>(716) 425-4000<br>(516) 361-7000<br>(914) 473-8102<br>(919) 870-4355<br>(216) 349-3100<br>(614) 431-8492<br>(513) 495-6800<br>(800) 544-9496<br>(503) 641-3681<br>(215) 997-1020<br>(215) 957-4100<br>(615) 690-5593<br>(512) 873-2000<br>(800) 343-2692<br>(214) 516-5100<br>(804) 285-2100<br>(206) 622-9960<br>(414) 792-0122 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

Field Applications Engineering Available Through All Sales Office

| CANADA<br>BRITISH COLUMBIA, Vancouver | (604) 293-7605  | MALAYSIA, Penang<br>MEXICO, Mexico City | 60(4)374514<br>52(5)282-2864 |

|---------------------------------------|-----------------|-----------------------------------------|------------------------------|

| ONTARIO, Toronto                      | (416) 497-8181  | MEXICO, Guadalajara                     | 52(36)21-8977                |

| ONTARIO, Ottawa                       | (613) 226-3491  | Marketing                               | 52(36)21-9023                |

| QUEBEC, Montreal                      | (514) 731-6881  | Customer Service                        | 52(36)669-9160               |

|                                       |                 | NETHERLANDS, Best                       | (31)49988 612 11             |

| INTERNATIONAL                         |                 | PUERTO RICO, San Juan                   | (809)793-2170                |

| AUSTRALIA, Melbourne                  | (61-3)887-0711  | SINGAPORE                               | (65)2945438                  |

| AUSTRALIA, Sydney                     | (61(2)906-3855  | SPAIN, Madrid                           | 34(1)457-8204                |

| BRAZIL, Sao Paulo                     | 55(11)815-4200  | or                                      | 34(1)457-8254                |

| CHINA, Beijing                        | 86 505-2180     | SWEDEN, Solna                           | 46(8)734-8800                |

| FINLAND, Helsinki                     | 358-0-35161191  | SWITZERLAND, Geneva                     | 41(22)7991111                |

| Car Phone                             | 358(49)211501   | SWITZERLAND, Zurich                     | 41(1)730 4074                |

| FRANCE, Paris/Vanves                  | 33(1)40 955 900 | TAIWAN, Taipei                          | 886(2)717-7089               |

| GERMANY, Langenhagen/ Hanover         | 49(511)789911   | THAILAND, Bangkok                       | (66-2)254-4910               |

| GERMANY, Munich                       | 49 89 92103-0   | UNITED KINGDOM, Aylesbury               | 44(296)395-252               |

| GERMANY, Nuremberg                    | 49 911 64-3044  |                                         |                              |

| GERMANY, Sindelfingen                 | 49 7031 69 910  | FULL LINE REPRESI                       | ENTATIVES                    |

| GERMANY, Wiesbaden                    | 49 611 761921   | COLORADO, Grand Junction                |                              |

| HONG KONG, Kwai Fong                  | 852-4808333     | Cheryl Lee Whitely                      | (303) 243-9658               |

| Tai Po                                | 852-6668333     | KANSAS, Wichita                         |                              |

| INDIA, Bangalore                      | (91-812)627094  | Melinda Shores/Kelly Greiving           | (316) 838 0190               |

| ISRAEL, Tel Aviv                      | 972(3)753-8222  | NEVADA, Reno                            |                              |

| ITALY, Milan                          | 39(2)82201      | Galena Technology Group                 | (702) 746 0642               |

| <b>JAPAN</b> , Aizu                   | 81(241)272231   | NEW MEXICO, Albuquerque                 |                              |

| JAPAN, Atsugi                         | 81(0462)23-0761 | S&S Technologies, Inc.                  | (505) 298-7177               |

| JAPAN, Kumagaya                       | 81(0485)26-2600 | UTAH, Salt Lake City                    |                              |

| JAPAN, Kyushu                         | 81(092)771-4212 | Utah Component Sales, Inc.              | (801) 561-5099               |

| JAPAN, Mito                           | 81(0292)26-2340 | WASHINGTON, Spokane                     |                              |

| JAPAN, Nagoya                         | 81(052)232-1621 | Doug Kenley                             | (509) 924-2322               |

| JAPAN, Osaka                          | 81(06)305-1801  | ARGENTINA, Buenos Aires                 |                              |

| JAPAN, Sendai                         | 81(22)268-4333  | Argonics, S.A.                          | (541) 343-1787               |

| JAPAN, Tachikawa                      | 81(0425)23-6700 |                                         |                              |

| JAPAN, Tokyo                          | 81(03)3440-3311 | HYBRID COMPONENTS                       |                              |

| JAPAN, Yokohama                       | 81(045)472-2751 | Elmo Semiconductor                      | (818) 768-7400               |

| KOREA, Pusan                          | 82(51)4635-035  | Minco Technology Labs Inc.              | (512) 834-2022               |

| KOREA, Seoul                          | 82(2)554-5188   | Semi Dice Inc.                          | (310) 594-4631               |

|                                       | * *             |                                         |                              |

# DOCUMENTATION FEEDBACK

FAX 512-891-8593—Documentation Comments Only (no technical questions please) http://www.mot.com/hpesd/docs\_survey.html—Documentation Feedback Only

The Motorola Technical Communications Department welcomes your suggestions for improving our documentation and encourages you to complete the documentation feedback form at the World Wide Web address listed above. In return for your efforts, you will receive a small token of our appreciation. Your help helps us measure how well we are serving your information requirements.

We also provide a fax number for you to submit any questions or comments about this document or how to order other documents. Please provide the part number and revision number (located in upper right-hand corner of the cover) and the title of the document. When referring to items in the manual, please reference by the page number, paragraph number, figure number, table number, and line number if needed. Please do not fax technical questions to this number.

When sending a fax, please provide your name, company, fax number, and phone number including area code.

#### For Internet Access:

Telnet: pirs.aus.sps.mot.com (Login: pirs)

WWW: http://pirs.aus.sps.mot.com/aesop/hmpg.html Query By Email: aesop\_query@pirs.aus.sps.mot.com

(Type "HELP" in text body.)

# For Dial-Up:

Phone: +1-512-891-3650

Phone (US or Canada): 1-800-843-3451

Connection Settings: N/8/1/F Data Rate: < 14,400 bps Terminal Emulation: VT100

Login: pirs

#### For AESOP Questions:

FAX: +1-512-891-8775

EMAIL: aesop\_sysop@pirs.aus.sps.mot.com

#### For Hotline Questions:

FAX (US or Canada): 1-800-248-8567

EMAIL: aesop\_support@pirs.aus.sps.mot.com

# **TABLE OF CONTENTS**

| Paragraph<br>Number | Title                                                         | Page<br>Numbe |  |  |

|---------------------|---------------------------------------------------------------|---------------|--|--|

|                     | Section 1                                                     |               |  |  |

|                     | Introduction                                                  |               |  |  |

| 1.1                 | Feature List                                                  | 1-1           |  |  |

| 1.2                 | Block Diagram                                                 | 1-2           |  |  |

| 1.3                 | Memory Map                                                    | 1-2           |  |  |

| 1.3.1               | Module Controller Base Address Register (MOBAR) Address (\$EE | E) 1-3        |  |  |

| 1.4                 | Register Overview                                             | •             |  |  |

|                     | Section 2                                                     |               |  |  |

|                     | MC68EN302 Module Bus Controller                               |               |  |  |

| 2.1                 | Introduction                                                  |               |  |  |

| 2.2                 | Top Level Memory Map                                          |               |  |  |

| 2.3                 | MBC Registers                                                 |               |  |  |

| 2.4                 | Module Bus Control (MBCTL)                                    |               |  |  |

| 2.5                 | Interrupt Extension Register (IER)                            |               |  |  |

| 2.6                 | Chip Select Extension Registers (CSER3–CSER0)                 |               |  |  |

| 2.7                 | Parity Control and Status Register (PCSR)                     | 2-6           |  |  |

| 2.8                 | Bus Interface                                                 | 2-7           |  |  |

| 2.8.1               | Bus Arbitration                                               | 2-7           |  |  |

| 2.9                 | Dynamic Bus Sizing                                            | 2-7           |  |  |

| 2.9.1               | Bus Cycle Timing                                              |               |  |  |

| 2.9.2               | Bus Error Handling                                            | 2-10          |  |  |

| 2.9.3               | Retry Handling                                                | 2-11          |  |  |

| 2.10                | Parity Logic                                                  | 2-11          |  |  |

| 2.10.1              | Parity Generation                                             | 2-11          |  |  |

| 2.10.2              | Parity Checking                                               | 2-11          |  |  |

| 2.10.3              | Parity Error Reporting                                        | 2-11          |  |  |

| 2.10.4              | Parity Pin Enable                                             | 2-12          |  |  |

| 2.11                | Interrupt Support                                             | 2-12          |  |  |

|                     | Section 3                                                     |               |  |  |

|                     | MC68EN302 DRAM Control Module                                 |               |  |  |

| 3.1                 | Introduction                                                  |               |  |  |

| 3.2                 | Memory Map                                                    | 3-1           |  |  |

| 3.3                 | DRAM Configuration Register (DCR)                             | 3-1           |  |  |

| 3.4                 | DRAM Refresh Register (DRFRSH)                                | 3-2           |  |  |

| 3.5                 | DRAM Base Address Register (DBA1-DBA0)                        |               |  |  |

| 3.6                 | DRAM Control Module Operation                                 |               |  |  |

| 3.6.1               | Reset Operation                                               | 3-3           |  |  |

| Paragraph    | Title                                             | Page       |

|--------------|---------------------------------------------------|------------|

| Number       |                                                   | Number     |

| 3.6.2        | Read and Write Cycle Operation                    | 3-4        |

| 3.7          | Refresh Operation                                 |            |

| 3.8          | DRAM Controller I/O                               |            |

| 3.8.1        | Control Signal Pins                               |            |

| 3.8.2        | Column Address Strobes (CAS1–CAS0)                |            |

| 3.8.3        | Row Address Strobes (RAS1–RAS0)                   |            |

| 3.8.4        | DRAM Read/Write (DRAMRW)                          |            |

| 3.8.5        | Address Mux (AMUX)                                |            |

| 3.8.6        | Parity (PARITY1-PARITY0)                          |            |

| 3.8.7        | Muxing Scheme                                     |            |

| 0.0.1        | Waxing Concine                                    | 0 7        |

|              | Section 4                                         |            |

| 4.1          | ETHERNET Controller                               | 4.0        |

| 4.1<br>4.1.1 | Register Description                              |            |

|              | Ethernet Control Register (ECNTRL)                |            |

| 4.1.2        | Ethernet DMA Configuration Status Register (EDMA) |            |

| 4.1.3        | Ethernet Maximum Receive Buffer Length (EMRBLR)   |            |

| 4.1.4        | Interrupt Vector Register (IVEC)                  |            |

| 4.1.5        | Interrupt Event Register (INTR_EVENT)             |            |

| 4.1.6        | Interrupt Mask Register (INTR_MASK)               |            |

| 4.1.7        | Ethernet Configuration (ECNFIG)                   |            |

| 4.1.8        | Ethernet Test (ETHER_TEST)                        |            |

| 4.1.9        | AR Control Register (AR_CNTRL)                    |            |

| 4.2          | Ethernet Buffer Descriptors                       |            |

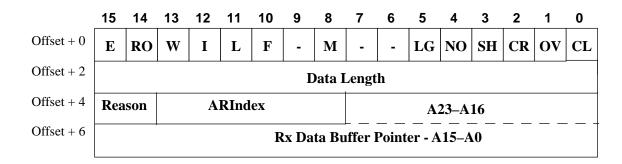

| 4.2.1        | Ethernet Receive Buffer Descriptor (Rx BD)        |            |

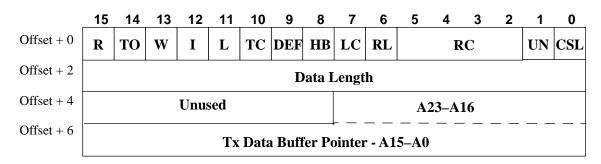

| 4.2.2        | Ethernet Transmit Buffer Descriptor               |            |

| 4.3          | DMA and Buffer Descriptor Logic                   |            |

| 4.3.1        | Buffer Descriptor Logic                           |            |

| 4.3.2        | DMA Logic                                         |            |

| 4.4          | Transmit and Receive FIFOs                        |            |

| 4.4.1        | Transmit FIFO                                     |            |

| 4.4.2        | Receive FIFO                                      |            |

| 4.5          | Ethernet Protocol Logic                           |            |

| 4.5.1        | Ethernet Transmit                                 |            |

| 4.5.2        | Ethernet Receive                                  |            |

| 4.5.3        | Ethernet Loopback                                 |            |

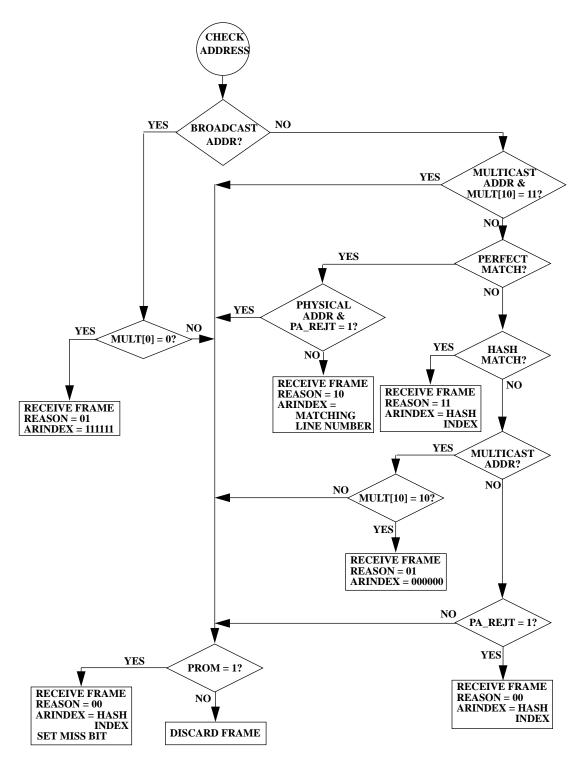

| 4.6          | Ethernet AR (Address Recognition)                 |            |

| 4.6.1        | Buffer Descriptor Modification                    |            |

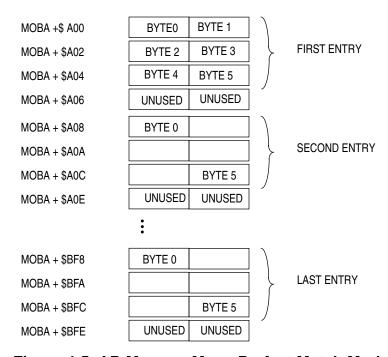

| 4.6.2        | Writing Addresses into Tables                     |            |

| 4.6.3        | Reading Addresses from Tables                     | 4-27       |

|              | Section 5                                         |            |

| <b>5</b> 4   | Signal Descriptions                               | <b>-</b> . |

| 5.1          | Pin/Signal Combinations                           |            |

| 5.2          | MC68EN302/MC68302 Common Signals                  |            |

| 5.3          | MC68302 Signals Removed or Redefined              | 5-5        |

| Paragraph<br>Number | Title                                                     |      |  |  |  |  |

|---------------------|-----------------------------------------------------------|------|--|--|--|--|

| 5.3.1               | RMC/IOUT1                                                 | 5-5  |  |  |  |  |

| 5.3.2               | IAC                                                       | 5-6  |  |  |  |  |

| 5.3.3               | BCLR                                                      | 5-6  |  |  |  |  |

| 5.3.4               | FRZ                                                       | 5-6  |  |  |  |  |

| 5.3.5               | BUSW                                                      | 5-6  |  |  |  |  |

| 5.3.6               | DISCPU                                                    |      |  |  |  |  |

| 5.4                 | MC68EN302 New Signals Muxed with Existing MC68302 Signals | 5-6  |  |  |  |  |

| 5.4.1               | AMUX - DRAM Address Mux                                   | 5-7  |  |  |  |  |

| 5.4.2               | RAS0 - DRAM Row Address Select, Bit Zero                  | 5-7  |  |  |  |  |

| 5.4.3               | RAS1 - DRAM Row Address Select Bit 1                      | 5-7  |  |  |  |  |

| 5.4.4               | CAS0 - DRAM Column Address Select Bit 0                   | 5-7  |  |  |  |  |

| 5.4.5               | CAS1- DRAM Column Address Select Bit 1                    | 5-7  |  |  |  |  |

| 5.4.6               | DRAMRW- DRAM Read/Write                                   | 5-7  |  |  |  |  |

| 5.4.7               | A0                                                        | 5-8  |  |  |  |  |

| 5.4.8               | WEL- Write Enable for Byte 1 (Bit 7-Bit 0)                | 5-8  |  |  |  |  |

| 5.4.9               | WEH - Write Enable for Byte 0 (Bit 15-Bit 8)              | 5-8  |  |  |  |  |

| 5.4.10              | OE - Output Enable                                        |      |  |  |  |  |

| 5.5                 | MC68EN302 Only Pin/Signals                                | 5-8  |  |  |  |  |

| 5.5.1               | GND                                                       | 5-8  |  |  |  |  |

| 5.5.2               | TRST - JTAG Reset Signal                                  | 5-8  |  |  |  |  |

| 5.5.3               | TMS - JTAG Test Mode Select                               | 5-9  |  |  |  |  |

| 5.5.4               | TDO - JTAG Test Data Out                                  | 5-9  |  |  |  |  |

| 5.5.5               | TDI - JTAG Test Data In                                   | 5-9  |  |  |  |  |

| 5.5.6               | TCK- JTAG Clock                                           | 5-9  |  |  |  |  |

| 5.5.7               | GND                                                       | 5-9  |  |  |  |  |

| 5.5.8               | TENA                                                      | 5-9  |  |  |  |  |

| 5.5.9               | TCLK                                                      | 5-9  |  |  |  |  |

| 5.5.10              | RCLK                                                      | 5-9  |  |  |  |  |

| 5.5.11              | RX                                                        | 5-9  |  |  |  |  |

| 5.5.12              | RENA                                                      | 5-9  |  |  |  |  |

| 5.5.13              | CLSN                                                      |      |  |  |  |  |

| 5.5.14              | PARITY0/DISCPU                                            | 5-9  |  |  |  |  |

| 5.5.15              | PARITY1/BUSW                                              |      |  |  |  |  |

| 5.5.16              | PARITYE/THREESTATE                                        | 5-10 |  |  |  |  |

| 5.6                 | DRAM Controller I/O                                       | 5-10 |  |  |  |  |

| 5.6.1               | Control Signal Pins                                       |      |  |  |  |  |

| 5.6.2               | Column Address Strobes (CAS1-CAS0)                        |      |  |  |  |  |

| 5.6.3               | Row Address Strobes (RAS1-RAS0)                           |      |  |  |  |  |

| 5.6.4               | DRAM Read/Write (DRAMRW)                                  | 5-10 |  |  |  |  |

| 5.6.5               | Address Mux (AMUX)                                        | 5-11 |  |  |  |  |

| 5.6.6               | Parity (PARITY1-PARITY0)                                  |      |  |  |  |  |

| 5.6.7               | Muxing Scheme                                             | 5-11 |  |  |  |  |

| Paragraph | Title                                                       | Page         |

|-----------|-------------------------------------------------------------|--------------|

| Number    |                                                             | Number       |

|           | Section 6                                                   |              |

|           | Applications                                                |              |

| 6.1       | Bringing the MC68EN302 Out of Reset                         | 6-1          |

| 6.2       | Moving a QUICC Ethernet Driver to a 68EN302 Ethernet Driver |              |

| 6.2.1     | C_PRES, C_MASK:                                             |              |

| 6.2.2     | CRCEC:                                                      | 6-4          |

| 6.2.3     | ALEC:                                                       | 6-4          |

| 6.2.4     | DISFC:                                                      | 6-4          |

| 6.2.5     | PADS:                                                       | 6-4          |

| 6.2.6     | RET_LIM:                                                    | 6-4          |

| 6.2.7     | RET_Cnt:                                                    | 6-5          |

| 6.2.8     | MFLR:                                                       |              |

| 6.2.9     | MINFLR:                                                     |              |

| 6.2.10    | MAXD1, MAXD2:                                               |              |

| 6.2.11    | MAX_b:                                                      |              |

| 6.2.12    | GADDR1-4 / PADDR_HML / IADDR1-4:                            |              |

| 6.2.13    | P_PER:                                                      |              |

| 6.2.14    | RFBD_ptr/TFBD_ptr/TLBD_ptr:                                 |              |

| 6.2.15    | TX_len:                                                     |              |

| 6.2.16    | BOFF_CNT:                                                   |              |

| 6.2.17    | TADDR_H/M/L:                                                |              |

| 6.2.18    | GSMR (QUICC Section 7.10.2)                                 | 6-6          |

|           | Section 7                                                   |              |

|           | IEEE 1149.1 (JTAG) Test Access Port                         |              |

| 7.1       | Overview                                                    | 7-1          |

| 7.1       | TAP Controller                                              |              |

| 7.3       | Boundary Scan Register                                      |              |

| 7.4       | Instruction Register                                        |              |

| 7.4.1     | EXTEST                                                      |              |

| 7.4.2     | SAMPLE/PRELOAD                                              |              |

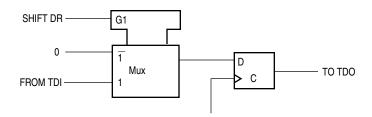

| 7.4.3     | BYPASS                                                      |              |

| 7.4.4     | CLAMP                                                       | _            |

| 7.4.5     | HI-Z                                                        |              |

| 7.5       | MC68EN302 Restrictions                                      |              |

| 7.6       | Non-Scan Chain Operation                                    |              |

|           |                                                             |              |

|           | Section 8                                                   |              |

| 0.4       | MC68EN302 Electrical Characteristics                        | 0.4          |

| 8.1       | Power Dissipation                                           |              |

| 8.2       | Changes to Existing MC68302 Timing Specs                    |              |

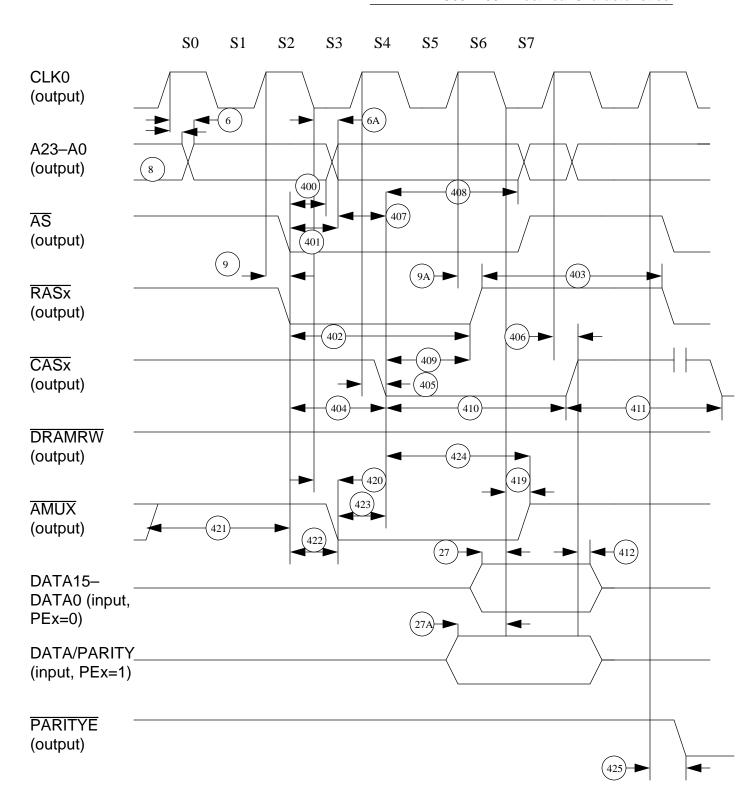

| 8.3       | DRAM Interface Timing                                       |              |

| 8.4       | Ethernet Timing                                             |              |

| 8.5       | JTAG Interface Timing                                       |              |

| 8.6       | OE, WEL, WEH Timing                                         |              |

| 8.6.1     | OE Timing                                                   | 8 <b>-</b> 9 |

| Paragraph<br>Number | Title                               | Page<br>Number |

|---------------------|-------------------------------------|----------------|

| 8.6.2               | WEL, WEH Timing                     | 8-9            |

|                     | Section 9                           |                |

|                     | Ordering and Mechanical Information |                |

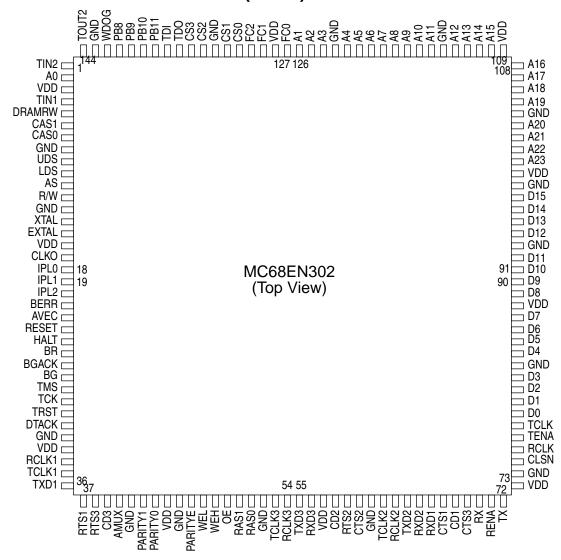

| 9.1                 | Pin Assignment                      | 9-1            |

| 9.1.1               | Pin Grid Array (PGA)                | 9-2            |

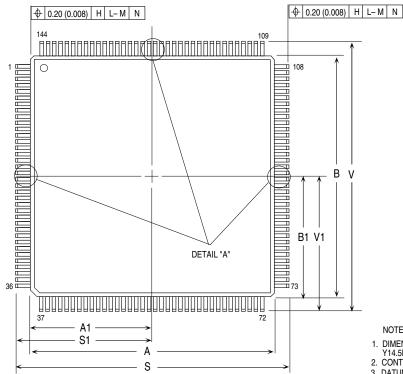

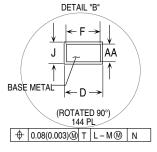

| 9.1.2               | 144 Thin Quad Flat Pack (TQFP)      | 9-3            |

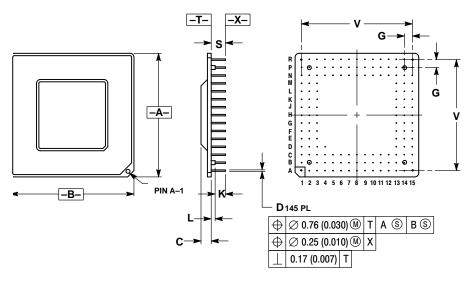

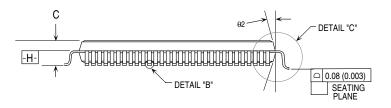

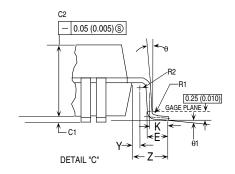

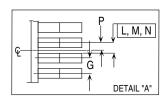

| 9.2                 | Package Dimensions                  | 9-4            |

| 9.2.1               | Pin Grid Array (PGA)                |                |

| 9.2.2               | 144 Thin Quad Flat Pack (TQFP)      | 9-5            |

| 9.3                 | Standard Ordering Information       | 9-6            |

# **LIST OF FIGURES**

| Figure<br>Number | Title                                          | Page<br>Number |

|------------------|------------------------------------------------|----------------|

| Figure 1-1.      | MC68EN302 Block Diagram                        | 1-2            |

| Figure 2-1.      | Top Level Bus Structure                        | 2-1            |

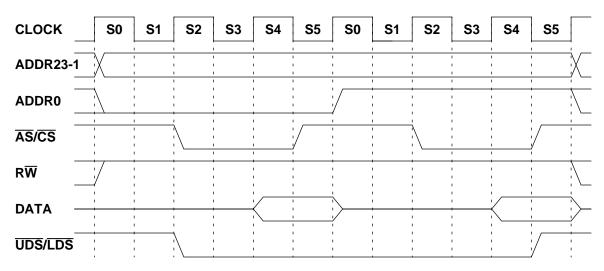

| Figure 2-2.      | 8-bit External to 16-bit Internal Read         | 2-8            |

| Figure 2-3.      | 16-bit Internal to 8-bit External Write        |                |

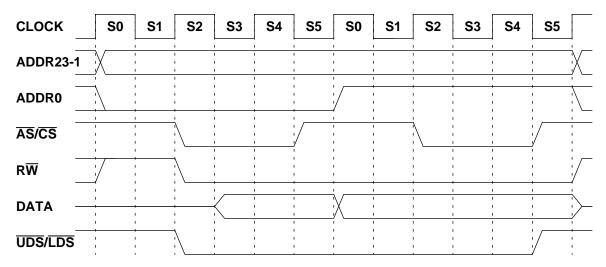

| Figure 2-4.      | Word Read with 3-Clock 8-Bit Accesses          | 2-9            |

| Figure 2-5.      | Word Write with 3-Clock 8-Bit Accesses         | 2-9            |

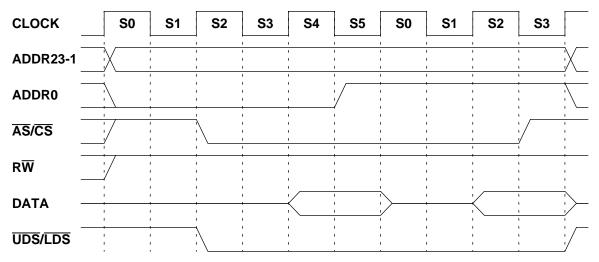

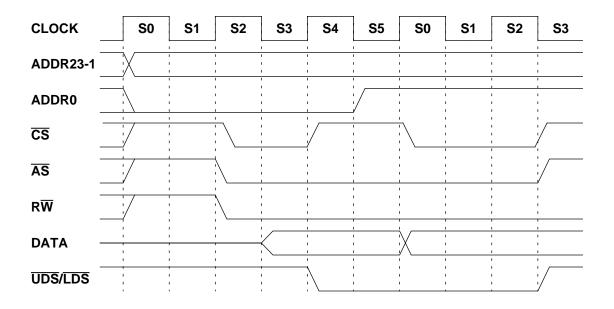

| Figure 2-6.      | Fast Cycle Word Read with -1 Wait State        | 2-10           |

| Figure 2-7.      | Fast Cycle Word Write with -1 Wait State       |                |

| Figure 2-8.      | External and Internal Interrupt Prioritization |                |

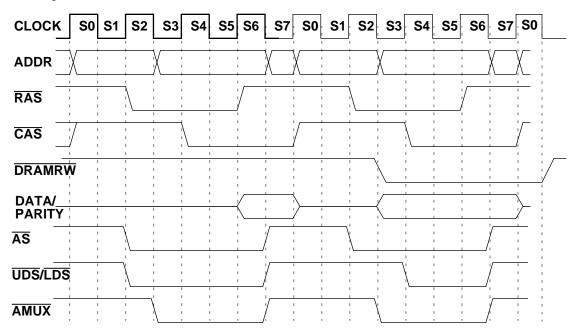

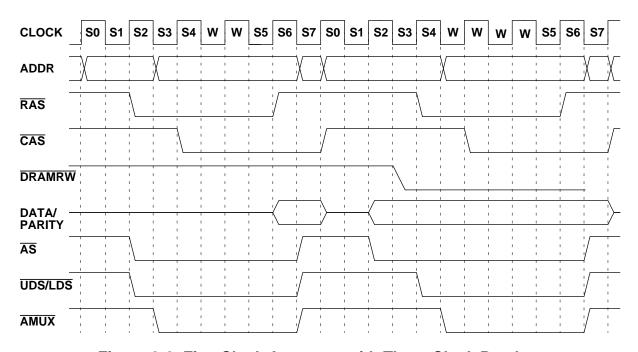

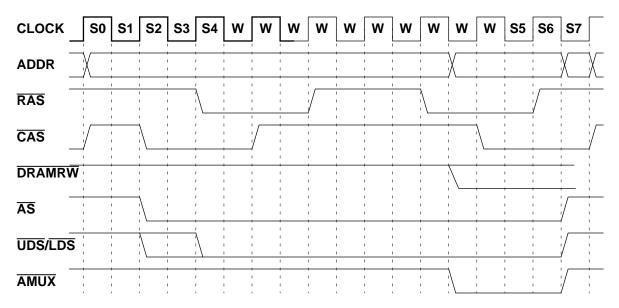

| Figure 3-1.      | Consecutive Four-Clock Accesses                |                |

| Figure 3-2.      | Five-Clock Accesses with Three-Clock Precharge | 3-5            |

| Figure 3-3.      | Precharge With DRAM Access Active              |                |

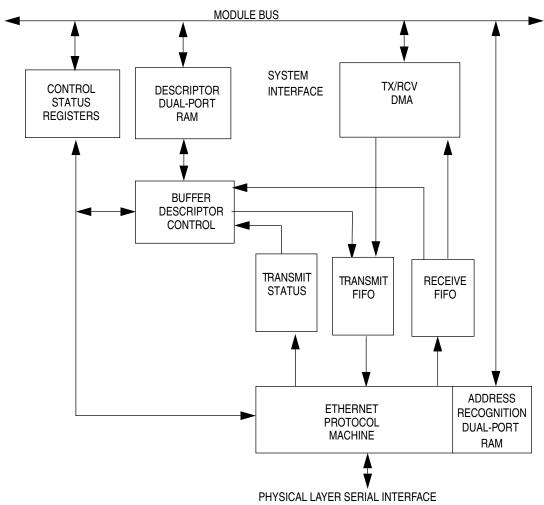

| Figure 4-1.      | Ethernet Controller Block Diagram              |                |

| Figure 4-2.      | Ethernet Receive Buffer D.0escriptor (Rx BD)   |                |

| Figure 4-3.      | Ethernet Transmit Buffer Descriptor (Tx BD)    |                |

| Figure 4-4.      | Ethernet Address Recognition Flowchart         |                |

| Figure 4-5.      | AR Memory Map - Perfect Match Mode             |                |

| Figure 4-6.      | AR Memory Map - Hash Mode                      |                |

| Figure 7-1.      | Test Logic Block Diagram                       |                |

| Figure 7-2.      | TAP Controller State Machine                   |                |

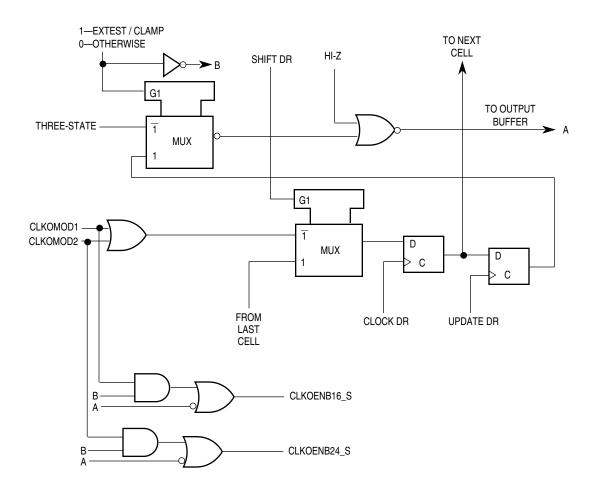

| Figure 7-3.      | Output Latch Cell (iocell)                     |                |

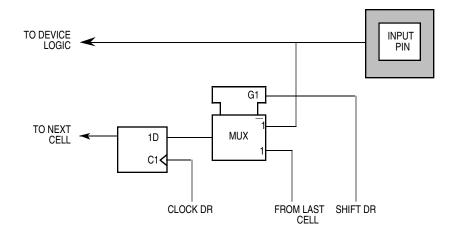

| Figure 7-4.      | Input Pin Cell (iscell)                        |                |

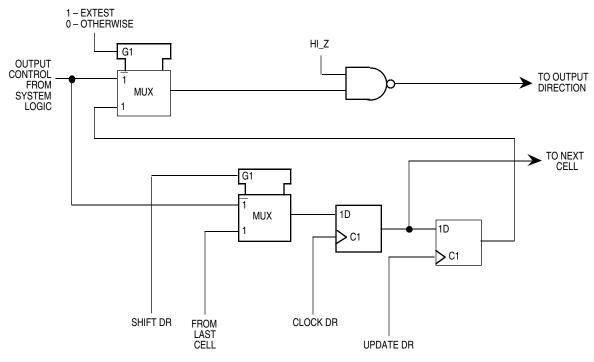

| Figure 7-5.      | Control Cell (dicell)                          |                |

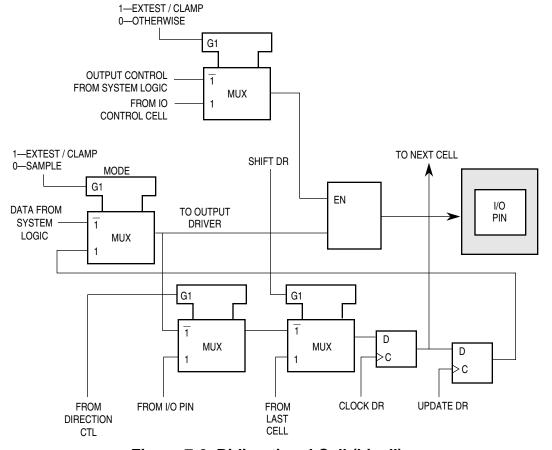

| Figure 7-6.      | Bidirectional Cell (bicell)                    |                |

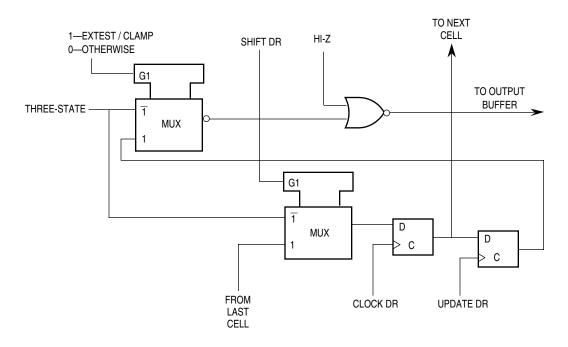

| Figure 7-7.      | Output Enable Cell (encell)                    |                |

| Figure 7-8.      | Output Enable Cell (encello)                   |                |

| Figure 7-9.      | Output Enable Cell (clko_encell)               | 7-11           |

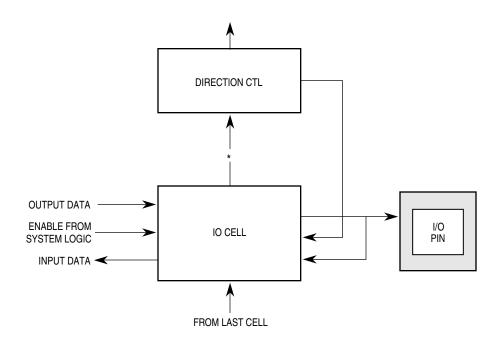

| Figure 7-10.     | General Arrangement for Bidirectional Pins     |                |

| Figure 7-11.     |                                                |                |

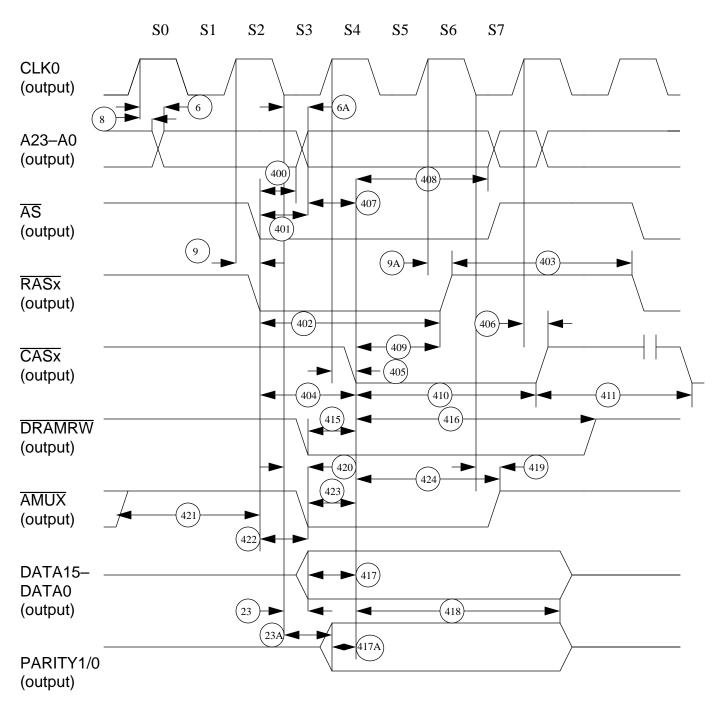

| Figure 8-1.      | DRAM Read Cycle                                |                |

| Figure 8-2.      | DRAM Write Cycle                               | 8-4            |

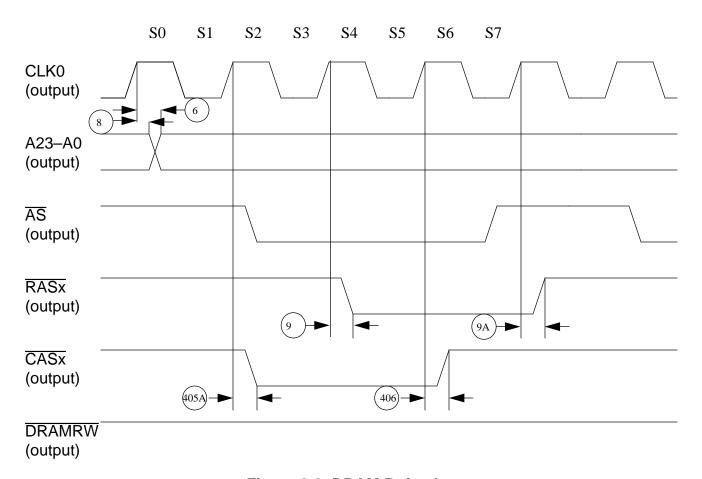

| Figure 8-3.      | DRAM Refresh                                   | 8-5            |

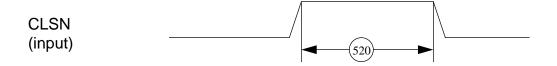

| Figure 8-4.      | Ethernet Collision Timing                      | 8-6            |

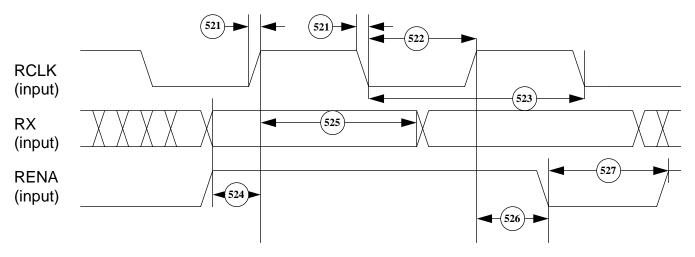

| Figure 8-5.      | Ethernet Receive Timing                        | 8-6            |

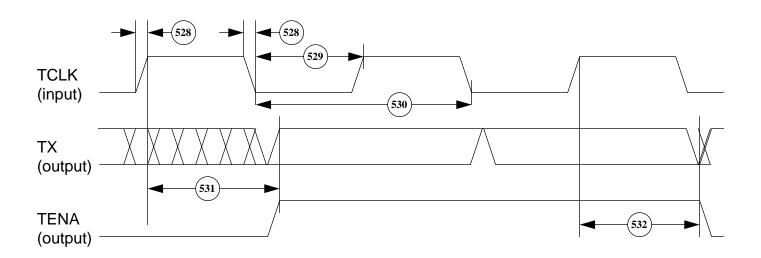

| Figure 8-6.      | Ethernet Transmit Timing                       |                |

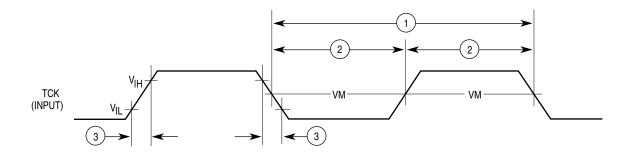

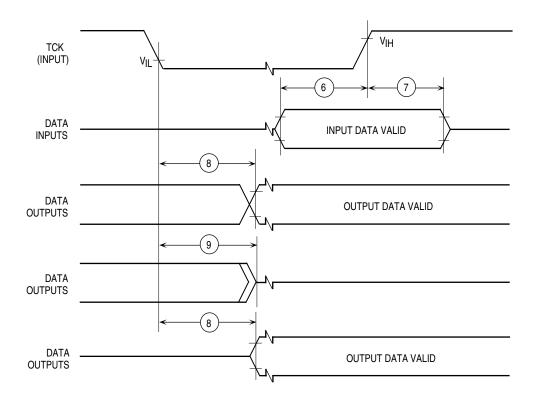

| Figure 8-7.      | Test Clock Input Timing Diagram                |                |

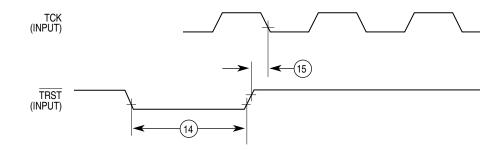

| Figure 8-8.      | TRST Timing Diagram                            |                |

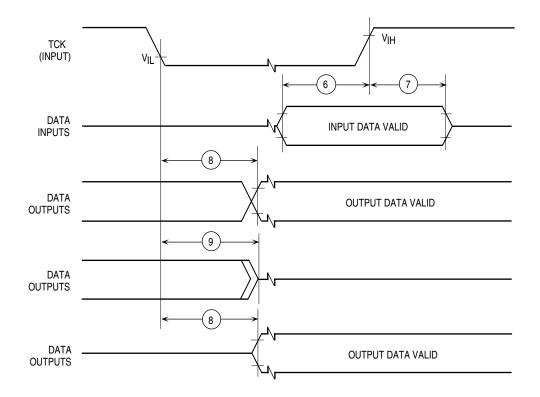

| Figure 8-9.      | Boundary Scan (JTAG) Timing Diagram            |                |

| Figure 8-10.     |                                                |                |

# **LIST OF TABLES**

| Table<br>Number | Title                                       | Page<br>Number |

|-----------------|---------------------------------------------|----------------|

| Table 1-1.      | MC68EN302 Additional Registers              | 1-4            |

| Table 2-1.      | High Level Memory Map of MBC and MB Modules | 2-2            |

| Table 2-2.      | Module Bus Controller Register Set          | 2-2            |

| Table 2-3.      | Pin Muxing Operation                        | 2-3            |

| Table 2-4.      | DT Bit Encoding                             | 2-5            |

| Table 2-5.      | Parity Pin Enable Operation                 |                |

| Table 3-1.      | DRAM Controller Registers                   |                |

| Table 3-2.      | Precharge Bit Encodings                     | 3-2            |

| Table 3-3.      | Wait State Bit Encodings                    | 3-2            |

| Table 3-4.      | Address Muxing Scheme                       | 3-7            |

| Table 4-1.      | Ethernet Controller Memory Map              | 4-2            |

| Table 4-2.      | BD RAM Address Ranges                       | 4-18           |

| Table 4-3.      | Unicast Address Processing                  | 4-24           |

| Table 4-4.      | Broadcast and Multicast Address Processing  | 4-24           |

| Table 5-1.      | MC68EN302 144-TQFP Pin/Signal Definition    | 5-1            |

| Table 5-2.      | Pin Muxing Control                          |                |

| Table 5-3.      | Address Muxing Scheme                       | 5-11           |

| Table 7-1.      | Boundary Scan Control Bits                  | 7-4            |

| Table 7-2.      | Boundary Scan Bit Definition                | 7-6            |

| Table 7-3.      | Instruction Decoding                        | 7-12           |

| Table 8-1.      | DRAM Interface Timing                       | 8-2            |

| Table 8-2.      | Ethernet Timing                             | 8-5            |

| Table of Contents |       |        |

|-------------------|-------|--------|

| Paragraph         | Title | Page   |

| Number            |       | Number |

# SECTION 1 INTRODUCTION

The MC68EN302 is a multiprotocol integrated communications controller based on the MC68302. The original MC68302 provided multiple WAN and ISDN support with three serial communcations channels, glueless memory control for SRAM and EPROM and various system integration features. The MC68EN302 builds upon the success of the MC68302 by adding an Ethernet controller which is completely independent of the three on-board serial channels as well as a DRAM control and a JTAG interface. No communications related features of the original 302 are lost when using either the Ethernet controller or the DRAM controller of the MC68EN302.

The Ethernet controller provides a 16-bit interface and provides complete IEEE 802.3 compatibility. The programming model for the Ethernet controller is based on the standard MC68302 programming model. Buffer descriptors for the Ethernet controller are compatible wiith the buffer descriptors used by the MC68360 QUICC Ethernet controller.

The DRAM controller is based upon other 300 family memory controllers with specific enhancements provided for supporting parity and external bus masters.

The JTAG interface is the standard IEEE1149.1 test interface.

#### 1.1 FEATURE LIST

The following MC68EN302 features are in addition to the MC68302 feature list:

- Full complement of existing three SCC's plus Ethernet channel

- Ethernet channel fully compliant with IEEE 802.3 MAC Specification.

- Supports data rates up to 10 Mbps.

- Supports the MC68302 style programming model.

- Bus bandwidth requirements reduced through 128 on-chip buffer descriptors.

- Independant 128 byte transmit and receive FIFO's.

- 64 entry CAM for Address Recognition.

- Ethernet collision results in retransmission from TX FIFO (no external bus access).

- Runt frames automatically cause RX FIFO to flush internally.

- Interfaces to MC68160 for 10Base-T or AUI Connection.

- Dynamic Bus Sizing

- Glueless ROM and SRAM interface

- DRAM Controller

- Glueless DRAM interface for internal bus master

- AMUX signal provided for external bus master use

- Parity generation/checking on a per byte basis

- Fully IEEE 1149.1 JTAG Compliant

- 144 TQFP package

#### 1.2 BLOCK DIAGRAM

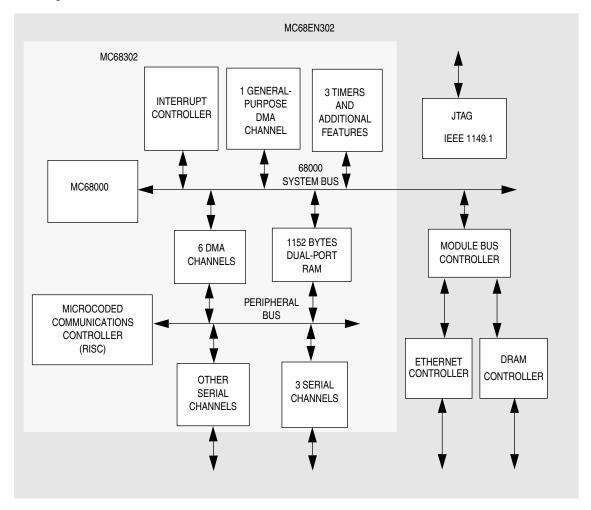

The MC68EN302 adds functionality to the pre-existing MC68302 by providing additional blocks external to the MC68302 which arbitrate for use of the 68000 bus for access to off-chip resources such as memory or other peripheral devices. This modular approach is shown in Figure .

Figure 1-1. MC68EN302 Block Diagram

#### 1.3 MEMORY MAP

The MC68EN302 memory map does not change the MC68302 memory map, but rather adds a new 4K module block. This is in addition to the 4K module block of the MC68302. Because of the additional register block, there are two Base Address Registers to program

in the MC68EN302. The BAR register is identical to the MC68302 BAR, and the Module Controller Base Address Register is specific to the MC68EN302.

# 1.3.1 Module Controller Base Address Register (MOBAR) Address (\$EE)

The Module Controller Base Address Register (MOBAR) sets the base address for the MC68EN302 registers which are in addition to the register set of the MC68302. The MOBAR is located at address \$0EE and its configuration and operation match the existing MC68302 BAR. The value of MOBAR after reset defaults to \$BFFE which places the Module Controller Block directly below the MC68302 Block. The MC68EN302 must be in supervisor mode for MOBAR to be written with a new value.

| 15  | 14  | 13  | 12  | 11   | 10   | 9    | 8    | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|-----|-----|-----|-----|------|------|------|------|------|------|------|------|------|------|------|------|

| FC2 | FC2 | FC0 | CFC | BA23 | BA22 | BA21 | BA20 | BA19 | BA18 | BA17 | BA16 | BA15 | BA14 | BA13 | BA12 |

# FC2-FC0-Function Code 2-Function Code 0

FC2-0 sets the address space of the 4 kbyte Module Controller Block. Depending on the value of the CFC bits, the MC68EN302 address compare logic uses these bits to cause an address match within its address space.DO NOT assign FC2-0 to the M68000 interrupt acknowledge space (FC2-0 = 111b).

## CFC—Compare Function Code

When cleared, the FC bits in the MOBAR are ignored and accesses to the Module Controller Block occur without comparing the FC bits. When set, the address space compare logic uses the FC bits in MOBAR to detect address matches.

MOBA—Module Controller Base Address.

The high address field is contained in bits 11-0 of the MOBAR and sets the starting address of the Module Controller Block.

#### 1.4 REGISTER OVERVIEW

The control and status registers for the Ethernet controller are all 16 bits with an address range of MOBA+\$000 to MOBA+\$FFF. The MC68EN302 registers in addition to the 302 register set are shown in Table 1-1. Note that even though the entire 302 register set is provided, special care must be taken when initializing the pre-existing 302 registers so there are no contention or compatibility issues during internal arbitration. The registers that require particular attention are:

- OR

- GIMR

- SCR.

Also, notice that DTACK is not returned for accesses to unimplemented CSRs in the MOBA address space.

# Table 1-1. MC68EN302 Additional Registers

|                          |                                      | _          | 1          |  |  |  |

|--------------------------|--------------------------------------|------------|------------|--|--|--|

| ADDRESS                  | NAME                                 | MNEMONIC   | TYPE       |  |  |  |

| MOBA + 000               | Module Bus Control                   | MBC        | Read/Write |  |  |  |

| MOBA + 002               | Interrupt Extension Register         | IER        | Read/Write |  |  |  |

| MOBA + 004               | Chip Select 0 Extension Register     | CSER0      | Read/Write |  |  |  |

| MOBA + 006               | Chip Select 1 Extension Register     | CSER1      | Read/Write |  |  |  |

| MOBA + 008               | Chip Select 2 Extension Register     | CSER2      | Read/Write |  |  |  |

| MOBA + 00A               | Chip Select 3 Extension Register     | CSER3      | Read/Write |  |  |  |

| MOBA + 00C               | Parity Control & Status Register     | PCSR       | Read/Write |  |  |  |

| MOBA + 010               | DRAM Configuration Register          | DCR        | Read/Write |  |  |  |

| MOBA + 012               | DRAM Refresh Register                | DRFRSH     | Read/Write |  |  |  |

| MOBA + 014               | DRAM Bank 0 Base Address Register    | DBA0       | Read/Write |  |  |  |

| MOBA + 016               | DRAM Bank 1 Base Address Register    | DBA1       | Read/Write |  |  |  |

| MOBA + 800               | Ethernet Control Register            | ECNTRL     | Read/Write |  |  |  |

| MOBA + 802               | Ethernet DMA Configuration Register  | EDMA       | Read/Write |  |  |  |

| MOBA + 804               | Maximum Receive Buffer Length        | EMRBLR     | Read/Write |  |  |  |

| MOBA + 806               | Interrupt Vector Register            | INTR_VECT  | Read/Write |  |  |  |

| MOBA + 808               | Interrupt Event                      | INTR_EVENT | Read/Write |  |  |  |

| MOBA + 80A               | Interrupt Mask Register              | INTR_MASK  | Read/Write |  |  |  |

| MOBA + 80C               | Ethernet Configuration               | ECNFIG     | Read/Write |  |  |  |

| MOBA + 80E               | Ethernet Test Register               | ETHER_TEST | Read/Write |  |  |  |

| MOBA + 810               | Address Recognition Control Register | AR_CNTRL   | Read/Write |  |  |  |

| MOBA + A00<br>MOBA + BFF | CAM Entry Table                      | CET        | Read/Write |  |  |  |

| MOBA + C00<br>MOBA + FFF | Buffer Descriptors Table             | EBD        | Read/Write |  |  |  |

|                          |                                      | i          |            |  |  |  |

# SECTION 2 MC68EN302 MODULE BUS CONTROLLER

## 2.1 INTRODUCTION

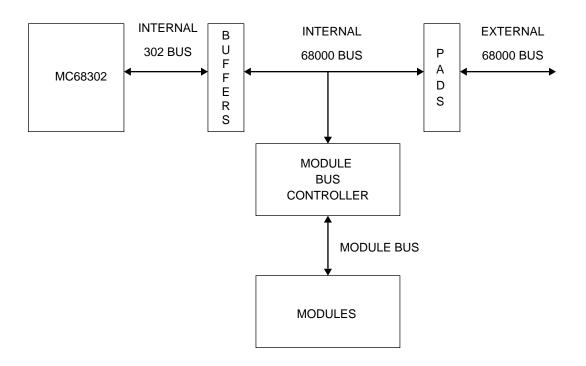

The model of the MC68EN302 is such that the internal 302 functions are unaffected by the addition of an Ethernet controller and the DRAM controller. The 302 core sees that it must arbitrate with other bus masters for access to the 'external' bus. In the MC68EN302, the Module Bus Controller provides the arbitration between the 302 core and the other modules (Ethernet and DRAM) for access to the bus external to the MC68EN302. The functions provided by the Module Bus Controller (MBC) are as follows:

- Interfaces between internal 68000 bus and the Module Bus.

- Performs Dynamic Bus sizing utilizing the chip select logic of the internal 68302.

- Provides Interrupt handling for Module Bus modules.

- Performs bus arbitration between external sources, the Module Bus, and the 68302 core.

Figure 2-1. Top Level Bus Structure

#### 2.2 TOP LEVEL MEMORY MAP

A top level diagram of register allocation for the modules in the MC68EN302 is shown in Table 2-1. A description of the DRAM control registers and the Ethernet Controller Registers are contained in the description of those modules.

Table 2-1. High Level Memory Map of MBC and MB Modules

| Address    | Block                         |  |  |  |  |

|------------|-------------------------------|--|--|--|--|

| MOBA + 000 | MBC Degisters                 |  |  |  |  |

| MOBA + 00D | MBC Registers                 |  |  |  |  |

|            |                               |  |  |  |  |

| MOBA + 010 | DDAM Controller Degisters     |  |  |  |  |

| MOBA + 019 | DRAM Controller Registers     |  |  |  |  |

|            |                               |  |  |  |  |

| MOBA + 800 | Ethornot Controllor Dogistors |  |  |  |  |

| MOBA + FFF | Ethernet Controller Registers |  |  |  |  |

# 2.3 MBC REGISTERS

A memory map of the MBC control registers is shown in Table 2-2.

**Table 2-2. Module Bus Controller Register Set**

| ADDRESS    | REGISTER NAME                    | MNEMONIC |

|------------|----------------------------------|----------|

| MOBA + 000 | Module Bus Control Register      | MBCTL    |

| MOBA + 002 | Interrupt Extension Register     | IER      |

| MOBA + 004 | Chip Select 0 Extension Register | CSER0    |

| MOBA + 006 | Chip Select 1 Extension Register | CSER1    |

| MOBA + 008 | Chip Select 2 Extension Register | CSER2    |

| MOBA + 00A | Chip Select 3 Extension Register | CSER3    |

| MOBA + 00C | Parity Control & Status Register | PCSR     |

# 2.4 MODULE BUS CONTROL (MBCTL)

The Module Bus Control register (MBCTL) provides the user control over the system level functionality of the MBC. This register defaults to \$0x5000 upon hardware reset.

| 15  | 14   | 13   | 12   | 11 | 10  | 9   | 8   | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-----|------|------|------|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| BCE | MFC2 | MFC1 | MFC0 | BB | PPE | PM9 | PM8 | PM7 | PM6 | PM5 | PM4 | PM3 | PM2 | PM1 | PM0 |

BCE—Bus Clear Enable. This bit controls the way in which the MBC responds to the Bus Clear function inside the MC68EN302. If BCE is zero, the MBC ignores the Bus Clear (BCLR) signal giving the DRAM and Ethernet modules priority over the 302 core. If this bit

is set, the MBC relinquishes the bus when it detects BCLR, allowing the internal 302 core priority over the DRAM and Ethernet controllers.

MFC—Module Function Code (MFC2-MC0). These bits determine the function code put out when the Ethernet DMA machine is active.

BB—Bus Error Byte. This status bit (read-only) is the state of Address 0 upon the last generated bus error. This information is useful when performing exception processing to determine the cause of bus errors generated when the 8-bit dynamic bus sizing option is used with the Chip Selects.

PPE—Parity Pin Enable. This bit, if set, enables parity on the appropriate pins. The parity signals are muxed on three MC68EN302 configuration pins which are sampled at hard reset to determine device operation. Once out of reset, the parity function may be enabled by the PPE bit. See 2.10.4 Parity Pin Enable for more details.

PM—Pin Muxes PM9—PM0. Depending upon the setting of these bits, the MC68EN302 is able to provide some enhancements over the 68302. Because many of these enhancements are with existing 68302 pins, the enhancements are provided as programmable options. Table 2-3 shows the effect of the PM bits. All PM bits are cleared at hardware reset.

| Mux Bit | Bit = 0<br>Pin Function | Bit = 1<br>Pin Function |

|---------|-------------------------|-------------------------|

| PM0     | AMUX                    | BRG1                    |

| PM1     | RAS0                    | BRG2/SDS2/PA7           |

| PM2     | RAS1                    | BRG3/PA12               |

| PM3     | CAS0                    | PB0/IACK7               |

| PM4     | CAS1                    | PB1/IACK6               |

| PM5     | DRAM_RW                 | PB2/IACK1               |

| PM6     | A0                      | TOUT1/PB4               |

| PM7     | DREQ/PA13               | WEL                     |

| PM8     | DACK/PA14               | WEH                     |

| PM9     | ŌĒ                      | DONE/PA15               |

**Table 2-3. Pin Muxing Operation**

# 2.5 INTERRUPT EXTENSION REGISTER (IER)

This register replaces the MOD, ET7, ET6, and ET1 bits in the pre-existing 302 GIMR (Global Interrupt Mode Register) requiring that when writing to the internal 302 core GIMR, the corresponding bits must be written as a zero. This register is \$0x0000 upon hardware reset.

| 15   | 14 | 13 | 12 | 11  | 10   | 9    | 8    | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|------|----|----|----|-----|------|------|------|---|---|---|---|---|---|---|---|

| IMOD | 0  | 0  | 0  | MIL | IET7 | IET6 | IET1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

IMOD—Interrupt Mode. This bit determines if the 3 interrupt inputs are configured as IPL pins or IRQ pins for the MC68EN302 and replace the MOD bit functionality in the internal

302 GIMR. For proper operation of the MC68EN302, the MOD bit must be zero in the internal 302 core.

- $0 = \text{Configures the pins as } \overline{\text{IPL2-IPL0}}.$

- 1 = Configures the pins as  $\overline{IRQ7}$ ,  $\overline{IRQ6}$ , and  $\overline{IRQ1}$ .

Bits 14–12—Reserved. Should be written as zero. These bits are always read as zero.

MIL—Module Interrupt Level. This bit determines the interrupt level at which Module Bus Controller interrupts are generated. Because the interrupt level of the internal 302 core is set at 4, and this bit predetermines the Module Bus Controller interrupt at either level 3 or 5, external interrupts should not be generated at level 4 or the level preset by MIL.

- 0 = Interrupts are generated at level 5

- 1 = Interrupts are generated at level 3.

IET7—Interrupt Edge Trigger Level 7. This bit has no effect unless IMOD=1 and replaces the operation of the ET7 bit in the Global Interrupt Mode Register (GIMR) of the internal 302 core. The ET7 bit in the GIMR register must equal zero for correct interrupt operation

- $0 = An interrupt is made pending when <math>\overline{IRQ7}$  is low.

- 1 = An interrupt is made pending when  $\overline{IRQ7}$  changes from a one to a zero (falling edge) of the MC68EN302.

IET6—Interrupt Edge Trigger Level 6. This bit is has no affect unless IMOD is one. This bit replaces the functionality of the ET6 bit in the Global Interrupt Mode Register (GIMR) of the internal 302 core. The ET6 bit in the GIMR register must be set to zero.

- $0 = An interrupt is made pending when <math>\overline{IRQ6}$  is low.

- 1 = An interrupt is made pending when  $\overline{IRQ6}$  changes from a one to a zero (falling edge).

IET1—Interrupt Edge Trigger Level 1. This bit is has no effect unless IMOD is one. This bit replaces the functionality of the ET1 bit in the Global Interrupt Mode Register (GIMR) of the internal 302 core. The ET1 bit in the GIMR register must be set to zero.

- 0 = An interrupt is made pending when IRQ1 is low.

- $1 = An interrupt is made pending when <math>\overline{IRQ1}$  changes from a one to a zero (falling edge).

Bits 7–0—Reserved. Should be written as zero. These bits are always read as zero.

# 2.6 CHIP SELECT EXTENSION REGISTERS (CSER3-CSER0)

These registers provide additional functionality above the 68302 chip selects including 8-bit bus operation and parity generation and checking. Before setting the FCE, DT2–DT0 or EN8 bits, be sure that an external DTACK is supported by programming the 302 DTACK field in the corresponding OR register to 111. These registers are initialized to 0x000C or 0x000D upon hard reset (refer to the EN8 bit for more detail).

If at RESET, the 8-bit mode is selected through use of the PARITY1/BUSW pin, the DTACK field in OR0 of the 302 core is forced to 111. This results in the DT2–DT0 field of CSER0 controlling DTACK.

During reset, CS1, CS2 and CS3 are disabled via the EN bit in the BR1, BR2 and BR3 registers.

Note that when in disable CPU mode, the CS0 function is replaced by IOUT2.

| _ |   | _ |   |   | - | - | _ | 7    | - | _ |     | _   |     |     | -   |  |

|---|---|---|---|---|---|---|---|------|---|---|-----|-----|-----|-----|-----|--|

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | CSPE | 0 | 0 | FCE | DT2 | DT1 | DT0 | EN8 |  |

Bits 15–8—Reserved. Should be written to zero by the host processor. These bits are always read as zero.

CSPE—Chip Select Parity Enable. This bit enables parity checking and generation when the corresponding Chip Select is generated. Unless the corresponding chip select is set to 8-bit operation, parity is generated and checked on both bytes.

Bits 6–5—Reserved. Should be written to zero by the host processor. This bit is always read as zero.

FCE—Fast Cycle Enable. This bit enables fast mode operation. When using fast cycles,  $\overline{CS}$  and  $\overline{AS}$  are not negated between 8 bits of a 16 bit transfer, allowing a 16-bit transfer to occur on an 8-bit bus in 5 clocks rather than 6.

DT2–DT0—DTACK. These bits are used to determine whether DTACK is generated internally with a programmable number of wait states or externally by the peripheral. When done internally, the MC68EN302 provides the option of allowing 16-bit accesses to take place in two-three clock external 8-bit accesses. The 68000 only sees a single six clock access internally during this mode of operation. This functionality is also referred to as 'minus one wait state option.' Note that an 8-bit operand access requires a 4 clock bus cycle. Table 2-4 shows how the bits are encoded.

DT BIT ENCODING **WAIT STATES** 000 -1 001 0 010 1 011 2 100 3 101 4 110 5 No DTACK 111

Table 2-4. DT Bit Encoding

EN8—Enable 8-bit chip select. When set to a one, the 8-bit chip select operation is enabled. If the system is booted from an 8-bit memory, the system must drive the BUSW pin low during system reset which sets the EN8 bit for all four CSER registers. This assures that the device is able to access 8-bit memories as well as 16-bit memories. In 8-bit mode bits D15—D8 of the data bus are used.

# 2.7 PARITY CONTROL AND STATUS REGISTER (PCSR)

This register controls and gives the status of the parity checking portions of the parity circuitry. This register is set to 0x0000 upon hardware reset.

| 15  | 14   | 13   | 12   | 11   | 10   | 9    | 8    | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|-----|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|

| PIE | OPAR | PEC3 | PEC2 | PEC1 | PEC0 | PED1 | PED0 | PIV7 | PIV6 | PIV5 | PIV4 | PIV3 | PIV2 | PIV1 | PIV0 |

PIE—Parity Error Interrupt Enable. This bit determines if an interrupt is generated when a parity error is detected.

- 0 = No interrupt is generated.

- 1 = Either a level 3 or level 5 interrupt is generated, depending upon the encoding of the MIL bit in the IER register.

OPAR—Odd Parity. This bit is used to determine if odd or even parity is used.

- 0 = Parity is even.

- 1 = Parity is odd.

PEC—Parity Error Chip Selects (PEC3–PEC0). These status bits indicate that there was a parity error in the corresponding Chip Select Bank. If one of the three bits is set to one, a parity error is detected in the corresponding bank. If the PIE bit is set, a level 5 (or 3) interrupt is driven to the processor as long as one of the PEC3–PEC0 bits are set. PEC3–PEC0 are sticky bits which are cleared when a one is written to them or upon hardware reset. Writing a zero does not change the value of the PEC bits. The PARITYE pin is asserted until the PEC3–PEC0 bits are all cleared.

#### NOTE

If the Parity Pin Enable bit (PPE in MBC CSR) = 0 and parity is enabled with CSPE in CSER3–CSER0, then a parity error will be reported on the associated PEC bit.

PED—Parity Error DRAM (PED1–PED0). These status bits indicate that there was a parity error in the corresponding DRAM bank. If one of the two bits is set to one, a parity error is detected in the corresponding bank. If the PIE bit is set, a level 5 (or 3) interrupt is driven to the processor as long as one of the PED bits is set. PED are sticky bits which are cleared when a one is written to them or upon hardware reset. Writing a zero does not change the value of the PED bits. Writing a zero does not change the value of the PED bits. The PARITYE pin is asserted as long as a PED bit is set.

#### NOTE

If the Parity Pin Enable bit (PPE in MBC CSR) = 0 and parity is enabled on the DRAM interface (PE1 and/or PE0 = 1 in DCR) then a parity error will be reported on PED1–PED0.

PIV—Parity Error Interrupt Vector (PIV7–PIV0). If the PIE bit is set, a parity error generates a level 5 (or 3) interrupt. The PIV bits determine what interrupt vector is returned in response to a level 5 (or 3) parity error interrupt.

#### 2.8 BUS INTERFACE

The MBC is responsible for determining the source of the bus mastership (module bus, external 68K bus or internal 302 core) and for controlling the direction of the buses. The layer of buffering between the internal 302 and internal 68000 buses mimics the operation of the 68302 external bus, giving the module bus the appearance of an external master from the viewpoint of the internal 302 core. The MBC does not affect the operation of the bus outside the MC68EN302 unless it arbitrates for that bus and is given bus mastership. The operation of the MBC as bus master is such that the bus external to the MC68EN302 operates as if an existing 302 peripheral is bus master. This is accomplished by:

- Providing I/O control at the pad which overrides the existing 68302 I/O control.

- Intercepting the external arbitration signals and merging them with the MBC arbitration.

#### 2.8.1 Bus Arbitration

The MBC provides the circuitry which prioritizes the bus mastership requests in the following order (highest priority to lowest):

- External bus requests

- Module bus requests (Ethernet module)

- internal 302 core

#### 2.9 DYNAMIC BUS SIZING

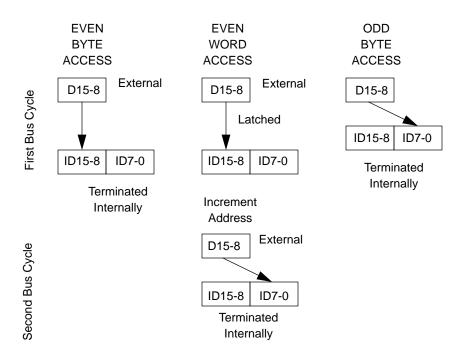

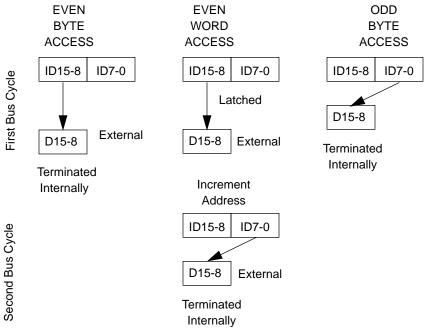

The MBC accommodates dynamic bus sizing by providing control to operate on the internal 68000 bus as a 16-bit device while simultaneously providing an 8-bit option externally. Control is provided via the EN8 bit in the CSER3–CSER0 registers and via the BUSW pin. The MBC routes data into the proper byte of the word D15–D8, increments the address, and runs a second bus cycle.

When reading and writing, the MBC will assure proper operation when performing even byte accesses, even word accesses, and odd byte accesses. Figure 2-4 shows the read cases, and Figure 2-5 shows the write cases. The even word access is the only case requiring two bus cycles. When an internal bus cycles is taking place, both  $\overline{\rm AS}$  and the appropriate chip select will be in operation (except when FAST CYCLES are used). The address is incremented only in the case of an even address access. Because of this, the address increment only involves setting A0 to one.

Figure 2-2. 8-bit External to 16-bit Internal Read

Note that an external access of 16-bits to an 8-bit port requires an external address increment as well as data muxing. It is generally recommended that external accesses using the 8-bit chip select extensions access only 8-bits at a time and access that data on the upper 8-bits of the bus.

Figure 2-3. 16-bit Internal to 8-bit External Write

# 2.9.1 Bus Cycle Timing

The 8-bit extension logic for dynamic sizing is programmable from -1 to 5 wait states, and allows the external logic to terminate the cycle. Even word accesses are a special case which require specific control operations to allow the device to provide two external bus cycles. In some cases, the timing generated looks like two comparable 68000 cycles. There are two exceptions to this. First, the -1 wait state timing is a special case, since the 68000 bus is defined as a minimum 4 clock bus. The second exception is the Fast Cycle case. The -1 wait state case appears externally as two 16-bit 3 clock bus cycles. Figure 2-4 shows the timing for the read case, while Figure 2-5 shows the timing for writes.

Figure 2-4. Word Read with 3-Clock 8-Bit Accesses

Figure 2-5. Word Write with 3-Clock 8-Bit Accesses

The fast cycle case differs from the normal cycle in that  $\overline{AS}$  and chip select do not negate between the first and second half of the 16-bit access, allowing the two bus cycles to be

reduced one extra clock. A0 is incremented one half clock earlier in this scheme to allow sufficient address access in the second portion of the bus cycle. Figure 2-6 shows the fast cycle read case, while Figure 2-7 shows the fast cycle write case. In order to use fast cycles with SRAM, the  $\overline{\text{CS}}$  signal is high between cycles, accommodating a write to SRAMs.

Figure 2-6. Fast Cycle Word Read with -1 Wait State

Figure 2-7. Fast Cycle Word Write with -1 Wait State

# 2.9.2 Bus Error Handling

Since the external bus may operate as an 8-bit bus, at the same time the internal bus operates as 16-bits, a bus error passed from the external bus to the internal bus does not specify which byte has been faulted. To assure that information is not lost, the Bus Error

Byte (BB) bit is provided in the MBC register. This bit reflects the state of A0 during the last bus error caused by an access to a byte peripheral.

# 2.9.3 Retry Handling

In most cases, an MC68EN302 retry is identical to 302 retry operation. If however, a retry occurs during the second bus cycle of a word access to an 8-bit port, the retry signal is passed to the initiating master. This causes both of the cycles to be retried, instead of just the second cycle.

#### 2.10 PARITY LOGIC

The MC68EN302 provides parity support to generate, check, and report parity and parity errors.

# 2.10.1 Parity Generation

The MC68EN302 provides the option of generating and checking parity for the 4 chip selects and the 2 DRAM banks. In the case of a write, parity is generated with one bit of parity per byte of data. The parity is output on the parity pins and delayed from other data by the propagation delay through the parity generator.

# 2.10.2 Parity Checking

Parity checking is performed on read accesses. If the 8-bit option of the Chip Select logic is used, parity is checked on only the upper 8-bits. In all other options, parity is checked on both bytes.

# 2.10.3 Parity Error Reporting

Parity error reporting is accomplished via three mechanisms.

Parity Error Pin

This pin is asserted when a parity error is detected. Parity error detection does not occur with enough time to generate a bus error on the affected cycle. The parity error pin may be used with external circuitry to facilitate parity error handling. This pin is not negated until all the parity error register bits are cleared.

Parity Error Status Bits

There are 6 PCSR register bits dedicated to providing status on parity errors, corresponding to the 2 DRAM banks and the 4 Chip Selects. If a parity error is detected, the bit that corresponds to the module that generated the error is set. These bits are reset to zero and are cleared by writing a one.

Parity Error Interrupt

The PIE bit in the PCSR register is provided to allow the option of generating a level 5 (or 3) interrupt in the event that a parity error is generated. If this option is selected, the interrupt is driven after the error is detected until the Parity Error Status Bits are cleared.

# 2.10.4 Parity Pin Enable

During hardware reset, the parity pin enable bit (PPE) in the MBC register (see 2.4 Module Bus Control (MBCTL)) is cleared, which results in the parity pins becoming inputs. Each of the three pins is sampled for a different function, as shown in Table 2-5. After exiting

| PPE = 0      | PPE = 1      |

|--------------|--------------|

| PIN FUNCTION | PIN FUNCTION |

| DISCPU       | PARITY0      |

| BUSW         | PARITY1      |

| THREES       | PARITYE      |

**Table 2-5. Parity Pin Enable Operation**

hardware reset, these pins are sampled to determine chip functions. Pullup or pulldown resistors are required for presetting the desired state if the parity pins are to be later programmed as input/output pins. After hardware reset, the PPE bit can be set to enable the parity pins as outputs. The PPE bit should be set to enable parity even on reads.

#### 2.11 INTERRUPT SUPPORT

All module bus and module bus controller interrupts are at level 5 or at level 3 if MIL is set (See 2.5 Interrupt Extension Register (IER)). There are two sources of interrupts in the MBC: One is the Ethernet controller; the second source is the parity error interrupt. The parity error interrupt is the higher priority of the two. If an interrupt acknowledge cycle is generated when both interrupts are asserted, the MBC responds to the parity error interrupt by driving its vector onto the internal 68000 bus. Only after the parity error interrupt is cleared will the Ethernet controller respond to an IACK cycle.

In order to accommodate an additional interrupt source within the MC68EN302, an additional Interrupt Mode (IMOD) bit is provided in the MBC. This bit configures the Interrupt pins as  $\overline{IRQ}$  or  $\overline{IPL}$  lines. This replaces the MOD bit in the Global Interrupt Mode Register (GIMR). This means that the existing MOD bit in the Global Interrupt Mode Register (GIMR) must always remain at zero. The IMOD bit in the IER register duplicates this function in the MBC.

Since the MBC generates a level 5 (or level 3) interrupt, and there is no way to resolve IACK conflicts with the external circuitry, a level 5 (or level 3) interrupt should not be asserted externally. Figure 2-8 summarizes the interrupt configuration and priorities.

| Priority<br>Level | Normal Mode<br>IPL2-IPL0 | Dedicated Mode<br>IRQ7, IRQ6, IRQ1 | Interrupt<br>Source |

|-------------------|--------------------------|------------------------------------|---------------------|

| 7 (Highest)       | 000                      | ĪRQ7                               | External            |

| 6                 | 001                      | ĪRQ6                               | External            |

| 5                 | **                       | *                                  | MBC/External        |

| 4                 | *                        | *                                  | Internal 302        |

| 3                 | **                       | *                                  | External/MBC        |

| 2                 | 101                      | *                                  | External            |

| 1 (Lowest)        | 110                      | ĪRQ1                               | External            |

Figure 2-8. External and Internal Interrupt Prioritization

The MBC passes the interrupt vector (see 4.1.4 Interrupt Vector Register (IVEC)) from the Module bus to the 68000 bus.

<sup>\*</sup>Priority level not available to an external device in this mode \*\* The level not selected by MIL is available but not both level 3 and level 5.

# SECTION 3 MC68EN302 DRAM CONTROL MODULE

## 3.1 INTRODUCTION

The MC68EN302, like its predecessor the MC68302, can be connected with DRAM-type memories easily. The difference in the MC68EN302 lies in the DRAM Control Module (DCM), which was developed to provide seamless integration of the 68000 core with DRAM memories. The MC68EN302 DRAM controller is able to support up to two 16-bit wide banks and an address range from 128kbytes to 8Mbytes. Selection between the two banks occurs externally through the MC68EN302  $\overline{RAS1}$ – $\overline{RAS0}$  signals, and byte selection occurs via the  $\overline{CAS1}$ – $\overline{CAS0}$  signals. The user is able to select cycle lengths ranging in duration from 4 to 7 clocks. The MC68EN302 also provides programmable refresh rates which can range anywhere from 16 to 4096 system clocks, or be disabled altogether.

#### 3.2 MEMORY MAP

Table 3-1 shows the basic memory map of the DRAM Control Module registers.

**ADDRESS** NAME **MNEMONIC TYPE** FC MOBA + 010 **DRAM Configuration Register** DCR Read/Write S S MOBA + 012 **DRAM Refresh Register** DRFRSH Read/Write MOBA + 014 DRAM Bank 0 Base Address Register DBA0 Read/Write S MOBA + 016 DRAM Bank 1 Base Address Register DBA1 Read/Write S

**Table 3-1. DRAM Controller Registers**

# 3.3 DRAM CONFIGURATION REGISTER (DCR)

This register controls the specific operation of each bank of DRAM and is initialized to zero at hardware reset.

| 15 | 14 | 13 | 12 | 11 | 10 | 9   | 8   | 7  | 6  | 5  | 4  | 3   | 2   | 1    | 0    |

|----|----|----|----|----|----|-----|-----|----|----|----|----|-----|-----|------|------|

| 0  | 0  | 0  | 0  | E1 | E0 | PE1 | PE0 | P1 | P0 | W1 | W0 | WP1 | WP0 | S/U1 | S/U0 |

Bits 15–12—Reserved. Should be written to zero by the host processor. These bits are always read as zero.

E1-E0—Refresh Enable Bits.

- 0 = Disable refresh operation in the corresponding DRAM bank

- 1 = Enable refresh operation in the corresponding bank.

PE1-PE0—Enable Parity.

- 0 = Parity is generated but not checked

- 1 = Parity is generated on writes, and parity is checked on reads in the corresponding bank. If a parity error is detected the bus cycle is terminated with a bus error.

#### **NOTE**

If the Parity Pin Enable bit (PPE in MBC CSR) = 0 and parity is enabled on the DRAM interface (PE1 and/or PE0 = 1 in DCR) then a parity error will be reported on PED1–PED0.

P1-P0—RAS Precharge bits. These bits control the minimum number of clocks the RAS signal is precharged between bus cycles. Table 3-3 shows the encoding for these bits.

| P1 | P0 | PRECHARGE CLOCKS |

|----|----|------------------|

| 0  | 0  | 2                |

| 0  | 1  | 3                |

| 1  | 0  | 4                |

| 1  | 1  | 5                |

**Table 3-2. Precharge Bit Encodings**

W1-W0—Wait state bits. These bits control the number of wait states required for DRAM bank accesses. Table 3-3 shows the wait state bit encodings.

| W1 | W0 | WAIT STATES |

|----|----|-------------|

| 0  | 0  | 0           |

| 0  | 1  | 1           |

| 1  | 0  | 2           |

| 1  | 1  | 3           |

Table 3-3. Wait State Bit Encodings

WP1-WP0—Write Protect. This bit enables and disables write protection to a corresponding DRAM bank.

- 0 = The corresponding DRAM bank may be written.

- 1 = Write access to the corresponding DRAM bank returns a bus error.

S/U1-S/U0—Supervisor/User. This bit determines whether the given DRAM bank decodes to Supervisor Space (FC = 6 & 5) or both Supervisor and User (FC = 6 & 5 & 1 & 2) Space.

- 0 = Respond to Supervisor accesses only

- 1 = Respond to Supervisor and User Space.

# 3.4 DRAM REFRESH REGISTER (DRFRSH)

This register controls the operation of the refresh circuitry and is initialized to zero on hardware reset.

| 15 |   | _ |   |   | _ | - | _ |    | -  | -  |    | _  |    |    | -  |

|----|---|---|---|---|---|---|---|----|----|----|----|----|----|----|----|

| 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | R7 | R6 | R5 | R4 | R3 | R2 | R1 | R0 |

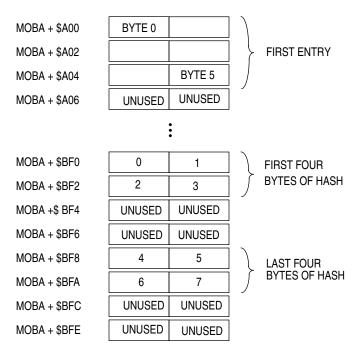

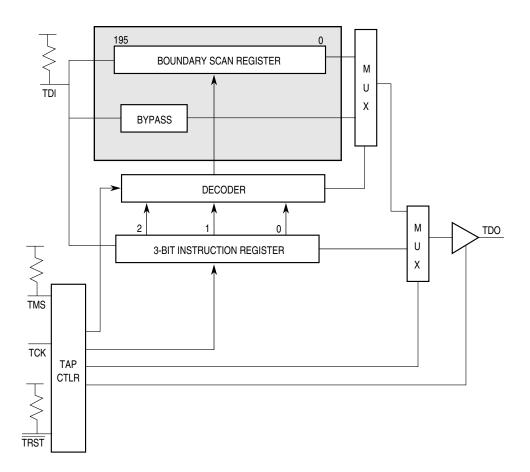

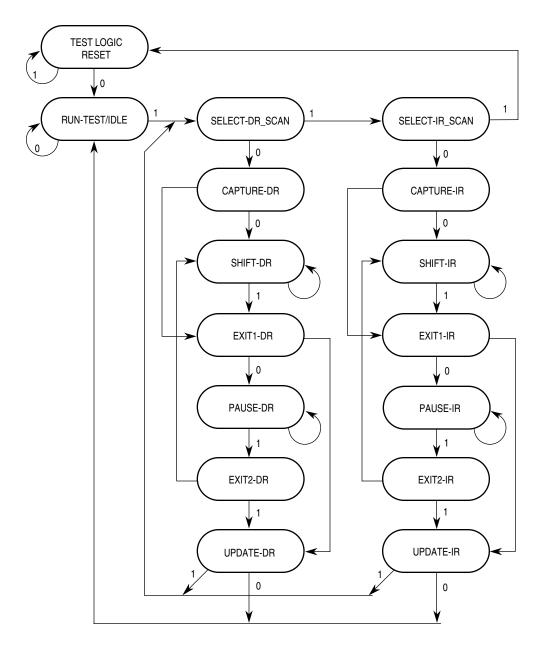

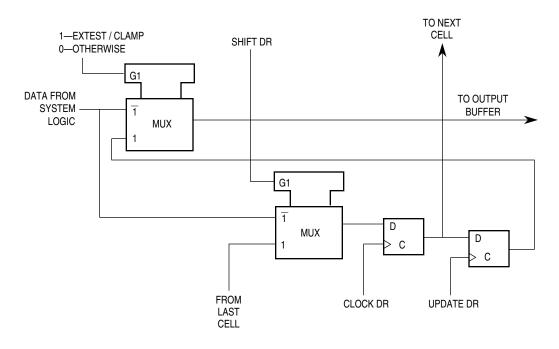

Bits 15–8—Reserved. Should be written to zero by the host processor. These bits are always read as zero.