**RoHS Recast Compliant**

# **Industrial Secure Digital Card**

**R1-M Product Specifications (Standard Temperature)**

September 16, 2020 Version 1.2

Apacer Technology Inc.

1F, No.32, Zhongcheng Rd., Tucheng Dist., New Taipei City, Taiwan, R.O.C Tel: +886-2-2267-8000 Fax: +886-2-2267-2261 www.apacer.com

# **Specifications Overview:**

- Fully Compatible with SD Card Specifications 3.0, 2.0 and 1.1

- SD Memory Card Specifications, Part 1, Physical Layer Specification, Ver 3.01 Final

- SD Memory Card Specifications, Part 2, File System Specification, Ver 3.00

- SD Memory Card Specifications, Part 3, Security Specification, Ver 3.00

- Capacity

- 8, 16 GB

- Performance\*

- Sequential read: Up to 90 MB/sec

- Sequential write: Up to 25 MB/sec

- Random read (4K): Up to 1,400 IOPS

- Random write (4K): Up to 95 IOPS

#### Flash Management

- Built-in advanced ECC algorithm

- Global Wear Leveling

- Flash bad-block management

- Page Mapping

- S.M.A.R.T.

- Power Failure Management

- SMART Read Refresh<sup>™</sup>

#### NAND Flash Type: MLC

- Temperature Range

- Operating: -25°C to 85°C

- Storage: -40°C to 85°C

- Operating Voltage: 2.7V ~ 3.6V

- Power Consumption\*

- Operating: 115 mA

- Standby: 265 µA

- Bus Speed Mode: Support Class 10 with UHS-I\*\*

- DS: Default Speed up to 25MHz 3.3V signaling

- HS: High Speed up to 50MHz 3.3V signaling

- SDR12: SDR up to 25MHz 1.8V signaling

- SDR25: SDR up to 50MHz 1.8V signaling

- SDR50: SDR up to 100MHz 1.8V signaling

- SDR104: SDR up to 208MHz 1.8V signaling

1

- DDR50: DDR up to 50MHz 1.8V signaling

- SD-Protocol Compatible

- Supports SD SPI Mode

- Physical Dimensions: 32mm (L) x 24mm (W) x 2.1mm (H)

- RoHS Recast Compliant (2011/65/EU)

\*Varies from capacities. Performance values presented here are typical and measured based on USB 3.0 card reader. The results may vary depending on settings and platforms.

\*\*Timing in 1.8V signaling is different from that of 3.3V signaling. Operation mode selection command is complaint with SD 3.0, referring to SDA's Part 1, Physical Layer Specification, Ver 3.01 (Section 3.9).

# **Table of Contents**

| 1. General Descriptions                                                | 4  |

|------------------------------------------------------------------------|----|

| 1.1. Product Functional Block                                          | 4  |

| 1.2 Flash Management                                                   | 5  |

| 1.2.1 Bad Block Management                                             | 5  |

| 1.2.2 Powerful ECC Algorithms                                          | 5  |

| 1.2.3 Global Wear Leveling                                             | 5  |

| 1.2.4 S.M.A.R.T.                                                       | 5  |

| 1.2.5 Power Failure Management                                         |    |

| 1.2.6 SMART Read Refresh <sup>™</sup>                                  | 5  |

| 1.2.7 Page Mapping                                                     | 6  |

| 2. Electrical Characteristics                                          | 7  |

| 2.1 Card Architecture                                                  | 7  |

| 2.2 Pin Assignment                                                     | 7  |

| 2.3 Capacity Specifications                                            | 8  |

| 2.4 Performance Specifications                                         | 8  |

| 2.5 DC Power Supply                                                    | 8  |

| 2.6 Power Consumption                                                  | 8  |

| 3. Physical Characteristics                                            | 9  |

| 3.1 Physical Dimensions                                                | 9  |

| 3.2 Durability Specifications                                          | 10 |

| 4. AC Characteristics                                                  | 11 |

| 4.1 SD Interface Timing (Default)                                      | 11 |

| 4.2 SD Interface Timing (High Speed Mode)                              | 12 |

| 4.3 SD Interface Timing (SDR12, SDR25, SDR50 and SDR104 Modes) Input   | 14 |

| 4.3.1 Clock Timing                                                     | 14 |

| 4.3.2 Card Input Timing                                                | 14 |

| 4.3.3 Card Output Timing of Fixed Data Window (SDR12, SDR25 and SDR50) | 15 |

| 4.3.4 Output Timing of Variable Window (SDR104)                        | 15 |

| 4.3.5 SD Interface Timing (DDR50 Mode)                                 | 16 |

| 4.3.6 Bus Timings – Parameters Values (DDR50 Mode)                     | 17 |

| 5. Product Ordering Information                                        | 18 |

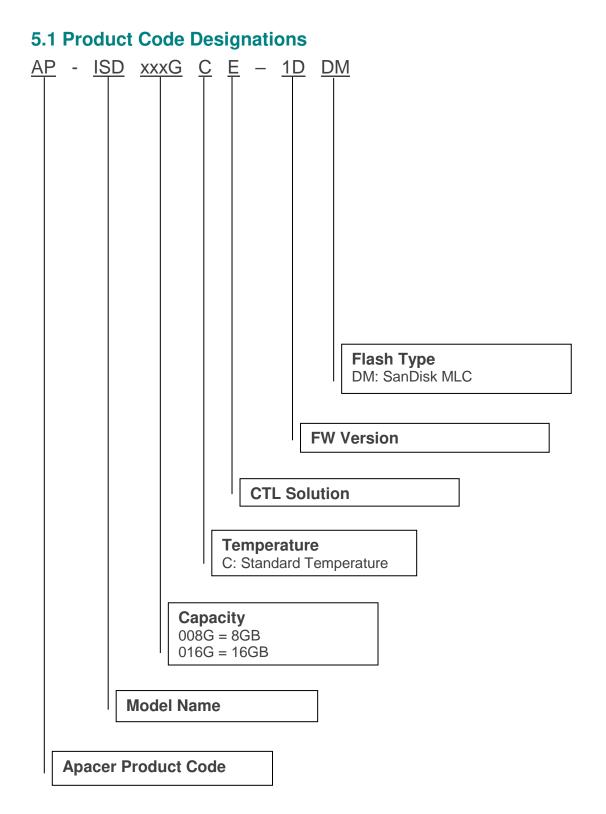

| 5.1 Product Code Designations                                          | 18 |

# **1. General Descriptions**

As the demand of reliable and high-performance data storage in a small form factor increases, Apacer's SD card is designed specifically for rigorous applications by offering maximum endurance, reliability, and agility, where extreme traceability, enhanced data integrity, and exceptionally velocity are required.

Regarding compatibility, this industrial SD card is compatible with SD Memory Card Specifications, Physical Layer specification, File System Specification and Part 3 Security Specification. Furthermore, the SD card is compatible with SD protocol. With built in ECC, wear-leveling and bad block management, this industrial SD card serves as an ideal portable storage solution.

### **1.1. Product Functional Block**

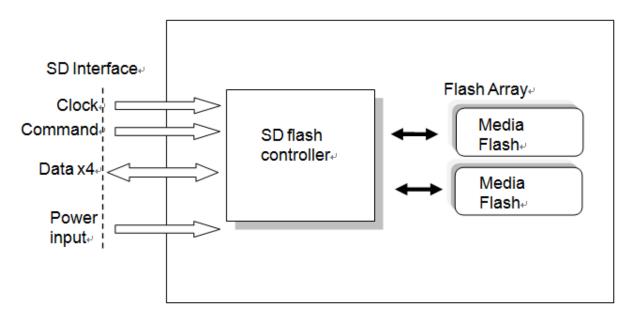

The SD contains a flash controller and flash media with SD standard interface.

Figure 2-1 Block Diagram

### **1.2 Flash Management**

#### **1.2.1 Bad Block Management**

Bad blocks are blocks that include one or more invalid bits, and their reliability is not guaranteed. Blocks that are identified and marked as bad by the manufacturer are referred to as "Initial Bad Blocks". Bad blocks that are developed during the lifespan of the flash are named "Later Bad Blocks". Apacer implements an efficient bad block management algorithm to detect the factory-produced bad blocks and manages any bad blocks that appear with use. This practice further prevents data being stored into bad blocks and improves the data reliability.

### **1.2.2 Powerful ECC Algorithms**

Flash memory cells will deteriorate with use, which might generate random bit errors in the stored data. Thus, the SD card applies the BCH ECC Algorithm, which can detect and correct errors occur during read process, ensure data been read correctly, as well as protect data from corruption. The SD controller can detect and correct up to 43 bits error in 1K bytes.

### 1.2.3 Global Wear Leveling

NAND Flash devices can only undergo a limited number of program/erase cycles, and in most cases, the flash media are not used evenly. If some area get updated more frequently than others, the lifetime of the device would be reduced significantly. Thus, Global Wear Leveling technique is applied to extend the lifespan of NAND Flash by evenly distributing writes and erase cycles across the media.

Apacer provides Global Wear Leveling algorithm, which can efficiently spread out the flash usage through the whole flash media area. Moreover, by implementing Global Wear Leveling algorithm, the life expectancy of the NAND Flash is greatly improved.

#### 1.2.4 S.M.A.R.T.

SMART, an acronym for Self-Monitoring, Analysis and Reporting Technology, is a special function that allows a memory device to automatically monitor its health. Apacer provides a program named SmartInfo Tool to observe Apacer's SD and MicroSD cards. Note that this tool can only support Apacer's industrial SD and MicroSD cards. This tool will display firmware version, endurance life ratio, good block ratio, and so forth.

### **1.2.5 Power Failure Management**

Apacer industrial SD and MicroSD cards provide complete data protection mechanism during every abnormal power shutdown situation, such as power failure at programming data, updating system tables, erasing blocks, etc. Apacer Power-Loss Protection mechanism includes:

- Maintaining data correctness and increasing the reliability of the data stored in the NAND Flash memory.

- Protecting F/W table and the data written to flash from data loss in the event of power off.

### 1.2.6 SMART Read Refresh<sup>™</sup>

Apacer's SMART Read Refresh plays a proactive role in avoiding read disturb errors from occurring to ensure health status of all blocks of NAND flash. Developed for read-intensive applications in particular, SMART Read Refresh is employed to make sure that during read operations, when the read operation threshold is reached, the data is refreshed by re-writing it to a different block for subsequent use.

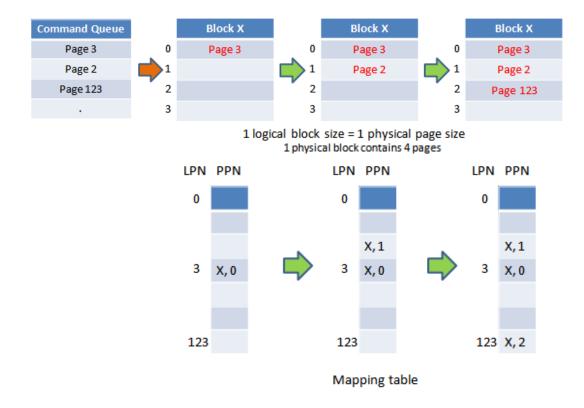

#### 1.2.7 Page Mapping

Page-level mapping uses one page as the unit of mapping. The most important characteristic of pagelevel mapping is that each logical page can be mapped to any physical page on the flash memory device. This mapping algorithm allows different size of data to be written to a block as if the data is written to a data pool and it does not need to take extra operations to process a write command. The below example shows how page-level mapping performs a write command:

Host instructs three write commands: page 3, 2, and 123. The three pages are written into block X in sequence of command queue. Once all write commands are completed, the mapping table updates itself automatically.

Note: The example only shows the concept of how page-level mapping work and do not necessary happen in an actual case.

This fine-grained page-level mapping scheme makes better capability for handling random data, and increases overall performance and endurance significantly. However, page-level mapping requires SSDs to incorporate a larger RAM in order to maintain its mapping table.

# **2. Electrical Characteristics**

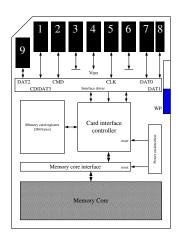

### 2.1 Card Architecture

Write Enabled

Write Protected

7

## 2.2 Pin Assignment

#### Table 2-1 Pin Descriptions

|     | SD Mode |                              |          | SPI Mode              |

|-----|---------|------------------------------|----------|-----------------------|

| Pin | Name    | Description                  | Name     | Description           |

| 1   | CD/DAT3 | Card detect/Data line[Bit 3] | CS       | Chip select           |

| 2   | CMD     | Command/Response             | DI       | Data in               |

| 3   | VSS1    | Supply voltage ground        | VSS      | Supply voltage ground |

| 4   | VDD     | Supply voltage               | VDD      | Supply voltage        |

| 5   | CLK     | Clock                        | SCLK     | Clock                 |

| 6   | VSS2    | Supply voltage ground        | VSS2     | Supply voltage ground |

| 7   | DAT0    | Data line[Bit 0]             | DO       | Data out              |

| 8   | DAT1    | Data line[Bit 1]             | Reserved |                       |

| 9   | DAT2    | Data line[Bit 2]             | Reserved |                       |

### 2.3 Capacity Specifications

The following table shows the specific capacity for the SD card.

#### Table 2-2 Capacity Specifications

| Capacity | Total bytes*   |

|----------|----------------|

| 8 GB     | 7,734,296,576  |

| 16 GB    | 15,468,593,152 |

Note: The statistics may vary depending on file systems of various OS. User data bytes do not indicate total useable bytes. LBA count addressed in the table above indicates total user storage capacity and will remain the same throughout the lifespan of the device. However, the total usable capacity of the SD is most likely to be less than the total physical capacity because a small portion of the capacity is reserved for device maintenance usages.

### 2.4 Performance Specifications

Performances of the SD card are shown in the table below.

#### Table 2-3 Performance Specifications

| Capacity<br>Performance  | 8 GB  | 16 GB |

|--------------------------|-------|-------|

| Sequential Read (MB/s)   | 90    | 90    |

| Sequential Write (MB/s)  | 25    | 25    |

| Random Read IOPS** (4K)  | 1,400 | 1,300 |

| Random Write IOPS** (4K) | 95    | 95    |

Note:

Results may differ from various flash configurations or host system setting.

\*Sequential performance is based on CrystalDiskMark 5.2.1 with file size 1,000MB.

\*\*Random performance measured using IOMeter with Queue Depth 32.

\*\*\*Performance results are measured based on USB 3.0 card reader.

### 2.5 DC Power Supply

#### Table 2-4 Operating Voltage

| Symbol | Parameter            | Min. | Тур. | Max. | Unit |

|--------|----------------------|------|------|------|------|

| Vdd    | Power Supply Voltage | 2.7  | 3.3  | 3.6  | V    |

### 2.6 Power Consumption

#### Table 2-5 Power Consumption

| Capacity<br>Mode | 8 GB | 16 GB |

|------------------|------|-------|

| Operating (mA)   | 105  | 115   |

| Standby (µA)     | 265  | 265   |

| Mater            |      |       |

Note:

\*All values are typical and may vary depending on flash configurations or host system settings.

\*\*Active power is an average power measurement performed using CrystalDiskMark with 128KB sequential read/write transfers.

# **3. Physical Characteristics**

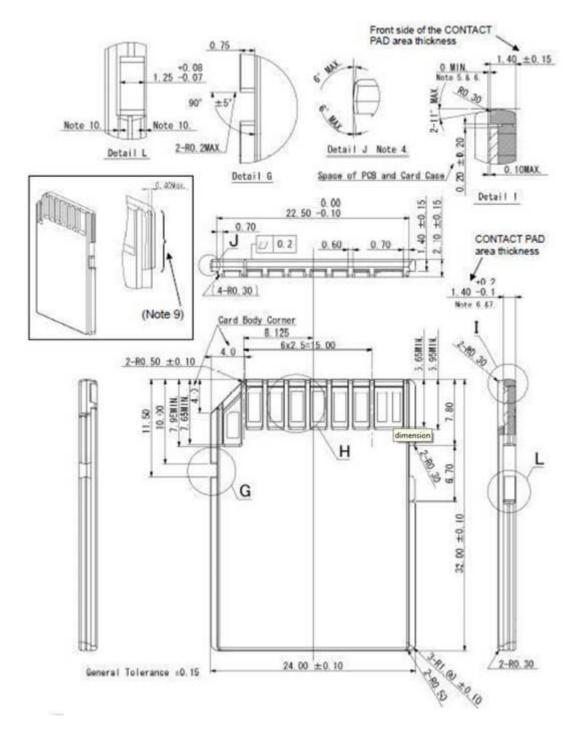

### **3.1 Physical Dimensions**

# 3.2 Durability Specifications

| Item                                                                                                                                        | Specifications                                                                                                                                 |

|---------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>–</b> .                                                                                                                                  | -25°C to 85°C (Operating)                                                                                                                      |

| Temperature                                                                                                                                 | -40°C to 85°C (Storage)                                                                                                                        |

| Shock                                                                                                                                       | 1,500G, 0.5ms                                                                                                                                  |

| Vibration                                                                                                                                   | 20Hz~80Hz/1.52mm (frequency/displacement)<br>80Hz~2000Hz/20G (frequency/displacement)<br>X, Y, Z axis/60mins each                              |

| Drop                                                                                                                                        | 1.5m free fall, 6 surfaces of each                                                                                                             |

| Bending                                                                                                                                     | $\geq$ 10N, hold 1min/5times                                                                                                                   |

| Torque                                                                                                                                      | 0.15N-m or 2.5deg, hold 30 seconds/ 5 times                                                                                                    |

| Salt spray                                                                                                                                  | Concentration: 3% NaCl at 35°C (storage for 24 hours)                                                                                          |

| Waterproof                                                                                                                                  | JIS IPX7 compliance, Water temperature 25°C<br>Water depth: the lowest point of unit is locating 1000mm below surface<br>(storage for 30 mins) |

| X-Ray Exposure0.1 Gy of medium-energy radiation<br>(70 KeV to 140 KeV, cumulative dose per year) to both side<br>card ;storage for 30 mins) |                                                                                                                                                |

| Switch Cycle                                                                                                                                | 0.4~0.5N, 1000 times                                                                                                                           |

| Durability                                                                                                                                  | 10,000 times mating cycle                                                                                                                      |

| ESD                                                                                                                                         | Contact: +/-4KV each item 25 times<br>Air: +/-8KV 10 times                                                                                     |

Table 3-1 Durability Specifications

# **4. AC Characteristics**

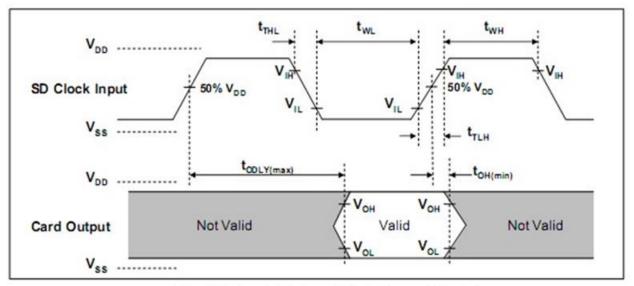

### 4.1 SD Interface Timing (Default)

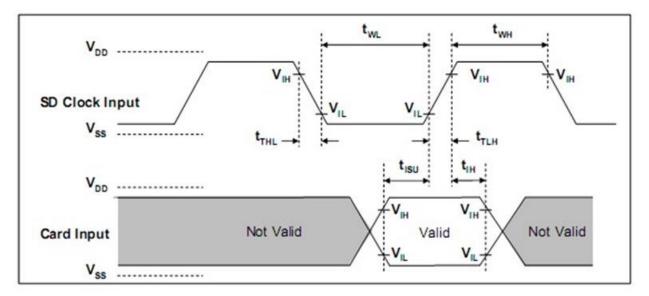

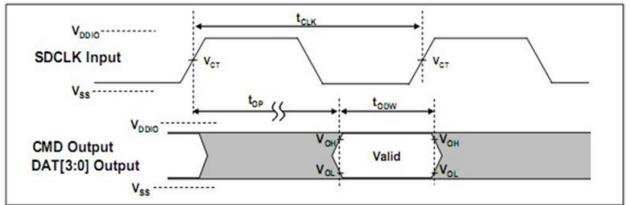

### Card input Timing (Default Speed Card)+

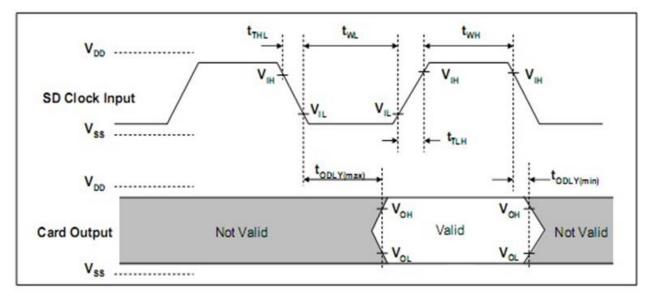

### Card Output Timing (Default Speed Mode)-

| SYMBOL          | PARAMETER                                   | MIN         | МАХ       | UNIT                   | REMARK                                |  |  |  |

|-----------------|---------------------------------------------|-------------|-----------|------------------------|---------------------------------------|--|--|--|

|                 | Clock CLK (All values are refe              | erred to mi | n(V⊮) and | max(V <sub>IL</sub> )) |                                       |  |  |  |

| fpp             | Clock frequency data transfer               | 0           | 25        | MHz                    | C <sub>card</sub> ≤ 10 pF<br>(1 card) |  |  |  |

| fod             | Clock frequency identification              | 0(1)/100    | 400       | KHz                    | C <sub>card</sub> ≤ 10 pF<br>(1 card) |  |  |  |

| tw∟             | Clock low time                              | 10          | -         | ns                     | C <sub>card</sub> ≤ 10 pF<br>(1 card) |  |  |  |

| twн             | Clock high time                             | 10          | -         | ns                     | C <sub>card</sub> ≤ 10 pF<br>(1 card) |  |  |  |

| tт∟н            | Clock rise time                             | -           | 10        | ns                     | C <sub>card</sub> ≤ 10 pF<br>(1 card) |  |  |  |

| t⊤н∟            | Clock fall time                             | -           | 10        | ns                     | C <sub>card</sub> ≤ 10 pF<br>(1 card) |  |  |  |

|                 | Inputs CMD, DAT (                           | Referenced  | to CLK)   |                        | (1 00.0)                              |  |  |  |

| tisu            |                                             |             | -         | ns                     | C <sub>card</sub> ≤10 pF<br>(1 card)  |  |  |  |

| tтн             | Input hold time                             | 5           | -         | ns                     | C <sub>card</sub> ≤ 10 pF<br>(1 card) |  |  |  |

|                 | Outputs CMD, DAT (Referenced to CLK)        |             |           |                        |                                       |  |  |  |

| todly           | Output delay time during data transfer mode | 0           | 14        | ns                     | C <sub>L</sub> ≤ 40 pF<br>(1 card)    |  |  |  |

| t <sub>OH</sub> | Output hold time                            | 0           | 50        | ns                     | C <sub>L</sub> ≤ 40 pF<br>(1 card)    |  |  |  |

(1)0Hz means to stop the clock. The given minimum frequency range is for cases that require the clock to be continued.

### 4.2 SD Interface Timing (High Speed Mode)

Card Input Timing (High Speed Card)+

Card Output Timing (High Speed Mode)

| SYMBOL          | PARAMETER                                      | MIN         | МАХ                       | UNIT                   | REMARK                    |

|-----------------|------------------------------------------------|-------------|---------------------------|------------------------|---------------------------|

|                 | Clock CLK (All values are refe                 | erred to mi | n(V <sub>IH</sub> ) and ı | max(V <sub>IL</sub> )) |                           |

| fpp             | Clock frequency data transfer                  | 0           | 50                        | MHz                    | Ccard ≤ 10 pF<br>(1 card) |

| twL             | Clock low time                                 | 7           | -                         | ns                     | Ccard ≤ 10 pF<br>(1 card) |

| twн             | Clock high time                                | 7           | -                         | ns                     | Ccard ≤ 10 pF<br>(1 card) |

| tт∟н            | Clock rise time                                | -           | 3                         | ns                     | Ccard ≤ 10 pF<br>(1 card) |

| tтн∟            | Clock fall time                                | -           | 3                         | ns                     | Ccard ≤ 10 pF<br>(1 card) |

|                 | Inputs CMD, DAT (F                             | Referenced  | I to CLK)                 |                        |                           |

| tisu            | Input setup time                               | 6           | -                         | ns                     | Ccard ≤ 10 pF<br>(1 card) |

| tтн             | Input hold time                                | 2           | -                         | ns                     | Ccard ≤ 10 pF<br>(1 card) |

|                 | Outputs CMD, DAT (                             | Reference   | d to CLK)                 |                        |                           |

| todly           | Output delay time during data<br>transfer made | -           | 14                        | ns                     | CL ≤ 40 pF<br>(1 card)    |

| t <sub>OH</sub> | Output hold time                               | 2.5         | -                         | ns                     | CL ≥ 15 pF<br>(1 card)    |

| CL              | Total system capacitance for each line*        | -           | 40                        | pF                     | 1 card                    |

\*In order to satisfy severe timing, host shall run on only one card

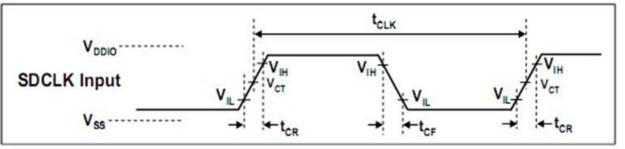

# 4.3 SD Interface Timing (SDR12, SDR25, SDR50 and SDR104 Modes) Input

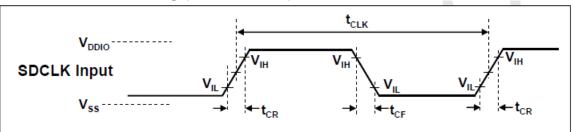

### 4.3.1 Clock Timing

### Clock Signal Timing-

| SYMBOL     | MIN | MAX                   | UNIT | REMARK                                                      |

|------------|-----|-----------------------|------|-------------------------------------------------------------|

| tськ       | 4.8 | -                     | ns   | 208MHz (Max.), Between rising edge, $V_{CT} = 0.975V$       |

| tcr, tcr   |     |                       |      | tcr, tcr < 2.00ns (max.) at 208MHz, Ccard=10pF              |

|            | -   | 0.2* t <sub>СLK</sub> | ns   | tcr, tcr < 2.00ns (max.) at 100MHz, C <sub>CARD</sub> =10pF |

|            |     |                       |      | The absolute maximum value of tcr, tcr is 10ns              |

|            |     |                       |      | regardless of clock frequency.                              |

| Clock Duty | 30  | 70                    | %    |                                                             |

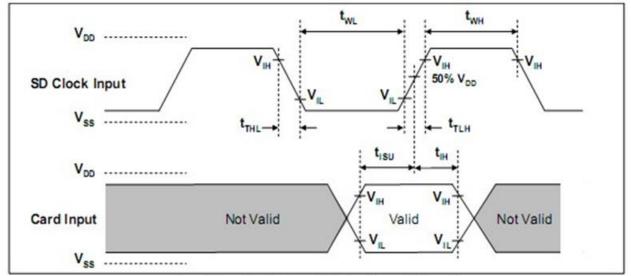

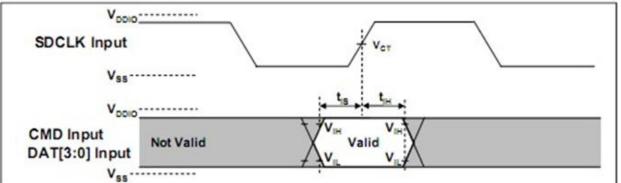

### 4.3.2 Card Input Timing

| Card Input Timing₀ |      |                      |      |                                      |  |  |  |

|--------------------|------|----------------------|------|--------------------------------------|--|--|--|

| SYMBOL             | MIN  | MAX UNIT SDR104 MODE |      |                                      |  |  |  |

| t <sub>IS</sub>    | 1.40 | -                    | ns   | $C_{CARD} = 10 pF, V_{CT} = 0.975 V$ |  |  |  |

| t <sub>IH</sub>    | 0.80 | -                    | ns   | $C_{CARD} = 5pF, V_{CT} = 0.975V$    |  |  |  |

| SYMBOL             | MIN  | MAX                  | UNIT | SDR12, SDR25 and SDR50 MODES         |  |  |  |

| t <sub>IS</sub>    | 3.00 | -                    | ns   | $C_{CARD} = 10 pF, V_{CT} = 0.975 V$ |  |  |  |

| t <sub>IH</sub>    | 0.80 | -                    | ns   | $C_{CARD} = 5pF, V_{CT} = 0.975V$    |  |  |  |

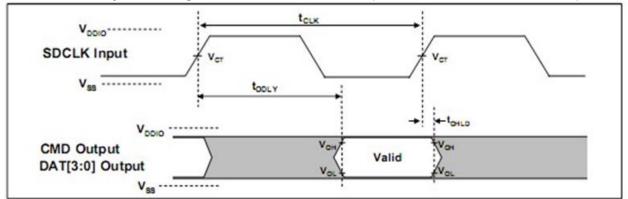

### 4.3.3 Card Output Timing of Fixed Data Window (SDR12, SDR25 and SDR50)

### Output Timing of Fixed Date Window.

| SYMBOL            | MIN | MAX | UNIT | REMARK                                                                    |

|-------------------|-----|-----|------|---------------------------------------------------------------------------|

| t <sub>ODLY</sub> | -   | 7.5 | ns   | $t_{CLK} \ge 10.0$ ns, CL=30pF, using driver Type B, for SDR50.           |

| t <sub>ODLY</sub> |     | 14  | ns   | $t_{CLK} \ge 20.0$ ns, CL=40pF, using driver Type B, for SDR25 and SDR12. |

| t <sub>он</sub>   | 1.5 | -   | ns   | Hold time at the t <sub>ODLY</sub> (min.). CL=15pF                        |

### 4.3.4 Output Timing of Variable Window (SDR104)

#### Output Timing of Variable Data Window

| SYMBOL           | MIN  | MAX   | UNIT | REMARK                                                 |  |  |

|------------------|------|-------|------|--------------------------------------------------------|--|--|

| t <sub>OP</sub>  | -    | 2     | UI   | Card Output Phase                                      |  |  |

| ∆t <sub>OP</sub> | -350 | +1550 | ps   | Delay variation due to temperature change after tuning |  |  |

| t <sub>odw</sub> | 0.60 | -     | UI   | t <sub>ODW</sub> = 2.88ns at 208MHz                    |  |  |

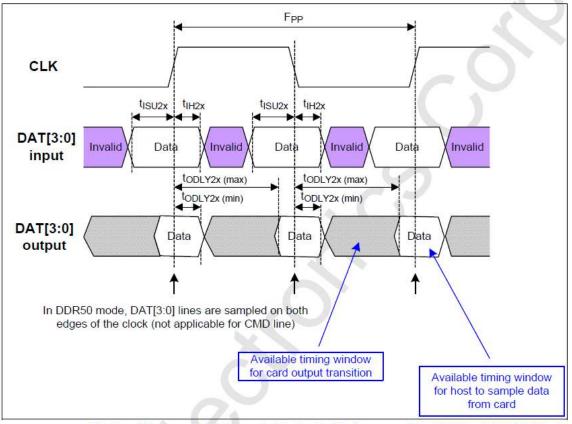

#### 4.3.5 SD Interface Timing (DDR50 Mode)

|                                   | Clock Signal Timing   |                       |    |                                                                           |  |  |

|-----------------------------------|-----------------------|-----------------------|----|---------------------------------------------------------------------------|--|--|

| SYMBOL                            | . MIN MAX UNIT REMARK |                       |    |                                                                           |  |  |

| tclk                              | 20                    | -                     | ns | 50MHz (Max.), Between rising edge                                         |  |  |

| t <sub>CR</sub> , t <sub>CF</sub> | -                     | 0.2* t <sub>CLK</sub> | ns | t <sub>CR</sub> , t <sub>CF</sub> < 4.00ns (max.) at 50MHz,<br>CCARD=10pF |  |  |

| Clock Duty                        | 45                    | 55                    | %  |                                                                           |  |  |

Timing Diagram DAT Inputs/Outputs Referenced to CLK in DDR50 Mode

|                     | i i i u u u u u u u u u u u u u u u u u        |           |            |                        | nouo/                                 |

|---------------------|------------------------------------------------|-----------|------------|------------------------|---------------------------------------|

| Symbol              | Parameters                                     | Min       | Max        | Unit                   | Remark                                |

|                     | Input C                                        | MD (refe  | erenced to | o CLK risi             | ng edge)                              |

| tisu                | Input set-up time                              | 6         | -          | ns                     | C <sub>card</sub> ≤ 10 pF<br>(1 card) |

| tıн                 | Input hold time                                | 0.8       | -          | ns                     | C <sub>card</sub> ≤ 10 pF<br>(1 card) |

|                     | Output                                         | CMD (ref  | erenced    | to CLK ris             | ing edge)                             |

| todly               | Output Delay time during<br>Data Transfer Mode | -         | 13.7       | ns                     | C <sub>L</sub> ≤30 pF<br>(1 card)     |

| Тон                 | Output Hold time                               | 1.5       | -          | ns                     | C∟≥15 pF<br>(1 card)                  |

|                     | Inputs DAT (                                   | reference | ed to CLK  | rising and             | d falling edges)                      |

| t <sub>ISU2x</sub>  | Input set-up time                              | 3         | -          | ns                     | C <sub>card</sub> ≤ 10 pF<br>(1 card) |

| t <sub>IH2x</sub>   | Input hold time                                | 0.8       | -          | ns                     | C <sub>card</sub> ≤ 10 pF<br>(1 card) |

|                     | Outputs DAT                                    | (referenc | ed to CLI  | <pre>K rising ar</pre> | nd falling edges)                     |

| t <sub>ODLY2x</sub> | Output Delay time during<br>Data Transfer Mode | -         | 7.0        | ns                     | C∟≤25 pF<br>(1 card)                  |

| T <sub>OH2x</sub>   | Output Hold time                               | 1.5       | -          | ns                     | C∟≥15 pF<br>(1 card)                  |

### 4.3.6 Bus Timings – Parameters Values (DDR50 Mode)

# **5. Product Ordering Information**

### **5.2 Valid Combinations**

| Capacity | Part Number       |

|----------|-------------------|

| 8GB      | AP-ISD008GCE-1DDM |

| 16GB     | AP-ISD016GCE-1DDM |

**Note:** Valid combinations are those products in mass production or will be in mass production. Consult your Apacer sales representative to confirm availability of valid combinations and to determine availability of new combinations.

# **Revision History**

| Revision | Date       | Description                                                                                                                  | Remark |

|----------|------------|------------------------------------------------------------------------------------------------------------------------------|--------|

| 1.0      | 12/15/2017 | Official release                                                                                                             |        |

| 1.1      | 12/19/2017 | Added seq. read/write QD32 and random read/write IOPS to Features page and 2.4 Performance Specifications                    |        |

| 1.2      | 9/16/2020  | <ul> <li>Renamed Read Disturb Management to<br/>SMART Read Refresh</li> <li>Updated 1.2.2 Powerful ECC Algorithms</li> </ul> |        |

### **Global Presence**

#### Taiwan (Headquarters)

Apacer Technology Inc. 1F., No.32, Zhongcheng Rd., Tucheng Dist., New Taipei City 236, Taiwan R.O.C. Tel: 886-2-2267-8000 Fax: 886-2-2267-2261 amtsales@apacer.com

#### Japan

Apacer Technology Corp. 6F, Daiyontamachi Bldg., 2-17-12, Shibaura, Minato-Ku, Tokyo, 108-0023, Japan Tel: 81-3-5419-2668 Fax: 81-3-5419-0018 jpservices@apacer.com

#### China

Apacer Electronic (Shanghai) Co., Ltd Room D, 22/FL, No.2, Lane 600, JieyunPlaza, Tianshan RD, Shanghai, 200051, China Tel: 86-21-6228-9939

Fax: 86-21-6228-9936 sales@apacer.com.cn

**U.S.A. Apacer Memory America, Inc.** 46732 Lakeview Blvd., Fremont, CA 94538 Tel: 1-408-518-8699 Fax: 1-510-249-9551 <u>sa@apacerus.com</u>

#### Europe

Apacer Technology B.V. Science Park Eindhoven 5051 5692 EB Son, The Netherlands Tel: 31-40-267-0000 Fax: 31-40-290-0686 sales@apacer.nl

#### India

Apacer Technologies Pvt Ltd, 1874, South End C Cross, 9<sup>th</sup> Block Jayanagar, Bangalore-560069, India Tel: 91-80-4152-9061/62 Fax: 91-80-4170-0215 sales\_india@apacer.com