# High Input Voltage, Adjustable 3-Terminal Linear Regulator

#### Features

- 13.2 to 100V input voltage range

- Stable with 100nF output capacitor

- Adjustable 1.20 to 88V output regulation

- 5% reference voltage tolerance

- Output current limiting, 50mA min.

- 10µA typical ADJ current

- Over temperature protection

- Available in 3 different packages

## Applications

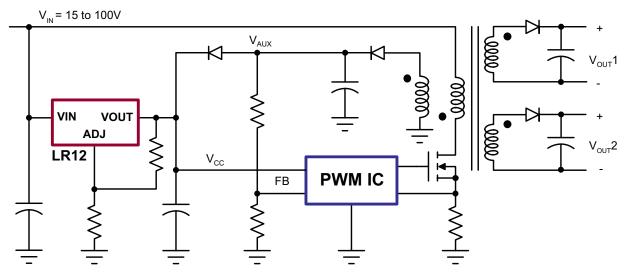

- DC/DC SMPS startup circuits

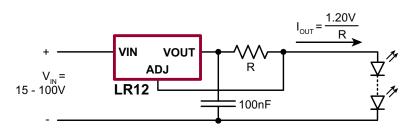

- Adjustable high voltage constant current sources

- Industrial controls

- Motor controls

- Battery powered systems

- Power supplies

- Telecom applications

- LED drivers

- Automotive applications

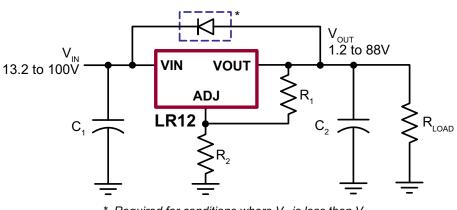

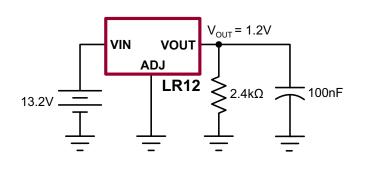

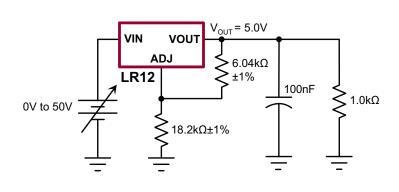

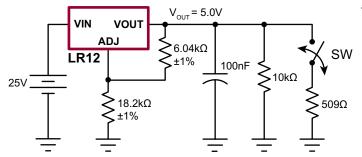

LR12 Typical Application

### **General Description**

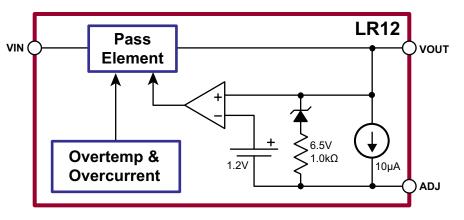

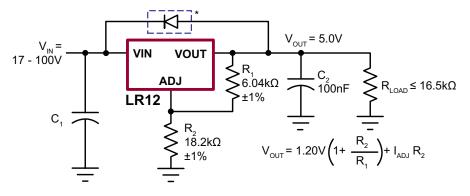

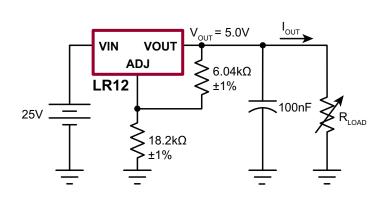

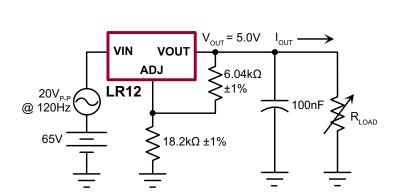

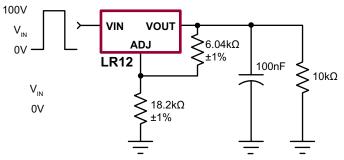

The Supertex LR12 is a high voltage, low output current, adjustable linear regulator. It has a wide operating input voltage range of 13.2 - 100V. The output voltage can be adjusted from 1.20 - 88V, provided that the input voltage is at least 12V greater than the output voltage. The output voltage can be adjusted by means of two external resistors R<sub>1</sub> and R<sub>2</sub> as shown in the typical application circuits. The LR12 regulates the voltage difference between VOUT and ADJ pins to a nominal value of 1.20V. The 1.20V is amplified by the external resistor ratio R<sub>1</sub> and R<sub>2</sub>. An internal constant bias current of typically 10µA is connected to the ADJ pin. This increases V<sub>OUT</sub> by a constant voltage of 10µA times R<sub>2</sub>.

The LR12 has current limiting and temperature limiting. The output current limit is 100mA maximum and the minimum temperature limit is 125°C. An output short circuit current will therefore be limited to 100mA maximum. When the junction temperature reaches its temperature limit, the output current and/or output voltage will decrease to keep the junction temperature from exceeding its temperature limit. For SMPS start-up circuit applications, the LR12 turns off when an external voltage greater than the output voltage of the LR12 is applied to VOUT of the LR12. To maintain stability, a bypass capacitor of 100nF or larger and a minimum DC output current of 500 $\mu$ A are required.

\* Required for conditions where  $V_{_{\rm IN}}$  is less than  $V_{_{\rm OUT}}$

# \_

#### **Ordering Information**

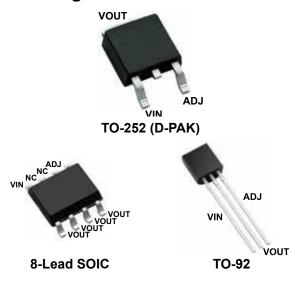

| Part Number   | Package Options | Packing   |

|---------------|-----------------|-----------|

| LR12K4-G      | TO-252 (D-PAK)  | 2000/Reel |

| LR12LG-G      | 8-Lead SOIC     | 2500/Reel |

| LR12N3-G      | TO-92           | 1000/Bag  |

| LR12N3-G P002 | TO-92           | 2000/Reel |

| LR12N3-G P003 | TO-92           | 2000/Reel |

| LR12N3-G P005 | TO-92           | 2000/Reel |

| LR12N3-G P013 | TO-92           | 2000/Reel |

| LR12N3-G P014 | TO-92           | 2000/Reel |

-G denotes a lead (Pb)-free / RoHS compliant package

### **Absolute Maximum Ratings**

| Parameter                                                                           | Value                |

|-------------------------------------------------------------------------------------|----------------------|

| V <sub>IN-ADJ</sub>                                                                 | -0.5V to +120V       |

| V <sub>OUT-ADJ</sub>                                                                | -10V to +10V         |

| V <sub>IN</sub> - V <sub>OUT</sub>                                                  | -0.5V to +120V       |

| Operating ambient temperature                                                       | -40°C to +85°C       |

| Operating junction temperature                                                      | -40°C to +125°C      |

| Storage temperature                                                                 | -65°C to +150°C      |

| Power Dissipation @ T <sub>A</sub> = 25°C<br>TO-252 (D-PAK)<br>8-Lead SOIC<br>TO-92 | 2.0W<br>1.8W<br>0.6W |

#### **Typical Thermal Resistance**

| Package     | <i>θ<sub>ja</sub></i> (°C/W) |

|-------------|------------------------------|

| TO-252      | 81°C/W                       |

| 8-Lead SOIC | 101°C/W                      |

| TO-92       | 132°C/W                      |

#### **Pin Configuration**

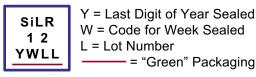

#### **Product Marking**

|     | Si YYWW<br>LR12K4<br>LLLLLLL | YY = Year Sealed<br>WW = Week Sealed<br>L = Lot Number<br>= "Green" Packaging |

|-----|------------------------------|-------------------------------------------------------------------------------|

| ack | age may or may no            | ot include the following marks: Si or $oldsymbol{G}$                          |

Package may or may not include the following marks: Si or Ŵ TO-252 (D-PAK)

| G | YYWW        |

|---|-------------|

|   | LR12        |

| • | <u>LLLL</u> |

YY = Year Sealed WW = Week Sealed L = Lot Number \_\_\_\_\_ = "Green" Packaging

Package may or may not include the following marks: Si or

#### 8-Lead SOIC

W = Code for Week Sealed L = Lot Number - = "Green" Packaging

Package may or may not include the following marks: Si or **TO-92**

#### **Electrical Characteristics** (Test conditions unless otherwise specified: $-40^{\circ}C < T_a < +85^{\circ}C$ )

| Sym                               | Parameter                          | Min  | Тур   | Max  | Units | Conditions                                                                         |

|-----------------------------------|------------------------------------|------|-------|------|-------|------------------------------------------------------------------------------------|

| V <sub>IN</sub> -V <sub>OUT</sub> | Input to output voltage difference | 12   | -     | 98.8 | V     |                                                                                    |

| V <sub>OUT</sub>                  | Overall output voltage regulation  | 1.14 | 1.20  | 1.26 | V     | $13.2V < V_{IN} < 100V, R_1 = 2.4K\Omega, R_2 = 0$                                 |

|                                   | Line regulation                    | -    | 0.003 | 0.03 | %/V   | 15V < V <sub>IN</sub> <100V, V <sub>OUT</sub> = 5.0V, I <sub>OUT</sub> = 0.5A      |

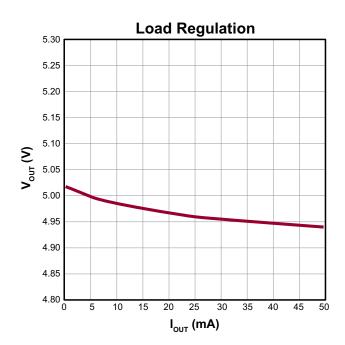

| ΔV <sub>out</sub>                 | Load regulation                    | -    | 1.4   | 3.0  | %     | V <sub>IN</sub> = 15V, V <sub>OUT</sub> = 5.0V,<br>0.5mA< I <sub>OUT</sub> <50mA   |

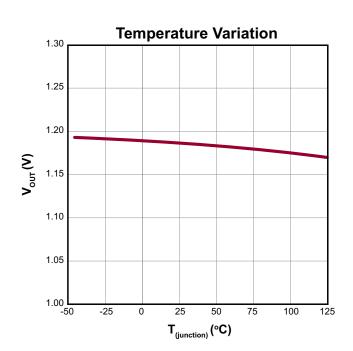

|                                   | Temperature regulation             | -1.0 | -     | +1.0 | %     | $V_{IN} = 15V, V_{OUT} = 5.0V, I_{OUT} = 10mA, -40^{\circ}C < T_{A} < 85^{\circ}C$ |

#### Electrical Characteristics (cont.)

| Sym                                 | Parameter                       | Min | Тур | Max  | Units | Conditions                                                      |

|-------------------------------------|---------------------------------|-----|-----|------|-------|-----------------------------------------------------------------|

|                                     |                                 | 50  | -   | 100  | ma    | T <sub>J</sub> < 85°C, V <sub>IN</sub> - V <sub>OUT</sub> < 12V |

| I <sub>OUT</sub>                    | Output current limit            | -   | -   | -0.5 | ma    | $T_{J} < 125^{\circ}C, V_{IN} - V_{OUT} < 100V$                 |

|                                     | Minimum output current          |     | -   | -    | mA    | Includes $R_1$ and load current                                 |

| I <sub>ADJ</sub>                    | Adjust output current           | 5.0 | 10  | 15   | μA    |                                                                 |

| C2                                  | Minimum output load capacitance | 100 | -   | -    | nF    |                                                                 |

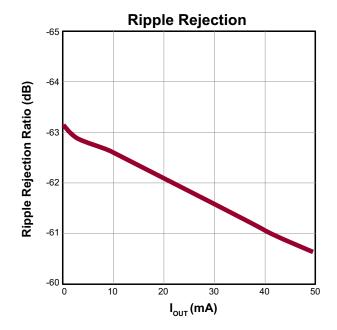

| DV <sub>OUT</sub> /D <sub>VIN</sub> | Ripple rejection ratio          | 50  | 60  | -    | dB    | 120Hz, V <sub>OUT</sub> = 5.0V                                  |

| T <sub>LIMIT</sub>                  | Junction temperature limit      | 125 | -   | -    | °C    |                                                                 |

### **Functional Block Diagram**

# **Current Limit**

#### **Typical Application Circuits**

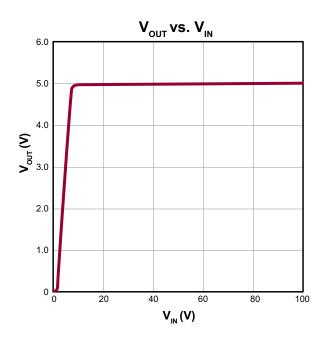

#### Figure 1: High Input Voltage, 5.0V Output Linear Regulator

\* Required for conditions where  $V_{IN}$  is less than  $V_{OUT}$

#### Figure 2: SMPS Start-Up Circuit

Figure 3: High Voltage Adjustable Constant Current Source

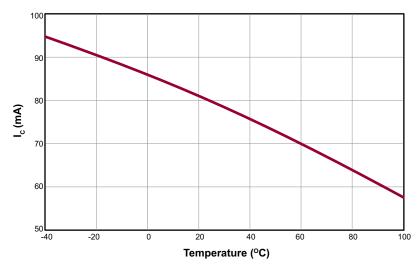

#### **Typical Performance Curves**

### Typical Performance Curves (cont.)

#### Typical Performance Curves (cont)

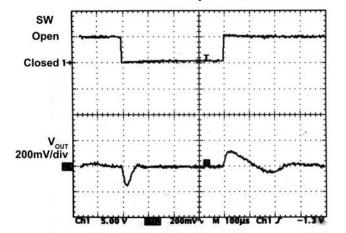

#### Load Transient Response

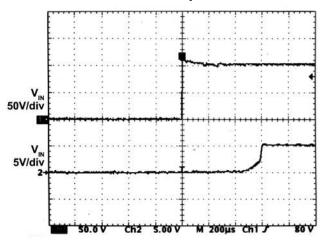

Line Transient Response

Load Transient Response, Load = 509Ω

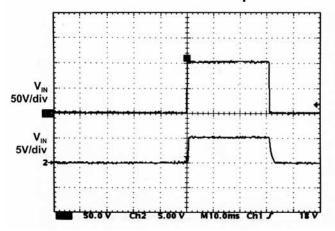

Line Turn On/Off Response

Line Power Up Transient

Line Power Down Transient

# LR12

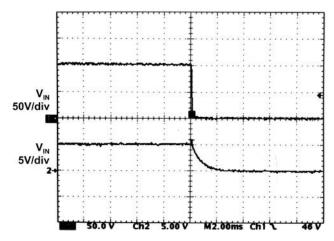

# 3-Lead TO-252 (D-PAK) Package Outline (K4)

#### Note:

1. Although 4 terminal locations are shown, only 3 are functional. Lead number 2 was removed.

| Symb     | ol  | Α    | A1    | b    | b2   | b3   | c2   | D    | D1    | Ε    | E1    | е           | Н    | L    | L1          | L2          | L3   | L4    | L5   | θ   | θ1              |

|----------|-----|------|-------|------|------|------|------|------|-------|------|-------|-------------|------|------|-------------|-------------|------|-------|------|-----|-----------------|

| Dimen-   | MIN | .086 | .000* | .025 | .030 | .195 | .018 | .235 | .205  | .250 | .170  |             | .370 | .055 |             |             | .035 | .025* | .045 | 00  | 00              |

| sion     | NOM | -    | -     | -    | -    | -    | -    | .240 | -     | -    | -     | .090<br>BSC | -    | .060 | .108<br>REF | .020<br>BSC | -    | -     | -    | -   | -               |

| (inches) | MAX | .094 | .005  | .035 | .045 | .215 | .035 | .245 | .217* | .265 | .182* |             | .410 | .070 |             |             | .050 | .040  | .060 | 10º | 15 <sup>0</sup> |

JEDEC Registration TO-252, Variation AA, Issue E, June 2004.

\* This dimension is not specified in the JEDEC drawing.

Drawings not to scale.

Supertex Doc. #: DSPD-3TO252K4, Version E091009.

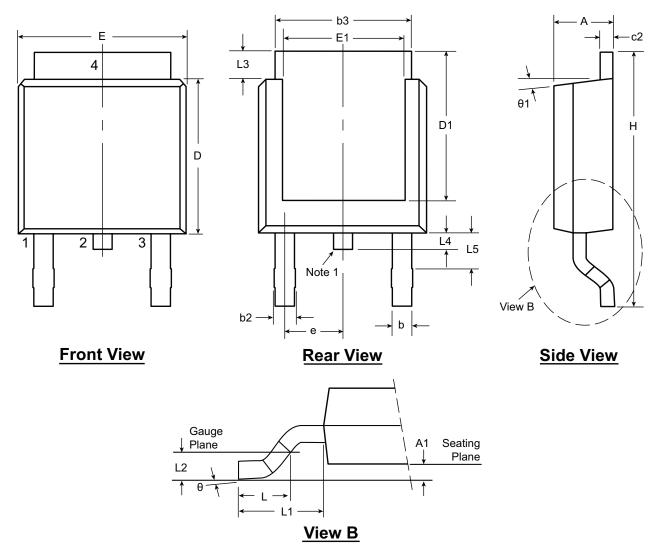

### 8-Lead SOIC (Narrow Body) Package Outline (LG) 4.90x3.90mm body, 1.75mm height (max), 1.27mm pitch

#### Note:

1. This chamfer feature is optional. A Pin 1 identifier must be located in the index area indicated. The Pin 1 identifier can be: a molded mark/identifier; an embedded metal marker; or a printed indicator.

| Symbo             |     | Α     | A1   | A2    | b    | D     | E     | E1    | е           | h    | L    | L1          | L2          | θ          | θ1              |

|-------------------|-----|-------|------|-------|------|-------|-------|-------|-------------|------|------|-------------|-------------|------------|-----------------|

|                   | MIN | 1.35* | 0.10 | 1.25  | 0.31 | 4.80* | 5.80* | 3.80* |             | 0.25 | 0.40 |             |             | <b>0</b> 0 | 5 <sup>0</sup>  |

| Dimension<br>(mm) | NOM | -     | -    | -     | -    | 4.90  | 6.00  | 3.90  | 1.27<br>BSC | -    | -    | 1.04<br>REF | 0.25<br>BSC | -          | -               |

| ()                | MAX | 1.75  | 0.25 | 1.65* | 0.51 | 5.00* | 6.20* | 4.00* |             | 0.50 | 1.27 |             |             | <b>8</b> 0 | 15 <sup>0</sup> |

JEDEC Registration MS-012, Variation AA, Issue E, Sept. 2005.

\* This dimension is not specified in the JEDEC drawing.

Drawings are not to scale.

Supertex Doc. #: DSPD-8SOLGTG, Version 1041309.

**LR12**

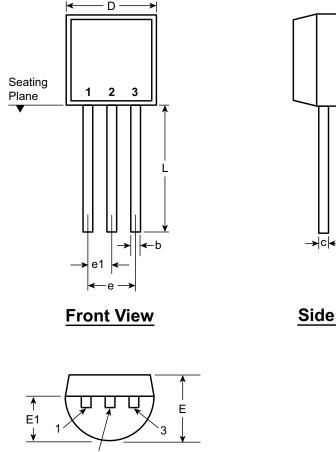

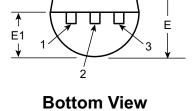

# 3-Lead TO-92 Package Outline (N3)

Side View

| Symb                   | lool | Α    | b     | С     | D    | E    | E1   | e    | e1   | L     |

|------------------------|------|------|-------|-------|------|------|------|------|------|-------|

|                        | MIN  | .170 | .014† | .014† | .175 | .125 | .080 | .095 | .045 | .500  |

| Dimensions<br>(inches) | NOM  | -    | -     | -     | -    | -    | -    | -    | -    | -     |

| (incres)               | MAX  | .210 | .022† | .022† | .205 | .165 | .105 | .105 | .055 | .610* |

JEDEC Registration TO-92.

\* This dimension is not specified in the JEDEC drawing.

† This dimension differs from the JEDEC drawing.

Drawings not to scale.

Supertex Doc.#: DSPD-3TO92N3, Version E041009.

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to http://www.supertex.com/packaging.html.)

Supertex inc. does not recommend the use of its products in life support applications, and will not knowingly sell them for use in such applications unless it receives an adequate "product liability indemnification insurance agreement." **Supertex inc.** does not assume responsibility for use of devices described, and limits its liability to the replacement of the devices determined defective due to workmanship. No responsibility is assumed for possible omissions and inaccuracies. Circuitry and specifications are subject to change without notice. For the latest product specifications refer to the **Supertex inc.** (website: http://www.supertex.com)

©2013 Supertex inc. All rights reserved. Unauthorized use or reproduction is prohibited.