# **ADC1038**

ADC1038 10-Bit Serial I/O A/D Converter with Analog Multiplexer and Track/Hold Function

Literature Number: SNAS063

June 1999

# **ADC1038**

# 10-Bit Serial I/O A/D Converter with Analog Multiplexer and Track/Hold Function

# **General Description**

The ADC1038 is a 10-bit successive approximation A/D converters with serial I/O. The serial input controls a single-ended analog multiplexer that selects one of 8 input channels. The serial output data can be configured into a left- or right-justified format.

An input track/hold is implemented by a capacitive reference ladder and sampled-data comparator. This allows the analog input to vary during the A/D conversion cycle.

Separate serial I/O and conversion clock inputs are provided to facilitate the interface to various microprocessors.

# **Applications**

- Engine control

- Process control

- Instrumentation

- Test equipment

# **Features**

- Serial I/O ( MICROWIRE™ compatible)

- Separate asynchronous converter clock and serial data I/O clock

- Analog input track/hold function

- Ratiometric or absolute voltage referencing

- No zero or full scale adjustment required

- 0V to 5V analog input range with single 5V power supply

- TTL/MOS input/output compatible

- No missing codes

# **Key Specifications**

| ■ Resolution                                         | 10 bit        |

|------------------------------------------------------|---------------|

| ■ Total unadjusted error                             | ±1 LSB (max)  |

| ■ Single supply                                      | 5V ±5%        |

| ■ Power dissipation                                  | 20 mW (max)   |

| ■ Max. conversion time (f <sub>C</sub> = 3 MHz)      | 13.7 µs (max) |

| ■ Serial data exchange time (f <sub>S</sub> = 1 MHz) | 10 µs (max)   |

# **Connection Diagrams**

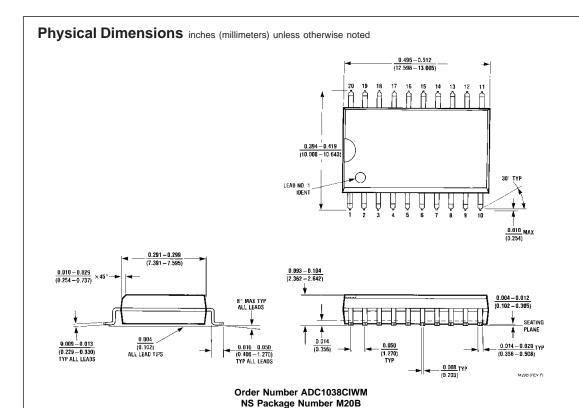

### SO Package

Top View ADC1038 In NS Package M20B

# **Ordering Information**

| Industrial −40°C ≤ T <sub>A</sub> ≤ +85 | °C Package |

|-----------------------------------------|------------|

| ADC1038CIWM                             | M20B       |

TRI-STATE® is a registered trademark of National Semiconductor Corporation. MICROWIRE $^{\text{TM}}$  is a trademark of National Semiconductor Corporation.

# Absolute Maximum Ratings (Notes 1, 3)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

Supply Voltage ( $V_{CC}$ ) 6.5V Voltage at Inputs and Outputs -0.3V to  $V_{CC}$  + 0.3V Input Current at Any Pin (Note 4) ±5 mA Package Input Current (Note 4) ±20 mA

Package Dissipation

at  $T_A = 25^{\circ}C$  (Note 5) 500 mW ESD Susceptability (Note 6) 2000V

Soldering Information

SO Package (Note 7):

Vapor Phase (60 sec.)

215°C

Infrared (15 sec.)

220°C

Storage Temperature

-65°C to +150°C

# Operating Ratings (Notes 2, 3)

$\begin{array}{ll} \text{Temperature Range} & T_{\text{MIN}} \leq T_{\text{A}} \leq T_{\text{MAX}} \\ \text{ADC1038CIWM} & -40^{\circ}\text{C} \leq T_{\text{A}} \leq +85^{\circ}\text{C} \\ \text{Supply Voltage (V}_{\text{CC}}) & 4.75 \text{ V}_{\text{DC}} \text{ to 5.25 V}_{\text{DC}} \\ \end{array}$

Reference Voltage

$(V_{REF} = V_{REF}^{+} - V_{REF}^{-})$  2.0  $V_{DC}$  to  $V_{CC} + 0.05V$

# **Electrical Characteristics**

The following specifications apply for  $V_{CC}$  = +5.0V,  $V_{REF}$  = +4.6V,  $f_S$  = 700 kHz, and  $f_C$  = 3 MHz unless otherwise specified. **Boldface limits apply for T<sub>A</sub>** = T<sub>J</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>; all other limits T<sub>A</sub> = T<sub>J</sub> = 25°C.

| Symbol              | Parar                                 | neter            | Conditions                                                      | Typical  | Limit                    | Units      |

|---------------------|---------------------------------------|------------------|-----------------------------------------------------------------|----------|--------------------------|------------|

|                     |                                       |                  |                                                                 | (Note 8) | (Note 9)                 | (Limits)   |

| CONVER              | RTER AND MULTIPL                      | EXER CHARACTER   | RISTICS                                                         |          |                          |            |

|                     | Total Unadjusted                      | CIN, CIWM, CMJ   | (Note 10)                                                       |          | ±1                       | LSB (max)  |

|                     | Error                                 |                  |                                                                 |          |                          |            |

|                     | Differential Linearity                | i                |                                                                 |          | 10                       | Bits (min) |

| R <sub>REF</sub>    | Reference Input Resistance            |                  |                                                                 | 8        |                          | kΩ         |

|                     |                                       |                  |                                                                 |          | 5                        | kΩ (min)   |

|                     |                                       |                  |                                                                 |          | 11                       | kΩ (max)   |

| $V_{REF}$           | Reference Voltage                     |                  |                                                                 |          | (V <sub>CC</sub> + 0.05) | V (max)    |

| V <sub>IN</sub>     | Analog Input Voltage                  |                  | (Note 11)                                                       |          | (V <sub>CC</sub> + 0.05) | V (max)    |

|                     |                                       |                  |                                                                 |          | (GND - 0.05)             | V (min)    |

|                     | On Channel Leakag                     | je Current       | On Channel = 5 V <sub>DC</sub> ,                                | 5.0      | 200                      | nA (max)   |

|                     |                                       |                  | Off Channel = 0 V <sub>DC</sub>                                 |          | 500                      | nA (max)   |

|                     | (Note 12)                             |                  | On Channel = 0 V <sub>DC</sub> ,                                | 5.0      | -200                     | nA (max)   |

|                     | Off Channel Leakage Current (Note 12) |                  | Off Channel = 5 V <sub>DC</sub>                                 |          | -500                     | nA (max)   |

|                     |                                       |                  | On Channel = 5 V <sub>DC</sub> ,                                | 5.0      | -200                     | nA (max)   |

|                     |                                       |                  | Off Channel = 0 V <sub>DC</sub>                                 |          | -500                     | nA (max)   |

|                     |                                       |                  | On Channel = 0 V <sub>DC</sub> ,                                | 5.0      | 200                      | nA (max)   |

|                     |                                       |                  | Off Channel = 5 V <sub>DC</sub>                                 |          | 500                      | nA (max)   |

|                     | Power Supply                          | Zero Error       | $4.75 \text{ V}_{DC} \le \text{V}_{CC} \le 5.25 \text{ V}_{DC}$ |          | ±1/4                     | LSB (max)  |

|                     | Sensitivity                           | Full Scale Error |                                                                 |          | ±1/4                     | LSB (max)  |

| DIGITAL             | AND DC CHARACT                        | ERISTICS         |                                                                 |          |                          |            |

| $V_{IN(1)}$         | Logical "1" Input Vo                  | ltage            | $V_{CC} = 5.25 V_{DC}$                                          |          | 2.0                      | V (min)    |

| $V_{IN(0)}$         | Logical "0" Input Vo                  | ltage            | $V_{CC} = 4.75 V_{DC}$                                          |          | 0.8                      | V (max)    |

| I <sub>IN(1)</sub>  | Logical "1" Input Cu                  | rrent            | $V_{IN} = 5.0 V_{DC}$                                           | 0.005    | 2.5                      | μA (max)   |

| I <sub>IN(0)</sub>  | Logical "0" Input Cu                  | rrent            | $V_{IN} = 0 V_{DC}$                                             | -0.005   | -2.5                     | μA (max)   |

| $V_{OUT(1)}$        | Logical "1" Output V                  | /oltage          | $V_{CC} = 4.75 V_{DC}$                                          |          |                          |            |

|                     |                                       |                  | I <sub>OUT</sub> = -360 μA                                      |          | 2.4                      | V (min)    |

|                     |                                       |                  | I <sub>OUT</sub> = -10 μA                                       |          | 4.5                      | V (min)    |

| V <sub>OUT(0)</sub> | Logical "0" Output \                  | /oltage          | $V_{CC} = 4.75 V_{DC}$                                          |          | 0.4                      | V (max)    |

|                     |                                       |                  | I <sub>OUT</sub> = 1.6 mA                                       |          |                          |            |

| I <sub>OUT</sub>    | TRI-STATE Output Current              |                  | V <sub>OUT</sub> = 0V                                           | -0.01    | -3                       | μA (max)   |

|                     |                                       |                  | V <sub>OUT</sub> = 5V                                           | 0.01     | 3                        | μA (max)   |

| I <sub>SOURCE</sub> | Output Source Curr                    | ent              | V <sub>OUT</sub> = 0V                                           | -14      | -6.5                     | mA (min)   |

| I <sub>SINK</sub>   | Output Sink Current                   | t                | V <sub>OUT</sub> = V <sub>CC</sub>                              | 16       | 8.0                      | mA (min)   |

| I <sub>cc</sub>     | Supply Current                        |                  | CS = HIGH, V <sub>RFF</sub> Open                                | 1.5      | 3                        | mA (max)   |

# **Electrical Characteristics** (Continued)

The following specifications apply for  $V_{CC}$  = +5.0V,  $V_{REF}$  = +4.6V,  $f_S$  = 700 kHz, and  $f_C$  = 3 MHz unless otherwise specified. Boldface limits apply for  $T_A$  =  $T_J$  =  $T_{MIN}$  to  $T_{MAX}$ ; all other limits  $T_A$  =  $T_J$  = 25°C.

| Symbol                            | Parameter                                                               |                               | Conditions                                       |                                                  | Typical  | Limit                   | Units     |  |

|-----------------------------------|-------------------------------------------------------------------------|-------------------------------|--------------------------------------------------|--------------------------------------------------|----------|-------------------------|-----------|--|

|                                   |                                                                         |                               |                                                  |                                                  | (Note 8) | (Note 9)                | (Limits)  |  |

| AC CHA                            | RACTERISTICS                                                            |                               |                                                  |                                                  |          |                         | •         |  |

| f <sub>C</sub>                    | Conversion Clock (C <sub>CLK</sub> )                                    |                               |                                                  |                                                  | 0.7      |                         | MHz (min) |  |

|                                   | Frequency                                                               |                               |                                                  |                                                  | 4.0      | 3.0                     | MHz (max) |  |

| f <sub>S</sub>                    | Serial Data Clock (S                                                    | S <sub>CLK</sub> )            | $f_C = 3 \text{ MHz}, F$                         | R/L = "0"                                        | 183      |                         | kHz (min) |  |

|                                   | Frequency (Note 13                                                      | )                             | $f_C = 3 \text{ MHz}, F$                         |                                                  | 622      |                         | kHz (min) |  |

|                                   |                                                                         |                               | $f_C = 3 \text{ MHz}, F$                         | $R/\overline{L}$ = "0" or $R/\overline{L}$ = "1" | 2        | 1.0                     | MHz (max) |  |

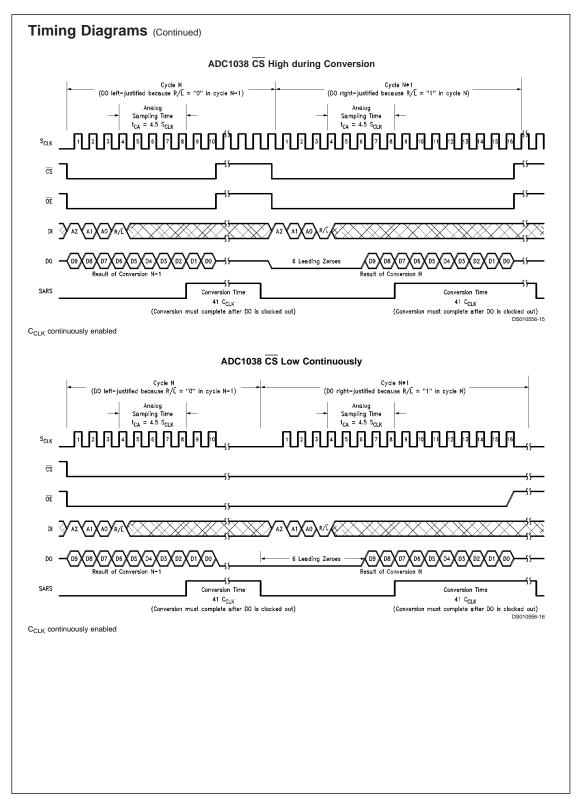

| T <sub>C</sub>                    | Conversion Time                                                         |                               | Not Including                                    | MUX Addressing and                               |          | 41 (1/f <sub>C</sub> )  | (max)     |  |

|                                   |                                                                         |                               | Analog Input Sampling Times                      |                                                  |          | + 200 ns                |           |  |

| t <sub>CA</sub>                   | Analog Sampling Time                                                    |                               | After Address                                    | is Latched, CS = Low                             |          | 4.5 (1/f <sub>S</sub> ) | (max)     |  |

|                                   |                                                                         |                               |                                                  |                                                  |          | + 200 ns                |           |  |

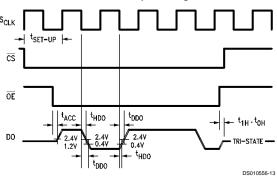

| t <sub>ACC</sub>                  | Access Time Delay from $\overline{\text{CS}}$ or $\overline{\text{OE}}$ |                               | OE = "0"                                         |                                                  | 100      | 200                     | ns (max)  |  |

|                                   | Falling Edge to DO Data Valid                                           |                               |                                                  |                                                  |          |                         |           |  |

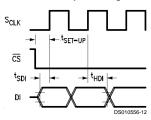

| t <sub>SET-UP</sub>               | Set-up Time of CS Falling                                               |                               |                                                  |                                                  | 75       | 150                     | ns (min)  |  |

|                                   | Edge to S <sub>CLK</sub> Rising                                         | g Edge                        |                                                  |                                                  |          |                         |           |  |

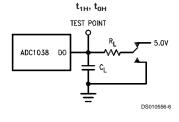

| t <sub>1H</sub> , t <sub>OH</sub> | Delay from OE or CS Rising                                              |                               | $R_L = 3 k\Omega, C_I$                           | = 100 pF                                         | 100      | 120                     | ns (max)  |  |

|                                   | Edge to DO TRI-ST                                                       | ATE                           |                                                  |                                                  |          |                         |           |  |

| t <sub>HDI</sub>                  | DI Hold Time from S <sub>CLK</sub> Rising Edge                          |                               |                                                  |                                                  | 0        | 50                      | ns (min)  |  |

| t <sub>SDI</sub>                  | DI Set-up Time to S <sub>CLK</sub> Rising Edge                          |                               |                                                  |                                                  | 50       | 100                     | ns (min)  |  |

| $t_{HDO}$                         | DO Hold Time from                                                       | S <sub>CLK</sub> Falling Edge | $R_L = 30 \text{ k}\Omega, C$                    | C <sub>L</sub> = 100 pF                          | 70       | 10                      | ns (min)  |  |

| $t_{DDO}$                         | Delay from S <sub>CLK</sub> Fa                                          | lling                         | $R_L = 30 \text{ k}\Omega, C_L = 100 \text{ pF}$ |                                                  | 150      | 250                     | ns (max)  |  |

|                                   | Edge to DO Data Valid                                                   |                               |                                                  |                                                  |          |                         |           |  |

| t <sub>RDO</sub>                  | DO Rise Time                                                            |                               | $R_L = 30 \text{ k}\Omega$ ,                     | TRI-STATE to High                                | 35       | 75                      | ns (max)  |  |

|                                   |                                                                         |                               | C <sub>L</sub> = 100 pF                          | Low to High                                      | 75       | 150                     | ns (max)  |  |

| t <sub>FDO</sub>                  | DO Fall Time                                                            |                               | $R_L = 30 \text{ k}\Omega$                       | TRI-STATE to Low                                 | 35       | 75                      | ns (max)  |  |

|                                   |                                                                         |                               | C <sub>L</sub> = 100 pF                          | High to Low                                      | 75       | 150                     | ns (max)  |  |

| C <sub>IN</sub>                   | Input Capacitance                                                       |                               | Analog Inputs                                    | (CH0-CH7)                                        | 50       |                         | pF        |  |

|                                   |                                                                         |                               | All Other Inputs                                 |                                                  | 7.5      |                         | pF        |  |

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur.

Note 2: Operating Ratings indicate conditions for which the device is functional, but do not guarantee specific performance limits. For guaranteed specifications and test conditions, see the Electrical Characteristics. The guaranteed specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions.

Note 3: All voltages are measured with respect to AGND and DGND, unless otherwise specified.

Note 4: When the input voltage  $(V_{IN})$  at any pin exceeds the power supplies  $(V_{IN} < DGND, \text{ or } V_{IN} > V_{CC})$  the current at that pin should be limited to 5 mA. The 20 mA maximum package input current rating limits the number of pins that can safely exceed the power supplies with an input current of 5 mA to four pins.

Note 5: The maximum power dissipation must be derated at elevated temperatures and is dictated by  $T_{Jmax}$ ,  $\theta_{JA}$  and the ambient temperature,  $T_A$ . The maximum allowable power dissipation at any temperature is  $P_D = (T_{Jmax} - T_A)/\theta_{JA}$  or the number given in the Absolute Maximum Ratings, whichever is lower. For this device,  $T_{Jmax} = 125$ °C. The typical thermal resistance  $(\theta_{JA})$  when board mounted is 64°C/W.

Note 6: Human body model, 100 pF capacitor discharged through a 1.5 k $\Omega$  resistor.

Note 7: See AN450 "Surface Mounting Methods and Their Effect on Product Reliability" or Linear Databook section "Surface Mount" for other methods of soldering surface mount devices.

Note 8: Typicals are at  $T_J$  = 25°C and represent most likely parametric norm.

Note 9: Limits are guaranteed to National's AOQL (Average Outgoing Quality Level).

Note 10: Total unadjusted error includes offset, full-scale, linearity, multiplexer, and hold step errors.

Note 11: Two on-chip diodes are tied to each analog input. They will forward-conduct for analog input voltages one diode drop below ground or one diode drop greater than  $V_{CC}$  supply. Be careful during testing at low  $V_{CC}$  levels (4.5V), as high level analog inputs (5V) can cause an input diode to conduct, especially at elevated temperatures, which will cause errors for analog inputs near full-scale. The spec allows 50 mV forward bias of either diode; this means that as long as the analog  $V_{IN}$  does not exceed the supply voltage by more than 50 mV, the output code will be correct. Exceeding this range on an unselected channel will corrupt the reading of a selected channel. To achieve an absolute 0  $V_{DC}$  to 5  $V_{DC}$  input voltage range will therefore require a minimum supply voltage of 4.950  $V_{DC}$  over temperature variations, initial tolerance and loading.

Note 12: Channel leakage current is measured after the channel selection.

Note 13: In order to synchronize the serial data exchange properly, SARS needs to go low after completion of the serial I/O data exchange. If this does not occur the output shift register will be reset and the correct output data lost. The minimum limit for S<sub>CLK</sub> will depend on C<sub>CLK</sub> frequency and whether right-justified or left-justified, and can be determined by the following equations:

$f_S > (8.5/41)$  ( $f_C$ ) with right-justification (R/ $\overline{L}$  = "1") and  $f_S > (2.5/41)$  ( $f_C$ ) with left-justification (R/ $\overline{L}$  = "0").

# **Typical Performance Characteristics**

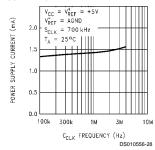

# Power Supply Current ( $I_{CC}$ ) vs $C_{CLK}$

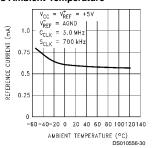

# Power Supply Current (I<sub>CC</sub>) vs Ambient Temperature

# Reference Current (I<sub>REF</sub>) vs Ambient Temperature

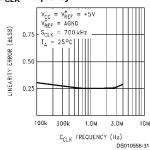

# Linearity Error vs C<sub>CLK</sub> Frequency

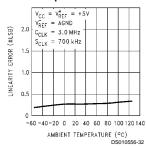

### Linearity Error vs Ambient Temperature

# Linearity Error vs Reference Voltage

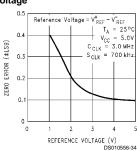

## Zero Error vs Reference Voltage

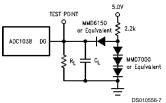

# **Test Circuits**

# DO except "TRI-STATE"

# Leakage Current

# **Timing Diagrams**

# DO High to Low State

# DO Low to High State

# DO "TRI-STATE" Rise and Fall Times

DS010556-8

# DI Data Input Timing

# DO Data Output Timing

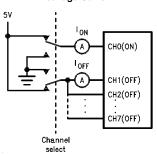

# Multiplexer Address/Channel Assignment Table

|    | MUX Address | Analog |          |

|----|-------------|--------|----------|

| A2 | A1          | A0     | Channel  |

|    |             |        | Selected |

| 0  | 0           | 0      | CH0      |

| 0  | 0           | 1      | CH1      |

| 0  | 1           | 0      | CH2      |

| 0  | 1           | 1      | CH3      |

| ı     | Analog |    |          |

|-------|--------|----|----------|

| A2 A1 |        | A0 | Channel  |

|       |        |    | Selected |

| 1     | 0      | 0  | CH4      |

| 1     | 0      | 1  | CH5      |

| 1     | 1      | 0  | CH6      |

| 1     | 1      | 1  | CH7      |

# 1.0 Pin Descriptions

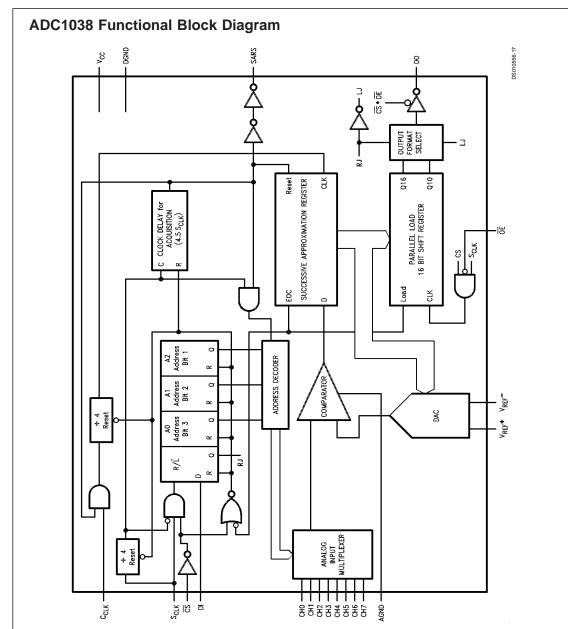

C<sub>CLK</sub> The clock applied to this input controls the successive approximation conversion time interval.

The clock frequency applied to this input can be between 700 kHz and 4 MHz.

S<sub>CLK</sub> The serial data clock input. Th

The serial data clock input. The clock applied to this input controls the rate at which the serial data exchange occurs and the analog sampling time available to acquire an analog input voltage. The rising edge loads the information on the DI pin into the multiplexer address shift reg-

ister (address register). This address controls which channel of the analog input multiplexer (MUX) is selected.

The falling edge shifts the data resulting from the previous A/D conversion out on DO.  $\overline{\text{CS}}$  and  $\overline{\text{OE}}$  enable or disable the above functions.

The serial data input pin. The data applied to this pin is shifted by  $S_{\rm CLK}$  into the multiplexer address register. The first 3 bits of data (A0–A2) are the MUX channel address (see the Multiplexer Address/Channel Assignment tables). The fourth bit (R/ $\bar{\rm L}$ ) determines the data format of the conversion result in the conversion to be

# 1.0 Pin Descriptions (Continued)

started. When R/L is low the output data format is left-justified; when high it is right-justified. When right-justified, six leading "0"s are output on DO before the MSB information; thus the complete conversion result is shifted out in 16 clock periods.

DO

The data output pin. The A/D conversion result (D0–D9) is output on this pin. This result can be left- or right-justified depending on the value of R/L bit shifted in on DI.

SARS This pin is an output and indicates the status of the internal successive approximation register (SAR). When high, it signals that the A/D conversion is in progress. This pin is set high after the analog input sampling time (t<sub>CA</sub>) and remains high for 41 C<sub>CLK</sub> periods. When SARS goes low, the output shift register has been loaded with the conversion result and another A/D conversion sequence can be started.

The chip select pin. When a low is applied to this pin, the rising edge of S<sub>CLK</sub> shifts the data on DI into the address register.

OE The output enable pin. When OE and CS are both low the falling edge of S<sub>CLK</sub> shifts out the previous A/D conversion data on the DO pin.

CH0-CH7 The analog inputs of the MUX. A channel input is selected by the address information at the DI pin, which is loaded on the rising edge of S<sub>CLK</sub> into the address register.

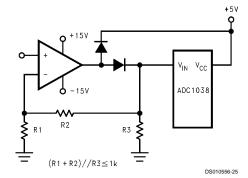

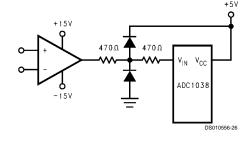

Source impedances (R<sub>S</sub>) driving these inputs should be kept below 1 k $\Omega$ . If R<sub>S</sub> is greater than 1 k $\Omega$ , the sampled data comparator will not have enough time to acquire the correct value of the applied input voltage.

The voltage applied to these inputs should not exceed  $V_{\rm CC}$  or go below DGND or AGND by more than 50 mV. Exceeding this range on an unselected channel will corrupt the reading of a selected channel.

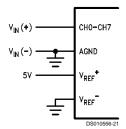

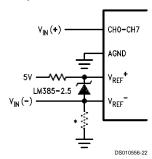

$V_{REF}^{+}$  The positive analog voltage reference for the analog inputs. In order to maintain accuracy the voltage range of  $V_{REF}$  ( $V_{REF} = V_{REF}^{+} - V_{REF}^{-}$ ) is 2.5  $V_{DC}$  to 5.0  $V_{DC}$  and the voltage at  $V_{REF}^{+}$  cannot exceed  $V_{CC}$  + 50 mV.

$V_{REF}^-$  The negative voltage reference for the analog inputs. In order to maintain accuracy the voltage at this pin must not go below DGND and AGND by more than 50 mV or exceed 40% of  $V_{CC}$  (for  $V_{CC} = 5V$ ,  $V_{REF}^-$  (max) = 2V).

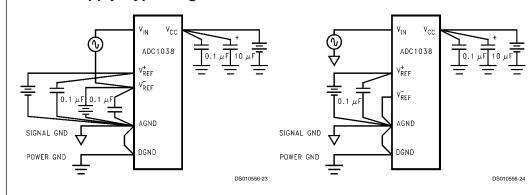

$V_{CC}$  The power supply pin. The operating voltage range of  $V_{CC}$  is 4.75  $V_{DC}$  to 5.25  $V_{DC}$ .  $V_{CC}$  should be bypassed with 10  $\mu F$  and 0.1  $\mu F$  capacitors to digital ground for proper operation of the A/D converter.

DGND,

AGND

The digital and analog ground pins. In order to maintain accuracy the voltage difference between these two pins must not exceed 300 mV.

GND The digital and analog ground pin for the ADC1031.

# 2.0 Functional Description

### 2.1 DIGITAL INTERFACE

The ADC1038 implement its serial interface via seven digital control lines. There are two clock inputs for the ADC1038. The S<sub>CLK</sub> controls the rate at which the serial data exchange occurs and the duration of the analog sampling time window. The C<sub>CLK</sub> controls the conversion time and must be continuously enabled. A low on  $\overline{\text{CS}}$  enables the rising edge of  $\text{S}_{\text{CLK}}$ to shift in the serial multiplexer addressing data on the DI pin. The first three bits of this data select the analog input channel (see the Channel Addressing Tables). The following bit, R/L , selects the output data format (right-justified or left-justified) for the conversion to be started. With CS and OE low the DO pin is active (out of TRI-STATE®) and the falling edge of S<sub>CLK</sub> shifts out the data from the previous analog conversion. When the first conversion is started the data shifted out on DO is erroneous as it depends on the state of the Parallel Load 16-Bit Shift Register on power up, which is unpredictable

The ADC1031 implements its serial interface with only four control pins since it has only one analog input and comes in an eight pin mini-dip package. The  $S_{\rm CLK},\,C_{\rm CLK},\,\overline{\rm CS}$  and  $\overline{\rm DO}$  pins are available for the serial interface. The output data format cannot be selected and defaults to a left-justified format. The state of DO is controlled by  $\overline{\rm CS}$  only.

### 2.2 OUTPUT DATA FORMAT

When  $R/\overline{L}$  is low the output data format is left-justified; when high it is right-justified. When right-justified, six leading "0"s are output on DO before the MSB, and the complete conversion result is shifted out in 16 clock periods.

# 2.3 CS HIGH DURING CONVERSION

With a continuous  $S_{CLK}$  input,  $\overline{CS}$  must be used to synchronize the serial data exchange. A valid  $\overline{CS}$  is recognized if it occurs at least 100 ns ( $t_{SET-UP}$ ) before the rising edge of  $S_{CLK}$ , thus causing data to be input on DI. If this does not occur there will be an uncertainty as to which  $S_{CLK}$  rising edge will clock in the first bit of data.  $\overline{CS}$  must remain low during the complete I/O exchange. Also,  $\overline{OE}$  needs to be low if data from the previous conversion needs to be accessed.

### 2.3.1 CS LOW CONTINUOUSLY

Another way to accomplish synchronous serial communication is to tie  $\overline{CS}$  low continuously and use SARS and  $S_{\rm CLK}$  to synchronize the serial data exchange.  $S_{\rm CLK}$  can be disabled low during the conversion time and enabled after SARS goes low. With  $\overline{CS}$  low during the conversion time a zero will remain on DO until the conversion is completed. Once the conversion is complete, the falling edge of SARS will shift out on DO the MSB before  $S_{\rm CLK}$  is enabled. This MSB would be a leading zero if right-justified or D9 if left-justified. The rest of the data will be shifted out once  $S_{\rm CLK}$  is enabled as discussed previously. If  $\overline{CS}$  goes high during the conversion seult is not affected so long as  $\overline{CS}$  remains high until the end of the conversion.

# 2.4 TYING $\mathbf{S}_{\text{CLK}}$ and $\mathbf{C}_{\text{CLK}}$ TOGETHER

$S_{\rm CLK}$  and  $C_{\rm CLK}$  can be tied together. The total conversion time will increase because the maximum clock frequency is now 1 MHz. The timing diagrams and the serial I/O exchange time (10  $S_{\rm CLK}$  cycles) remain the same, but the conversion time ( $T_{\rm C}$  = 41  $C_{\rm CLK}$  cycles) lengthens from a minimum of 14  $\mu s$  to a minimum of 41  $\mu s$ . In the case where  $\overline{\rm CS}$

# 2.0 Functional Description (Continued)

is low continuously, since the applied clock cannot be disabled, SARS must be used to synchronize the data output on DO and initiate a new conversion. The falling edge of SARS sends the MSB information out on DO. The next rising edge of the clock shifts in MUX address bit A2 on DI. The following clock falling edge will clock the next data bit of information out on DO. A conversion will be started after MUX addressing information has been loaded in (3 more clocks) and the analog sampling time (4.5 clocks) has elapsed.

# 3.0 Analog Considerations

### 3.1 THE INPUT SAMPLE AND HOLD

The sample/hold capacitor is implemented in its capacitive ladder structure. After the channel address is received, the ladder is switched to sample the proper analog input. This sampling mode is maintained for 4.5  $S_{\rm CLK}$  cycles after the multiplexer addressing information is loaded in. The sampling of the analog input starts on  $S_{\rm CLK}$ 's 4th rising edge.

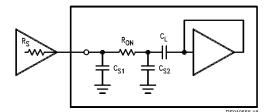

FIGURE 1. Analog Input Model

An acquisition window of 4.5  $S_{\rm CLK}$  cycles is available to allow the ladder capacitance to settle to the analog input voltage. Any change in the analog voltage before or after the acquisition window will not effect the A/D conversion result.

In the most simple case, the ladder's acquisition time is determined by the  $R_{on}~(9~k\Omega)$  of the multiplexer switches, the  $C_{S1}~(3.5~pF)$  and the total ladder  $(C_{L})$  and stray  $(C_{S2})$  capacitance (48 pF). For large source resistance the analog input can be modeled as an RC network as shown in Figure~1. The values shown yield an acquisition time of about 3  $\mu s$  for 10 bit accuracy with a zero to a full scale change in the reading. External source resistance and capacitance will lengthen the acquisition time and should be accounted for.

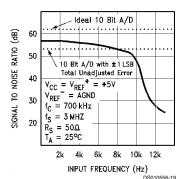

The curve "Signal to Noise Ratio vs Output Frequency" (Figure 2) gives an indication of the usable bandwidth. The signal to noise ratio of an ideal A/D is the ratio of the RMS value

of the full scale input signal amplitude to the value of the total error amplitude (including noise) caused by the transfer function of the A/D. An ideal 10 bit A/D converter with a total unadjusted error of 0 LSB would have a signal to noise ratio of about 62 dB, which can be derived from the equation:

$$S/N = 6.02(N) + 1.76$$

where S/N is in dB and N is the number of bits. Figure 2 shows the signal to noise ratio vs. input frequency of a typical ADC1038 with  $\frac{1}{2}$  LSB total unadjusted error. The dotted lines show signal-to-noise ratios for an ideal (noiseless) 10 bit A/D with 0 LSB error and an A/D with a 1 LSB error.

The sample-and-hold error specifications are included in the error and timing specifications of the A/D. The hold step and gain error sample/hold specs are taken into account in the total unadjusted error specification, while the hold settling time is included in the A/D's maximum conversion time specification. The hold droop rate can be thought of as being zero since an unlimited amount of time can pass between a conversion and the reading of data. However, once the data is read it is lost and another conversion is started.

### 3.2 INPUT FILTERING

Due to the sampling nature of the analog input, transients will appear on the input pins. They are caused by the ladder capacitance and internal stray capacitance charging current flowing into  $V_{\rm IN}$ . These transients will not degrade the A/D's performance if they settle out within the sampling window. This will occur if external source resistance is kept to a minimum

FIGURE 2. ADC1038 Signal to Noise Ratio vs Input Frequency

# 3.0 Analog Considerations (Continued)

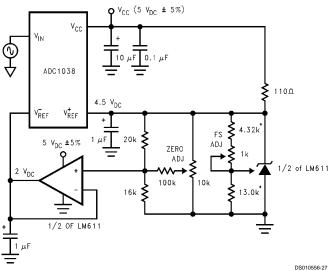

### External Reference 2.5V Full Scale

# V<sub>IN</sub>(+) CH0-CH7 V<sub>IN</sub>(-) AGND V<sub>REF</sub><sup>+</sup> V<sub>REF</sub> DS010556-20

# Power Supply as Reference

### Input Not Referred to GND

Note 14: \*Current path must still exist from V<sub>IN</sub>(-) to ground

# FIGURE 3. Analog Input Options

# 3.3 REFERENCE AND INPUT

The two V<sub>REF</sub> inputs are fully differential and define the zero to full-scale input range of the A to D converter. This allows the designer to easily vary the span of the analog input since this range will be equivalent to the voltage difference between V<sub>REF</sub>+ and V<sub>REF</sub>-. By reducing V<sub>REF</sub> (V<sub>REF</sub> = V<sub>REF</sub>+ – V<sub>REF</sub>-) to less than 5V, the sensitivity of the converter can be increased (i.e., if V<sub>REF</sub> = 2V then 1 LSB = 1.95 mV). The input/reference arrangement also facilitates ratiometric op-

eration and in many cases the chip power supply can be used for transducer power as well as the  $\rm V_{\rm REF}$  source.

This reference flexibility lets the input span not only be varied but also offset from zero. The voltage at  $V_{\rm REF}-$  sets the input level which produces a digital output of all zeros. Though  $V_{\rm IN}$  is not itself differential, the reference design allows nearly differential-input capability for many measurement applications.  $Figure\ 3$  shows some of the configurations that are possible.

# **Power Supply Bypassing**

# **Protecting the Analog Inputs**

Diodes are IN914

# Zero-Shift and Span-Adjust (2V $\leq$ $V_{\text{IN}} \leq$ 4.5V)

\*1% resistors

# LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

Tel: 1-800-272-9959 Fax: 1-800-737-7018 Email: support@nsc.com

www.national.com

# National Semiconductor

Fax: 449 (0) 1 80-530 85 86

Email: europe.support@nsc.com

Deutsch Tel: 449 (0) 1 80-530 85 85

English Tel: 449 (0) 1 80-532 78 32

Français Tel: 449 (0) 1 80-532 93 58

Italiano Tel: 449 (0) 1 80-534 16 80

National Semiconductor Asia Pacific Customer Response Group Tel: 65-2544466 Fax: 65-2504466

Email: sea.support@nsc.com

National Semiconductor Japan Ltd. Tel: 81-3-5639-7560 Fax: 81-3-5639-7507

### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

# Products Applications

Audio www.ti.com/audio Communications and Telecom www.ti.com/communications **Amplifiers** amplifier.ti.com Computers and Peripherals www.ti.com/computers dataconverter.ti.com Consumer Electronics www.ti.com/consumer-apps **Data Converters DLP® Products** www.dlp.com **Energy and Lighting** www.ti.com/energy DSP dsp.ti.com Industrial www.ti.com/industrial Clocks and Timers www.ti.com/clocks Medical www.ti.com/medical

Interface

interface.ti.com

Security

www.ti.com/security

Logic

logic.ti.com

Space, Avionics and Defense

www.ti.com/space-avionics-defense

Power Mgmt power.ti.com Transportation and Automotive www.ti.com/automotive

Microcontrollers microcontroller.ti.com Video and Imaging www.ti.com/video

RFID <u>www.ti-rfid.com</u>

OMAP Mobile Processors www.ti.com/omap

Wireless Connectivity www.ti.com/wirelessconnectivity

TI E2E Community Home Page e2e.ti.com

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2011, Texas Instruments Incorporated