# PCI Express Gen II Compliant, 8-Differential Channel Switch with 8:4 Mux/DeMux Option

#### **Features**

• 8 Differential Channel SPST switch with Mux/DeMux option

• PCI Express Gen II performance

• Low Bit-to-Bit Skew: 10ps (between +/- signals)

• Low Crosstalk: -15dB @ 3.0 GHz

• Low Off Isolation: -26db @ 3.0 GHz

•  $V_{DD}$  Operating Range: +1.4V to +1.8V  $\pm 10\%$

• ESD Tolerance >2kV HBM

• Packaging (Pb-free & Green): 42-contact TQFN (ZH42)

### **Description**

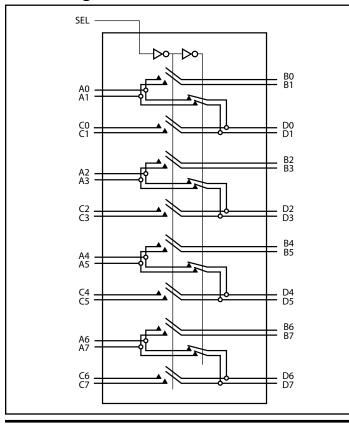

Pericom semiconductor's PI2PCIE2422 is an 8 to 4 channel differential multiplexer/demultiplexer featuring 8-channel pass-through. It supports two full PCI Express lanes at 5.0Gbps Gen II performance.

With the select control input low Port A connects to Port B, and Port C connects to port D for an 8-channel differential pass-though. When the select control input is high Port A connects to Port D, and Port B and Port C are in a high-impedance state. The mux/demux function is between Port A and Ports B or D as determined by the select input control.

### **Truth Table**

| Function               | SEL |

|------------------------|-----|

| Ax = Bx $Cx = Dx$      | L   |

| Ax = Dx $B = C = Hi-Z$ | Н   |

## **Block Diagram**

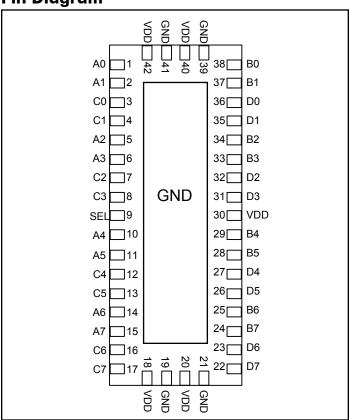

# Pin Diagram

14-0035 1 www.pericom.com 04/02/2014

# **Pin Description**

| Pin #              | Pin Name          | I/O | Description                                                                                      |  |

|--------------------|-------------------|-----|--------------------------------------------------------------------------------------------------|--|

| 1, 2               | A0, A1            | I/O | Signal I/O (typically a differential pair)                                                       |  |

| 3, 4               | C0, C1            | I/O | Signal I/O (typically a differential pair)                                                       |  |

| 5, 6               | A2, A3            | I/O | Signal I/O (typically a differential pair)                                                       |  |

| 7, 8               | C2, C3            | I/O | Signal I/O (typically a differential pair)                                                       |  |

| 10, 11             | A4, A5            | I/O | Signal I/O (typically a differential pair)                                                       |  |

| 12, 13             | C4, C5            | I/O | Signal I/O (typically a differential pair)                                                       |  |

| 14, 15             | A6, A7            | I/O | Signal I/O (typically a differential pair)                                                       |  |

| 16, 17             | C6, C7            | I/O | Signal I/O (typically a differential pair)                                                       |  |

| 22, 23             | D7, D6            | I/O | Signal I/O (typically a differential pair)                                                       |  |

| 24, 25             | B7, B6            | I/O | Signal I/O (typically a differential pair)                                                       |  |

| 26, 27             | D5, D4            | I/O | Signal I/O (typically a differential pair)                                                       |  |

| 28,29              | B5, B4            | I/O | Signal I/O (typically a differential pair)                                                       |  |

| 31, 32             | D3, D2            | I/O | Signal I/O (typically a differential pair)                                                       |  |

| 33, 34             | B3, B2            | I/O | Signal I/O (typically a differential pair)                                                       |  |

| 35, 36             | D1, D0            | I/O | Signal I/O (typically a differential pair)                                                       |  |

| 37, 38             | B1, B0            | I/O | Signal I/O (typically a differential pair)                                                       |  |

| 9                  | SEL               | I   | Operation mode Select                                                                            |  |

|                    |                   |     | (when SEL=0: $A \rightarrow B$ , $C \rightarrow D$ , when SEL=1: $A \rightarrow D$ , B & C=Hi-Z) |  |

| 18, 20, 30, 40, 42 | $V_{\mathrm{DD}}$ | Pwr | 1.8V positive supply voltage                                                                     |  |

| 19, 21, 39, 41     | GND               | Pwr | Power ground                                                                                     |  |

### **Maximum Ratings**

(Above which useful life may be impaired. For user guidelines, not tested.)

| Storage Temperature | 0.5V to +2.5V<br>0.5V to V <sub>DD</sub><br>120mA |

|---------------------|---------------------------------------------------|

| Power Dissipation   |                                                   |

| _                   |                                                   |

**Note:** Stresses greater than those listed under MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

### DC Electrical Characteristics for Switching over Operating Range

$(T_A = -40^{\circ}C \text{ to } +85^{\circ}C, V_{DD} = 1.4V \text{ to } 1.8V \pm 10\%)$

| Paramenter          | Description             | Test Conditions                               | Min                                                      | Typ <sup>(1)</sup> | Max                       | Units |

|---------------------|-------------------------|-----------------------------------------------|----------------------------------------------------------|--------------------|---------------------------|-------|

| $V_{IH}$            | Input HIGH Voltage      | Guaranteed HIGH level                         | 0.65 x V <sub>DD</sub>                                   |                    |                           |       |

| $v_{\mathrm{IL}}$   | Input LOW Voltage       | Guaranteed LOW level                          | -0.5                                                     |                    | 0.35 x<br>V <sub>DD</sub> | V     |

| V <sub>IK</sub>     | Clamp Diode Voltage     | $V_{DD} = Max., I_{IN} = -18mA$               | $_{\rm D} = {\rm Max., I_{\rm IN}} = -18{\rm mA}$ $-0.7$ |                    | -1.2                      |       |

| IIH                 | Input HIGH Current      | $V_{DD} = Max., V_{IN} = V_{DD}$              |                                                          |                    | ±5                        |       |

| IIL                 | Input LOW Current       | $V_{DD} = Max., V_{IN} = GND$                 |                                                          |                    | ±5                        | μΑ    |

| R <sub>ON</sub>     | On Resistance           | $V_{DD} = Min., V_{IN} = 1.3V, I_{IN} = 40mA$ |                                                          |                    | 10                        | Ohm   |

| C <sub>ON(AB)</sub> | Capacitance on A/B, C/D | $V_{IN} = 0, V_{DD} = 1.8V$                   |                                                          | 2.0                |                           | pF    |

#### Note:

### **Power Supply Characteristics**

| Parameters | Description                    | Test Conditions <sup>(1)</sup>                   | Min. | <b>Typ.</b> <sup>(2)</sup> | Max. | Units |

|------------|--------------------------------|--------------------------------------------------|------|----------------------------|------|-------|

| $I_{DD}$   | Quiescent Power Supply Current | $V_{DD} = Max., V_{IN} = GND \text{ or } V_{DD}$ |      |                            | 400  | μΑ    |

#### Notes:

- 1. For Max. or Min. conditions, use appropriate value specified under Electrical Characteristics for the applicable device type.

- 2. Typical values are at  $V_{DD} = 1.8V$ ,  $T_A = 25^{\circ}C$  ambient and maximum loading.

# **Dynamic Electrical Characteristics Over the Operating Range**

$(T_A = -40^{\circ} \text{ to } +85^{\circ}\text{C}, V_{DD} = 1.8V \pm 10\%, GND=0V)$

| Parameter         | Description                 | Test Conditions                                                          | Min. | Typ. <sup>(1)</sup> | Max. | Units |

|-------------------|-----------------------------|--------------------------------------------------------------------------|------|---------------------|------|-------|

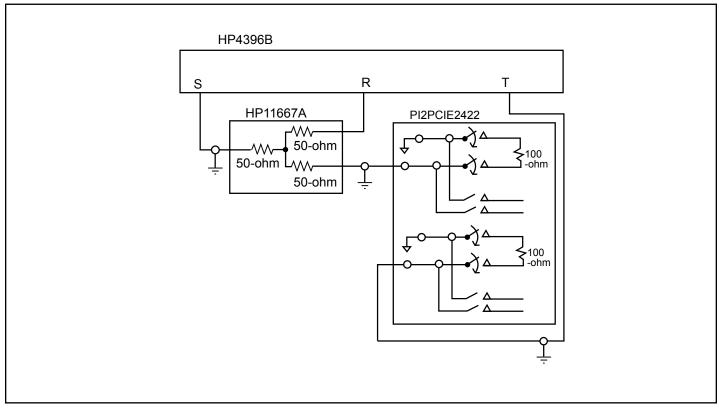

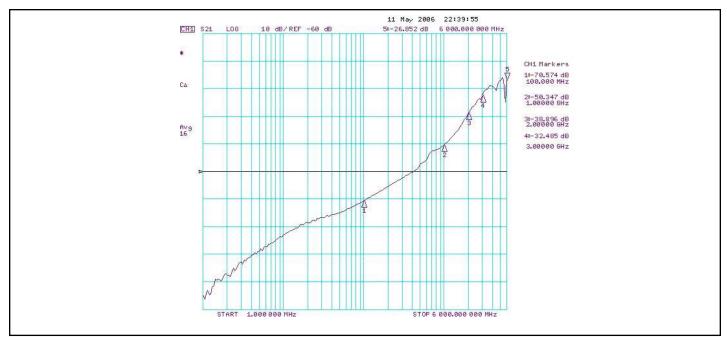

| X <sub>TALK</sub> | Crosstalk                   | See Fig. 1 for Measurement Setup, $f = 3.00 \text{ GHz}$<br>f = 100  MHz |      | -15<br>-50          |      |       |

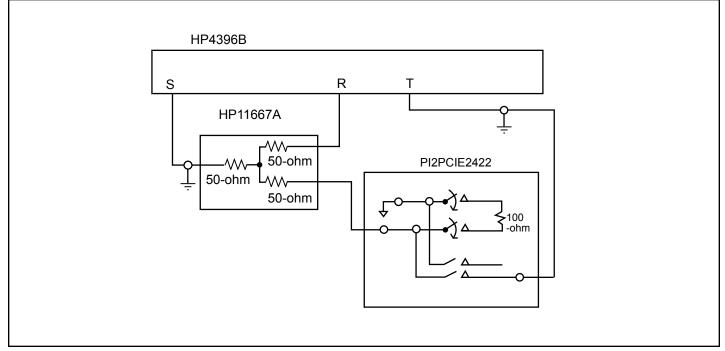

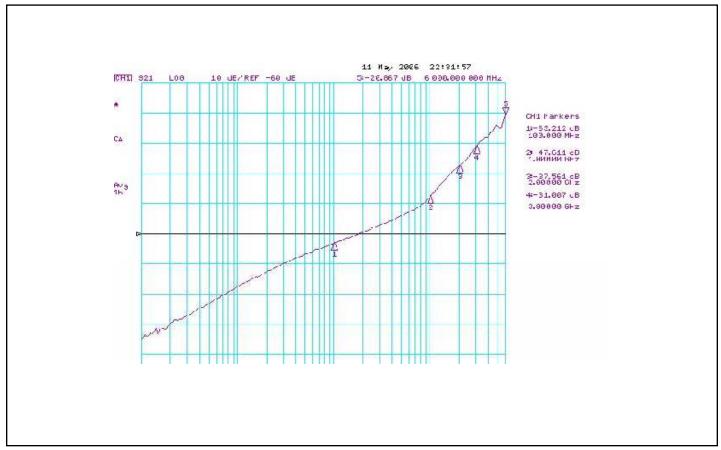

| O <sub>IRR</sub>  | OFF Isolation               | See Fig. 2 for Measurement Setup, $f = 3.00 \text{ GHz}$<br>f = 100  MHz |      | -15<br>-45          |      | dB    |

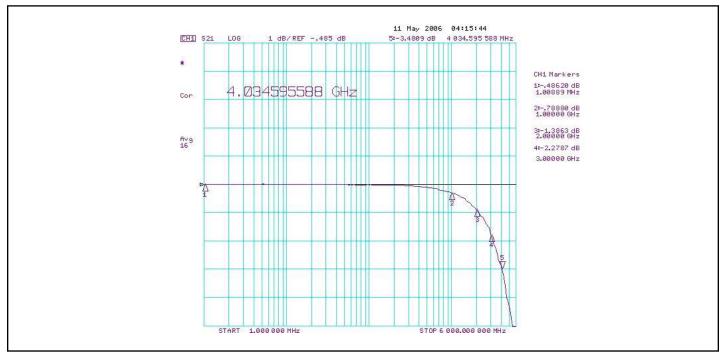

| I <sub>LOSS</sub> | Differential Insertion Loss | f=3 GHz                                                                  |      | -3                  |      |       |

| BW                | Bandwidth (-3dB)            |                                                                          |      | 2.5                 |      | GHz   |

#### Notes

<sup>1.</sup> Typical values are at  $V_{DD} = 1.5V$ ,  $T_A = 25^{\circ}C$  ambient and maximum loading.

<sup>1.</sup> Guaranteed by design. Typical values are at  $V_{DD} = 1.5V$ ,  $T_a = 25$ °C ambient and maximum loading.

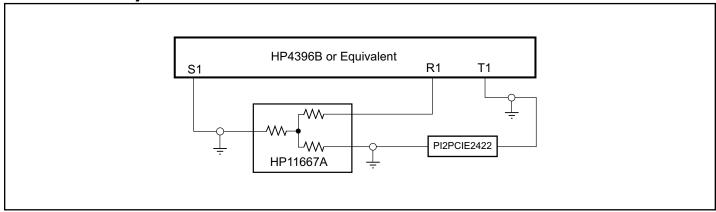

Fig 1: Crosstalk Setup

Fig 2: Off-isolation setup

Fig 3: Typical Crosstalk Plot from 1MHz to 6.0GHz, VDD=1.5V, 25°C

Fig 4: Typical Off Isolation Plot from 1 MHz to 6.0 GHz, V<sub>DD</sub> = 1.5V, TA=25°C

Fig 5: Typical Insertion Loss Plot from 1MHz to 6.0GHz, VDD=1.5V, 25C

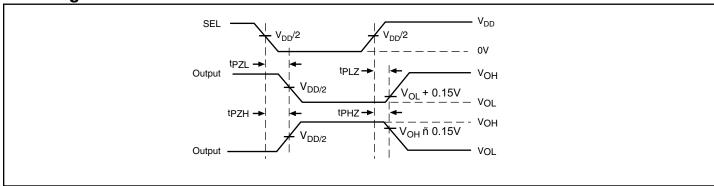

# **Switching Characteristics**

$(T_A = -40^{\circ} \text{ to } +85^{\circ}\text{C}, V_{DD} = 1.5\text{V} \pm 10\%)$

| Paramenter                       | Description                                                |     | Тур. | Max.  | Units   |  |

|----------------------------------|------------------------------------------------------------|-----|------|-------|---------|--|

| tpzh, tpzl                       | Line Enable Time - SEL to AN, BN                           | 0.5 |      | 15    | <b></b> |  |

| tpHZ, tPLZ                       | Line Disable Time - SEL to A <sub>N</sub> , B <sub>N</sub> | 0.5 |      | 15 ns |         |  |

| t <sub>b-b</sub>                 | Bit-to-bit skew within same differential pair              |     |      | 10    | 200     |  |

| t <sub>ch</sub> -t <sub>ch</sub> | Channel-to-channel timing skew                             |     |      | 50    | ps      |  |

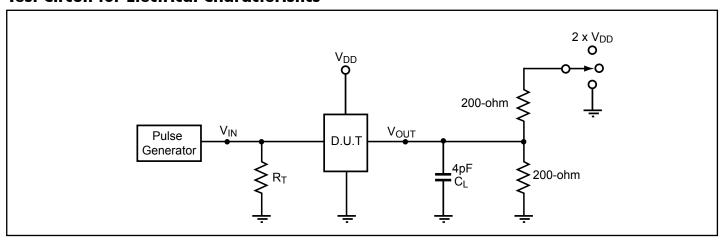

# Test Circuit for Electrical Characteristics<sup>(1-5)</sup>

#### Notes:

- 1.  $C_L = Load$  capacitance: includes jig and probe capacitance.

- 2.  $R_T$  = Termination resistance: should be equal to  $Z_{OUT}$  of the Pulse Generator

- 3. Waveform 1 is for an output with internal conditions such that the output is low except when disabled by the output control. Waveform 2 is for an output with internal conditions such that the output is high except when disabled by the output control.

- 4. All input impulses are supplied by generators having the following characteristics:  $PRR \le MHz$ ,  $Z_O = 50\Omega$ ,  $t_R \le 2.5$ ns,  $t_F \le 2.5$ ns.

- 5. The outputs are measured one at a time with one transition per measurement.

### **Switch Positions**

| Test                                                   | Switch              |

|--------------------------------------------------------|---------------------|

| t <sub>PLZ</sub> , t <sub>PZL</sub> (output on B-side) | 2 x V <sub>DD</sub> |

| t <sub>PHZ</sub> , t <sub>PZH</sub> (output on B-side) | GND                 |

| Prop Delay                                             | Open                |

# **Test Circuit for Dynamic Electrical Characteristics**

# **Switching Waveforms**

**Voltage Waveforms Enable and Disable Times**

### **Applications Information**

Rail-to-Rail is a registered trademark of Nippon Motorola, Ltd

# PCI Express Application Specific Measurements and Test Set-up

Figure 6: the test set-up for the PI2PCIE2422 eye test

#### Notes

- 1. A modified PI2PCIE2422 application board with 16-inch differential trace is used for Eye management.

- 2. Agilent N4902B BERT is used to generate a K28.5 pattern at 5 Gbps with 500mV single-end swing.

- 3. To create the P12PCIE2422-free test condition, the P12PCIE2422 chip is removed and a wire is connected between the trace and output probe.

- 4. An Agilent Infinuum 54855A is used and Serial Data Analysis software is ran to capture the Eye.

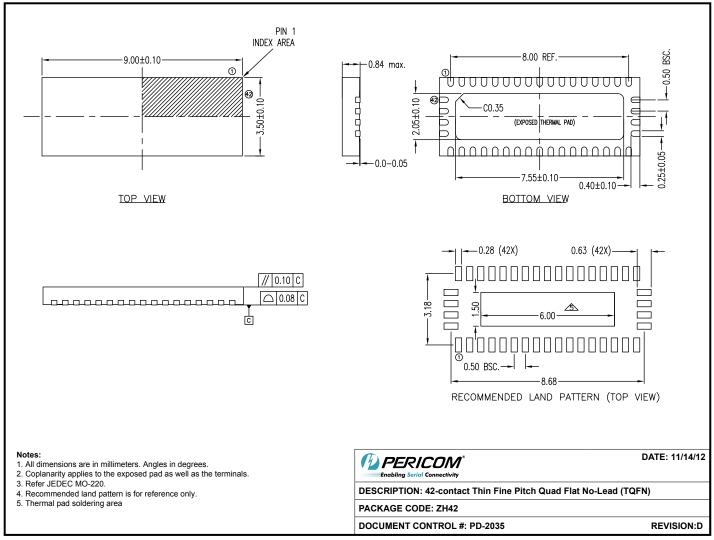

## Packaging Mechanical: 42-Contact TQFN (ZH)

12-0529

# **Ordering Information**

| Ordering Code  | Package Code | Package Description                                  |

|----------------|--------------|------------------------------------------------------|

| PI2PCIE2422ZHE | ZH           | 42-contact, Thin Fine Pitch Quad Flat No-Lead (TQFN) |

#### Notes:

- 1. Thermal characteristics can be found on the company web site at www.pericom.com/packaging/

- 2. E = Lead-free and green

- 2. X suffix = tape and reel