# **MPQ2484**

75V, Multi-Topology LED Controller with Multiple Dimming Modes, AEC-Q100 Qualified

#### DESCRIPTION

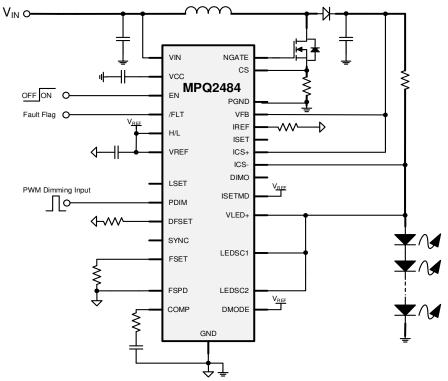

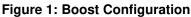

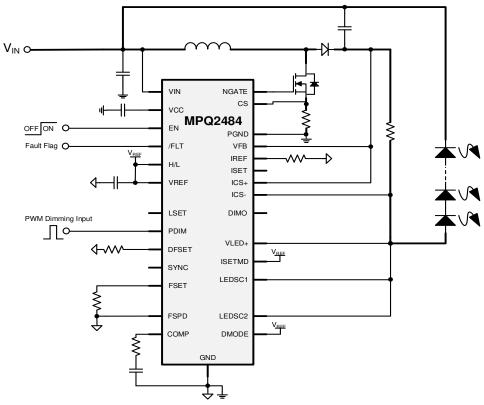

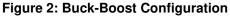

The MPQ2484 is a flexible, multi-topology, asynchronous controller for LED lights with a high brightness. The device supports buck, boost, and buck-boost configurations, which makes it well-suited for multi-purpose applications. The MPQ2484 features a wide 4.5V to 45V input voltage ( $V_{IN}$ ) range, with a maximum boost voltage up to 75V. Peak current mode operation provides fast transient response and eases loop stabilization.

The switching frequency  $(f_{SW})$  can be set by the FSET pin, or it can be synchronized by a 100kHz to 2.2MHz external clock signal. The configurable frequency spread spectrum (FSS) function can periodically enable dither switching to improve EMI.

The MPQ2484 provides dimming switch mode with a P-channel MOSFET. During normal operation without a P-channel MOSFET, twostep dimming or PWM dimming can be selected.

Robust fault protections include thermal shutdown, cycle-by-cycle peak current limiting, output over-voltage protection (OVP), output short-circuit protection (SCP), LED open protection, and LED short protection. The fault indicator outputs an active logic low signal if a fault occurs.

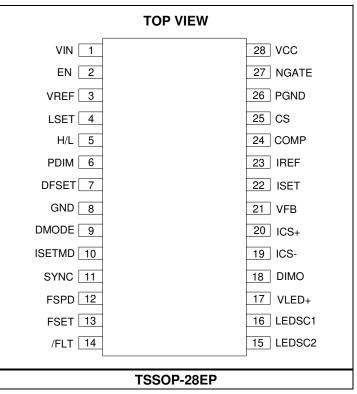

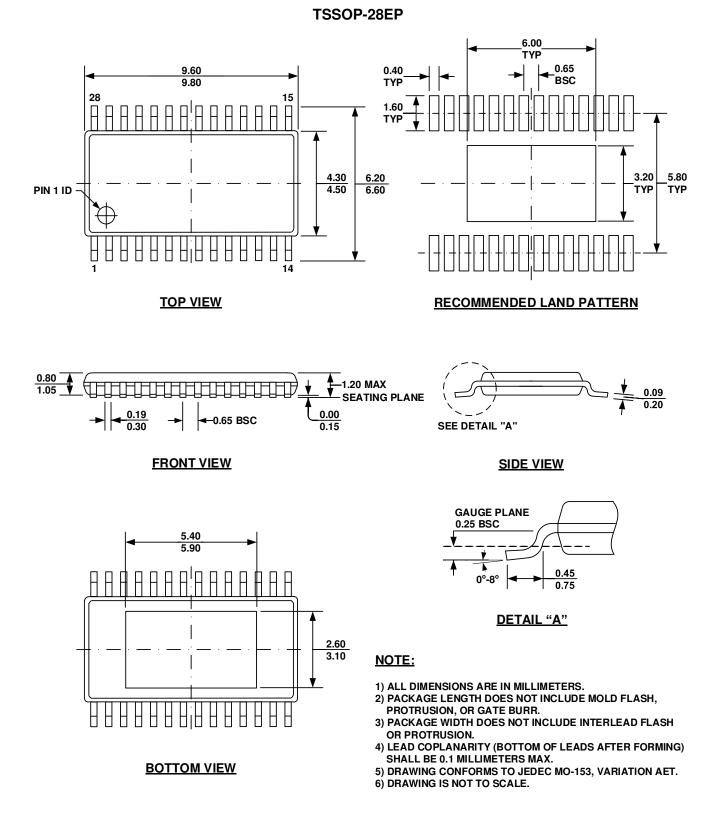

The MPQ2484 is available in a TSSOP-28EP package.

#### FEATURES

- Built to Handle Automotive Lighting:

- Load Dump Up to 45V

- Cold Crank Down to 4.5V

- Maximum 75V Boost Output

- Multiple Dimming Modes

- Two-Step Dimming via the H/L Pin

- External PWM Dimming via the PDIM Pin

- Integrated P-Channel Dimming MOSFET Driver

- o Available in AEC-Q100 Grade 1

- Supports Buck, Boost, and Buck-Boost Topologies

- Low-Noise EMI/EMC:

- Frequency Spread Spectrum (FSS)

- Configurable or Synchronizable Switching Frequency (f<sub>SW</sub>)

- Robust Protections:

- Cycle-by-Cycle Current Limit

- Output Over-Voltage Protection (OVP)

- Open LED Protection

- LED String Anode/Cathode to Battery/Ground Short Protection

- One or More LEDs Short Protection

- Over-Temperature Shutdown

- Fault Flag Output

- Additional Features:

- <5µA Shutdown Current</li>

- <1mA Quiescent Current</li>

- Configurable Current-Sense Reference via an External Setting Resistor

- External Loop Compensation

- o Available in a TSSOP-28EP Package

#### APPLICATIONS

- Automotive Exterior LED Lighting:

- o Headlights

- Daytime Running Lights (DRLs)

- o Fog Lights/Signal Lights

- Indoor and Outdoor LED Lighting

- Commercial and Industrial LED Lighting

All MPS parts are lead-free, halogen-free, and adhere to the RoHS directive. For MPS green status, please visit the MPS website under Quality Assurance. "MPS", the MPS logo, and "Simple, Easy Solutions" are trademarks of Monolithic Power Systems, Inc. or its subsidiaries.

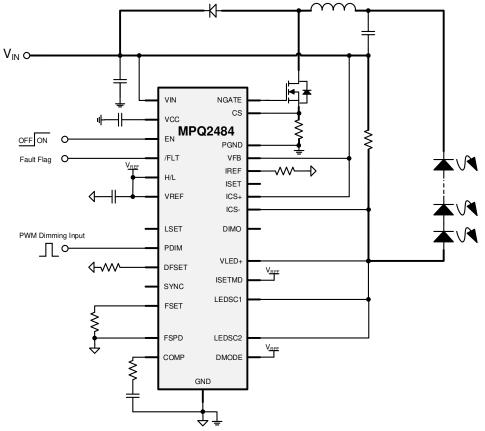

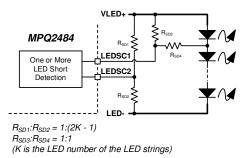

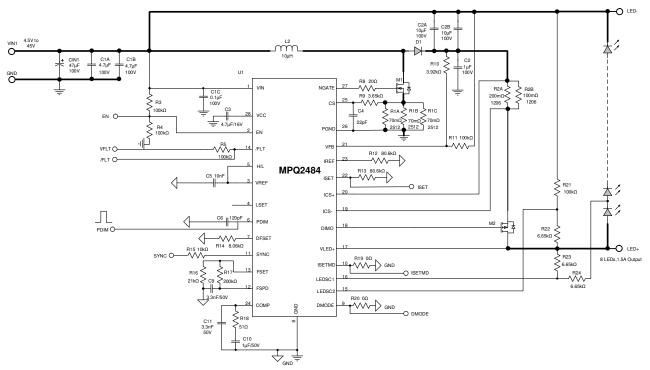

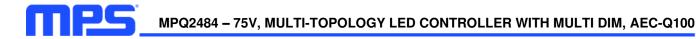

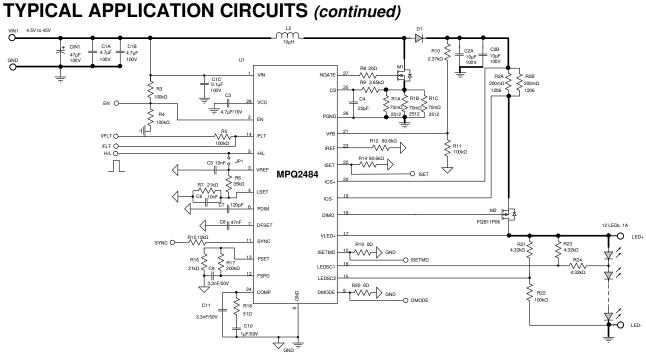

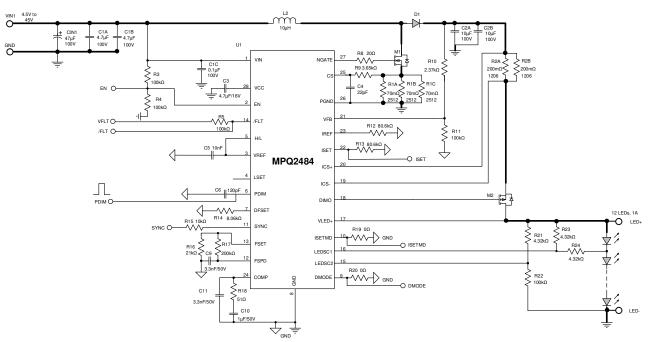

#### **TYPICAL APPLICATION**

MPS \_\_

Figure 3: Buck Configuration

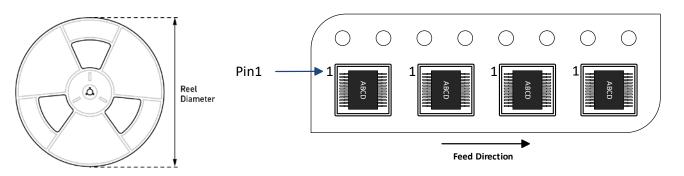

#### **ORDERING INFORMATION**

| Part Number*   | Package    | Top Marking | MSL Rating** |  |

|----------------|------------|-------------|--------------|--|

| MPQ2484GF-AEC1 | TSSOP-28EP | See Below   | Level 2a     |  |

\*For Tape & Reel, add suffix -Z (e.g. MPQ2484GF-AEC1-Z). \*\*Moisture Sensitivity Level Rating

#### **TOP MARKING (MPQ2484GF-AEC1)**

MPSYYWW

MP2484

LLLLLLLL

MPS: MPS prefix YY: Year code WW: Week code MP2484: Part number LLLLLLLL: Lot number

#### PACKAGE REFERENCE

#### **PIN FUNCTIONS**

| Pin # | Name   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | VIN    | Power supply input. Connect a bypass capacitor from VIN to PGND to reduce noise.                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

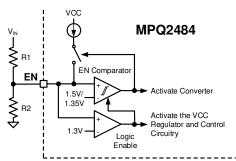

| 2     | EN     | <b>On/off control input and custom input UVLO setting.</b> The EN pin can be driven by an external logic signal to enable and disable the chip. Pull EN above 1.3V to enable the part; pull it below 0.4V to shut down the part. Set a configurable input voltage ( $V_{IN}$ ) under-voltage lockout (UVLO) threshold by tying a resistor divider from the input to the EN pin. Do not float EN.                                                                                                                                            |

| 3     | VREF   | <b>2.37V reference output.</b> VREF is the reference for LED short detection. Bypass VREF to GND with an external 1nF to 10nF ceramic capacitor.                                                                                                                                                                                                                                                                                                                                                                                            |

| 4     | LSET   | <b>Dimming duty setting for two-step dimming.</b> If the H/L pin is pulled down to ground, the LSET pin's voltage determines the two-step dimming duty cycle. A resistor divider is tied from VREF to LSET to set the two-step dimming threshold. If two-step dimming mode is not used, float the LSET pin.                                                                                                                                                                                                                                 |

| 5     | H/L    | <b>Two-step dimming control input.</b> When two-step dimming is selected and the H/L pin is logic high, the LED output current is set to full scale (no dimming). If the H/L pin is logic low, the LSET voltage sets the two-step dimming threshold. If two-step dimming mode is not used, connect the H/L pin to VREF. Do not float H/L.                                                                                                                                                                                                   |

| 6     | PDIM   | <b>PWM dimming pulse input.</b> If PWM dimming is selected, connect the H/L pin to VREF and apply a PWM signal to the PDIM pin for LED dimming. When PDIM is pulled down to logic low, switching stops and DIMO pulls high to turn off the dimming P-channel MOSFET. Connect a ceramic bypass capacitor from the PDIM pin to GND when two-step dimming is activated.                                                                                                                                                                        |

| 7     | DFSET  | <b>Two-step dimming frequency setting.</b> Connect an external capacitor from the DFSET pin to GND. The internal source/sink current source charges and discharges the capacitor repeatedly to generate a stable triangular wave. The LSET level is compared to the triangular wave to output a PWM dimming signal. If PWM dimming is used, tie the DFSET pin to ground using a 7.14k $\Omega$ to 8.46k $\Omega$ resistor. A 8.06k $\Omega$ resistor is recommended.                                                                        |

| 8     | GND    | Signal ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 9     | DMODE  | <b>Dimming mode control input.</b> If the DMODE pin is pulled down to GND, place an additional P-channel MOSFET in series with the LED string to improve dimming performance. This additional MOSFET can also act as a protection MOSFET in buck-boost and boost mode. If this pin is logic high, the P-channel MOSFET driver is disabled. Do not float DMODE.                                                                                                                                                                              |

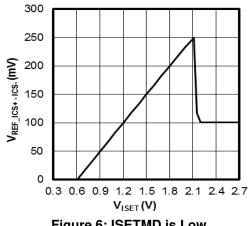

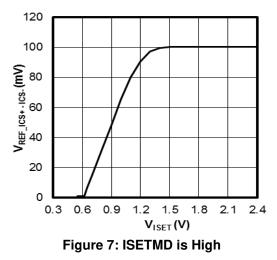

| 10    | ISETMD | <b>Current-sense reference selection input.</b> If the ISETMD pin is logic high, the LED current-<br>setting reference voltage (ICS+ - ICS-) is set between 0mV and 100mV when the ISET<br>voltage (V <sub>ISET</sub> ) rises from 0.6V to 1.2V. This supports thermal derating when an NTC resistor<br>is tied from ISET to GND. If the ISETMD pin is pulled down to GND, the LED current can be<br>set at up to 200% of the nominal value when V <sub>ISET</sub> rises from 0.6V to 1.8V. This feature can<br>be used for analog dimming. |

| 11    | SYNC   | <b>Synchronization input.</b> If an external clock pulse signal is connected to the SYNC pin, the frequency setting function on the FSET pin is disabled, and the chip synchronizes its switching with the external clock. Ensure that the SYNC high level exceeds 1.4V and that the low level is below 0.6V. Float SYNC if external synchronization is not used.                                                                                                                                                                           |

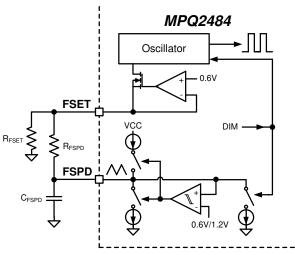

| 12    | FSPD   | <b>Frequency spread spectrum (FSS) output ramp.</b> Connect a capacitor from the FSPD pin to GND, and connect a resistor between the FSPD and FSET pins to dither the switching frequency (fsw) for spread spectrum. Remove the resistor if FSS is disabled. For more details, see the Frequency Spread Spectrum section on page 44.                                                                                                                                                                                                        |

| 13    | FSET   | <b>Switching frequency setting.</b> Connect an external resistor from FSET to GND to set the internal switching clock frequency. $R_{FSET}$ (k $\Omega$ ) = 8333 / fsw (kHz). Do not float FSET.                                                                                                                                                                                                                                                                                                                                            |

# PIN FUNCTIONS (continued)

| Pin # | Name   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14    | /FLT   | <b>Fault flag indicator output.</b> The /FLT pin is an active-low, open-drain output. Connect an external pull-up resistor to this pin. If a fault status is activated, /FLT is pulled down to GND. If the system recovers and no fault status is detected for 30µs, then the /FLT pin is released to an open-drain condition.                                                                                                                                                                                                                                                             |

| 15    | LEDSC2 | <b>One or more LEDs short sense input 2.</b> The LEDSC2 pin senses the LED string's voltage drop via a resistor divider. Short LEDSC2 and LEDSC1 to LED+ if this protection is not used.                                                                                                                                                                                                                                                                                                                                                                                                   |

| 16    | LEDSC1 | <b>One or more LEDs short sense input 1.</b> The LEDSC1 pin senses a single LED's voltage drop via a resistor divider. Short LEDSC1 and LEDSC2 to LED+ if this protection is not used.                                                                                                                                                                                                                                                                                                                                                                                                     |

| 17    | VLED+  | <b>LED string anode input.</b> The VLED+ pin is used for fault detection with other pins. If an external dimming P-channel MOSFET is not connected, short VLED+ to ICS                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 18    | DIMO   | <b>Dimming P-channel MOSFET gate driver output.</b> If the dimming P-channel MOSFET is connected, the DIMO pin drives the external P-channel MOSFET as a dimming switch. Float DIMO if the external P-channel MOSFET is not connected.                                                                                                                                                                                                                                                                                                                                                     |

| 19    | ICS-   | High-side LED current-sense negative input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 20    | ICS+   | <b>High-side LED current-sense positive input.</b> For full-scale LED current control, the voltage between ICS+ and ICS- is regulated to 100mV.                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 21    | VFB    | <b>LED string voltage feedback input.</b> Connect a resistor divider from ICS+ to the LED string cathode. The VFB pin is tied to the tap of the resistor divider to sense the LED string voltage for over-voltage protection (OVP).                                                                                                                                                                                                                                                                                                                                                        |

| 22    | ISET   | <b>LED current setting.</b> Connect an external resistor from ISET to ground. $V_{ISET}$ can set the reference voltage ( $V_{REF}$ ) for the LED current regulator. When ISETMD is pulled down to GND and $V_{ISET}$ rises up from 0.6V to 1.8V, $V_{REF}$ rises from 0mV to 200mV. This feature can be used after setting a resistor on the LED light load, which allows the LED current to be adjusted. When ISETMD is pulled high and $V_{ISET}$ rises from 0.6V to 1.2V, $V_{REF}$ rises from 0mV to 100mV. If the ISET pin is left floating, the current reference is fixed at 100mV. |

| 23    | IREF   | <b>Biased current setting for ISET.</b> The IREF pin sets the bias current (I <sub>ISET</sub> = 100 x I <sub>IREF</sub> ) for the ISET resistor to improve accuracy. Tie a resistor from IREF to ground. Do not float IREF.                                                                                                                                                                                                                                                                                                                                                                |

| 24    | COMP   | <b>Compensation connection.</b> The COMP pin is the internal error amplifier's (EA's) output. Connect a resistor and capacitor network to this pin for system stability.                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 25    | CS     | <b>N-channel MOSFET current-sense input.</b> Tie a current-sense resistor from the N-channel MOSFET source to PGND to sense the switching current and set the current limit. Add a resistor/capacitor network between CS and the current-sense resistor to configure the slope compensation.                                                                                                                                                                                                                                                                                               |

| 26    | PGND   | Power ground. Ground return for the N-channel MOSFET's current sense.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 27    | NGATE  | <b>Power N-channel MOSFET gate driver output.</b> Connect NGATE to the gate of the N-channel MOSFET.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 28    | VCC    | <b>8.5V internal regulator output.</b> VCC supplies power to both control blocks and the N-channel MOSFET's gate driver. Bypass VCC to PGND with an external ceramic capacitor.                                                                                                                                                                                                                                                                                                                                                                                                            |

#### ABSOLUTE MAXIMUM RATINGS (1)

#### Electrostatic Discharge (ESD) Ratings

| Human body model (HBM)     | Class 2 (3)  |

|----------------------------|--------------|

| Charged device model (CDM) | Class C2 (4) |

#### **Recommended Operating Conditions**

| Supply voltage (V <sub>IN</sub> )            | 4.5V to 45V |

|----------------------------------------------|-------------|

| Max boost voltage ICS+ to PGND               | 75V         |

| Operating junction temp (T <sub>J</sub> )40° | C to +150°C |

# Thermal Resistance <sup>(5)</sup> $\theta_{JA}$ $\theta_{JC}$

#### TSSOP-28EP

JESD51-7.....6.....°C/W

#### Notes:

- Absolute maximum ratings are rated under room temperature unless otherwise noted. Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature, T<sub>J</sub> (MAX), the junction-toambient thermal resistance,  $\theta_{JA}$ , and the ambient temperature, T<sub>A</sub>. The maximum allowable continuous power dissipation at any ambient temperature is calculated by P<sub>D</sub> (MAX) = (T<sub>J</sub> (MAX) - T<sub>A</sub>) /  $\theta_{JA}$ . Exceeding the maximum allowable power dissipation can cause excessive die temperature, and the device may go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- 3) Per AEC-Q100-002.

- 4) Per AEC-Q100-011.

- 5) Measured on JESD51-7, 4-layer PCB. The value of  $\theta_{JA}$  given in this table is only valid for comparison with other packages and cannot be used for design purposes. These values were calculated in accordance with JESD51-7 and simulated on a specified JEDEC board. They do not represent the performance obtained in an actual application.

# **ELECTRICAL CHARACTERISTICS**

$V_{IN} = 12V$ ,  $V_{EN} = 2V$ ,  $T_J = -40^{\circ}C$  to  $+150^{\circ}C$ , all voltages with respect to ground, typical values are at  $T_J = 25^{\circ}C$ , unless otherwise noted.

| Parameters                                         | Symbol              | Condition                                                                                                            | Min   | Тур   | Max  | Units |

|----------------------------------------------------|---------------------|----------------------------------------------------------------------------------------------------------------------|-------|-------|------|-------|

| Input Supply Voltage                               |                     |                                                                                                                      |       |       |      | -     |

| Operating range                                    | VIN                 |                                                                                                                      | 4.5   |       | 45   | V     |

| VIN under-voltage lockout<br>(UVLO) threshold      | VIN_UVLO            | V <sub>IN</sub> falling                                                                                              | 3.6   | 3.9   | 4.2  | V     |

| VIN UVLO hysteresis                                | VIN_UVLO_HYS        |                                                                                                                      |       | 250   | 500  | mV    |

| Input Supply Current                               |                     |                                                                                                                      | ·     |       |      | •     |

| Shutdown current                                   | Isd                 | V <sub>EN</sub> = 0V, ICS+ floating                                                                                  |       | 1     | 5    | μA    |

| Quiescent current (normal)                         | lq                  | No switching                                                                                                         |       | 0.7   | 1    | mA    |

| VCC Regulator                                      |                     | ·                                                                                                                    |       |       |      |       |

| Regulator output voltage                           | Vcc                 | $10V \le V_{IN} \le 15V,$<br>$0.1mA \le I_{CC} \le 50mA$<br>$15V \le V_{IN} \le 45V,$<br>$0.1mA \le I_{CC} \le 35mA$ | 7.8   | 8.5   | 9.2  | v     |

| Dropout voltage                                    | V <sub>CC_DR</sub>  | $V_{IN} = 4.5V, I_{CC} = 50mA$                                                                                       |       | 520   | 1150 | mV    |

| Short-circuit current limit                        |                     | $V_{CC} = 0V$                                                                                                        | 55    | 100   | 150  | mA    |

| VCC UVLO threshold                                 | Vcc uvlo            | V <sub>cc</sub> falling                                                                                              | 3.6   | 3.9   | 4.2  | V     |

| VCC UVLO hysteresis                                | Vcc_uvlo_hys        |                                                                                                                      |       | 235   | 500  | mV    |

| Reference Regulator                                |                     |                                                                                                                      |       |       |      |       |

| VREF output voltage                                | V <sub>REF</sub>    | $4.5V \le V_{IN} \le 45V,$<br>$0\mu A \le I_{REF} \le 100\mu A$                                                      | 2.31  | 2.37  | 2.43 | V     |

| Short-circuit current<br>limitation                | IREF_MAX            | V <sub>REF</sub> = 0V                                                                                                |       | 220   |      | μA    |

| Oscillator                                         |                     | ·                                                                                                                    |       |       |      |       |

| Switching frequency                                | fsw                 |                                                                                                                      | 100   |       | 2200 | kHz   |

|                                                    |                     | $R_{FREQ} = 82.5 k\Omega$                                                                                            | 85    | 100   | 125  |       |

| Oscillator frequency<br>accuracy                   | fsw                 | $R_{FREQ} = 17.8 k\Omega$                                                                                            | 423   | 470   | 517  | kHz   |

| accuracy                                           |                     | $R_{FREQ} = 3.3 k\Omega$                                                                                             | 1980  | 2200  | 2420 |       |

| Biased voltage at FSET                             | VFSET               |                                                                                                                      | 0.575 | 0.608 | 0.63 | V     |

| Maximum duty cycle                                 | Dмах                | $\label{eq:VCS} \begin{array}{l} V_{CS} = 0V, \\ V_{ICS+} - V_{ICS-} = 0.09V \end{array}$                            | 92    | 95    | 98   | %     |

| Synchronization frequency range                    | fsync               | fsync < 2.2MHz                                                                                                       | 110%  |       | 170% | fsw   |

| SYNC logic high threshold                          | V <sub>SYNC_H</sub> | V <sub>SYNC</sub> rising                                                                                             | 1.4   |       |      | V     |

| SYNC logic low threshold                           | V <sub>SYNC_L</sub> | VSYNC falling                                                                                                        |       |       | 0.5  | V     |

| SYNC minimal logic high pulse width <sup>(6)</sup> | tsync_pw_min        |                                                                                                                      | 200   |       |      | ns    |

# ELECTRICAL CHARACTERISTICS (continued)

$V_{IN} = 12V$ ,  $V_{EN} = 2V$ ,  $T_J = -40^{\circ}C$  to  $+150^{\circ}C$ , all voltages with respect to ground, typical values are at  $T_J = 25^{\circ}C$ , unless otherwise noted.

| Parameters                              | Symbol                      | Condition                                        | Min  | Тур  | Max  | Units |

|-----------------------------------------|-----------------------------|--------------------------------------------------|------|------|------|-------|

| Frequency Spread Spectrum               |                             | •                                                | •    |      |      |       |

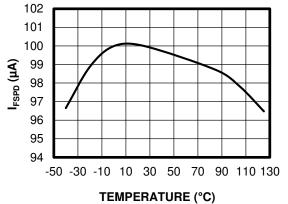

| FSPD source current                     | IFSPD_SOURCE                | DIM on, V <sub>FSPD</sub> = 0V                   | 70   | 100  | 130  | μA    |

| FSPD sink current                       | IFSPD_SINK                  | DIM on, $V_{FSPD} = 2.5V$                        | 70   | 100  | 130  | μA    |

| FSPD high flip threshold                | V <sub>FSPD_H</sub>         | DIM on, V <sub>FSPD</sub> rising                 | 1.1  | 1.2  | 1.3  | V     |

| FSPD low flip threshold                 | V <sub>FSPD_L</sub>         | DIM on, V <sub>FSPD</sub> falling                | 0.52 | 0.6  | 0.68 | V     |

| Enable                                  |                             |                                                  |      |      |      |       |

| Logic enable threshold                  | VEN_LOGIC_H                 | V <sub>EN</sub> rising                           | 1.3  |      |      | V     |

| Logic disable threshold                 | V <sub>EN_LOGIC_L</sub>     | V <sub>EN</sub> falling                          |      |      | 0.4  | V     |

| System enable threshold                 | VEN_SYS_ON                  | V <sub>EN</sub> rising                           | 1.42 | 1.5  | 1.58 | V     |

| Pull-up hysteresis current              | IEN_SYS_HYS                 | After the converter works                        | 200  | 630  | 1000 | nA    |

| Hysteresis voltage                      | VEN_SYS_HYS                 |                                                  | 50   | 150  | 300  | mV    |

| NMOS Driver                             |                             |                                                  |      |      |      |       |

| NGATE output voltage                    | Vue                         | $V_{CC} = 8.5V$                                  | 8    | 8.5  |      | V     |

| NGATE output voltage                    | VNGATE                      | $V_{CC} = V_{CC_UVLO} + 50mV$                    | 3.5  |      |      | V     |

| NGATE pull-up resistor                  | <b>R</b> <sub>PULL-UP</sub> | $V_{CC} = 8.5V, V_{NGATE} = 0V$                  |      | 1000 | 2000 | mΩ    |

| NGATE pull-up resistor                  | <b>R</b> PULL-UP            | $V_{CC} = V_{NGATE} = 8.5V$                      |      | 1500 | 2500 | mΩ    |

| NGATE rising time (6)                   | tr_ng                       | C <sub>NGATE</sub> = 10nF                        |      | 30   |      | ns    |

| NGATE falling time (6)                  | t <sub>F_NG</sub>           | C <sub>NGATE</sub> = 10nF                        |      | 30   |      | ns    |

| NMOS Current Sense Compa                | rator                       |                                                  | ·    |      |      |       |

| Leading edge blanking time              | tcs_leb                     |                                                  |      | 90   |      | ns    |

| Current-sense clamp voltage             | Vcs_clamp                   | Cycle-by-cycle limit                             | 360  | 400  | 440  | mV    |

| Slope compensation ramp<br>peak current | ISLOP_PK                    | Ramp peak current during<br>each switching cycle | 37   | 50   | 60   | μA    |

| Dimming PMOS Driver                     |                             |                                                  |      |      |      |       |

| Biased voltage UVLO threshold           | VICS+_UVLO                  | V <sub>ICS+</sub> falling                        | 7.9  | 8.5  | 9.1  | V     |

| Biased voltage UVLO<br>hysteresis       | VICS+_HYS                   |                                                  | 100  | 200  | 300  | mV    |

| DIMO lowest output voltage              | N                           | 12V < V <sub>ICS+</sub> < 75V                    | -12  | -11  | -10  | V     |

| with respect to $V_{ICS+}$              | Vdimo_min                   | $V_{ICS+} = V_{ICS+}UVLO + 50mV$                 |      |      | -6.5 | V     |

| DIMO peak source current                | IDIMO_SOURCE                | V <sub>DIMO</sub> - V <sub>ICS+</sub> = -8.5V    | 25   | 50   | 80   | mA    |

| DIMO peak sink current                  | IDIMO_SINK                  | VDIMO = VICS+                                    | 30   | 50   | 65   | mA    |

# ELECTRICAL CHARACTERISTICS (continued)

$V_{IN} = 12V$ ,  $V_{EN} = 2V$ ,  $T_J = -40^{\circ}C$  to  $+150^{\circ}C$ , all voltages with respect to ground, typical values are at  $T_J = 25^{\circ}C$ , unless otherwise noted.

| Parameters                               | Symbol                              | Condition                                     | Min                           | Тур   | Max                           | Units   |

|------------------------------------------|-------------------------------------|-----------------------------------------------|-------------------------------|-------|-------------------------------|---------|

| LED Current Regulation                   | -                                   |                                               | •                             | •     | •                             | <u></u> |

| Feedback reference voltage               | VICS_FB                             | 100% scale, ±5%                               | 93                            | 100   | 107                           | mV      |

| ICS+ bias current                        | I <sub>CS+</sub>                    | DIM off, $V_{ICS+} = 75V$                     |                               | 170   | 250                           | μA      |

| ICS- bias current                        | Ics-                                |                                               | -200                          |       | +200                          | nA      |

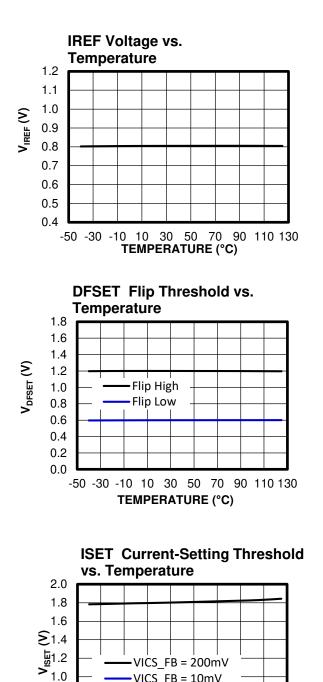

| Biased voltage at IREF                   | VIREF                               |                                               | 0.785                         | 0.805 | 0.825                         | V       |

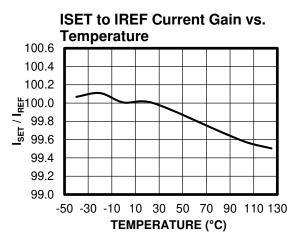

| Current gain                             | I <sub>SET</sub> / I <sub>REF</sub> |                                               | 95                            | 100   | 105                           | %       |

| ISET max current setting threshold       | V <sub>ISET_MAX</sub>               | V <sub>ICS_FB</sub> = 200mV                   | 1.4                           | 1.8   | 2.2                           | V       |

| ISET min current setting threshold       | VISET_MIN                           | V <sub>ICS_FB</sub> = 10mV                    | 0.5                           | 0.63  | 0.73                          | V       |

| VLED+ bias current                       | IVLED+                              |                                               | 40                            | 75    | 100                           | μA      |

| Compensation                             |                                     |                                               |                               |       |                               |         |

| Error amplifier (EA)<br>transconductance | Gea                                 |                                               | 3.1                           | 4.5   | 5.9                           | mA/V    |

| COMP source current                      | ICOMP_SOURCE                        | $V_{COMP} = 0V$                               | 200                           | 570   | 1000                          | μA      |

| COMP sink current                        | ICOMP_SINK                          | $V_{COMP} = 4.5V$                             | 200                           | 570   | 1000                          | μA      |

| Two-Step Dimming                         |                                     |                                               |                               | •     |                               |         |

| H/L high level threshold                 | V <sub>H/L_H</sub>                  | V <sub>H/L</sub> rising                       | 1.4                           |       |                               | V       |

| H/L low level threshold                  | V <sub>H/L_L</sub>                  | V <sub>H/L</sub> falling                      |                               |       | 0.6                           | V       |

| DFSET source current                     | IDFSET_SOURCE                       | Triangular wave, V <sub>DFSET</sub> = 0V      | 70                            | 100   | 130                           | μA      |

| DFSET sink current                       | Idfset_sink                         | Triangular wave,<br>V <sub>DFSET</sub> = 1.5V | 70                            | 100   | 130                           | μA      |

| DFSET high flip threshold                | Vdfset_h                            | VDFSET rising                                 | 1.122                         | 1.2   | 1.278                         | V       |

| DFSET low flip threshold                 | VDFSET_L                            | VDFSET falling                                | 0.56                          | 0.6   | 0.64                          | V       |

| PWM Dimming (Tie an 8.06k                | Ω Resistor from                     | m DFSET to Ground, or Set V                   | DFSET = 1V                    | ')    |                               |         |

| PDIM pull-up current                     | <b>I</b> PDIM                       | $V_{H/L}=2V,\ V_{PDIM}=0V$                    |                               | 3     | 5                             | μA      |

| PDIM logic high threshold                | V <sub>PDIM_H</sub>                 | V <sub>PDIM</sub> rising                      | V <sub>DFSET</sub> +<br>100mV |       |                               | V       |

| PDIM logic low threshold                 | Vpdim_l                             | VPDIM falling                                 |                               |       | V <sub>DFSET</sub> -<br>100mV | V       |

| PDIM to DIMO turn-on delay               | tpwm_delay_on                       | $C_{\text{DIMOICS+}} = 7nF$                   |                               | 3     |                               | μs      |

| PDIM to DIMO turn-off delay              | tpwm_delay_off                      | $C_{\text{DIMOICS+}} = 7nF$                   |                               | 2     |                               | μs      |

| Current-Sense Reference Se               | election                            |                                               |                               |       |                               |         |

| ISETMD logic high threshold              | VISETMD_H                           | VISETMD rising                                | 1.4                           |       |                               | V       |

| ISETMD logic low threshold               | VISETMD_L                           | VISETMD falling                               |                               |       | 0.6                           | V       |

| ISETMD pull-up current                   | IISETMD                             | VISETMD = 0V                                  |                               | 3     | 5                             | μA      |

| Dimming Mode Selection                   | T                                   | <b>.</b>                                      |                               |       |                               | •       |

| DMODE logic high threshold               | Vdmode_h                            | V <sub>DMODE</sub> rising                     | 1.4                           |       |                               | V       |

| DMODE logic low threshold                | V <sub>DMODE_L</sub>                | V <sub>DMODE</sub> falling                    |                               |       | 0.6                           | V       |

| DMODE pull-up current                    | IDMODE                              | V <sub>DMODE</sub> = 0V                       |                               | 3     | 5                             | μA      |

MPQ2484 Rev. 1.0 9/8/2021 MP

# ELECTRICAL CHARACTERISTICS (continued)

$V_{IN} = 12V$ ,  $V_{EN} = 2V$ ,  $T_J = -40^{\circ}C$  to  $+150^{\circ}C$ , all voltages with respect to ground, typical values are at  $T_J = 25^{\circ}C$ , unless otherwise noted.

| Parameters                                                                   | Symbol                 | Condition                                                  | Min                   | Тур       | Max  | Units           |

|------------------------------------------------------------------------------|------------------------|------------------------------------------------------------|-----------------------|-----------|------|-----------------|

| Over-Voltage Protection (witho                                               | ut Fault Flag Inc      | lication)                                                  |                       |           |      |                 |

| OVP threshold with respect to $V_{ICS+}$                                     | VFBOVP                 | (V <sub>FB</sub> - V <sub>ICS+</sub> ) falling             | -1.24                 | -1.17     | -1.1 | V               |

| OVP hysteresis                                                               | VFB <sub>OVP_HYS</sub> |                                                            | 50                    | 150       | 250  | mV              |

| VFB bias current                                                             | IVFB                   |                                                            | -65                   |           | +65  | nA              |

| <b>Under-Current Protection (UCF</b>                                         | ) (for OLP and S       | SCP, with Fault Flag Indicati                              | on)                   |           |      |                 |

| UCP threshold with respect to $V_{\text{ICS+}}$                              | VUCP                   | $V_{CC\_MODE} = 0V,$<br>( $V_{ICS^-} - V_{ICS^+}$ ) rising | -70                   | -50       | -30  | mV              |

| Short-Circuit Protection (SCP)                                               | with Fault Flag I      | ndication                                                  |                       |           |      |                 |

| SCP threshold with respect to $V_{ICS+}$                                     | VSCP                   | (V <sub>ICS-</sub> - V <sub>ICS+</sub> ) falling           | -325                  | -300      | -275 | mV              |

|                                                                              |                        | VLED + falling                                             | 1.3                   | 1.5       | 1.7  | V               |

| VLED+ short threshold                                                        | VLED+ SCP              | $(V_{LED} + - V_{IN})$ falling                             | 1.1                   | 1.5       | 2    | V               |

|                                                                              | VLED+_SCP              | $(V_{LED+} - V_{IN})$ is almost equal to 0V                | -0.45                 | 0         | +0.1 | V               |

| SCP fault activation delay time<br>(counter increases only at<br>dimming on) | tscp_delay             | Only level I                                               |                       | 4096      |      | Clock<br>cycles |

|                                                                              |                        | Level I and VLED+ short<br>or level II                     |                       | 32        |      | Clock<br>cycles |

| Short One or More LEDs Prote                                                 | ction (Activated       | and with Fault Flag Indicati                               | on in V <sub>DI</sub> | MODE = 2V | )    |                 |

|                                                                              | VIED AUADT             | Level I,<br> VLEDSC1 - VLEDSC2  rising                     | 20                    | 80        | 150  | mV              |

| LED short threshold                                                          | VLED_SHORT             | Level II,<br> VLEDSC1 - VLEDSC2  rising                    | 70                    | 180       | 270  | mV              |

| LED short fault activation delay time (counter increases only at             | tled_short_delay       | Level I                                                    |                       | 4096      |      | Clock<br>cycles |

| dimming on)                                                                  |                        | Level II                                                   |                       | 32        |      | Clock<br>cycles |

| Thermal Shutdown                                                             |                        |                                                            |                       |           |      |                 |

| Thermal shutdown threshold (6)                                               | T <sub>SD</sub>        | TJ rising                                                  |                       | 170       |      | °C              |

| Thermal shutdown hysteresis (6)                                              | T <sub>HYS</sub>       |                                                            |                       | 20        |      | °C              |

| Fault Recovery Timer                                                         |                        |                                                            |                       |           |      |                 |

| Hiccup delay time (counter increases when dimming is on)                     | tніссир                | After a fault status is activated, except OTP              |                       | 8192      |      | Clock<br>cycles |

| Fault Flag (Open Drain)                                                      |                        |                                                            |                       |           |      |                 |

| /FLT output low voltage                                                      | V <sub>FLT_L</sub>     | IFLT_SINK = 1mA                                            |                       |           | 200  | mV              |

| /FLT leakage current                                                         | IFLT_LKG               | V <sub>FLT</sub> = 5V                                      |                       |           | 1    | μA              |

Note:

6) Not tested in production. Guaranteed by design and characterization.

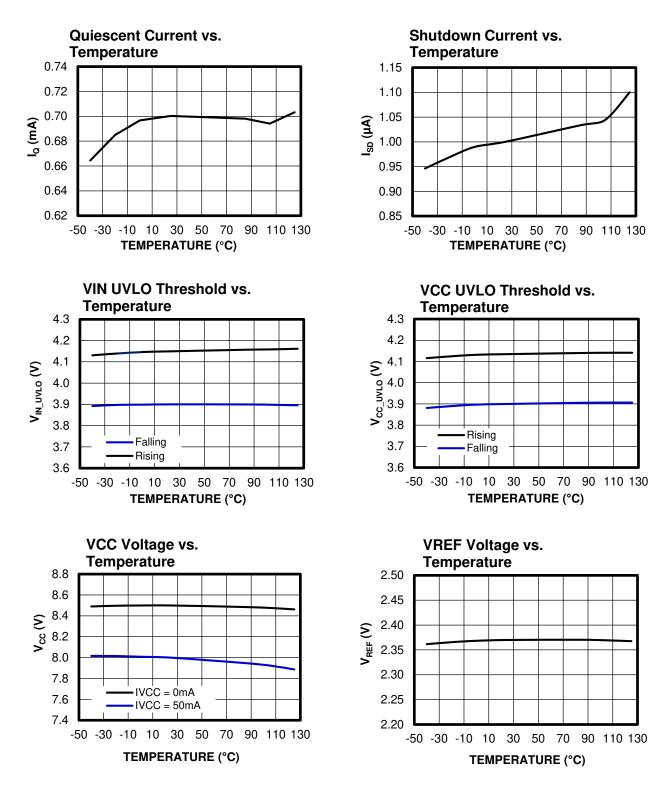

# **TYPICAL CHARACTERISTICS**

$V_{IN}$  = 12V,  $T_J$  = -40°C to +125°C, unless otherwise noted.

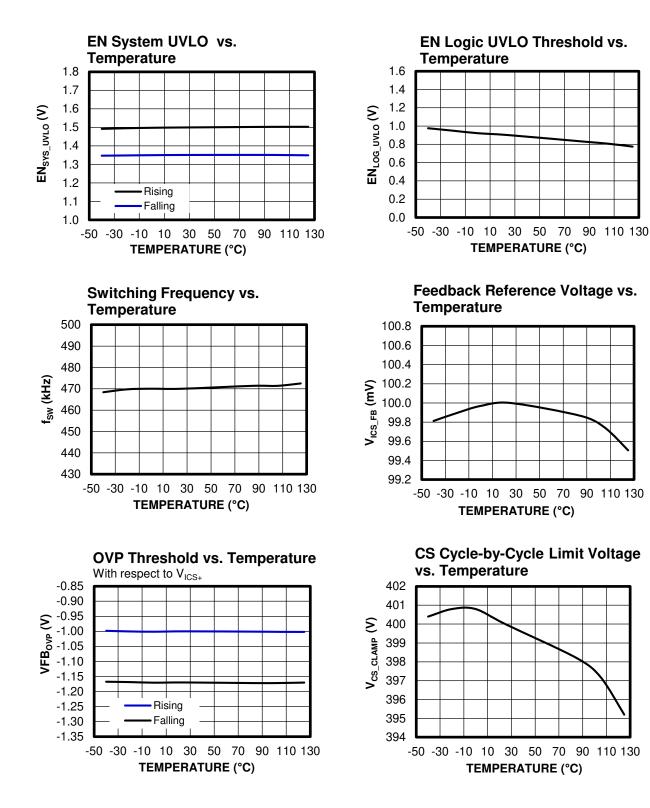

# TYPICAL CHARACTERISTICS (continued)

$V_{IN}$  = 12V,  $T_J$  = -40°C to +125°C, unless otherwise noted.

# **TYPICAL CHARACTERISTICS** (continued)

$V_{IN} = 12V$ ,  $T_J = -40^{\circ}C$  to  $+125^{\circ}C$ , unless otherwise noted.

VICS FB = 10mV

-50 -30 -10 10 30 50 70 90 110 130 **TEMPERATURE (°C)**

FSPD Source/Sink Current vs. **Temperature**

0.8 0.6 0.4

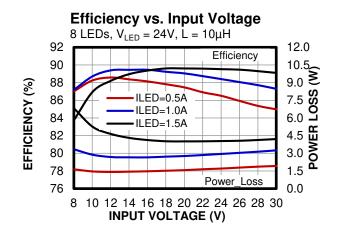

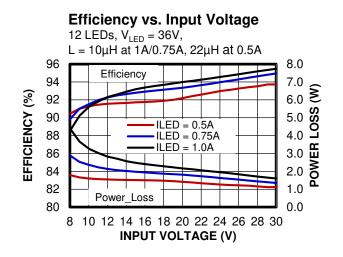

#### **TYPICAL PERFORMANCE CHARACTERISTICS**

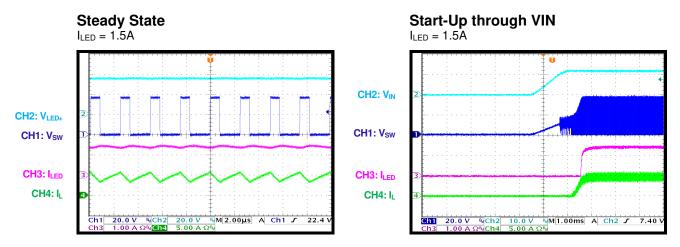

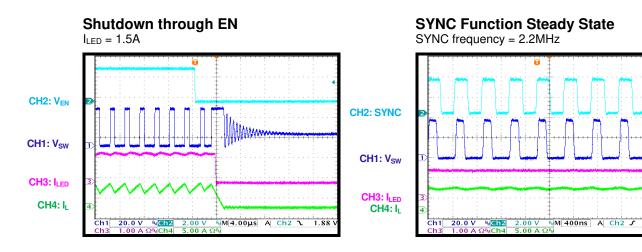

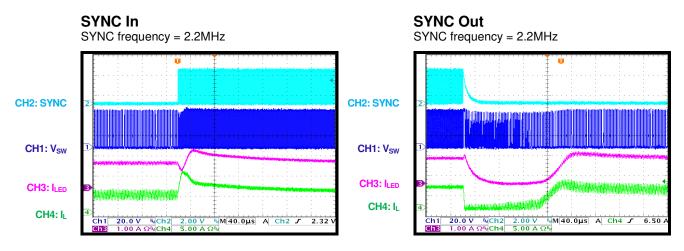

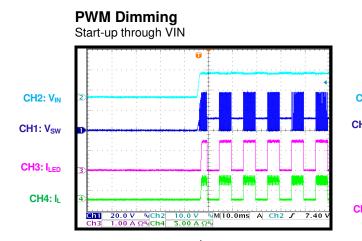

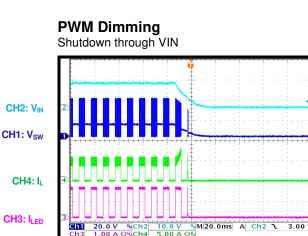

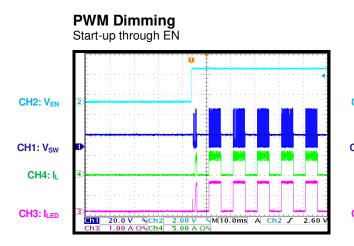

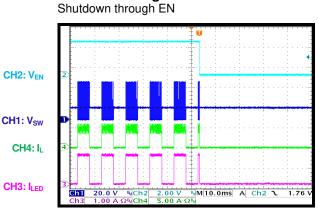

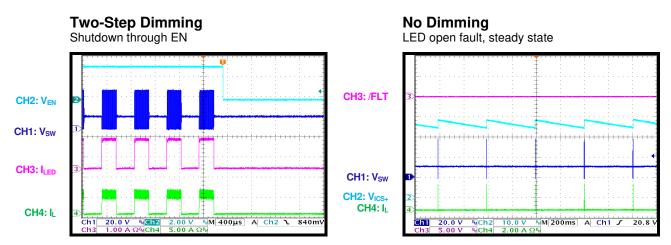

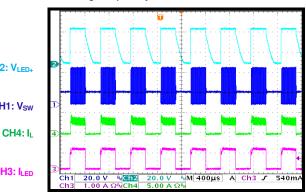

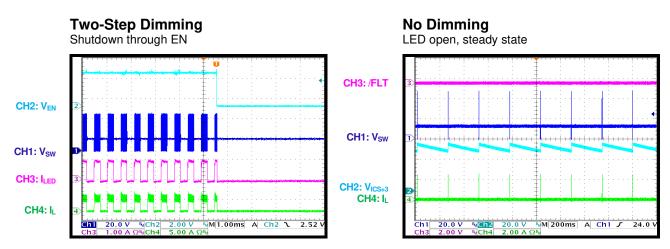

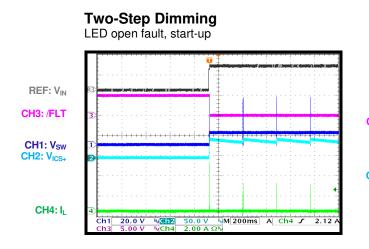

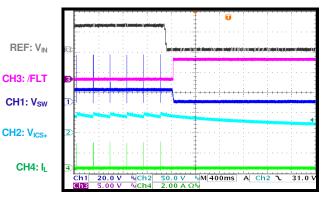

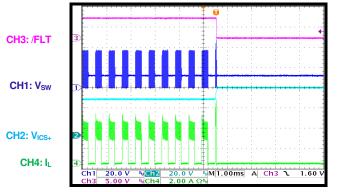

Buck-boost mode, 8 LEDs (V<sub>LED</sub> = 24V), V<sub>IN</sub> = 12V,  $f_{SW}$  = 410kHz, L = 10µH, T<sub>A</sub> = 25°C, unless otherwise noted.

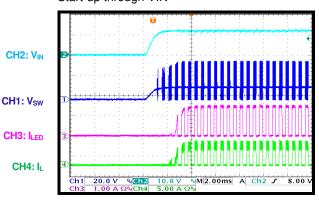

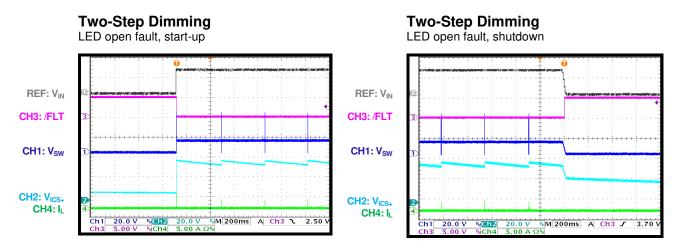

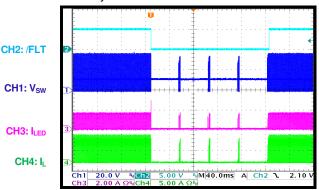

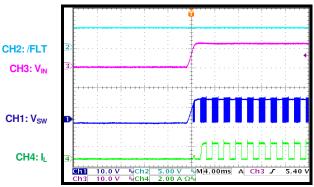

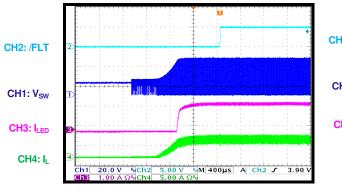

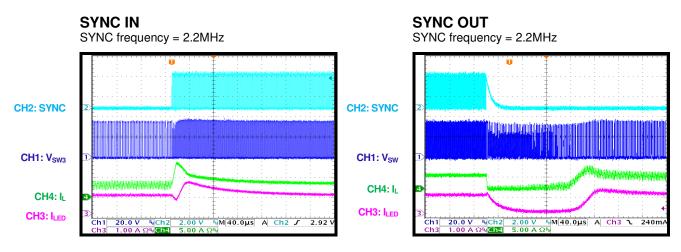

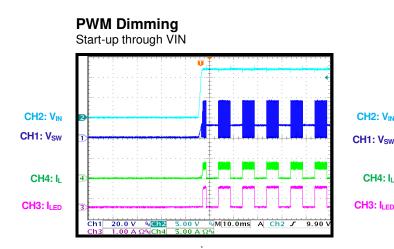

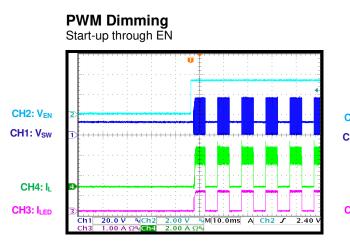

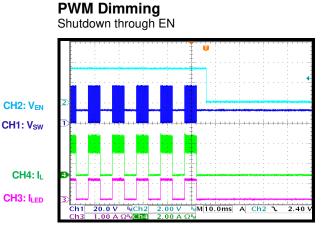

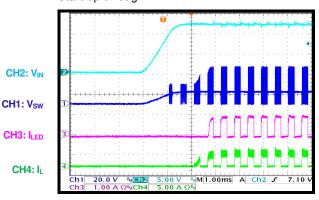

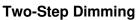

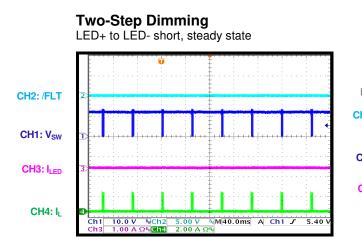

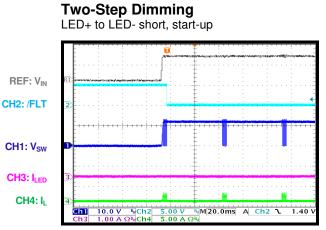

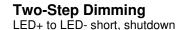

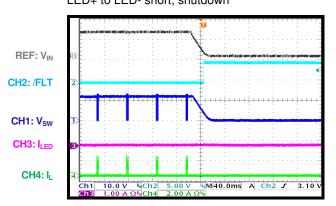

Buck-boost mode, 8 LEDs,  $V_{\text{LED}}$  = 24V,  $V_{\text{IN}}$  = 12V,  $f_{\text{SW}}$  = 410kHz, L = 10µH,  $T_{\text{A}}$  = 25°C, unless otherwise noted.

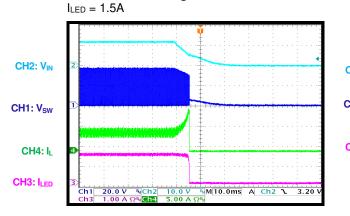

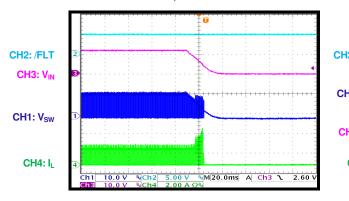

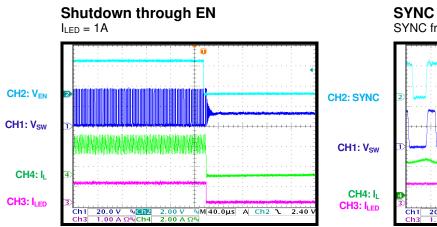

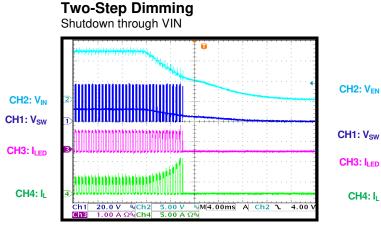

Shutdown through VIN

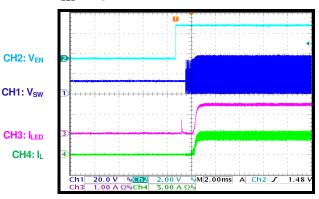

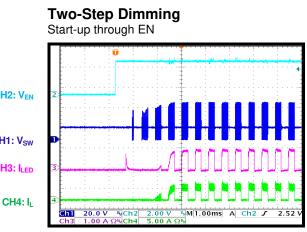

Start-Up through EN ILED = 1.5A

2.68

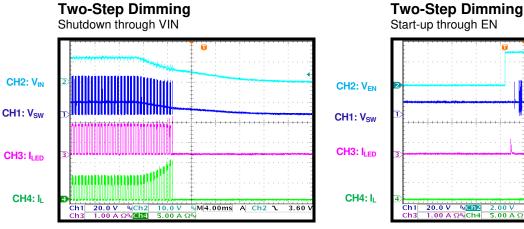

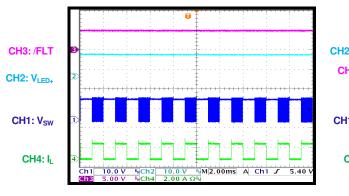

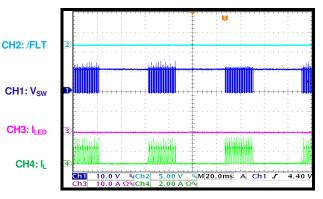

Buck-boost mode, 8 LEDs,  $V_{LED}$  = 24V,  $V_{IN}$  = 12V,  $f_{SW}$  = 410kHz, L = 10µH, T<sub>A</sub> = 25°C, unless otherwise noted.

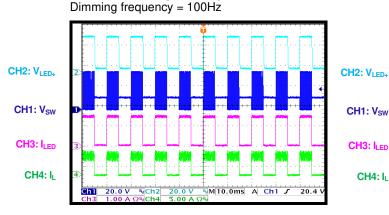

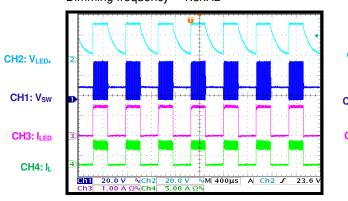

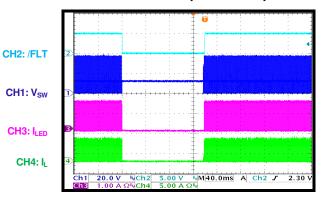

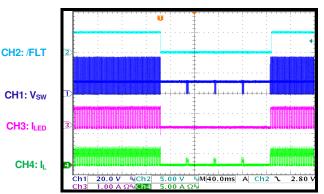

PWM Dimming Steady State

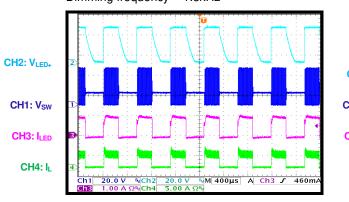

**PWM Dimming Steady State** Dimming frequency = 2kHz

MPQ2484 Rev. 1.0 9/8/2021 MPS Pt

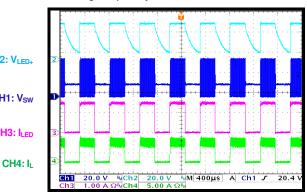

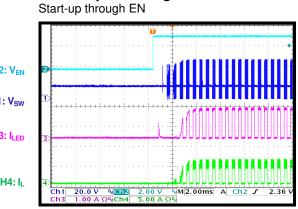

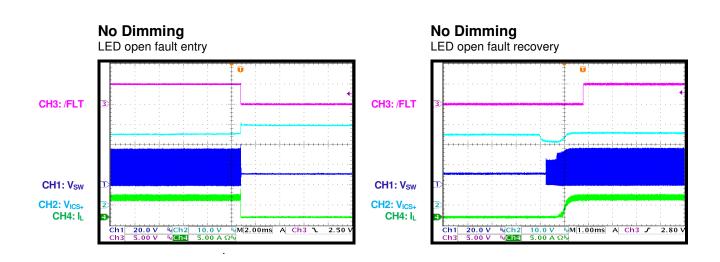

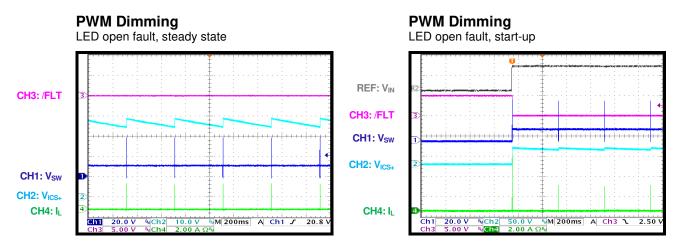

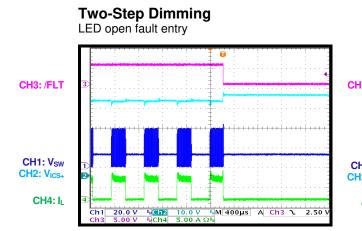

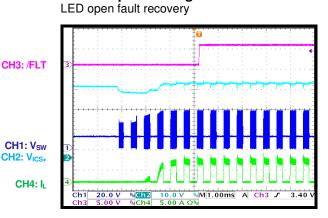

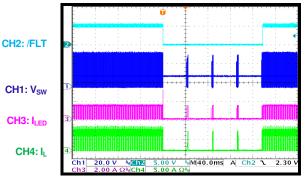

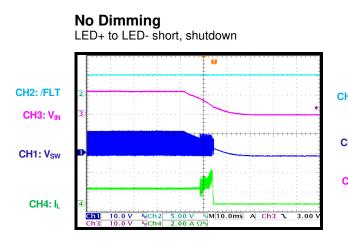

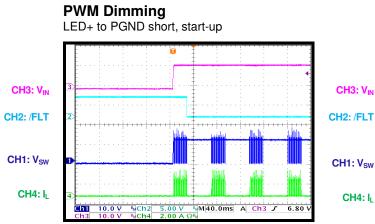

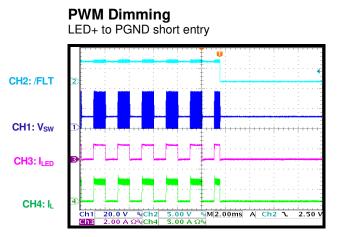

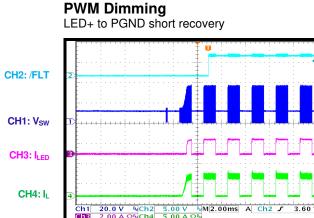

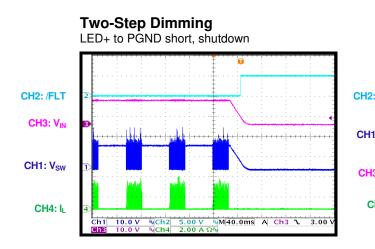

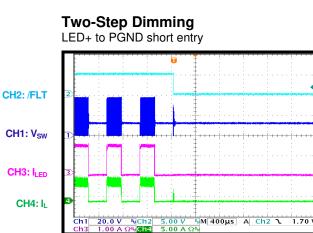

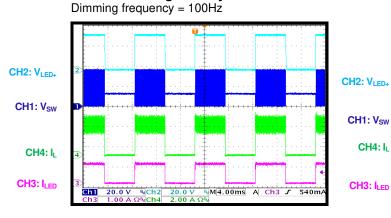

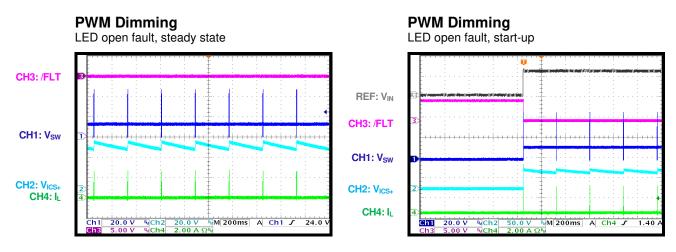

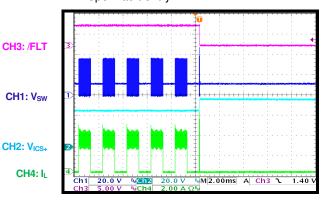

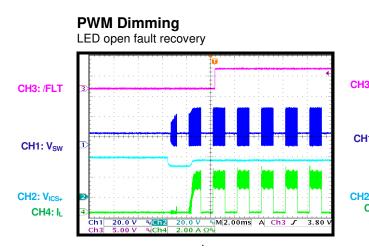

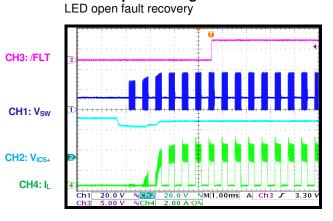

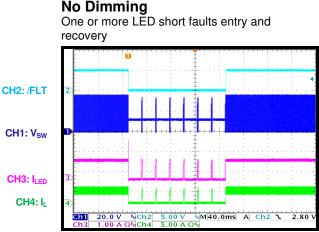

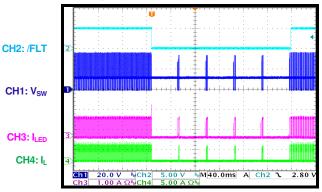

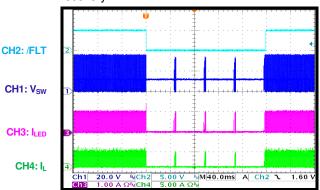

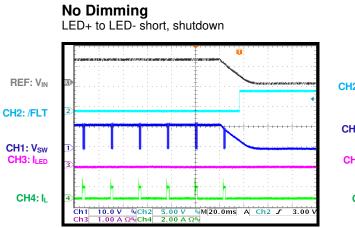

Buck-boost mode, 8 LEDs,  $V_{LED} = 24V$ ,  $V_{IN} = 12V$ ,  $f_{SW} = 410$ kHz, L = 10 $\mu$ H, T<sub>A</sub> = 25°C, unless otherwise noted.

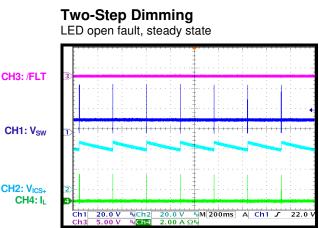

**Two-Step Dimming Steady State** Dimming frequency = 1.8kHz

**Two-Step Dimming** Start-up through VIN

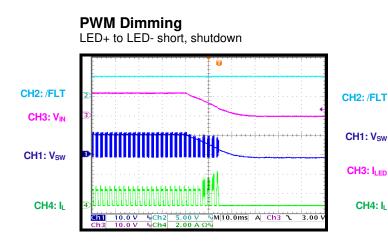

**PWM Dimming**

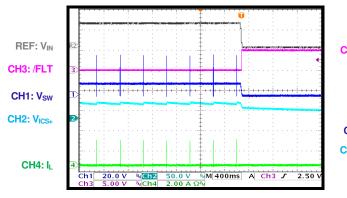

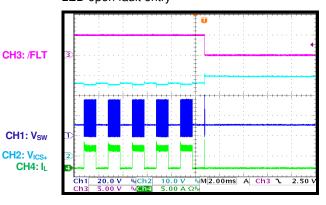

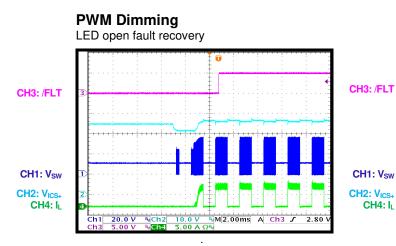

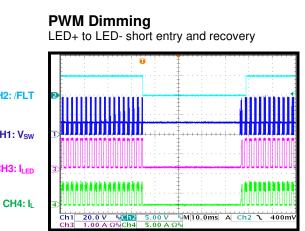

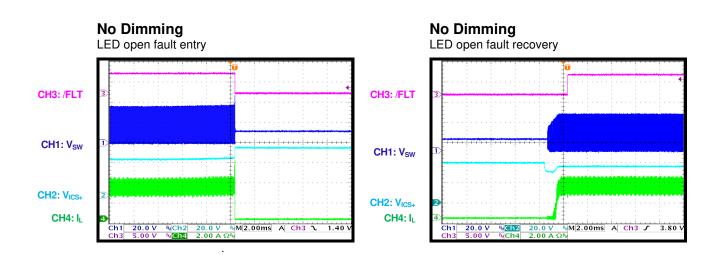

Buck-boost mode, 8 LEDs,  $V_{LED}$  = 24V,  $V_{IN}$  = 12V,  $f_{SW}$  = 410kHz, L = 10µH, T<sub>A</sub> = 25°C, unless otherwise noted.

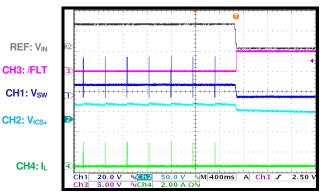

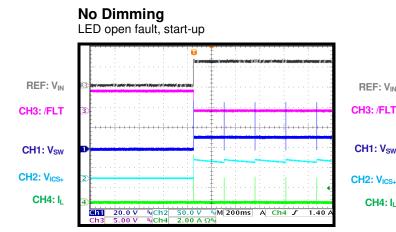

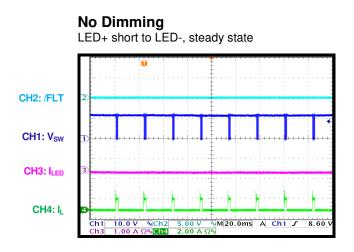

# No Dimming LED open fault, start-up REF: VIN Image: CH3: /FLT CH3: /FLT Image: CH2: VICS+ CH2: VICS+ Image: CH3: CH2: S0.0 V CH4: IL Image: CH3: S0.0 V

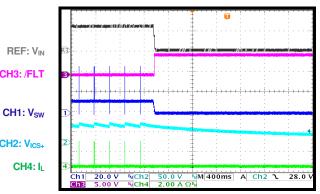

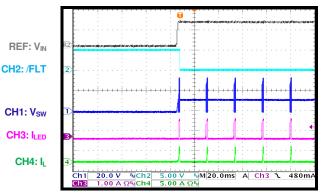

Buck-boost mode, 8 LEDs,  $V_{LED}$  = 24V,  $V_{IN}$  = 12V,  $f_{SW}$  = 410kHz, L = 10µH,  $T_A$  = 25°C, unless otherwise noted.

#### **PWM Dimming** LED open fault, shutdown

#### **PWM Dimming** LED open fault entry

# Two-Step Dimming LED open fault, steady state /FLT Joint Company Vsw

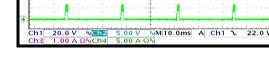

Ch1 20.0 V

NCh2

10.0 V <sup>6</sup> M 200ms A Ch1 *J* 24.8 2.00 A Ω<sup>5</sup>

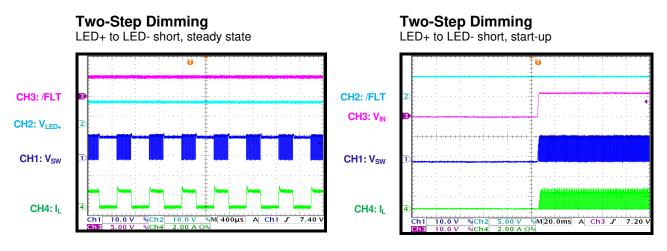

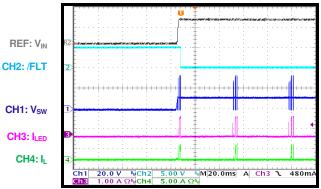

Buck-boost mode, 8 LEDs (V<sub>LED</sub> = 24V), V<sub>IN</sub> = 12V,  $f_{SW}$  = 410kHz, L = 10µH, T<sub>A</sub> = 25°C, unless otherwise noted.

Two-Step Dimming

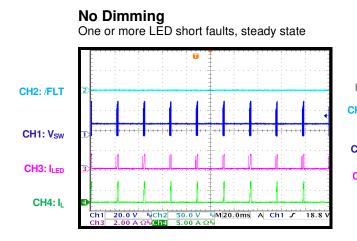

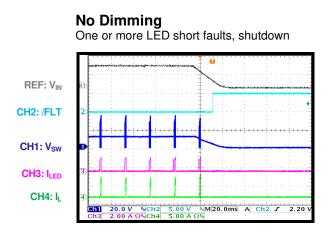

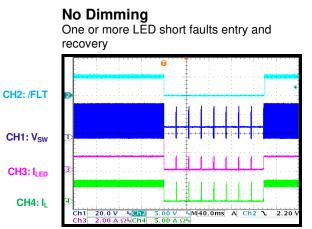

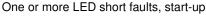

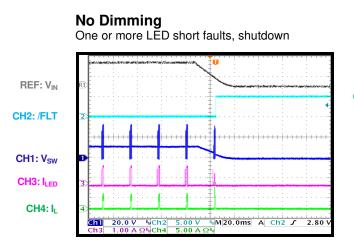

No Dimming One or more LED short faults, start-up

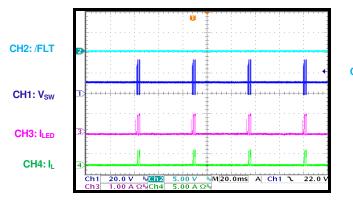

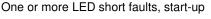

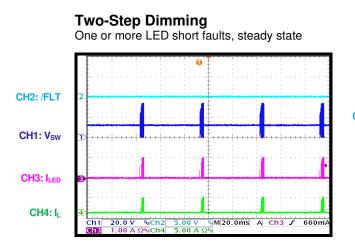

Buck-boost mode, 8 LEDs,  $V_{LED}$  = 24V,  $V_{IN}$  = 12V,  $f_{SW}$  = 410kHz, L = 10µH,  $T_A$  = 25°C, unless otherwise noted.

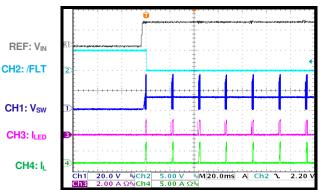

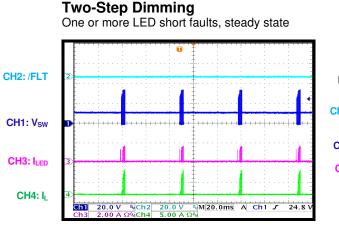

**PWM Dimming** One or more LED short faults, steady state

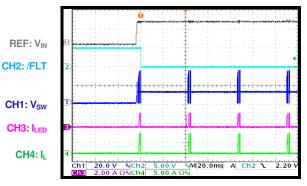

# **PWM Dimming**

One or more LED short faults entry and recovery

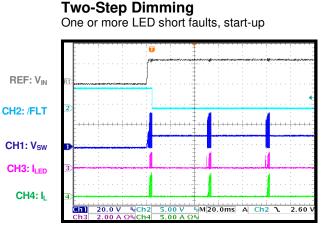

Buck-boost mode, 8 LEDs,  $V_{LED}$  = 24V,  $V_{IN}$  = 12V,  $f_{SW}$  = 410kHz, L = 10µH,  $T_A$  = 25°C, unless otherwise noted.

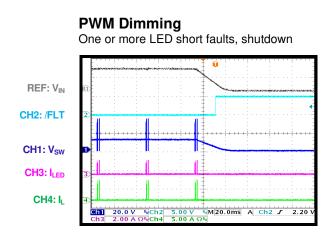

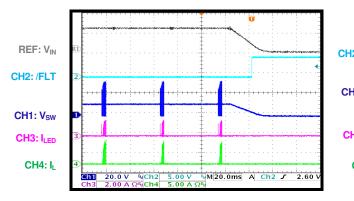

Two-Step Dimming

One or more LED short faults, shutdown

Two-Step Dimming

One or more LED short faults entry and recovery

MPQ2484 Rev. 1.0 9/8/2021 M

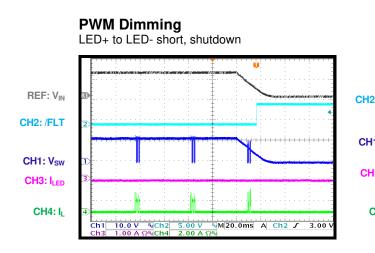

Buck-boost mode, 8 LEDs,  $V_{LED}$  = 24V,  $V_{IN}$  = 12V,  $f_{SW}$  = 410kHz, L = 10µH,  $T_A$  = 25°C, unless otherwise noted.

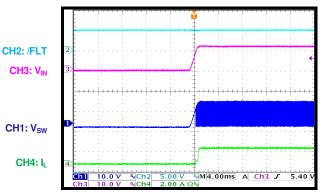

#### **PWM Dimming** LED+ to LED- short, steady state

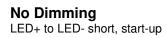

#### **PWM Dimming** LED+ to LED- short, start-up

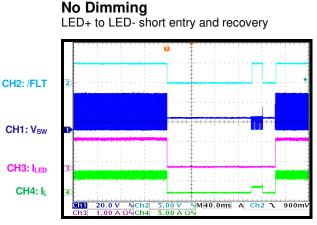

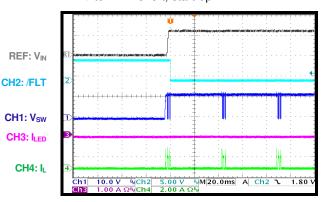

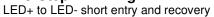

Buck-boost mode, 8 LEDs,  $V_{LED}$  = 24V,  $V_{IN}$  = 12V,  $f_{SW}$  = 410kHz, L = 10µH, T<sub>A</sub> = 25°C, unless otherwise noted.

#### Two-Step Dimming LED+ to LED- short, shutdown

#### Two-Step Dimming LED+ to LED- short entry and recovery

MPQ2484 Rev. 1.0 9/8/2021 MPS Pr

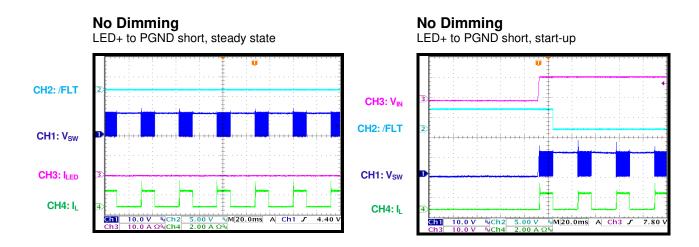

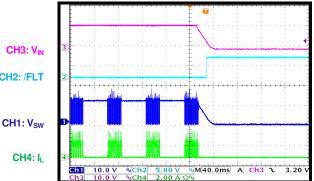

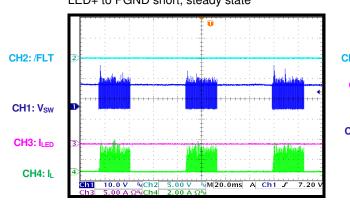

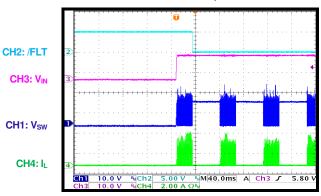

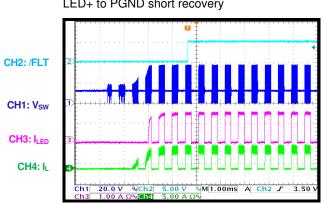

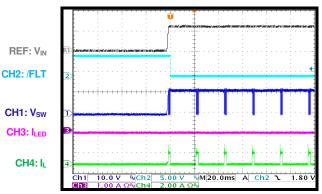

Buck-boost mode, 8 LEDs,  $V_{LED}$  = 24V,  $V_{IN}$  = 12V,  $f_{SW}$  = 410kHz, L = 10µH,  $T_A$  = 25°C, unless otherwise noted.

#### **No Dimming** LED+ to PGND short recovery

#### **PWM Dimming** LED+ to PGND short, steady state

#### **PWM Dimming** LED+ to PGND short, shutdown

# TYPICAL PERFORMANCE CHARACTERISTICS

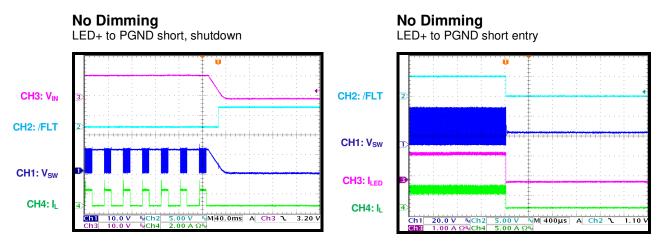

Buck-boost mode, 8 LEDs,  $V_{LED} = 24V$ ,  $V_{IN} = 12V$ ,  $f_{SW} = 410$ kHz, L = 10 $\mu$ H, T<sub>A</sub> = 25°C, unless otherwise noted.

**Two-Step Dimming** LED+ to PGND short, steady state

**Two-Step Dimming** LED+ to PGND short, start-up

Buck-boost mode, 8 LEDs,  $V_{LED}$  = 24V,  $V_{IN}$  = 12V,  $f_{SW}$  = 410kHz, L = 10\muH,  $T_A$  = 25°C, unless otherwise noted.

#### Two-Step Dimming LED+ to PGND short recovery

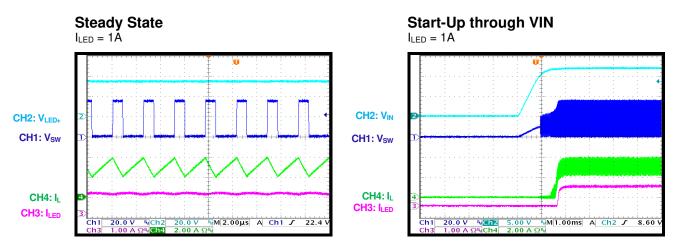

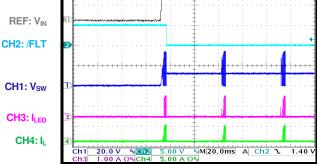

Boost mode, 12 LEDs,  $V_{\text{LED}}$  = 36V,  $V_{\text{IN}}$  = 12V,  $f_{\text{SW}}$  = 410kHz, L = 10µH,  $T_{\text{A}}$  = 25°C, unless otherwise noted.

Boost mode, 12 LEDs,  $V_{LED}$  = 36V,  $V_{IN}$  = 12V,  $f_{SW}$  = 410kHz, L = 10µH,  $T_A$  = 25°C, unless otherwise noted.

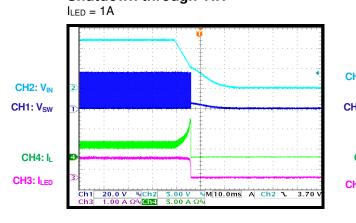

Shutdown through VIN

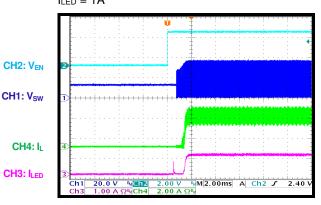

Start-Up through EN ILED = 1A

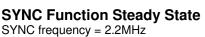

Boost mode, 12 LEDs,  $V_{\text{LED}}$  = 36V,  $V_{\text{IN}}$  = 12V,  $f_{\text{SW}}$  = 410kHz, L = 10µH,  $T_{\text{A}}$  = 25°C, unless otherwise noted.

**PWM Dimming Steady State**

Boost mode, 12 LEDs,  $V_{\text{LED}}$  = 36V,  $V_{\text{IN}}$  = 12V,  $f_{\text{SW}}$  = 410kHz, L = 10µH,  $T_{\text{A}}$  = 25°C, unless otherwise noted.

**Two-Step Dimming Steady State** Dimming frequency = 1.8kHz

Two-Step Dimming Start-up through VIN

Boost mode, 12 LEDs,  $V_{LED}$  = 36V,  $V_{IN}$  = 12V,  $f_{SW}$  = 410kHz, L = 10µH, T<sub>A</sub> = 25°C, unless otherwise noted.

#### No Dimming LED open fault, shutdown

MPQ2484 Rev. 1.0 9/8/2021 MPS

Boost mode, 12 LEDs,  $V_{\text{LED}}$  = 36V,  $V_{\text{IN}}$  = 12V,  $f_{\text{SW}}$  = 410kHz, L = 10µH,  $T_{\text{A}}$  = 25°C, unless otherwise noted.

# REF: VIN REF: VIN CH3: /FLT CH1: V<sub>SW</sub> CH2: VICS+ CH2: VICS+ CH4: IL Ch1: 20.0 V Wich2 50.0 V Width 2000 M (40000)

#### **PWM Dimming** LED open fault entry

Boost mode, 12 LEDs,  $V_{LED}$  = 36V,  $V_{IN}$  = 12V,  $f_{SW}$  = 410kHz, L = 10µH, T<sub>A</sub> = 25°C, unless otherwise noted.

Two-Step Dimming LED open fault, shutdown

Two-Step Dimming LED open fault entry

Two-Step Dimming

**No Dimming** One or more LED short fault, start-up

CH2: /FLT

CH3: I<sub>LED</sub> CH4: I<sub>L</sub>

CH1: Vsw

MPQ2484 Rev. 1.0 9/8/2021

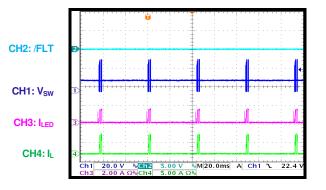

Boost mode, 12 LEDs,  $V_{LED}$  = 36V,  $V_{IN}$  = 12V,  $f_{SW}$  = 410kHz, L = 10µH, T<sub>A</sub> = 25°C, unless otherwise noted.

#### PWM Dimming

**PWM Dimming**

One or more LED short faults, steady state

PWM Dimming

#### **PWM Dimming**

One or more LED short faults entry and recovery

CH2: /FLT CH1: V<sub>SW</sub> CH3: I<sub>LED</sub> CH4: I<sub>L</sub> CH4: I<sub>L</sub> CH4: I<sub>L</sub> CH3: I<sub>LED</sub> CH4: I<sub>L</sub> CH4: I

#### MPQ2484 Rev. 1.0 9/8/2021 MPS

# **TYPICAL PERFORMANCE CHARACTERISTICS** (continued)

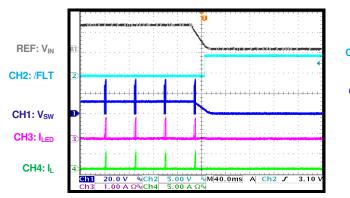

Boost mode, 12 LEDs,  $V_{\text{LED}}$  = 36V,  $V_{\text{IN}}$  = 12V,  $f_{\text{SW}}$  = 410kHz, L = 10µH,  $T_{\text{A}}$  = 25°C, unless otherwise noted.

Two-Step Dimming One or more LED short faults, start-up

Two-Step Dimming

One or more LED short faults, shutdown

One or more LED short faults entry and recovery

# **TYPICAL PERFORMANCE CHARACTERISTICS** (continued)

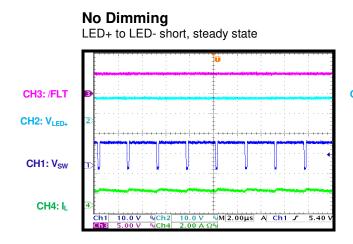

Boost mode, 12 LEDs,  $V_{\text{LED}}$  = 36V,  $V_{\text{IN}}$  = 12V,  $f_{\text{SW}}$  = 410kHz, L = 10µH,  $T_{\text{A}}$  = 25°C, unless otherwise noted.

CH2: /FLT CH1: V<sub>SW</sub> CH3: I<sub>LED</sub> CH4: I<sub>L</sub> CH4: I<sub>L</sub>

CH2: /FLT CH1: V<sub>SW</sub> CH3: ILED CH4: IL CH4: **PWM Dimming** LED+ to LED- short, start-up

No Dimming

**PWM Dimming** LED+ to LED- short entry and recovery

# **TYPICAL PERFORMANCE CHARACTERISTICS** (continued)

Boost mode, 12 LEDs,  $V_{LED} = 36V$ ,  $V_{IN} = 12V$ ,  $f_{SW} = 410$ kHz,  $L = 10\mu$ H,  $T_A = 25^{\circ}$ C, unless otherwise noted.

**Two-Step Dimming**

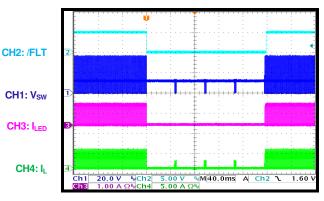

# FUNCTIONAL BLOCK DIAGRAM

# **OPERATION**

The MPQ2484 converter can support three single-channel LED driver configurations: boost mode, buck-boost mode, and low-side buck mode.

## **VCC Regulator**

An internal low-dropout (LDO) regulator outputs a nominal 8.5V VCC supply from the VIN pin. This supplies power for both control blocks, as well as the N-channel MOSFET's gate driver. The VCC regulator features a 100mA current limit to prevent short circuits on the VCC rail. Place a 1µF to 10µF, low-ESR ceramic bypass capacitor from VCC to PGND.

The VCC supply cannot maintain an 8.5V output once V<sub>IN</sub> drops below 8.5V. VCC can only be powered from VIN if  $V_{IN}$  is exceeds 8.5V, with the highest driver capacity possible. When V<sub>IN</sub> is below 8.5V, choose a MOSFET with a lower V<sub>GS TH</sub>. VCC can also be powered by an external auxiliary supply that meets its voltage limit.

## Under-Voltage Lockout (UVLO)

Under-voltage lockout (UVLO) prevents the device (and certain blocks) from operating at an insufficient supply voltage. There are three internal, fixed UVLO comparators that monitor  $V_{IN}$ ,  $V_{CC}$ , and  $V_{ICS+}$ .

The MPQ2484 stops switching if either  $V_{\text{IN}}$  or V<sub>CC</sub> falls below their respective UVLO threshold. Because the dimming P-channel MOSFET driver is powered from V<sub>ICS+</sub>, this MOSFET shuts down if V<sub>ICS+</sub> drops below its UVLO threshold.

If  $V_{IN}$  falls below 3.9V, all switching is disabled. Then the COMP voltage (V<sub>COMP</sub>) is pulled down until V<sub>IN</sub> exceeds 4.15V.

Similarly, if  $V_{CC}$  drops below 3.9V, switching is disabled and V<sub>COMP</sub> is then pulled down until Vcc exceeds 4.135V.

Since  $V_{CC}$  is the internal LDO output from VIN, the actual  $V_{CC}$  is determined by  $V_{IN}$  and the dropout voltage of the VCC regulator. The dropout voltage depends on the load current drawn from VCC. For applications with a higher switching frequency (fsw) or larger MOFFET driving capacity demand, there may be a rise in the VCC regulator's dropout voltage. If this occurs, V<sub>CC</sub> may reach its UVLO threshold before V<sub>IN</sub> when V<sub>IN</sub> drops.

If the converter's output voltage ( $V_{ICS+}$ ) drops below 8.5V, DIMO is pulled up to ICS+ to turn off the dimming P-channel MOSFET until VICS+ exceeds 8.7V. If V<sub>ICS+</sub> UVLO occurs, the device's performance is not affected.

In buck mode, VICS+ provides the input voltage, so ensure that  $V_{IN}$  exceeds  $V_{ICS+UVLO}$  if the Pchannel MOSFET is supposed to act as a dimming MOSFET. Note that the device can still operate in dimming mode without the dimming MOSFET. A dimming P-channel MOSFET is recommended for buck mode.

#### On/Off Control and Custom Input Under-Voltage Lockout (UVLO)

When EN is driven above its logic threshold, the VCC regulator is activated. Once Vcc exceeds its UVLO threshold, it starts to provide power to the internal control circuitry, and the integrated EN comparator begins operating.

If the EN voltage exceeds the comparator's upper threshold (typically 1.5V), the converter is enabled, and soft start (SS) begins. If EN falls below the comparator's lower threshold, then the converter stops switching; however, the VCC regulator and control circuitry continue working until the EN pin is pulled below its logic threshold (<0.4V). Then the chip enters shutdown mode while consuming a tiny input current.

In addition to providing standard on/off logic control, the integrated EN comparator allows the EN pin to set a custom input UVLO threshold by placing an external resistor divider from VIN to GND (see Figure 5).

Figure 5: Custom Input UVLO Set by EN

## MPQ2484 - 75V, MULTI-TOPOLOGY LED CONTROLLER WITH MULTI DIM, AEC-Q100

The EN voltage is achieved via the resistor divider ratio from VIN. When the EN level reaches the UVLO rising threshold for the integrated EN comparator (about 1.5V), the converter starts switching. Meanwhile, an internal  $0.63\mu$ A pull-up current source is enabled to source current out of the EN pin.

When  $V_{IN}$  drops to disable the converter, the EN voltage must drop below the EN comparator's UVLO threshold. This means  $V_{IN}$  must stay above the UVLO threshold to overcome the hysteresis from the 0.63µA pull-up current, as well as the inherent 150mV hysteresis of the EN comparator. As a result, the actual hysteresis can be set independently without changing the rising UVLO threshold.

#### Start-Up

If both VIN and EN exceed their UVLO rising thresholds, the internal LDO starts to charge the VCC capacitor. As  $V_{CC}$  rises to reach its  $V_{CC}$  UVLO threshold, the internal control circuitry and reference block operate. Once  $V_{IN}$ ,  $V_{CC}$ , and EN are enabled, the MPQ2484 begins switching. Internal SS is implemented to prevent the converter's output voltage and current from overshooting during start-up. Once  $V_{ICS+}$  exceeds its UVLO threshold, the P-channel MOSFET is used as a dimming switch.

## VREF Output

The MPQ2484 provides a 2.37V reference voltage ( $V_{REF}$ ) on the VREF pin. Connect a 1nF to 10nF ceramic capacitor from VREF to GND. This reference can only source up to 80µA of current.  $V_{REF}$  can set the LSET level via a resistor divider for two-step dimming, or it can work as the pull-up source for the control pins to set a logic high input.  $V_{REF}$  is also the reference voltage for one or more internal LED shorts detection. If  $V_{REF}$  drops below its threshold, a short is triggered.

# High-Side Current-Sense (CS) Reference Setting

The LED current is sensed by the high-side sensing resistor connected between ICS+ and ICS-. The ICS+ pin is tied to the output of the converter in boost or buck-boost mode, and connected to the input in buck mode. The ICSpin, which is on the other side of the currentsense resistor, goes to the source of the Pchannel MOSFET. If there is no external dimming MOSFET, then ICS- is directly connected to the LED string anode (VLED+). The chip regulates the voltage across the sensing resistor to 100mV if the ISET voltage exceeds 2.2V.

The MPQ2484 features a configurable LED current reference by monitoring the voltage on the setting resistor connected between ISET and ground. This resistor can be placed on LED light board to adjust the current. To reduce the noise created by a long connection wire, it is recommended to place a small capacitor close to the ISET pin.

The biased current can also be tuned by tying a resistor from IREF ( $I_{REF} = V_{IREF} / R_{IREF}$ ) to ground. The current through the IREF resistor configures the biased current on ISET ( $I_{SET} = 100 \times I_{REF}$ ). This means that changing the value of the setting resistor can adjust the LED current reference. For the relationship between  $V_{ISET}$  and the internal reference voltage, see the Mode and Current-Sense Reference Selection section on page 43.

#### Power Converter

Typically, the converter works in fixedfrequency, peak current control mode. At the beginning of each switching cycle, the Nchannel MOSFET turns on at the rising edge of the clock. A resistor tied from the CS pin to GND senses the N-channel MOSFET's current signal.

To prevent subharmonic oscillations when the duty cycles exceeds 50%, a stabilizing ramp is added to the N-channel MOSFET current-sense signal to generate the inductor peak current information. When the inductor peak current reaches the value set by  $V_{COMP}$  (which is the output voltage of the error amplifier), the N-channel MOSFET turns off until the next switching clock begins. The current is also limited by the 400mV clamped voltage on the VCS pin. This sets the converter's maximum power.

## Error Amplifier (EA)

The MPQ2484 converter incorporates a lowoffset error amplifier (EA) to provide compensation for the control loop. The feedback signal and reference voltage provide two different modes to regulate the LED current. The feedback signal switches to the voltage on

the high-side sensing resistor between ICS+ and ICS-. The reference voltage is about 100mV, but it can be adjusted by the ISET pin.

The internal EA outputs an amplified signal to the external compensation network. This signal is the difference between  $V_{BFF}$  and the feedback voltage ( $V_{FB}$ ), and it indicates  $V_{COMP}$ . V<sub>COMP</sub> is connected to the PWM comparator to control the N-channel MOSFET's peak current, which is sensed by a sensing resistor connected between the source of N-channel MOSFET and ground. During the N-channel MOSFET's turn-on time, the CS pin outputs a current ramp. The current then flows through a resistor (R<sub>CS</sub>) that is placed between the CS pin and the N-channel FET current-sense resistor. This current ramp configures slope compensation.

Once the CS level reaches  $V_{\text{COMP}}$ , the converter pulls down NGATE to turn off the N-channel MOSFET.

Note that the EA's transconductance is nonlinear. The EA's transconductance has a greater source ability than sink ability. Transconductance can help speed up LED regulation when PWM dimming is initiated.

## Oscillator

The MPQ2484's  $f_{SW}$  can be configured between 100kHz and 2.2MHz by connecting a resistor ( $R_{FSET}$ ) between the FSET pin and GND.  $R_{FSET}$  can be calculated with Equation (1):

$$R_{FSET}(k\Omega) = \frac{8333}{f_{SW}(kHz)}$$

(1)

For EMI-sensitive applications, the switching clock can be synchronized to an external clock signal that is applied to the SYNC pin. Once the external clock signal is added on the SYNC pin, the FSET setting no longer has any effect.

Ensure that the external clock signal frequency is at least 10% greater than the oscillator frequency set by FSET. If the external sync signal is lost, the internal oscillator controls the switching rate, and  $f_{SW}$  returns to the value set by FSET. This allows the switching clock to operate with intermittent synchronization signals.

# Mode and Current-Sense Reference Selection

Table 1 lists different modes that can beselected using the DMODE and ISETMD pins.

Table 1: Mode Selection

|        | DMODE (High)                                   | DMODE (Low)                                    |  |

|--------|------------------------------------------------|------------------------------------------------|--|

| ISETMD | Normal operation mode: The LED current can     | Dimming switch mode: The LED current can       |  |

| (High) | be configured up to 100% of its nominal value. | be configured up to 100% of its nominal value. |  |

| ISETMD | Normal operation mode: The LED current can     | Dimming switch mode: The LED current can       |  |

| (Low)  | be configured up to 200% of its nominal value. | be configured up to 200% of its nominal value. |  |

The DMODE pin selects whether the device operates in normal operation mode or dimming switch mode. If the logic is high, the dimming Pchannel MOSFET is not used. If DMODE is pulled down to GND, the dimming P-channel MOSFET is used as a dimming switch. The Pchannel MOSFET turns off during dimming, or if any fault is triggered. The ISETMD pin sets the internal reference voltage. If ISETMD is pulled down to GND, the ISET voltage rises from 0.6V to 1.8V, and the reference voltage rises linearly from 0mV to 200mV, which can be used for analog dimming. When the ISET voltage exceeds 2.3V, the reference stays at about 100mV (see Figure 6 on page 44).

Figure 6: ISETMD is Low

When the ISETMD pin is logic high, and the voltage on ISET rises from 0.6V to 1.2V, the reference voltage rises linearly from 0mV to 100mV. When the ISET voltage exceeds 1.2V, the reference voltage stays at about 100mV (see Figure 7).

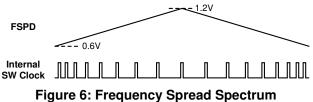

#### Frequency Spread Spectrum (FSS)

To optimize EMI performance, the MPQ2484 provides a frequency spread spectrum (FSS) function. Connect a capacitor from the FSPD pin to GND. The internal source and sink currents (both 100µA) charges or discharges the capacitor repeatedly to generate a stable triangular ramp waveform between 0.6V and 1.2V. This triangular ramp voltage works with the resistor connected between the FSPD and FSET pins to generate a current. The current flowing out from the FSET pin can dither fsw for frequency spread spectrum. The spread spectrum frequency (f<sub>SS</sub>) can be estimated with Equation (2):

$$f_{SS} = \frac{I_{FSPD}}{2 \times C_{FSPD} \times \Delta U}$$

(2)

Where I<sub>FSPD</sub> is the FSPD source/sink current (100µA), C<sub>ESPD</sub> is the capacitor between FSPD and GND, and  $\Delta U = 0.6V$  (1.2V - 0.6V).

The spread spectrum scope ( $\Delta f_{SS}$ ) can be calculated with Equation (3):

$$\Delta f_{SS} = f_{SW} \times \frac{R_{FSET}}{R_{FSPD}}$$

(3)

Where R<sub>FSPD</sub> is the resistor between FSPD and FSET.

The  $f_{SW}$  scope is between ( $f_{SW}$  -  $\Delta f_{SS}$ ) and  $f_{SW}$ . For example, if fsw = 400kHz, C<sub>FSPD</sub> = 3.3nF,  $R_{FSET} = 21k\Omega$ , and  $R_{FSPD} = 200k\Omega$ , then  $f_{SS}$  is 20kHz and fsw is dithered from 350kHz to 400kHz.

Figure 8 shows FSS operation.

Figure 8: Frequency Spread Spectrum

Figure 9 shows FSS waveforms.

**Waveforms**

The modulation frequency should be lower than the oscillator frequency set by FSET by a minimum factor of 10.

If an external clock signal applied to the SYNC pin, the FSS mechanism is screened. Remove RESPD if FSS is disabled.

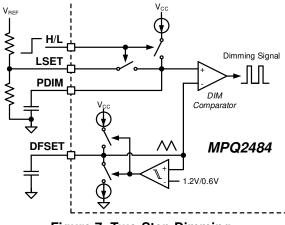

#### **Two-Step Dimming**

Connect a bypass capacitor from PDIM to GND for two-step dimming mode. The two-step dimming frequency can be configured by placing a capacitor between the DFSET pin and GND. The internal source and sink currents charge and discharge the capacitor repeatedly to generate a stable triangular ramp waveform between 0.6V and 1.2V. The two-step dimming frequency ( $f_{\text{DIM}}$ ) can be estimated with Equation (4):

$$f_{\text{DIM}} = \frac{I_{\text{DFSET}}}{2 \times C_{\text{DFSET}} \times \Delta U}$$

(4)

Where  $I_{DFSET}$  is the source/sink current (100µA),  $C_{DFSET}$  is the capacitor between DFSET and GND, and  $\Delta U = 0.6V$  (1.2V - 0.6V).

The two-step dimming duty  $(D_{\text{DIM}})$  can be calculated with Equation (5):

$$D_{\text{DIM}} = \frac{V_{\text{LSET}} - 0.6}{1.2 - 0.6}$$

(5)

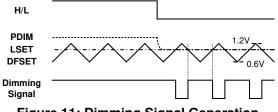

Where  $V_{LSET}$  is the LSET pin voltage. Figure 10 shows two-step dimming.

Figure 7: Two-Step Dimming

If the H/L pin is pulled up to a logic high input after two-step dimming is set, then the positive input of the DIM comparator is disconnected from the LSET pin. The internal pull-up current source charges the PDIM capacitor to 2V. The DIM comparator outputs a 100% duty cycle dimming signal, and the LED current is regulated at full scale.

If the H/L pin is set to logic low, the internal pullup current turns off, and the positive input of the DIM comparator is connected to the LSET pin. The LSET level can be set between 0.6V and 1.2V via an external resistor divider connected from VREF to the LSET pin. When compared to the DFSET triangular ramp waveform, the LSET voltage determines the duty cycle of the final dimming signal (see Figure 11).

Figure 11: Dimming Signal Generation

The MPQ2484 can switch between full-scale LED brightness and lower levels via the H/L signal.

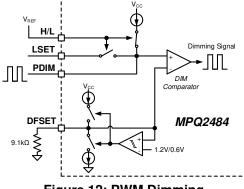

#### **PWM Dimming**

PWM dimming can be achieved by driving the PDIM pin with a pulsating voltage source. Tie the H/L pin to VREF, and connect a  $8.06k\Omega$  resistor from the DFSET pin to GND (V<sub>DFSET</sub> is always  $100\mu$ A x  $8.06k\Omega = 0.806$ V) to disable the dimming oscillator (see Figure 12).

Figure 12: PWM Dimming

When the voltage on the PDIM pin exceeds 1.2V (meaning it exceeds  $V_{DFSET}$ ), the DIM comparator outputs a dimming on signal. When the PDIM voltage drops below 0.4V (below  $V_{DFSET}$ ), a dimming off signal is generated. Ensure that the minimum PWM dimming on time is longer than 60µs, or the part will stop switching.

#### Analog Dimming

Analog dimming can be achieved via the ISETMD and ISET pins, which set the internal reference voltage. When the ISETMD pin is pulled down to GND, provide a linear voltage between 0.6V and 1.8V for the ISET pin. The reference voltage rises linearly from 0mV to 200mV.

#### **Dimming Performance**

The DIM comparator outputs a dimming signal to control the pulse width that modulates the output LED current. When the dimming signal is logic high, the MPQ2484 is enabled and the dimming P-channel MOSFET turns on. When the dimming signal is logic-low, the device stops switching and the dimming P-channel MOSFET turns off.

When the dimming signal is low, the internal EA's output is disconnected from both the PWM comparator and the COMP pin. The COMP level can remain constant when dimming is off.

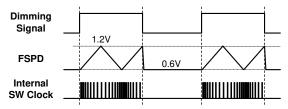

The dimming signal also affects the switching oscillator and FSS functions. If  $f_{SW}$  is set by the FSET pin, both the oscillator and FSS mechanisms are disabled when the dimming signal is off and the FSPD voltage is pulled down to 0.6V. When a dimming signal is received, the functions are reinitiated. This protocol can force the converter's switching clock to be synchronized by the dimming signal, which ensures each dimming cycle performs consistently (see Figure 13).

#### **Over-Voltage Protection (OVP)**

The MPQ2484 monitors the voltage across the LED strings. A resistor divider is connected from ICS+ to the cathode of the LED string, and the tap of the divider is tied to the VFB pin. When the differential voltage between ICS+ and VFB exceeds 1.17V, the converter stops switching, but the dimming P-channel MOSFET maintains its original status. If an open LED

fault is triggered at the same time, then the Pchannel MOSFET is disabled and the chip runs as it would during a fault condition. When the differential voltage drops below 1.02V, the overvoltage (OV) condition is removed, and the MPQ2484 restarts and resumes normal operation.

#### **Over-Current Protection (OCP)**

The cycle-by-cycle current limit restricts the N-channel MOSFET's maximum current via the current-sense resistor on the CS pin.  $V_{CS}$  is typically400mV.

#### **Open LED Protection**

If the LED string is disconnected from the system, the device cannot obtain the LED current information, and the converter automatically increases the output voltage until OVP is triggered.

If the dimming P-channel MOSFET is on when an OV condition is detected, the device checks the differential voltage between ICS+ and VLED+ to avoid start-up voltage overshoot. If the differential voltage is below 50mV, then an open LED fault occurs.

If the system operates without a dimming Pchannel MOSFET when an OV condition occurs, the device checks the voltage on the LED current-sense resistor between ICS+ and ICS-. If the voltage is below 50mV, then an open LED fault occurs.

If an open LED fault occurs, the converter and dimming P-channel MOSFET turn off, V<sub>COMP</sub> is pulled down to ground, and /FLT asserts. The fault recovery counter starts when the differential voltage between ICS+ and VFB drops below 1.02V. After 8192 consecutive clock cycles, the system restarts again with a soft start. During the recovery cycle, the /FLT signal stays latched. /FLT resets after 30µs without a fault.

# LED String Anode/Cathode to Battery/Ground Short Protection

If an LED short fault is detected, then the converter and dimming P-channel MOSFET turn off,  $V_{COMP}$  is pulled down to ground, and /FLT asserts. After 8192 consecutive clock cycles, the system restarts again with a soft start. During the recovery cycle, the /FLT signal

remains latched. /FLT resets once 30µs pass with no fault present.

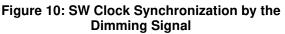

## **One or More LED Short Protection**

In certain cases, only one LED may short, but it is possible for several LEDs to short. The MPQ2484 features one or more LEDs short detection to guarantee that the light source stays sufficiently illuminated. There are two conditions that trigger one or more LED short protection:

- |V<sub>LEDSC1</sub> V<sub>LEDSC2</sub>| > 180mV for 32 consecutive clock cycles

- |V<sub>LEDSC1</sub> V<sub>LEDSC2</sub>| > 80mV for 4096 consecutive clock cycles