### FEATURES

- Simple Voltage Conversion, Including

- Negative Converter

- Voltage Doubler

- Wide Operating Range...1.5 V to 10 V

- Requires Only Two External (Noncritical) Capacitors

- No External Diode Over Full Temperature and Voltage Range

- Typical Open-Circuit Voltage Conversion Efficiency...99.9%

- Typical Power Efficiency...98%

- Full Testing at 3 V

# APPLICATIONS

- On-Board Negative Supplies

- Data-Acquisition Systems

- Portable Electronics

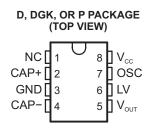

NC - No internal connection

# DESCRIPTION/ORDERING INFORMATION

The TL7660 is a CMOS switched-capacitor voltage converter that perform supply-voltage conversions from positive to negative. With only two noncritical external capacitors needed for the charge pump and charge reservoir functions, an input voltage within the range from 1.5 V to 10 V is converted to a complementary negative output voltage of -1.5 V to -10 V. The device can also be connected as a voltage doubler to generate output voltages up to 18.6 V with a 10-V input.

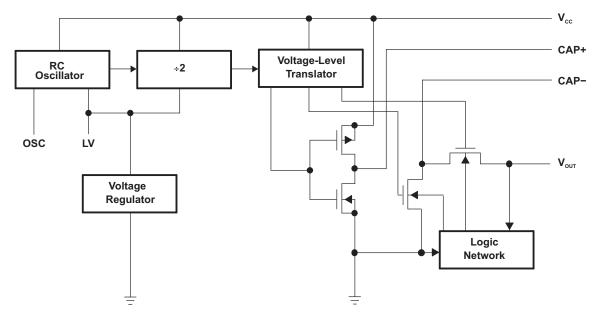

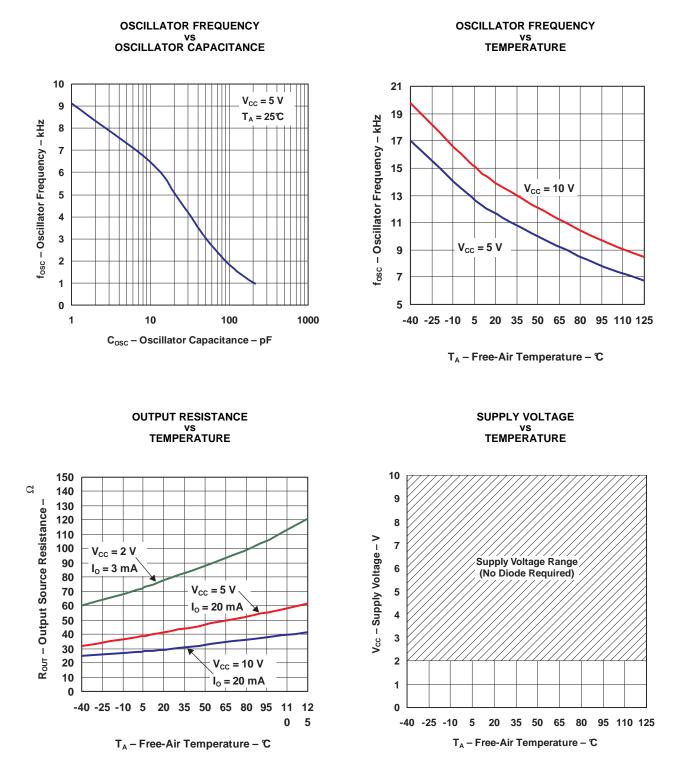

The basic building blocks of the IC include a linear regulator, an RC oscillator, a voltage-level translator, and four power MOS switches. To ensure latch-up-free operation, the circuitry automatically senses the most negative voltage in the device and ensures that the N-channel switch source-substrate junctions are not forward biased. The oscillator frequency runs at a nominal 10 kHz (for  $V_{CC} = 5$  V), but that frequency can be decreased by adding an external capacitor to the oscillator (OSC) terminal or increased by overdriving OSC with an external clock.

For low-voltage operation ( $V_{IN}$  < 3.5 V), LV should be tied to GND to bypass the internal series regulator. Above 3.5 V, LV should be left floating to prevent device latchup.

The TL7660C is characterized for operation over a free-air temperature range of  $-40^{\circ}$ C to  $85^{\circ}$ C. The TL7660I is characterized for operation over a free-air temperature range of  $-40^{\circ}$ C to  $125^{\circ}$ C.

| T <sub>A</sub> | PACK             | AGE <sup>(1)</sup> | ORDERABLE PART NUMBER | TOP-SIDE MARKING <sup>(2</sup> |  |  |

|----------------|------------------|--------------------|-----------------------|--------------------------------|--|--|

|                |                  | Reel of 250        | TL7660CDGKT           | TN4                            |  |  |

|                | MSOP/VSSOP – DGK | Reel of 2500       | TL7660CDGKR           | TM                             |  |  |

| –40°C to 85°C  | PDIP – P         | Tube of 50         | TL7660CP              | TL7660CP                       |  |  |

|                | SOIC – D         | Tube of 75         | TL7660CD              | - 7660C                        |  |  |

|                | 5010 - 0         | Reel of 2500       | TL7660CDR             | - 70000                        |  |  |

|                |                  | Reel of 250        | TL7660IDGKT           | TN                             |  |  |

|                | MSOP/VSSOP – DGK | Reel of 2500       | TL7660IDGKR           | - TN_                          |  |  |

| –40°C to 125°C | PDIP – P         | Tube of 50         | TL7660IP              | TL7660IP                       |  |  |

|                | SOIC - D         | Tube of 75         | TL7660ID              | 76601                          |  |  |

|                | 5010 - 0         | Reel of 2500       | TL7660IDR             | 76601                          |  |  |

### **ORDERING INFORMATION**

(1) Package drawings, standard packing quantities, thermal data, symbolization, and PCB design guidelines are available at www.ti.com/sc/package.

(2) DGK: The actual top-side marking has one additional character that indicates the assembly/test site.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

#### FUNCTIONAL BLOCK DIAGRAM

## Absolute Maximum Ratings<sup>(1)</sup>

over operating free-air temperature range (unless otherwise noted)

|                  |                                               |                         | MIN                   | MAX                   | UNIT |

|------------------|-----------------------------------------------|-------------------------|-----------------------|-----------------------|------|

| V <sub>CC</sub>  | Supply voltage                                | TL7660                  |                       | 10.5                  | V    |

| V                | OSC and $IV$ input voltage range $(2)$        | V <sub>CC</sub> < 5.5 V | -0.3                  | V <sub>CC</sub> + 0.3 | V    |

| VI               | OSC and LV input voltage range <sup>(2)</sup> | V <sub>CC</sub> > 5.5 V | V <sub>CC</sub> – 5.5 | V <sub>CC</sub> + 0.3 | v    |

| $I_{LV}$         | Current into LV <sup>(2)</sup>                | V <sub>CC</sub> > 3.5 V |                       | 20                    | μA   |

| t <sub>OS</sub>  | Output short-circuit duration                 | $V_{SUPPLY} \pm 5.5 V$  |                       | Continuous            |      |

|                  |                                               | D package               |                       | 97                    |      |

| $\theta_{JA}$    | Package thermal impedance <sup>(3)(4)</sup>   | DGK package             |                       | 172                   | °C/W |

|                  |                                               | P package               |                       | 85                    |      |

| TJ               | Junction temperature                          |                         |                       | 150                   | °C   |

| T <sub>stg</sub> | Storage temperature range                     |                         | -55                   | 150                   | °C   |

(1) Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) Connecting any input terminal to voltages greater than V<sub>CC</sub> or less than GND may cause destructive latchup. It is recommended that no inputs from sources operating from external supplies be applied prior to power up of the TL7660.

Maximum power dissipation is a function of T<sub>J</sub>(max), θ<sub>JA</sub>, and T<sub>A</sub>. The maximum allowable power dissipation at any allowable ambient (3) temperature is  $P_D = (T_J(max) - T_A)/\theta_{JA}$ . Operating at the absolute maximum  $T_J$  of 150°C can affect reliability. The package thermal impedance is calculated in accordance with JESD 51-7.

(4)

# **Recommended Operating Conditions**

|                 |                                               |         | MIN | MAX | UNIT |

|-----------------|-----------------------------------------------|---------|-----|-----|------|

| V <sub>CC</sub> | Supply voltage                                | TL7660  | 1.5 | 10  | V    |

| -               | T <sub>A</sub> Operating free-air temperature | TL7660C | -40 | 85  | °C   |

| IA              |                                               | TL7660I | -40 | 125 |      |

# **Electrical Characteristics**

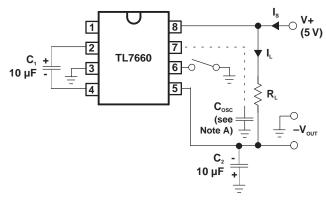

$V_{CC} = 5 \text{ V}, \text{ } C_{OSC} = 0, \text{ } \text{LV} = \text{Open}, \text{ } \text{T}_{A} = 25^{\circ}\text{C} \text{ (unless otherwise noted) (see Figure 1)}$

|                                           | PARAMETER                                | TEST CONDITIONS                      | T <sub>A</sub> <sup>(1)</sup> | MIN | TYP  | MAX | UNIT |

|-------------------------------------------|------------------------------------------|--------------------------------------|-------------------------------|-----|------|-----|------|

|                                           |                                          |                                      | 25°C                          |     | 45   | 110 |      |

| I <sub>CC</sub>                           | Supply current                           | $R_L = \infty$                       | -40°C to 85°C                 |     |      | 120 | μA   |

|                                           |                                          |                                      | -40°C to 125°C                |     |      | 135 |      |

| V <sub>CC,LOW</sub>                       | Supply voltage range (low)               | $R_L = 10 \text{ k}\Omega, LV = GND$ | Full range                    | 1.5 |      | 3.5 | V    |

| V <sub>CC,HIGH</sub>                      | Supply voltage range (high)              | $R_L = 10 \text{ k}\Omega$ , LV Open | Full range                    | 3   |      | 10  | V    |

|                                           |                                          |                                      | 25°C                          |     | 45   | 70  |      |

|                                           |                                          | I <sub>O</sub> = 20 mA               | -40°C to 85°C                 |     |      | 85  |      |

| R <sub>OUT</sub> Output source resistance | Outrast annual secietaria                |                                      | -40°C to 125°C                |     |      | 135 | 0    |

|                                           |                                          | 25°C                                 |                               |     | 125  | Ω   |      |

|                                           | $V_{CC}$ = 2 V, $I_{O}$ = 3 mA, LV = GND | -40°C to 85°C                        |                               |     | 200  |     |      |

|                                           |                                          |                                      | -40°C to 125°C                |     |      | 250 |      |

| f <sub>OSC</sub>                          | Oscillator frequency                     |                                      | 25°C                          |     | 10   |     | kHz  |

|                                           | David a Wieles and                       | D. SLO                               | 25°C                          | 96  | 98   |     |      |

| $\eta_{POWER}$ Power efficiency           |                                          | $R_{L} = 5 k\Omega$                  | -40°C to 125°C                | 95  |      |     | %    |

|                                           |                                          | <b>D</b>                             | 25°C                          | 99  | 99.9 |     | 0/   |

| η <sub>νουτ</sub>                         | Voltage conversion efficiency            | $R_L = \infty$                       | –40°C to 125°C                | 99  |      |     | %    |

| 7                                         | O stills to a local data as              | V <sub>CC</sub> = 2 V                | 0500                          |     | 1    |     | MΩ   |

| Z <sub>OSC</sub>                          | Oscillator impedance                     | $V_{CC} = 5 V$                       | 25°C                          |     | 100  |     | kΩ   |

(1) Full range is  $-40^{\circ}$ C to  $85^{\circ}$ C for the TL7660C and  $-40^{\circ}$ C to  $125^{\circ}$ C for the TL7660I.

## **Electrical Characteristics**

$V_{CC}$  = 3 V,  $C_{OSC}$  = 0, LV = GND, (unless otherwise noted) (see Figure 1)

|                                           | PARAMETER                     | TEST CONDITIONS     | T <sub>A</sub> | MIN | TYP | MAX | UNIT |  |

|-------------------------------------------|-------------------------------|---------------------|----------------|-----|-----|-----|------|--|

|                                           |                               |                     | 25°C           |     | 24  | 50  |      |  |

| I <sub>CC</sub>                           | Supply current <sup>(1)</sup> | $R_L = \infty$      | –40°C to 85°C  |     |     | 60  | μA   |  |

|                                           |                               |                     | –40°C to 125°C |     |     | 75  |      |  |

|                                           |                               |                     | 25°C           |     | 60  | 100 |      |  |

| R <sub>OUT</sub> Output source resistance | I <sub>O</sub> = 10 mA        | -40°C to 85°C       |                |     | 110 | Ω   |      |  |

|                                           |                               |                     | –40°C to 125°C |     |     | 120 |      |  |

| ſ                                         | Oppillator fragmanau          | 0 0                 | 25°C           | 5   | 9   |     |      |  |

| f <sub>OSC</sub>                          | Oscillator frequency          | $C_{OSC} = 0$       | –40°C to 125°C | 3   |     |     | kHz  |  |

|                                           | Devues officiences            |                     | 25°C           | 96  | 98  |     | 0/   |  |

| $\eta_{POWER}$ Power efficiency           |                               | $R_{L} = 5 k\Omega$ | –40°C to 125°C | 95  |     |     | %    |  |

|                                           | Voltogo conversion officiency | P                   | 25°C           | 99  |     |     | 0/   |  |

| $\eta_{VOUT}$                             | Voltage conversion efficiency | $R_L = \infty$      | –40°C to 125°C | 99  |     |     | %    |  |

(1) Derate linearly above  $50^{\circ}$ C by  $5.5 \text{ mW/}^{\circ}$ C.

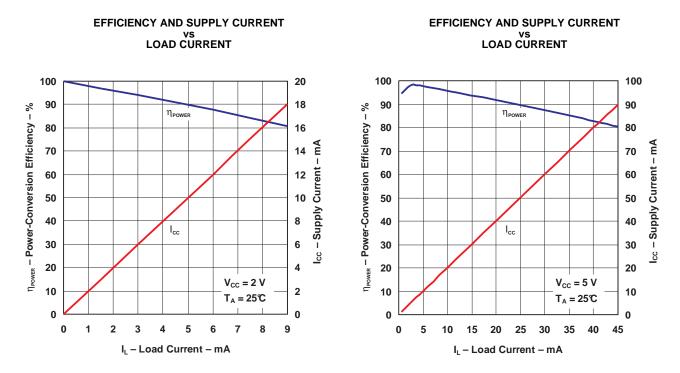

## **TYPICAL CHARACTERISTICS**

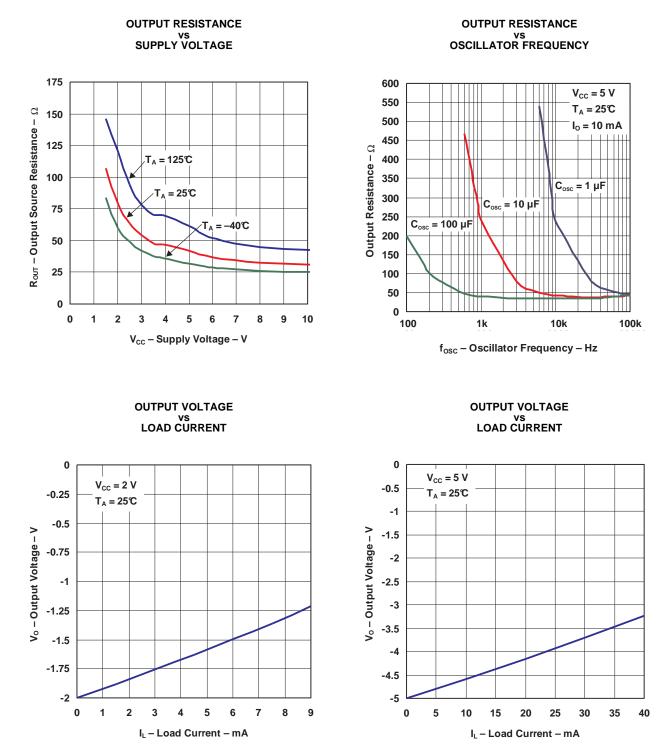

## **TYPICAL CHARACTERISTICS (continued)**

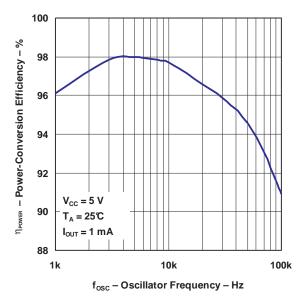

### **TYPICAL CHARACTERISTICS (continued)**

EFFICIENCY vs OSCILLATOR FREQUENCY

### **APPLICATION INFORMATION**

A. In the circuit, there is no external capacitor applied to terminal 7. However when device is plugged into a test socket, there is usually a very small but finite stray capacitance present on the order of 10 pF.

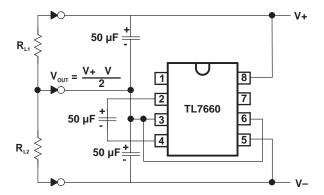

#### Figure 1. Test Circuit

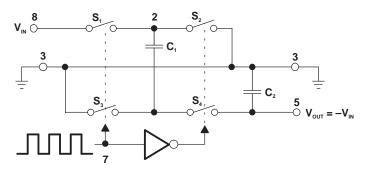

The TL7660 contains all the necessary circuitry to complete a negative voltage converter, with the exception of two external capacitors which may be inexpensive 10  $\mu$ F polarized electrolytic types. The mode of operation of the device may be best understood by considering Figure 2, which shows an idealized negative voltage converter. Capacitor C<sub>1</sub> is charged to a voltage, V<sub>CC</sub>, for the half cycle when switches S<sub>1</sub> and S<sub>3</sub> are closed. (Note: Switches S<sub>2</sub> and S<sub>4</sub> are open during this half cycle.) During the second half cycle of operation, switches S<sub>2</sub> and S<sub>4</sub> are closed, with S<sub>1</sub> and S<sub>3</sub> open, thereby shifting capacitor C<sub>1</sub> negatively by V<sub>CC</sub> volts. Charge is then transferred from C<sub>1</sub> to C<sub>2</sub> such that the voltage on C<sub>2</sub> is exactly V<sub>CC</sub>, assuming ideal switches and no load on C<sub>2</sub>. The TL7660 approaches this ideal situation more closely than existing non-mechanical circuits. In the TL7660, the four switches of Figure 2 are MOS power switches: S<sub>1</sub> is a p-channel device, and S<sub>2</sub>, S<sub>3</sub>, and S<sub>4</sub> are n-channel devices. The main difficulty with this design is that in integrating the switches, the substrates of S<sub>3</sub> and S<sub>4</sub> must always remain reverse biased with respect to their sources, but not so much as to degrade their ON resistances. In addition, at circuit start up and under output short circuit conditions (V<sub>OUT</sub> = V<sub>CC</sub>), the output voltage must be sensed and the substrate bias adjusted accordingly. Failure to accomplish this results in high power losses and probable device latchup. This problem is eliminated in the TL7660 by a logic network which senses the output voltage (V<sub>OUT</sub>) together with the level translators and switches the substrates of S<sub>3</sub> and S<sub>4</sub> to the correct level to maintain necessary reverse bias.

The voltage regulator portion of the TL7660 is an integral part of the anti-latchup circuitry; however, its inherent voltage drop can degrade operation at low voltages. Therefore, to improve low-voltage operation, the LV terminal should be connected to GND, disabling the regulator. For supply voltages greater than 3.5 V, the LV terminal must be left open to insure latchup proof operation and prevent device damage.

Figure 2. Idealized Negative-Voltage Converter

## **APPLICATION INFORMATION (continued)**

## **Theoretical Power Efficiency Considerations**

In theory, a voltage converter can approach 100% efficiency if certain conditions are met.

- The driver circuitry consumes minimal power.

- The output switches have extremely low ON resistance and virtually no offset.

- The impedances of the pump and reservoir capacitors are negligible at the pump frequency.

The TL7660 approaches these conditions for negative voltage conversion if large values of  $C_1$  and  $C_2$  are used.

Energy is only lost in the transfer of charge between capacitors if a change in voltage occurs. The energy lost is defined by:

$$\mathsf{E} = \frac{1}{2} \, \mathsf{C}_1 (\mathsf{V}_1^2 - \mathsf{V}_2^2)$$

Where  $V_1$  and  $V_2$  are the voltages on  $C_1$  during the pump and transfer cycles. If the impedances of  $C_1$  and  $C_2$  are relatively high at the pump frequency (see Figure 2) compared to the value of  $R_L$ , there is a substantial difference in the voltages  $V_1$  and  $V_2$ . Therefore, it is not only desirable to make  $C_2$  as large as possible to eliminate output voltage ripple but also to employ a correspondingly large value for  $C_1$  in order to achieve maximum efficiency of operation.

### Do's and Don'ts

- Do not exceed maximum supply voltages.

- Do not connect LV terminal to GND for supply voltages greater than 3.5 V.

- Do not short circuit the output to V<sub>CC</sub> supply for supply voltages above 5.5 V for extended periods, however, transient conditions including start-up are okay.

- When using polarized capacitors, the positive terminal of C<sub>1</sub> must be connected to terminal 2 of the TL7660, and the positive terminal of C<sub>2</sub> must be connected to GND.

- If the voltage supply driving the TL7660 has a large source impedance (25  $\Omega$  30  $\Omega$ ), then a 2.2- $\mu$ F capacitor from terminal 8 to ground may be required to limit rate of rise of input voltage to less than 2V/ $\mu$ s.

- Ensure that the output (terminal 5) does not go more positive than GND (terminal 3). Device latch up occurs under these conditions. A 1N914 or similar diode placed in parallel with C<sub>2</sub> prevents the device from latching up under these conditions (anode to terminal 5, cathode to terminal 3).

### **APPLICATION INFORMATION (continued)**

### **Typical Applications**

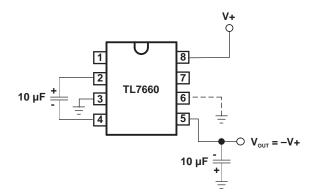

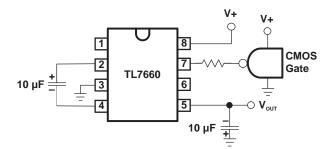

#### Simple Negative Voltage Converter

The majority of applications will undoubtedly utilize the TL7660 for generation of negative supply voltages. Figure 3 shows typical connections to provide a negative supply negative (GND) for supply voltages below 3.5 V.

Figure 3. Simple Negative-Voltage Converter

The output characteristics of the circuit in Figure 3 can be approximated by an ideal voltage source in series with a resistance. The voltage source has a value of  $-V_{CC}$ . The output impedance (R<sub>O</sub>) is a function of the ON resistance of the internal MOS switches (shown in Figure 2), the switching frequency, the value of C<sub>1</sub> and C<sub>2</sub>, and the ESR (equivalent series resistance) of C<sub>1</sub> and C<sub>2</sub>. A good first order approximation for R<sub>O</sub> is:

$$\begin{split} R_{O} &\approx 2(R_{SW1} + R_{SW3} + ESR_{C1}) + 2(R_{SW2} + R_{SW4} + ESR_{C1}) \\ R_{O} &\approx 2(R_{SW1} + R_{SW3} + ESR_{C1}) + 1/f_{PUMP}C_{1} + ESR_{C2} \end{split}$$

Where  $f_{PUMP} = f_{OSC}/2$ ,  $R_{SWX} = MOSFET$  switch resistance.

Combining the four RSWX terms as RSW, we see that:

$$R_{O} \approx 2 (R_{SW}) + 1/f_{PUMP}C_{1} + 4 (ESR_{C1}) + ESR_{C2}$$

$R_{SW}$ , the total switch resistance, is a function of supply voltage and temperature (See the Output Source Resistance graphs). Careful selection of  $C_1$  and  $C_2$  reduces the remaining terms, minimizing the output impedance. High value capacitors reduce the  $1/f_{PUMP}C_1$  component, and low ESR capacitors lower the ESR term. Increasing the oscillator frequency reduces the  $1/f_{PUMP}C_1$  term but may have the side effect of a net increase in output impedance when  $C_1 > 10 \ \mu$ F and there is no longer enough time to fully charge the capacitors every cycle. In a typical application where  $f_{OSC} = 10 \ \text{kHz}$  and  $C = C1 = C2 = 10 \ \mu$ F:

$$\begin{split} R_{O} &\approx 2(23) + 1/(5\times 10^{3})(10^{-5}) + 4(\text{ESR}_{\text{C1}}) + \text{ESR}_{\text{C2}} \\ R_{O} &\approx 46 + 20 + 5 \text{ (ESR}_{\text{C}}) \end{split}$$

Because the ESRs of the capacitors are reflected in the output impedance multiplied by a factor of 5, a high value could potentially swamp out a low  $1/f_{PUMP}C_1$  term, rendering an increase in switching frequency or filter capacitance ineffective. Typical electrolytic capacitors may have ESRs as high as 10  $\Omega$ .

# TL7660 CMOS VOLTAGE CONVERTER

SCAS794-JUNE 2006

### TEXAS INSTRUMENTS www.ti.com

## **APPLICATION INFORMATION (continued)**

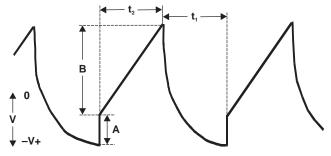

## **Output Ripple**

ESR also affects the ripple voltage seen at the output. The total ripple is determined by two voltages, A and B, as shown in Figure 4. Segment A is the voltage drop across the ESR of C<sub>2</sub> at the instant it goes from being charged by C<sub>1</sub> (current flow into C<sub>2</sub>) to being discharged through the load (current flowing out of C<sub>2</sub>). The magnitude of this current change is  $2 \times I_{OUT}$ , hence the total drop is  $2 \times I_{OUT} \times eSR_{C2}$  V. Segment B is the voltage change across C<sub>2</sub> during time t<sub>2</sub>, the half of the cycle when C<sub>2</sub> supplies current to the load. The drop at B is  $I_{OUT} \times t_2/C_2$  V. The peak-to-peak ripple voltage is the sum of these voltage drops:

$V_{RIPPLE} \approx (1/(2f_{PUMP}C_2) + 2(ESR_{C2})) \times I_{OUT}$

Again, a low ESR capacitor results in a higher performance output.

Figure 4. Output Ripple

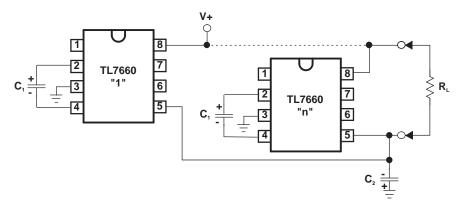

#### **Paralleling Devices**

Any number of TL7660 voltage converters may be paralleled to reduce output resistance (see Figure 5). The reservoir capacitor,  $C_2$ , serves all devices, while each device requires its own pump capacitor,  $C_1$ . The resultant output resistance would be approximately:

$R_{OUT} = R_{OUT}$  (of TL7660)/n (number of devices)

Figure 5. Paralleling Devices

## **APPLICATION INFORMATION (continued)**

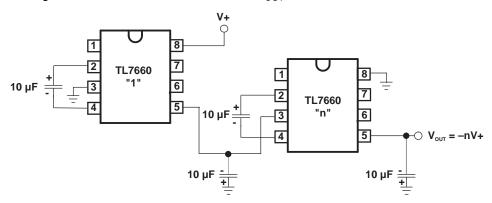

### **Cascading Devices**

The TL7660 may be cascaded as shown to produced larger negative multiplication of the initial supply voltage (see Figure 6). However, due to the finite efficiency of each device, the practical limit is 10 devices for light loads. The output voltage is defined by:

$$V_{OUT} = -n (V_{IN})$$

Where n is an integer representing the number of devices cascaded. The resulting output resistance would be approximately the weighted sum of the individual TL7660  $R_{OUT}$  values.

Figure 6. Cascading Devices for Increased Output Voltage

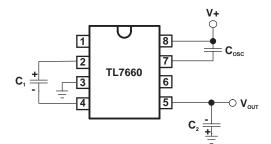

#### Changing the TL7660 Oscillator Frequency

It may be desirable in some applications, due to noise or other considerations, to increase the oscillator frequency. This is achieved by overdriving the oscillator from an external clock, as shown in Figure 7. To prevent possible device latchup, a 1-k $\Omega$  resistor must be used in series with the clock output. When the external clock frequency is generated using TTL logic, the addition of a 10-k $\Omega$  pullup resistor to V<sub>CC</sub> supply is required. Note that the pump frequency with external clocking, as with internal clocking, will be 1/2 of the clock frequency. Output transitions occur on the positive-going edge of the clock.

Figure 7. External Clocking

## TL7660 CMOS VOLTAGE CONVERTER SCAS794-JUNE 2006

## **APPLICATION INFORMATION (continued)**

It is also possible to increase the conversion efficiency of the TL7660 at low load levels by lowering the oscillator frequency (see Figure 8). This reduces the switching losses. However, lowering the oscillator frequency causes an undesirable increase in the impedance of the pump ( $C_1$ ) and reservoir ( $C_2$ ) capacitors; this is overcome by increasing the values of  $C_1$  and  $C_2$  by the same factor that the frequency has been reduced. For example, the addition of a 100-pF capacitor between terminal 7 (OSC) and  $V_{CC}$  lowers the oscillator frequency to 1 kHz from its nominal frequency of 10 kHz (a multiple of 10), and thereby necessitate a corresponding increase in the value of  $C_1$  and  $C_2$  (from 10  $\mu$ F to 100  $\mu$ F).

**Figure 8. Lowering Oscillator Frequency**

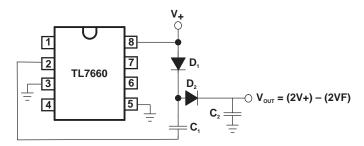

#### **Positive Voltage Doubling**

The TL7660 may be used to achieve positive voltage doubling using the circuit shown in Figure 9. In this application, the pump inverter switches of the TL7660 are used to charge  $C_1$  to a voltage level of  $V_{CC} - V_F$  (where  $V_{CC}$  is the supply voltage and  $V_F$  is the forward voltage drop of diode D1). On the transfer cycle, the voltage on  $C_1$  plus the supply voltage ( $V_{CC}$ ) is applied through diode  $D_2$  to capacitor  $C_2$ . The voltage thus created on  $C_2$  becomes ( $2V_{CC}$ ) – ( $2V_F$ ) or twice the supply voltage minus the combined forward voltage drops of diodes  $D_1$  and  $D_2$ .

The source impedance of the output  $(V_{OUT})$  depends on the output current.

Figure 9. Positive-Voltage Doubler

## **APPLICATION INFORMATION (continued)**

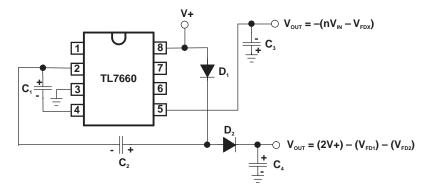

### **Combined Negative Voltage Conversion and Positive Supply Doubling**

Figure 10 combines the functions shown in Figure 3 and Figure 9 to provide negative voltage conversion and positive voltage doubling simultaneously. This approach would be, for example, suitable for generating +9 V and -5 V from an existing 5-V supply. In this instance, capacitors C<sub>1</sub> and C<sub>3</sub> perform the pump and reservoir functions, respectively, for the generation of the negative voltage, while capacitors C<sub>2</sub> and C<sub>4</sub> are pump and reservoir, respectively, for the doubled positive voltage. There is a penalty in this configuration that combines both functions, however, in that the source impedances of the generated supplies are somewhat higher, due to the finite impedance of the common charge pump driver at terminal 2 of the device.

Figure 10. Combined Negative-Voltage Converter and Positive-Voltage Doubler

#### Voltage Splitting

The bidirectional characteristics can also be used to split a higher supply in half (see Figure 11. The combined load is evenly shared between the two sides. Because the switches share the load in parallel, the output impedance is much lower than in the standard circuits, and higher currents can be drawn from the device. By using this circuit and then the circuit of Figure 6, 15 V can be converted (via 7.5 V, and -7.5 V) to a nominal -15 V, although with rather high series output resistance (~250  $\Omega$ ).

Figure 11. Splitting a Supply in Half

10-Dec-2020

# PACKAGING INFORMATION

| Orderable Device | Status<br>(1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan<br>(2) | Lead finish/<br>Ball material | MSL Peak Temp      | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|---------------|--------------|--------------------|------|----------------|-----------------|-------------------------------|--------------------|--------------|-------------------------|---------|

|                  |               |              |                    |      |                |                 | (6)                           |                    |              |                         |         |

| TL7660CD         | ACTIVE        | SOIC         | D                  | 8    | 75             | RoHS & Green    | NIPDAU                        | Level-1-260C-UNLIM | -40 to 85    | 7660C                   | Samples |

| TL7660CDGKR      | ACTIVE        | VSSOP        | DGK                | 8    | 2500           | RoHS & Green    | NIPDAU                        | Level-1-260C-UNLIM | -40 to 85    | ТМЕ                     | Samples |

| TL7660CDGKT      | ACTIVE        | VSSOP        | DGK                | 8    | 250            | RoHS & Green    | NIPDAU                        | Level-1-260C-UNLIM | -40 to 85    | ТМЕ                     | Samples |

| TL7660CDR        | ACTIVE        | SOIC         | D                  | 8    | 2500           | RoHS & Green    | NIPDAU                        | Level-1-260C-UNLIM | -40 to 85    | 7660C                   | Samples |

| TL7660CP         | ACTIVE        | PDIP         | Р                  | 8    | 50             | RoHS & Green    | NIPDAU                        | N / A for Pkg Type | -40 to 85    | TL7660CP                | Samples |

| TL7660ID         | ACTIVE        | SOIC         | D                  | 8    | 75             | RoHS & Green    | NIPDAU                        | Level-1-260C-UNLIM | -40 to 125   | 76601                   | Samples |

| TL7660IDGKR      | ACTIVE        | VSSOP        | DGK                | 8    | 2500           | RoHS & Green    | NIPDAU                        | Level-1-260C-UNLIM | -40 to 125   | TNE                     | Samples |

| TL7660IDGKT      | ACTIVE        | VSSOP        | DGK                | 8    | 250            | RoHS & Green    | NIPDAU                        | Level-1-260C-UNLIM | -40 to 125   | TNE                     | Samples |

| TL7660IDR        | ACTIVE        | SOIC         | D                  | 8    | 2500           | RoHS & Green    | NIPDAU                        | Level-1-260C-UNLIM | -40 to 125   | 76601                   | Samples |

| TL7660IP         | ACTIVE        | PDIP         | Р                  | 8    | 50             | RoHS & Green    | NIPDAU                        | N / A for Pkg Type | -40 to 125   | TL7660IP                | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

www.ti.com

# PACKAGE OPTION ADDENDUM

10-Dec-2020

(5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

<sup>(6)</sup> Lead finish/Ball material - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:**The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

Texas

STRUMENTS

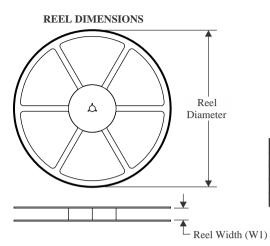

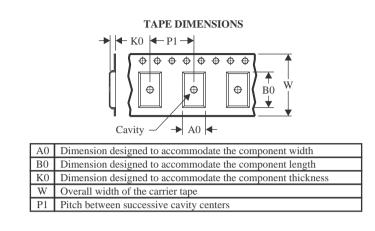

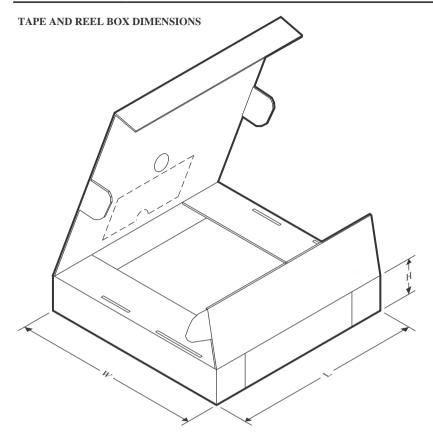

## TAPE AND REEL INFORMATION

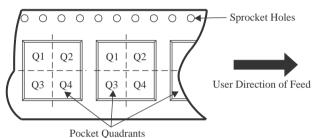

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| *All dimensions are nominal |                 |                    |   |      |                          |                          |            |            |            |            |           |                  |

|-----------------------------|-----------------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| Device                      | Package<br>Type | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

| TL7660CDGKR                 | VSSOP           | DGK                | 8 | 2500 | 330.0                    | 12.4                     | 5.3        | 3.3        | 1.3        | 8.0        | 12.0      | Q1               |

| TL7660CDGKT                 | VSSOP           | DGK                | 8 | 250  | 180.0                    | 12.4                     | 5.3        | 3.3        | 1.3        | 8.0        | 12.0      | Q1               |

| TL7660CDR                   | SOIC            | D                  | 8 | 2500 | 330.0                    | 12.4                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

| TL7660IDGKR                 | VSSOP           | DGK                | 8 | 2500 | 330.0                    | 12.4                     | 5.3        | 3.3        | 1.3        | 8.0        | 12.0      | Q1               |

| TL7660IDGKT                 | VSSOP           | DGK                | 8 | 250  | 180.0                    | 12.4                     | 5.3        | 3.3        | 1.3        | 8.0        | 12.0      | Q1               |

| TL7660IDR                   | SOIC            | D                  | 8 | 2500 | 330.0                    | 12.4                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

www.ti.com

# PACKAGE MATERIALS INFORMATION

3-Jun-2022

|--|

| Device      | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TL7660CDGKR | VSSOP        | DGK             | 8    | 2500 | 346.0       | 346.0      | 35.0        |

| TL7660CDGKT | VSSOP        | DGK             | 8    | 250  | 200.0       | 183.0      | 25.0        |

| TL7660CDR   | SOIC         | D               | 8    | 2500 | 340.5       | 336.1      | 25.0        |

| TL7660IDGKR | VSSOP        | DGK             | 8    | 2500 | 346.0       | 346.0      | 35.0        |

| TL7660IDGKT | VSSOP        | DGK             | 8    | 250  | 200.0       | 183.0      | 25.0        |

| TL7660IDR   | SOIC         | D               | 8    | 2500 | 340.5       | 336.1      | 25.0        |

# TEXAS INSTRUMENTS

www.ti.com

3-Jun-2022

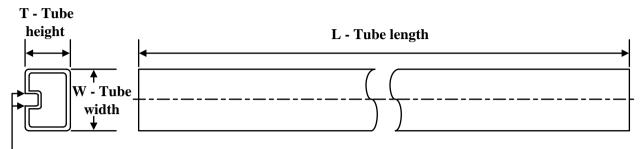

# TUBE

# - B - Alignment groove width

#### \*All dimensions are nominal

| Device   | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | T (µm) | B (mm) |

|----------|--------------|--------------|------|-----|--------|--------|--------|--------|

| TL7660CD | D            | SOIC         | 8    | 75  | 507    | 8      | 3940   | 4.32   |

| TL7660CP | Р            | PDIP         | 8    | 50  | 506    | 13.97  | 11230  | 4.32   |

| TL7660ID | D            | SOIC         | 8    | 75  | 507    | 8      | 3940   | 4.32   |

| TL7660IP | Р            | PDIP         | 8    | 50  | 506    | 13.97  | 11230  | 4.32   |

# **D0008A**

# **PACKAGE OUTLINE**

# SOIC - 1.75 mm max height

SMALL OUTLINE INTEGRATED CIRCUIT

NOTES:

1. Linear dimensions are in inches [millimeters]. Dimensions in parenthesis are for reference only. Controlling dimensions are in inches. Dimensioning and tolerancing per ASME Y14.5M.

- 2. This drawing is subject to change without notice.

- 3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed .006 [0.15] per side.

- This dimension does not include interlead flash.

Reference JEDEC registration MS-012, variation AA.

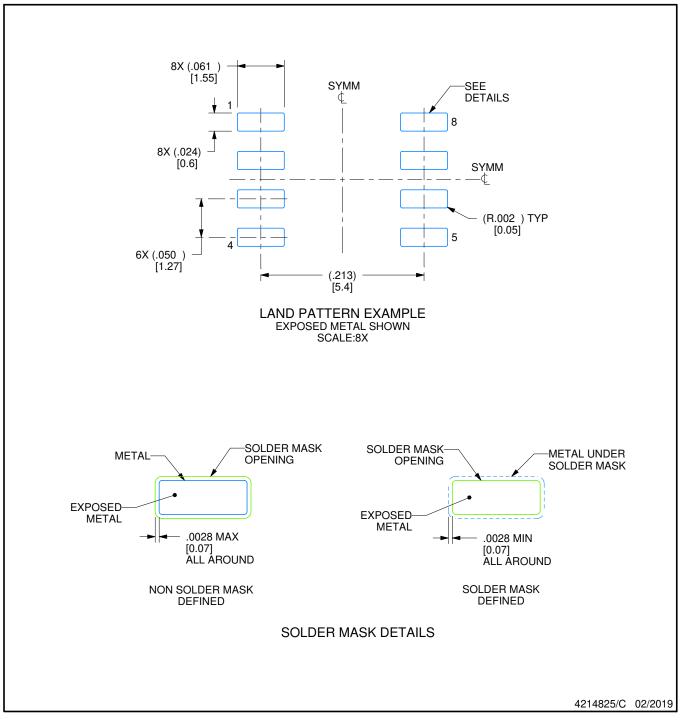

# D0008A

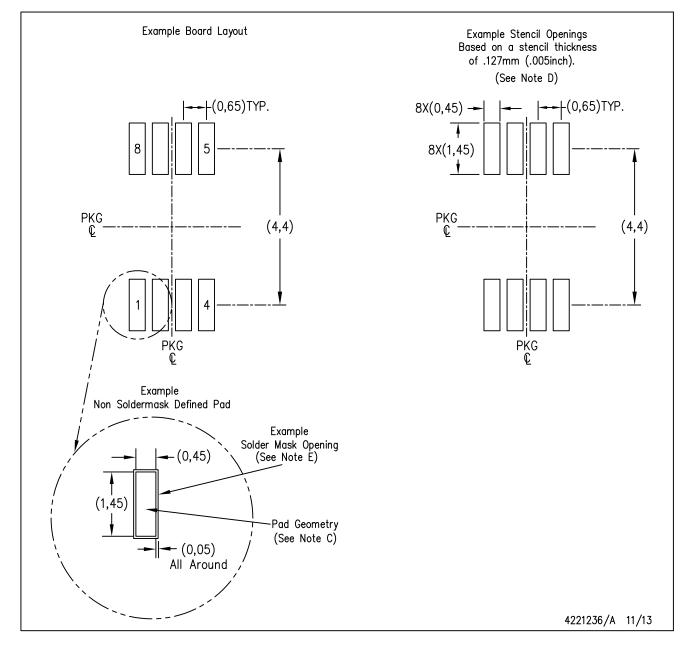

# **EXAMPLE BOARD LAYOUT**

# SOIC - 1.75 mm max height

SMALL OUTLINE INTEGRATED CIRCUIT

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

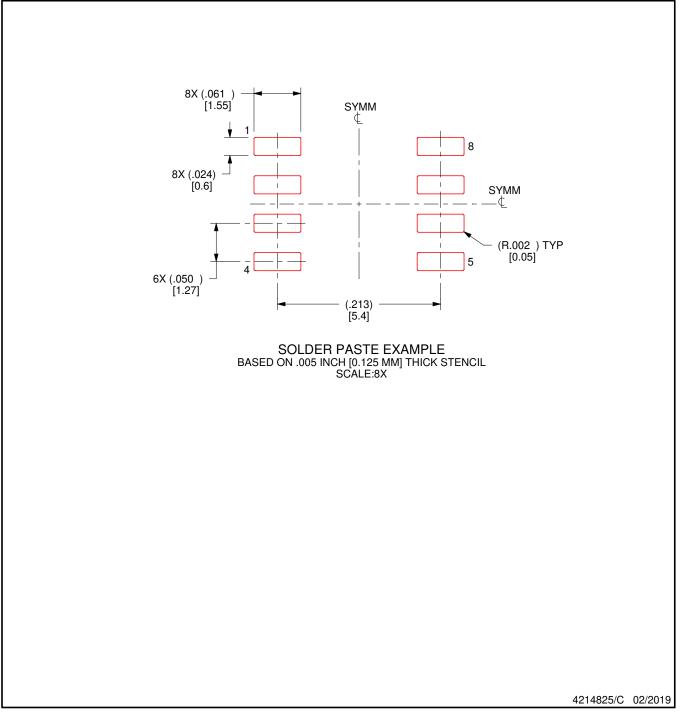

# D0008A

# **EXAMPLE STENCIL DESIGN**

# SOIC - 1.75 mm max height

SMALL OUTLINE INTEGRATED CIRCUIT

NOTES: (continued)

8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

9. Board assembly site may have different recommendations for stencil design.

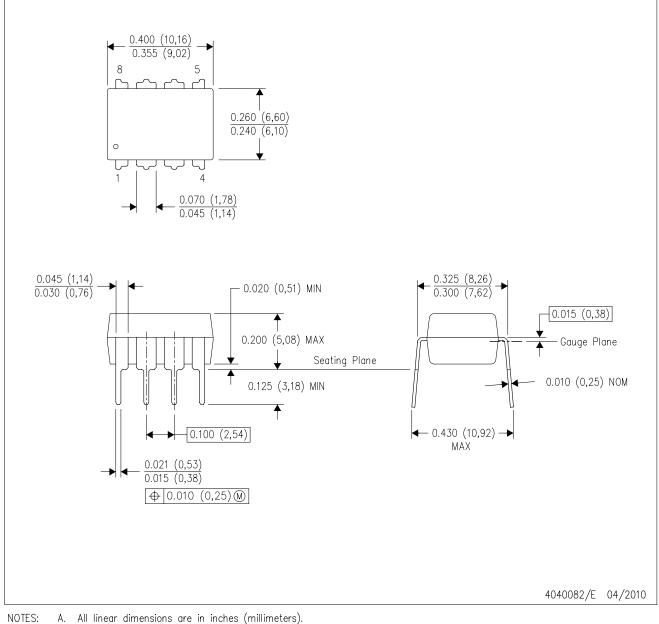

P(R-PDIP-T8)

PLASTIC DUAL-IN-LINE PACKAGE

- A. All linear dimensions are in inches (millimeters).B. This drawing is subject to change without notice.

- C. Falls within JEDEC MS-001 variation BA.

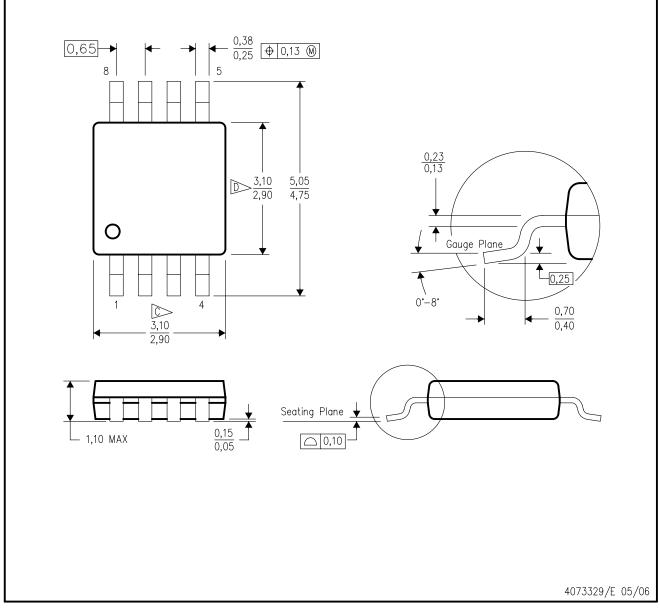

DGK (S-PDSO-G8)

PLASTIC SMALL-OUTLINE PACKAGE

NOTES: A. All linear dimensions are in millimeters.

B. This drawing is subject to change without notice.

Body length does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.15 per end.

- D> Body width does not include interlead flash. Interlead flash shall not exceed 0.50 per side.

- E. Falls within JEDEC MO-187 variation AA, except interlead flash.

# DGK (S-PDSO-G8)

# PLASTIC SMALL OUTLINE PACKAGE

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Publication IPC-7351 is recommended for alternate designs.

- D. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Refer to IPC-7525 for other stencil recommendations.

- E. Customers should contact their board fabrication site for solder mask tolerances between and around signal pads.

# IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated