# Dual 1:5 Differential Clock/Data Fanout Buffer

#### Features

- Dual sets of five ECL/PECL differential outputs

- Two ECL/PECL differential inputs

- · Hot-swappable/-insertable

- 50 ps output-to-output skew

- 150 ps device-to-device skew

- 500 ps propagation delay (typical)

- 0.8 ps RMS period jitter (max.)

- 1.5 GHz Operation (2.2 GHz max. toggle frequency)

- PECL mode supply range: V<sub>CC</sub> = 2.5V± 5% to 3.3V±5% with V<sub>EE</sub> = 0V

- + ECL mode supply range: V<sub>E E</sub> = -2.5V± 5% to -3.3V±5% with V<sub>CC</sub> = 0V

- Industrial temperature range: –40°C to 85°C

- 32-pin 1.4-mm TQFP package

- Temperature compensation like 100K ECL

- Pin compatible with MC100ES6210

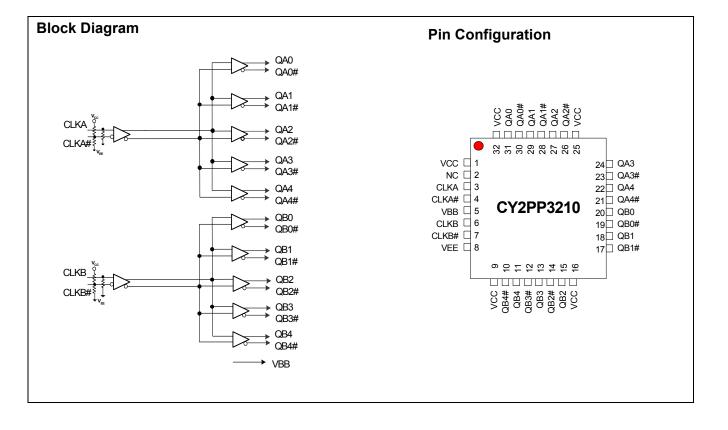

# **Functional Description**

The CY2PP3210 is a low-skew, low propagation delay dual 1-to-5 differential fanout buffer targeted to meet the requirements of high-performance clock and data distribution applications. The device is implemented on SiGe technology and has a fully differential internal architecture that is optimized to achieve low signal skews at operating frequencies of up to 1.5 GHz.

The device features two differential input paths that are differential internally. The CY2PP3210 may function not only as a differential clock buffer but also as a signal-level translator and fanout distributing a single-ended signal. An external bias pin, VBB, is provided for this purpose. In such an application, the VBB pin should be connected to either one of the CLKA# or CLKB# inputs and bypassed to ground via a 0.01- $\mu$ F capacitor. Traditionally, in ECL, it is used to provide the reference level to a receiving single-ended input that might have a differential bias point.

Since the CY2PP3210 introduces negligible jitter to the timing budget, it is the ideal choice for distributing high frequency, high precision clocks across back-planes and boards in communication systems. Furthermore, advanced circuit design schemes, such as internal temperature compensation, ensure that the CY2PP3210 delivers consistent performance over various platforms.

**Cypress Semiconductor Corporation** Document #: 38-07508 Rev.\*C 3901 North First Street

San Jose, CA 95134 • 408-943-2600 Revised July 28, 2004

## Pin Definitions<sup>[1, 2, 3]</sup>

| Pin            | Name               | <b>I/O</b> <sup>[1]</sup> | Туре     | Description                         |

|----------------|--------------------|---------------------------|----------|-------------------------------------|

| 2              | NC                 |                           |          | No connect.                         |

| 3              | CLKA,              | I,PD                      | ECL/PECL | ECL/PECL Differential Input Clocks. |

| 4              | CLKA#              | I,PD/PU                   | ECL/PECL | ECL/PECL Differential Input Clocks. |

| 5              | VBB <sup>[3]</sup> | 0                         | Bias     | Reference Voltage Output.           |

| 6              | CLKB,              | I,PD                      | ECL/PECL | ECL/PECL Differential Input Clocks. |

| 7              | CLKB#              | I,PD/PU                   | ECL/PECL | ECL/PECL Differential Input Clocks. |

| 8              | VEE <sup>[2]</sup> | -PWR                      | Power    | Negative Supply.                    |

| 1,9,16,25,32   | VCC                | +PWR                      | Power    | Positive Supply.                    |

| 31,29,27,24,22 | QA(0:4)            | 0                         | ECL/PECL | True output                         |

| 30,28,26,23,21 | QA#(0:4)           | 0                         | ECL/PECL | Complement output                   |

| 20,18,15,13,11 | QB(0:4)            | 0                         | ECL/PECL | True output                         |

| 19,17,14,12,10 | QB#(0:4)           | 0                         | ECL/PECL | Complement output                   |

#### **Governing Agencies**

The following agencies provide specifications that apply to the CY2PP3210. The agency name and relevant specification is listed below in Table 2.

#### Table 1.

| Agency Name | Specification                                                                      |

|-------------|------------------------------------------------------------------------------------|

| JEDEC       | JESD 020B (MSL)<br>JESD 51 (Theta JA)<br>JESD 8–2 (ECL)<br>JESD 65–B (skew,jitter) |

| Mil-Spec    | 883E Method 1012.1 (Thermal Theta JC)                                              |

Notes:

In the I/O column, the following notation is used: I for Input, O for Output, PD for Pull-Down, PU for Pull-Up, and PWR for Power

In ECL mode (negative power supply mode), V<sub>EE</sub> is either -3.3V or -2.5V and V<sub>CC</sub> is connected to GND (0V). In PECL mode (positive power supply mode), V<sub>EE</sub> is connected to GND (0V) and V<sub>CC</sub> is either +3.3V or +2.5V. In both modes, the input and output levels are referenced to the most positive supply (V<sub>CC</sub>) and are between V<sub>CC</sub> and V<sub>EE</sub>.

V<sub>BB</sub> is available for use for single-ended bias mode for |3.3V| supplies (not |2.5V|).

## **Absolute Maximum Ratings**

| Parameter        | Description                | Condition        | Min.    | Max. | Unit |

|------------------|----------------------------|------------------|---------|------|------|

| V <sub>CC</sub>  | Positive Supply Voltage    | Non-Functional   | -0.3    | 4.6  | V    |

| V <sub>EE</sub>  | Negative Supply Voltage    | Non-Functional   | -4.6    | 0.3  | V    |

| Τ <sub>S</sub>   | Temperature, Storage       | Non-Functional   | -65     | +150 | °C   |

| TJ               | Temperature, Junction      | Non-Functional   | 150     |      | °C   |

| ESD <sub>h</sub> | ESD Protection             | Human Body Model | 2000    |      | V    |

| M <sub>SL</sub>  | Moisture Sensitivity Level |                  | 3       |      |      |

| Gate Count       | Total Number of Used Gates | Assembled Die    | 50 gate |      |      |

Multiple Supplies: The Voltage on any input or I/O pin cannot exceed the power pin during power-up. Power supply sequencing is NOT required.

## **Operating Conditions**

| Parameter        | Description                                                           | Condition                                  | Min.            | Max.                  | Unit |

|------------------|-----------------------------------------------------------------------|--------------------------------------------|-----------------|-----------------------|------|

| I <sub>BB</sub>  | Output Reference Current                                              | Relative to V <sub>BB</sub>                | -               | 200                   | uA   |

| LUI              | Latch Up Immunity                                                     | Functional, typical                        | 1               | 00                    | mA   |

| T <sub>A</sub>   | Temperature, Operating Ambient                                        | Functional                                 | -40             | +85                   | °C   |

| Ø <sub>Jc</sub>  | Dissipation, Junction to Case                                         | Functional                                 | 29              | ) <sup>[4]</sup>      | °C/W |

| Ø <sub>Ja</sub>  | Dissipation, Junction to Ambient                                      | Functional                                 | 76              | 76 <sup>[4]</sup>     |      |

| I <sub>EE</sub>  | Maximum Quiescent Supply Current                                      | V <sub>EE</sub> pin <sup>[5]</sup>         | -               | 130                   | mA   |

| C <sub>IN</sub>  | Input pin capacitance                                                 |                                            | -               | 3                     | pF   |

| L <sub>IN</sub>  | Pin Inductance                                                        |                                            |                 | 1                     | nH   |

| V <sub>IN</sub>  | Input Voltage                                                         | Relative to V <sub>CC</sub> <sup>[6]</sup> | -0.3            | V <sub>CC</sub> + 0.3 | V    |

| V <sub>TT</sub>  | Output Termination Voltage                                            | Relative to V <sub>CC</sub> <sup>[6]</sup> | V <sub>CO</sub> | <sub>2</sub> -2       | V    |

| V <sub>OUT</sub> | Output Voltage                                                        | Relative to V <sub>CC</sub> <sup>[6]</sup> | -0.3            | V <sub>CC</sub> + 0.3 | V    |

| I <sub>IN</sub>  | Input Current <sup>[7]</sup> $V_{IN} = V_{IL}$ , or $V_{IN} = V_{IH}$ |                                            |                 |                       | uA   |

#### **PECL DC Electrical Specifications**

| Parameter                      | Description                                                              | Condition                                                              | Min.                                              | Max.                                           | Unit   |

|--------------------------------|--------------------------------------------------------------------------|------------------------------------------------------------------------|---------------------------------------------------|------------------------------------------------|--------|

| V <sub>CC</sub>                | Operating Voltage                                                        | 2.5V ± 5%, V <sub>EE</sub> = 0.0V<br>3.3V ± 5%, V <sub>EE</sub> = 0.0V | 2.375<br>3.135                                    | 2.625<br>3.465                                 | V<br>V |

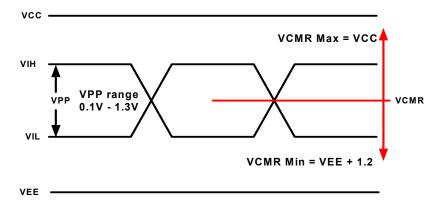

| V <sub>CMR</sub>               | Differential Cross Point Voltage <sup>[8]</sup>                          | Differential operation                                                 | 1.2                                               | V <sub>CC</sub>                                | V      |

| V <sub>OH</sub>                | Output High Voltage                                                      | I <sub>OH</sub> = –30 mA <sup>[9]</sup>                                | V <sub>CC</sub> – 1.25                            | V <sub>CC</sub> - 0.7                          | V      |

| V <sub>OL</sub>                | Output Low Voltage<br>$V_{CC} = 3.3V \pm 5\%$<br>$V_{CC} = 2.5V \pm 5\%$ | I <sub>OL</sub> = –5 mA <sup>[9]</sup>                                 | V <sub>CC</sub> – 1.995<br>V <sub>CC</sub> –1.995 | V <sub>CC</sub> – 1.5<br>V <sub>CC</sub> – 1.3 | V<br>V |

| V <sub>IH</sub>                | Input Voltage, High                                                      | Single-ended operation                                                 | V <sub>CC</sub> – 1.165                           | V <sub>CC</sub> -0.880 <sup>[10]</sup>         | V      |

| V <sub>IL</sub>                | Input Voltage, Low                                                       | Single-ended operation                                                 | V <sub>CC</sub> – 1.945 <sup>[10]</sup>           | V <sub>CC</sub> – 1.625                        | V      |

| V <sub>BB</sub> <sup>[3]</sup> | Output Reference Voltage                                                 | Relative to V <sub>CC</sub> <sup>[6]</sup>                             | V <sub>CC</sub> – 1.620                           | V <sub>CC</sub> – 1.220                        | V      |

Notes:

8. Refer to Figure 1

9. Equivalent to a termination of 50 $\Omega$  to VTT. I<sub>OHMIN</sub>=(V<sub>OHMIN</sub>-V<sub>TT</sub>)/50; I<sub>OHMAX</sub>=(V<sub>OHMAX</sub>-V<sub>TT</sub>)/50; I<sub>OLMIN</sub>=(V<sub>OLMIN</sub>-V<sub>TT</sub>)/50; I<sub>OLMAX</sub>=(V<sub>OLMAX</sub>-V<sub>TT</sub>)/50; I<sub>OLMAX</sub>=(V<sub>OLMAX</sub>

<sup>4.</sup> Theta JA EIA JEDEC 51 test board conditions (typical value); Theta JC 883E Method 1012.1

<sup>5.</sup> Power Calculation:  $V_{CC}$  is 3.3V±5% or 2.5V±5% 7. Inputs have internal pull-up/pull-down or biasing resistors which affect the input current.

## **ECL DC Electrical Specifications**

| Parameter                      | Description                                                                                  | Condition                                                                            | Min.                   | Max.                   | Unit |  |

|--------------------------------|----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|------------------------|------------------------|------|--|

| $V_{EE}$                       | Negative Power Supply                                                                        | $-2.5V \pm 5\%$ , V <sub>CC</sub> = 0.0V<br>$-3.3V \pm 5\%$ , V <sub>CC</sub> = 0.0V | -2.625<br>-3.465       | -2.375<br>-3.135       | V    |  |

| V <sub>CMR</sub>               | Differential cross point voltage <sup>[8]</sup>                                              | Differential operation                                                               | V <sub>EE</sub> + 1.2  | 0V                     | V    |  |

| V <sub>OH</sub>                | Output High Voltage                                                                          | I <sub>OH</sub> = –30 mA <sup>[9]</sup>                                              | -1.25                  | -0.7                   | V    |  |

| V <sub>OL</sub>                | Output Low Voltage<br>V <sub>EE</sub> = $-3.3V \pm 5\%$<br>V <sub>EE</sub> = $-2.5V \pm 5\%$ | I <sub>OL</sub> = –5 mA <sup>[9]</sup>                                               | -1.995<br>-1.995       | -1.5<br>-1.3           | V    |  |

| V <sub>IH</sub>                | Input Voltage, High                                                                          | Single-ended operation                                                               | -1.165                 | -0.880 <sup>[10]</sup> | V    |  |

| V <sub>IL</sub>                | Input Voltage, Low                                                                           | Single-ended operation                                                               | -1.945 <sup>[10]</sup> | -1.625                 | V    |  |

| V <sub>BB</sub> <sup>[3]</sup> | Output Reference Voltage                                                                     |                                                                                      | - 1.620                | - 1.220                | V    |  |

#### **AC Electrical Specifications**

| Parameter                      | Description                                      | Condition                                         | Min.              | Max.  | Unit |

|--------------------------------|--------------------------------------------------|---------------------------------------------------|-------------------|-------|------|

| V <sub>PP</sub>                | Differential Input Voltage <sup>[8]</sup>        | Differential operation                            | 0.1               | 1.3   | V    |

| F <sub>CLK</sub>               | Input Frequency                                  | 50% duty cycle Standard load                      |                   | 1.5   | GHz  |

| T <sub>PD</sub>                | Propagation Delay CLKA or CLKB to<br>Output pair | 660 MHz <sup>[11]</sup>                           | 280               | 750   | ps   |

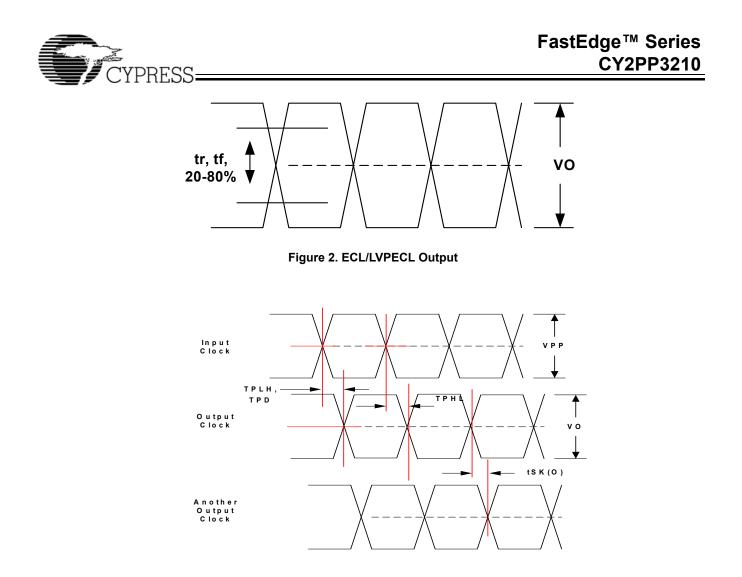

| Vo                             | Output Voltage (peak-to-peak; see<br>Figure 2)   | < 1 GHz                                           | 0.375             | _     | V    |

| V <sub>CMRO</sub>              | Output Common Voltage Range (typ.)               |                                                   | V <sub>CC</sub> - | 1.425 | V    |

| tsk <sub>(0)</sub>             | Output-to-output Skew                            | 660 MHz <sup>[11]</sup> , See Figure 3            | _                 | 50    | ps   |

| tsk <sub>(PP)</sub>            | Part-to-Part Output Skew                         | 660 MHz <sup>[11]</sup>                           | -                 | 150   | ps   |

| T <sub>PER</sub>               | Output Period Jitter (rms) <sup>[12]</sup>       | 660 MHz <sup>[11]</sup>                           | _                 | 0.8   | ps   |

| tsk <sub>(P)</sub>             | Output Pulse Skew <sup>[13]</sup>                | 660 MHz <sup>[11]</sup> , See Figure 3            | -                 | 50    | ps   |

| T <sub>R</sub> ,T <sub>F</sub> | Output Rise/Fall Time (see Figure 2)             | 660 MHz 50% duty cycle<br>Differential 20% to 80% | 0.08              | 0.3   | ns   |

# **Timing Definitions**

#### Figure 1. PECL/ECL Input Waveform Definitions

Notes: 11.50% duty cycle; standard load; differential operation

12. For 3.3V supplies. Jitter measured differentially using an Agilent 8133A Pulse Generator with an 8500A LeCroy Wavemaster Oscilloscope using at least 10,000 data points

13. Output pulse skew is the absolute difference of the propagation delay times:  $|t_{PLH} - t_{PHL}|$ .

Figure 3. Propagation Delay (T<sub>PD</sub>), output pulse skew ( $|t_{PLH}-t_{PHL}|$ ), and output-to-output skew ( $t_{SK(O)}$ ) for both CLKA or CLKB to Output Pair, PECL/ECL to PECL/ECL

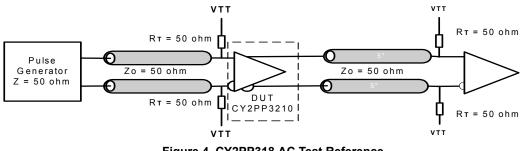

#### **Test Configuration**

Standard test load using a differential pulse generator and differential measurement instrument.

Figure 4. CY2PP318 AC Test Reference

# **Applications Information**

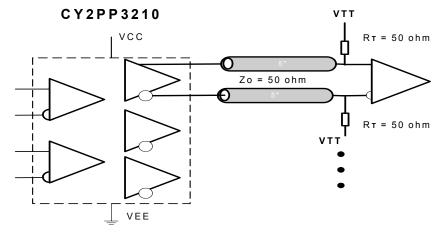

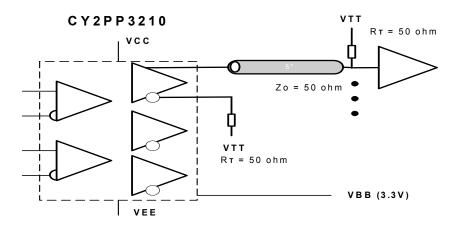

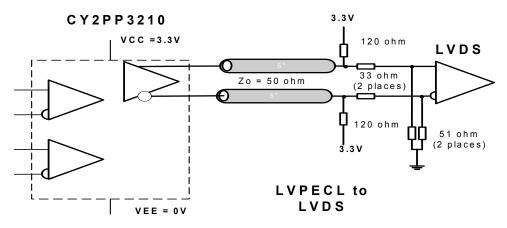

#### **Termination Examples**

Figure 5. Standard LVPECL – PECL Output Termination

Figure 6. Driving a PECL/ECL Single-ended Input

Figure 7. Low-voltage Positive Emitter-coupled Logic (LVPECL) to a Low-voltage Differential Signaling (LVDS) Interface

One output is shown for clarity

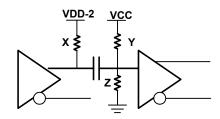

# Figure 8. Termination for LVPECL to HTSL interface for VCC=2.5V would use X=50 Ohms, Y=2300 Ohms, and Z=1000 Ohms. See application note titled, "PECL Translation, SAW Oscillators, and Specs" for other signalling standards and supplies.

# **Ordering Information**

| Part Number  | Package Type                | Product Flow             |  |

|--------------|-----------------------------|--------------------------|--|

| CY2PP3210AI  | 32-pin TQFP                 | Industrial, –40° to 85°C |  |

| CY2PP3210AIT | 32-pin TQFP – Tape and Reel | Industrial, –40° to 85°C |  |

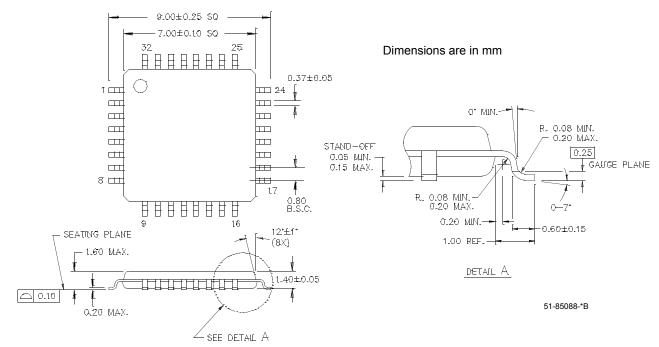

# Package Drawing and Dimension

#### 32-Lead Thin Plastic Quad Flatpack 7 x 7 x 1.4 mm A32.14

FastEdge is a trademark of Cypress Semiconductor. All product and company names mentioned in this document are the trademarks of their respective holders.

© Cypress Semiconductor Corporation, 2004. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress product. Nor does it convey or imply any license under patent or other rights. Cypress products are not warranted nor intended to be used for medical, life support, life saving, critical control or safety applications, unless pursuant to an express written agreement with Cypress. Furthermore, Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

# Document History Page

| Document Title: CY2PP3210 FastEdge™ Series Dual 1:5 Differential Clock/Data Fanout Buffer<br>Document Number: 38-07508 |         |               |                    |                                                                                                                                                                                                                                                            |

|------------------------------------------------------------------------------------------------------------------------|---------|---------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REV.                                                                                                                   | ECN NO. | lssue<br>Date | Orig. of<br>Change | Description of Change                                                                                                                                                                                                                                      |

| **                                                                                                                     | 122396  | 02/12/03      | RGL                | New Data Sheet                                                                                                                                                                                                                                             |

| *A                                                                                                                     | 125458  | 04/17/03      | RGL                | Corrected pins 26 to 31 from Q2#, Q2, Q1#, Q1, Q0#, Q0 to QA2#, QA2, QA1#, QA1,QA0#, QA0 in the Pin Configuration diagram Changed pins 9, 16, 25, 32 from VCC to VCCO Changed the title to FastEdge™ Series Dual 1:5 Differential Clock/Data Fanout Buffer |

| *В                                                                                                                     | 229370  | See ECN       | RGL                | Supplied data to all the TBD's to match the device                                                                                                                                                                                                         |

| *C                                                                                                                     | 247616  | See ECN       | RGL/GGK            | Changed $V_{OH}$ and $V_{OL}$ to match the Char Data                                                                                                                                                                                                       |