## Please note that Cypress is an Infineon Technologies Company.

The document following this cover page is marked as "Cypress" document as this is the company that originally developed the product. Please note that Infineon will continue to offer the product to new and existing customers as part of the Infineon product portfolio.

## Continuity of document content

The fact that Infineon offers the following product as part of the Infineon product portfolio does not lead to any changes to this document. Future revisions will occur when appropriate, and any changes will be set out on the document history page.

## Continuity of ordering part numbers

Infineon continues to support existing part numbers. Please continue to use the ordering part numbers listed in the datasheet for ordering.

# 16-Mbit (1M × 16) Static RAM

#### Features

- High speed □ t<sub>AA</sub> = 10 ns

- Embedded error-correcting code (ECC) for single-bit error correction

- Low active power □ I<sub>CC</sub> = 90 mA typical

- Low CMOS standby power □ I<sub>SB2</sub> = 20 mA typical

- Operating voltages of 3.3 ± 0.3 V

- 1.0 V data retention

- Transistor-transistor logic (TTL) compatible inputs and outputs

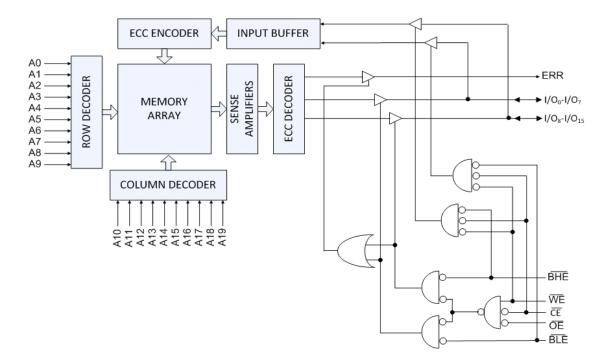

- ERR pin to indicate 1-bit error detection and correction

- Available in Pb-free 54-pin TSOP II package

#### **Functional Description**

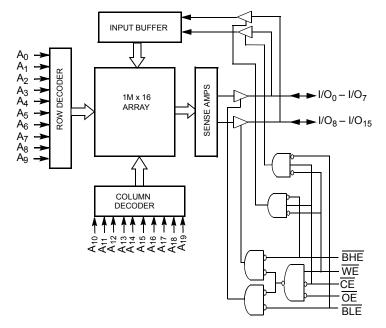

The CY7C10612G and CY7C10612GE are high performance CMOS fast static RAM devices with embedded ECC. These devices are offered in single chip enable option. The CY7C10612GE device includes an error indication pin that signals an error-detection and correction event during a read cycle.

To write to the device, take Chip Enables  $\overline{(CE)}$  and Write Enable  $\overline{(WE)}$  input LOW. If Byte Low Enable (BLE) is LOW, then data from I/O pins (I/O<sub>0</sub> through I/O<sub>7</sub>), is written into the location specified on the address pins (A<sub>0</sub> through A<sub>19</sub>). If Byte High Enable (BHE) is LOW, then data from I/O pins (I/O<sub>8</sub> through I/O<sub>15</sub>) is written into the location specified on the address pins (A<sub>0</sub> through A<sub>19</sub>).

To read <u>from</u> the device, take Chip Enable ( $\overline{\text{CE}}$ ) and Output Enable ( $\overline{\text{OE}}$ ) LOW <u>while</u> forcing the Write Enable (WE) HIGH. If Byte Low Enable (BLE) is LOW, then data from the memory location specified by the address pins appears on I/O<sub>0</sub> to I/O<sub>7</sub>. If Byte High Enable (BHE) is LOW, then data from memory appears on I/O<sub>8</sub> to I/O<sub>15</sub>. See Truth Table on page 14 for a complete description of Read and Write modes.

The input or output pins  $(I/O_0 \text{ through } I/O_{15})$  are placed in a high impedance state when the device is deselected (CE HIGH), the outputs are disabled (OE HIGH), the BHE and BLE are disabled (BHE, BLE HIGH), or during a write operation (CE LOW and WE LOW).

On the CY7C10612GE devices the detection and correction of a single-bit error in the accessed location is indicated by the assertion of the ERR output (ERR = high). See the Truth Table on page 14 for a complete description of read and write modes.

The CY7C10612G and CY7C10612GE are available in a 54-pin TSOP II package.

For a complete list of related documentation, click here.

#### **Selection Guide**

| Description                  |     | Unit |

|------------------------------|-----|------|

| Maximum Access Time          | 10  | ns   |

| Maximum Operating Current    | 110 | mA   |

| Maximum CMOS Standby Current | 30  | mA   |

198 Champion Court

## Logic Block Diagram – CY7C10612G

## Logic Block Diagram – CY7C10612GE

## Contents

| Pin Configurations             | 4  |

|--------------------------------|----|

| Maximum Ratings                | 6  |

| Operating Range                | 6  |

| DC Electrical Characteristics  | 6  |

| Capacitance                    | 7  |

| Thermal Resistance             | 7  |

| AC Test Loads and Waveforms    | 7  |

| Data Retention Characteristics | 8  |

| Data Retention Waveform        | 8  |

| AC Switching Characteristics   | 9  |

| Switching Waveforms            |    |

| Truth Table                    | 14 |

| ERR Output - CY7C10612GE       | 14 |

|                                |    |

| Ordering Information1                    | 15 |

|------------------------------------------|----|

| Ordering Code Definitions1               | 15 |

| Package Diagrams1                        | 16 |

| Acronyms                                 | 17 |

| Document Conventions1                    | 17 |

| Units of Measure1                        | 17 |

| Document History Page1                   | 8  |

| Sales, Solutions, and Legal Information1 | 19 |

| Worldwide Sales and Design Support1      | 19 |

| Products1                                | 19 |

| PSoC® Solutions1                         | 19 |

| Cypress Developer Community1             | 19 |

| Technical Support1                       |    |

## **Pin Configurations**

#### Figure 1. 54-pin TSOP II pinout (Top View) <sup>[1]</sup> CY7C10612G

| I/O <sub>12</sub>     | 54 🔲 I/O <sub>11</sub> |

|-----------------------|------------------------|

| V <sub>CC</sub>       | 53 🗆 V <sub>SS</sub>   |

| I/O <sub>13</sub> 🗖 3 | 52 🗌 I/O <sub>10</sub> |

| I/O <sub>14</sub> _ 4 | 51 🔲 I/O <sub>9</sub>  |

| V <sub>SS</sub> 🗖 5   | 50 🗌 V <sub>CC</sub>   |

| I/O <sub>15</sub> 🗌 6 | 49 🗖 I/O <sub>8</sub>  |

| A <sub>4</sub> 🗖 7    | 48 🗖 A <sub>5</sub>    |

| A3 🗖 8                | 47 🗖 A <sub>6</sub>    |

| A <sub>2</sub> 🗌 9    | 46 🗌 A <sub>7</sub>    |

| A <sub>1</sub> 🗌 10   | 45 🗖 A <sub>8</sub>    |

| A <sub>0</sub> 🗌 11   | 44 🗆 A <sub>9</sub>    |

| BHE 12                | 43 🗌 NC                |

| CE 13                 | 42 🗌 🛛 🛛 🛛 🕁           |

| V <sub>CC</sub> 14    | 41 🗌 V <sub>SS</sub>   |

| WE 15                 | 40 🗆 NC                |

| NC 🗌 16               | 39 🗌 BLE               |

| A <sub>19</sub> 🗌 17  | 38 🗌 A <sub>10</sub>   |

| A <sub>18</sub>       | 37 🗖 A <sub>11</sub>   |

| A <sub>17</sub>       | 36 🗆 A <sub>12</sub>   |

| A <sub>16</sub> _ 20  | 35 🗌 A <sub>13</sub>   |

| A <sub>15</sub> 21    | 34 🗌 A <sub>14</sub>   |

| I/O <sub>0</sub> □22  | 33 🔲 I/O <sub>7</sub>  |

| V <sub>CC</sub> 23    | 32 🗌 V <sub>SS</sub>   |

| I/O <sub>1</sub> 24   | 31 🗌 I/O <sub>6</sub>  |

| I/O <sub>2</sub> □ 25 | 30 🗌 I/O <sub>5</sub>  |

|                       | 29 🗌 V <sub>CC</sub>   |

| I/O <sub>3</sub> □27  | 28 🗆 I/O <sub>4</sub>  |

|                       |                        |

Note

1. NC pins are not connected on the die.

#### Pin Configurations (continued)

# Figure 2. 54-pin TSOP II pinout with ERR (Top View) <sup>[2, 3]</sup> CY7C10612GE

| _                 |            |          |   |                                     |

|-------------------|------------|----------|---|-------------------------------------|

| I/O <sub>12</sub> | 1          | 54       |   | I/O <sub>11</sub>                   |

| V <sub>CC</sub>   | 2          | 53       |   | V <sub>SS</sub>                     |

| I/O <sub>13</sub> | 3          | 52       |   | I/O <sub>10</sub>                   |

| I/O <sub>14</sub> | 4          | 51       | 6 | I/O <sub>9</sub>                    |

| V <sub>SS</sub>   | 5          | 50       |   | Vcc                                 |

| I/O <sub>15</sub> | 6          | 49       |   | I/O <sub>8</sub>                    |

| A <sub>4</sub>    | 7          | 48       |   | A <sub>5</sub>                      |

| A <sub>3</sub>    | 8          | 47       |   | A <sub>6</sub>                      |

| A <sub>2</sub> [  | 9          | 46       |   | A <sub>7</sub>                      |

|                   | 10         | 45       |   | A <sub>8</sub>                      |

|                   | 11         | 44       |   | A <sub>9</sub>                      |

|                   | 12         | 43       |   | ERR                                 |

| CE 🗌              | 13         | 42       |   | OE                                  |

|                   | 14         | 41       |   | V <sub>SS</sub>                     |

|                   | 15         | 40       |   | NC                                  |

|                   | 16         | 39       |   | BLE                                 |

|                   | 17         | 38       |   | A <sub>10</sub>                     |

|                   | 18         | 37       |   | A <sub>11</sub>                     |

|                   | 19         | 36       | H | A <sub>12</sub>                     |

|                   | 20         | 35       | Ľ | A <sub>13</sub>                     |

|                   | 21         | 34       | H | A <sub>14</sub>                     |

|                   | 22         | 33       | H | 1/0 <sub>7</sub>                    |

|                   | 23         | 32       | H | V <sub>SS</sub><br>I/O <sub>6</sub> |

|                   | 24<br>25   | 31<br>30 | H | 1/06                                |

|                   | 26         | 30<br>29 | H | 1/0 <sub>5</sub>                    |

|                   | 20<br>27   | 28       | Ħ | V <sub>CC</sub><br>I/O <sub>4</sub> |

| "U3 L             | <u>-</u> 1 | 20       | Ľ | 1/04                                |

Note

NC pins are not connected on the die.

ERR is an Output pin. If not used, this pin should be left floating.

#### **Maximum Ratings**

Exceeding maximum ratings may shorten the useful life of the device. User guidelines are not tested.

| Storage Temperature65 °C to +150 °C                                           |

|-------------------------------------------------------------------------------|

| Ambient Temperature<br>with Power Applied55 °C to +125 °C                     |

| Supply Voltage on $V_{CC}$ Relative to $GND^{[4]}$ –0.5 V to $V_{CC}$ + 0.5 V |

| DC Voltage Applied to Outputs in High Z State $^{[4]}$ –0.5 V to V_CC + 0.5 V |

| DC Input Voltage <sup>[4]</sup>                        | –0.5 V to $V_{CC}$ + 0.5 V |

|--------------------------------------------------------|----------------------------|

| Current into Outputs (LOW)                             |                            |

| Static Discharge Voltage<br>(MIL-STD-883, Method 3015) | >2001 V                    |

| Latch Up Current                                       | > 200 mA                   |

#### **Operating Range**

| Range      | Ambient Temperature | V <sub>cc</sub> |

|------------|---------------------|-----------------|

| Industrial | –40 °C to +85 °C    | $3.3~V\pm0.3~V$ |

### **DC Electrical Characteristics**

Over the operating range of -40 °C to 85 °C

| Deremeter                      | Description                                     |                    | Test Conditions                                                                                                                                                                                                        |                                                                   | 10 ns |                           |                       | Unit |

|--------------------------------|-------------------------------------------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|-------|---------------------------|-----------------------|------|

| Parameter                      |                                                 |                    |                                                                                                                                                                                                                        |                                                                   | Min   | <b>Typ</b> <sup>[5]</sup> | Max                   | Unit |

| V <sub>OH</sub>                | Output HIGH                                     | 2.2 V to 2.7 V     | V <sub>CC</sub> = Min, I <sub>OH</sub> = -4.0                                                                                                                                                                          | mA                                                                | 2.2   | -                         | -                     | V    |

|                                | Voltage                                         | 2.7 V to 3.0 V     | V <sub>CC</sub> = Min, I <sub>OH</sub> = -4.0                                                                                                                                                                          | mA                                                                | 2.4   | -                         | -                     |      |

| V <sub>OL</sub>                | Output LOW Volta                                | ige                | V <sub>CC</sub> = Min, I <sub>OL</sub> = 8 mA                                                                                                                                                                          | ł                                                                 | -     | -                         | 0.4                   | V    |

| V <sub>IH</sub> <sup>[4]</sup> | Input HIGH Voltage                              |                    | -                                                                                                                                                                                                                      |                                                                   | 2.0   | -                         | V <sub>CC</sub> + 0.3 | V    |

| V <sub>IL</sub> <sup>[4]</sup> | Input LOW Voltage                               |                    | -                                                                                                                                                                                                                      |                                                                   | -0.3  | -                         | 0.8                   | V    |

| I <sub>IX</sub>                | Input Leakage Current                           |                    | $GND \leq V_{IN} \leq V_{CC}$                                                                                                                                                                                          |                                                                   | -1.0  | -                         | +1.0                  | μA   |

| I <sub>OZ</sub>                | Output Leakage Current                          |                    | $GND \leq V_{OUT} \leq V_{CC}, O$                                                                                                                                                                                      | utput disabled                                                    | -1.0  | -                         | +1.0                  | μA   |

| I <sub>CC</sub>                | Operating Supply Current                        |                    | V <sub>CC</sub> = Max,                                                                                                                                                                                                 | f = 100 MHz                                                       | -     | 90.0                      | 110.0                 | mA   |

|                                |                                                 |                    | I <sub>OUT</sub> = 0 mA,<br>CMOS levels                                                                                                                                                                                | f = 66.7 MHz                                                      | _     | 70.0                      | 80.0                  | mA   |

| I <sub>SB1</sub>               | Automatic CE Power-down<br>Current – TTL Inputs |                    | $\begin{array}{l} \text{Max V}_{\text{CC}}, \ \overline{\text{CE}} \geq \text{V}_{\text{IH}} \\ \text{V}_{\text{IN}} \geq \text{V}_{\text{IH}} \text{ or } \text{V}_{\text{IN}} \leq \text{V}_{\text{IL}} \end{array}$ | $f = f_{MAX}$                                                     | -     | -                         | 40.0                  | mA   |

| I <sub>SB2</sub>               | Automatic CE Pov<br>Current – CMOS              | wer-down<br>Inputs | Max V <sub>CC</sub> , <u>CE</u> ≥ V <sub>CC</sub> -<br>V <sub>IN</sub> ≥ V <sub>CC</sub> - 0.2 V or V <sub>I</sub>                                                                                                     | - 0.2 V <sup>[5]</sup> ,<br><sub>N</sub> <u>&lt;</u> 0.2 V, f = 0 | -     | 20.0                      | 30.0                  | mA   |

Notes

- 4. V<sub>IL(min)</sub> = -2.0 V and V<sub>IH(max)</sub> = V<sub>CC</sub> + 2 V for pulse durations of less than 20 ns.

5. Typical values are included only for reference and are not guaranteed or tested. Typical values are measured at V<sub>CC</sub> = 1.8 V (for a V<sub>CC</sub> range of 1.65 V–2.2 V), V<sub>CC</sub> = 3 V (for a V<sub>CC</sub> range of 2.2 V–3.6 V), and V<sub>CC</sub> = 5 V (for a V<sub>CC</sub> range of 4.5 V–5.5 V), T<sub>A</sub> = 25 °C.

### Capacitance

| Parameter [6]    | Description       | Test Conditions                                                  | 54-pin TSOP II | Unit |

|------------------|-------------------|------------------------------------------------------------------|----------------|------|

| C <sub>IN</sub>  | Input Capacitance | $T_A = 25 \text{ °C}, f = 1 \text{ MHz}, V_{CC} = 3.3 \text{ V}$ | 10             | pF   |

| C <sub>OUT</sub> | I/O Capacitance   |                                                                  |                |      |

#### **Thermal Resistance**

| Parameter [6]   | Description                                 | Test Conditions                                                         | 54-pin TSOP II | Unit |

|-----------------|---------------------------------------------|-------------------------------------------------------------------------|----------------|------|

| $\Theta_{JA}$   | Thermal Resistance<br>(junction to ambient) | Still air, soldered on a 3 × 4.5 inch, four-layer printed circuit board | 93.63          | °C/W |

| Θ <sub>JC</sub> | Thermal Resistance<br>(junction to case)    |                                                                         | 21.58          |      |

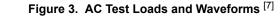

#### **AC Test Loads and Waveforms**

Notes

6. Tested initially and after any design or process changes that may affect these parameters.

7. Full-device AC operation assumes a 100-µs ramp time from 0 to V<sub>CC</sub> (min) and 100-µs wait time after V<sub>CC</sub> stabilizes to its operational value.

#### **Data Retention Characteristics**

Over the Operating Range -45 °C to 85 °C

| Parameter                         | Description                          | Conditions                                                                                                                                                | Min  | <b>Typ</b> <sup>[8]</sup> | Max  | Unit |

|-----------------------------------|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------------------|------|------|

| V <sub>DR</sub>                   | V <sub>CC</sub> for Data Retention   | -                                                                                                                                                         | 1.0  | -                         | Ι    | V    |

| I <sub>CCDR</sub>                 | Data Retention Current               | $ \begin{array}{l} V_{CC} = 2 \ V, \ \overline{CE} \geq V_{CC} - 0.2 \ V, \\ V_{IN} \geq V_{CC} - 0.2 \ V \ \text{or} \ V_{IN} \leq 0.2 \ V \end{array} $ | -    | _                         | 30.0 | mA   |

| t <sub>CDR</sub> <sup>[9]</sup>   | Chip Deselect to Data Retention Time | -                                                                                                                                                         | 0.0  | -                         | -    | ns   |

| t <sub>R</sub> <sup>[9, 10]</sup> | Operation Recovery Time              | -                                                                                                                                                         | 10.0 | -                         | Ι    | ns   |

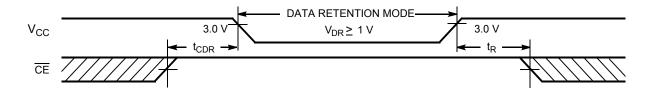

#### **Data Retention Waveform**

Notes

<sup>8.</sup> Typical values are included for reference only and are not guaranteed or tested. Typical values are measured at  $V_{CC} = V_{CC(typ)}$ ,  $T_A = 25 \text{ °C}$ . 9. This parameter is guaranteed by design and is not tested. 10. Full device operation requires linear  $V_{CC}$  ramp from  $V_{DR}$  to  $V_{CC(min.)} \ge 100 \,\mu\text{s}$  or stable at  $V_{CC(min.)} \ge 100 \,\mu\text{s}$ .

### AC Switching Characteristics

Over the Operating Range

| Parameter [11]     | Description                                         | -1    | -10     |    |  |

|--------------------|-----------------------------------------------------|-------|---------|----|--|

| Parameter          | Description                                         | Min   | Min Max |    |  |

| Read Cycle         |                                                     |       |         |    |  |

| t <sub>POWER</sub> | V <sub>CC</sub> to the first access <sup>[12]</sup> | 100.0 | -       | μs |  |

| t <sub>RC</sub>    | Read cycle time                                     | 10.0  | _       | ns |  |

| t <sub>AA</sub>    | Address to data valid                               | -     | 10.0    | ns |  |

| t <sub>OHA</sub>   | Data hold from address change                       | 3.0   | _       | ns |  |

| t <sub>ACE</sub>   | CE LOW to data valid                                | -     | 10.0    | ns |  |

| t <sub>DOE</sub>   | OE LOW to data valid                                | -     | 5.0     | ns |  |

| t <sub>LZOE</sub>  | OE LOW to low Z [13, 14, 15]                        | 0.0   | _       | ns |  |

| t <sub>HZOE</sub>  | OE HIGH to high Z <sup>[13, 14, 15]</sup>           | -     | 5.0     | ns |  |

| t <sub>LZCE</sub>  | CE LOW to low Z [13, 14, 15]                        | 3.0   | -       | ns |  |

| t <sub>HZCE</sub>  | CE HIGH to high Z <sup>[13, 14, 15]</sup>           | _     | 5.0     | ns |  |

| t <sub>PU</sub>    | CE LOW to power-up <sup>[16]</sup>                  | 0.0   | -       | ns |  |

| t <sub>PD</sub>    | CE HIGH to power-down <sup>[16]</sup>               | _     | 10.0    | ns |  |

| t <sub>DBE</sub>   | Byte enable to data valid                           | _     | 5.0     | ns |  |

| t <sub>LZBE</sub>  | Byte enable to low Z                                | 1.0   | _       | ns |  |

| t <sub>HZBE</sub>  | Byte disable to high Z                              | -     | 6.0     | ns |  |

| Write Cycle [17    | , 18]                                               | ·     |         | •  |  |

| t <sub>WC</sub>    | Write cycle time                                    | 10.0  | _       | ns |  |

| t <sub>SCE</sub>   | CE LOW to write end                                 | 7.0   | _       | ns |  |

| t <sub>AW</sub>    | Address setup to write end                          | 7.0   | _       | ns |  |

| t <sub>HA</sub>    | Address hold from write end                         | 0.0   | _       | ns |  |

| t <sub>SA</sub>    | Address setup to write start                        | 0.0   | _       | ns |  |

| t <sub>PWE</sub>   | WE pulse width                                      | 7.0   | _       | ns |  |

| t <sub>SD</sub>    | Data setup to write end                             | 5.0   | _       | ns |  |

| t <sub>HD</sub>    | Data hold from write end                            | 0.0   | -       | ns |  |

| t <sub>LZWE</sub>  | WE HIGH to low Z [13, 14, 15]                       | 3.0   | -       | ns |  |

| t <sub>HZWE</sub>  | WE LOW to high Z <sup>[13, 14, 15]</sup>            | _     | 5.0     | ns |  |

| t <sub>BW</sub>    | Byte enable to end of write                         | 7.0   | -       | ns |  |

Notes

14. At any temperature and voltage condition,  $t_{HZCE}$  is less than  $t_{LZCE}$ ,  $t_{HZBE}$  is less than  $t_{LZDE}$ ,  $t_{HZOE}$  is less than  $t_{LZOE}$ , and  $t_{HZWE}$  is less than  $t_{LZWE}$  for any device. 15. Tested initially and after any design or process changes that may affect these parameters.

16. These parameters are guaranteed by design and are not tested.

17. The internal write time of the memory is defined by the overlap of  $\overline{WE}$ ,  $\overline{CE} = V_{IL}$ . Chip enable must be active and  $\overline{WE}$  and byte enables must be LOW to initiate a write, and the transition of any of these signals can terminate. The input data setup and hold timing should be referenced to the edge of the signal that terminates the write. 18. The minimum write cycle time for Write Cycle No. 2 (WE Controlled,  $\overline{OE}$  LOW) is the sum of t<sub>HZWE</sub> and t<sub>SD</sub>.

Test conditions assume signal transition time of 3 ns or less, timing reference levels of 1.5 V, and input pulse levels of 0 to 3.0 V. Test conditions for the read cycle use output loading shown in part a) of Figure 3 on page 7, unless specified otherwise.

t<sub>POWER</sub> gives the minimum amount of time that the power supply is at typical V<sub>CC</sub> values until the first memory access is performed.

t<sub>HZOE</sub>, t<sub>HZCE</sub>, t<sub>HZWE</sub>, t<sub>HZEE</sub>, t<sub>LZWE</sub>, and t<sub>LZBE</sub> are specified with a load capacitance of 5 pF as in (b) of Figure 3 on page 7. Transition is measured ±200 mV from steady state voltage.

#### **Switching Waveforms**

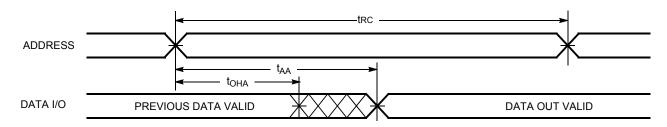

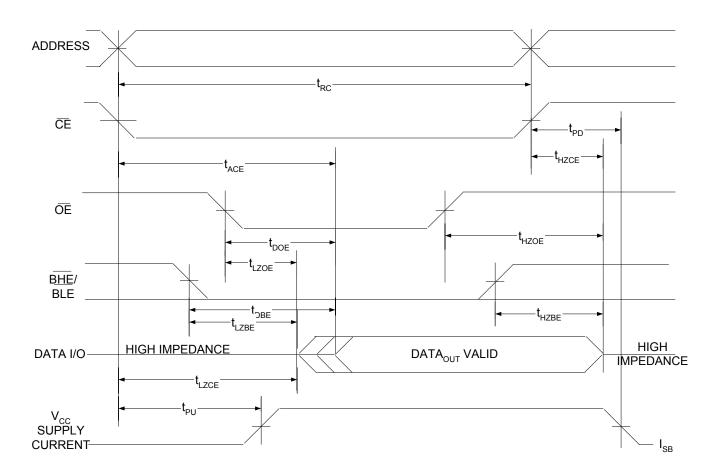

Figure 5. Read Cycle No. 1 (Address Transition Controlled) for CY7C10612G <sup>[19, 20]</sup>

Notes

19. <u>The</u> device is continuously selected.  $\overline{OE}$ ,  $\overline{CE} = V_{IL}$ ,  $\overline{BHE}$ ,  $\overline{BLE}$  or both =  $V_{IL}$ .

20.  $\overline{\text{WE}}$  is HIGH for read cycle.

<sup>21.</sup> Address valid before or similar to  $\overline{CE}$  transition LOW.

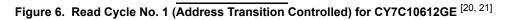

#### Switching Waveforms (continued)

Figure 7. Read Cycle No. 2 (OE Controlled) <sup>[22, 23]</sup>

Notes

22. WE is HIGH for read cycle.

23. Address valid before or similar to CE transition LOW.

#### Switching Waveforms (continued)

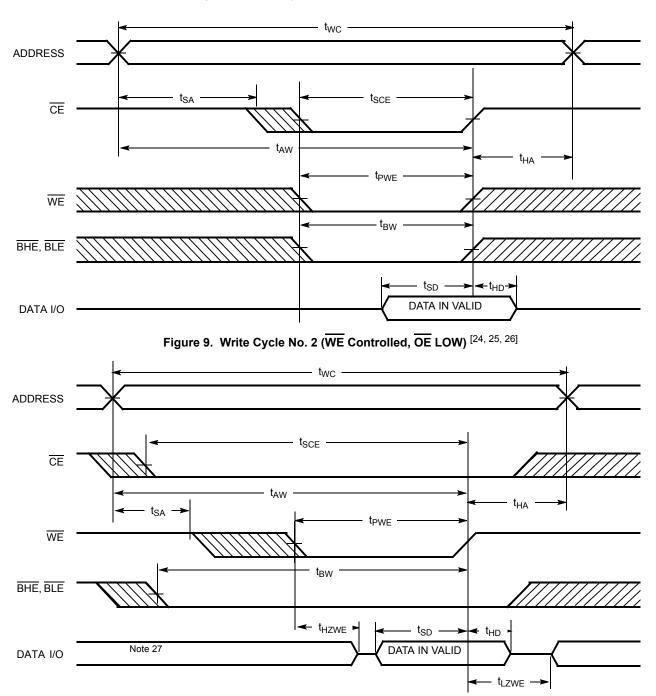

Figure 8. Write Cycle No. 1 (CE Controlled) <sup>[24, 25, 26]</sup>

#### Notes

24. Data I/O is high impedance if  $\overline{OE}$ ,  $\overline{BHE}$ , and/or  $\overline{BLE} = V_{IH}$ .

- 25. The internal write time of the memory is defined by the overlap of  $\overline{WE} = V_{IL}$ ,  $\overline{CE} = V_{IL}$  and  $\overline{BHE}$  or  $\overline{BLE} = V_{IL}$ . These signals must be LOW to initiate a write, and the HIGH transition of any of these signals can terminate the operation. The input data setup and hold timing should be referenced to the edge of the signal that terminates the write.

- 26. The minimum write cycle pulse width should be equal to the sum of  $t_{HZWE}$  and  $t_{SD}$ .

- 27. During this period the I/Os are in output state. Do not apply input signals.

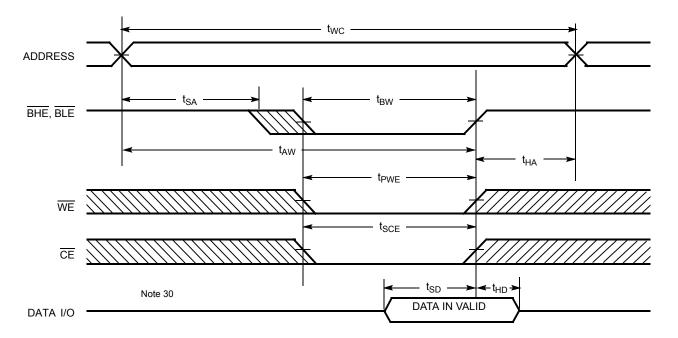

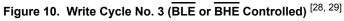

#### Switching Waveforms (continued)

Notes

28. Data I/O is high impedance if OE, BHE, and/or BLE = V<sub>IH</sub>.

29. The internal write time of the memory is defined by the overlap of WE = V<sub>IL</sub>, CE = V<sub>IL</sub> and BHE or BLE = V<sub>IL</sub>. These signals must be LOW to initiate a write, and the HIGH transition of any of these signals can terminate the operation. The input data setup and hold timing should be referenced to the edge of the signal that terminates in the terminate the operation. The input data setup and hold timing should be referenced to the edge of the signal that terminates in the terminate the operation. the write.

30. During this period, the I/Os are in output state. Do not apply input signals.

## Truth Table

| CE | OE | WE | BLE | BHE | I/O <sub>0</sub> –I/O <sub>7</sub> | I/O <sub>8</sub> –I/O <sub>15</sub> | Mode                       | Power                      |

|----|----|----|-----|-----|------------------------------------|-------------------------------------|----------------------------|----------------------------|

| Н  | Х  | Х  | Х   | Х   | High Z                             | High Z                              | Power-down                 | Standby (I <sub>SB</sub> ) |

| L  | L  | Н  | L   | L   | Data Out                           | Data Out                            | Read all bits              | Active (I <sub>CC</sub> )  |

| L  | L  | Н  | L   | Н   | Data Out                           | High Z                              | Read lower bits only       | Active (I <sub>CC</sub> )  |

| L  | L  | Н  | Н   | L   | High Z                             | Data Out                            | Read upper bits only       | Active (I <sub>CC</sub> )  |

| L  | Х  | L  | L   | L   | Data In                            | Data In                             | Write all bits             | Active (I <sub>CC</sub> )  |

| L  | Х  | L  | L   | Н   | Data In                            | High Z                              | Write lower bits only      | Active (I <sub>CC</sub> )  |

| L  | Х  | L  | Н   | L   | High Z                             | Data In                             | Write upper bits only      | Active (I <sub>CC</sub> )  |

| L  | Н  | Н  | Х   | Х   | High Z                             | High Z                              | Selected, outputs disabled | Active (I <sub>CC</sub> )  |

## ERR Output – CY7C10612GE

| Output <sup>[31]</sup> | Mode                                                      |  |  |

|------------------------|-----------------------------------------------------------|--|--|

| 0                      | Read Operation, no error in the stored data.              |  |  |

| 1                      | Read Operation, single-bit error detected and corrected.  |  |  |

| High-Z                 | Device deselected or Outputs disabled or Write Operation. |  |  |

#### **Ordering Information**

| Speed<br>(ns) | Ordering Code         | Package<br>Diagram | Package Type (Pb-free)                      | Operating<br>Range |

|---------------|-----------------------|--------------------|---------------------------------------------|--------------------|

| 10            | CY7C10612G30-10ZSXI   | 51-85160           | 54-pin TSOP II                              | Industrial         |

|               | CY7C10612G30-10ZSXIT  |                    | 54-pin TSOP II, Tape and Reel               |                    |

|               | CY7C10612GE30-10ZSXI  |                    | 54-pin TSOP II, with ERR Pin                |                    |

|               | CY7C10612GE30-10ZSXIT | 1                  | 54-pin TSOP II, with ERR Pin, Tape and Reel |                    |

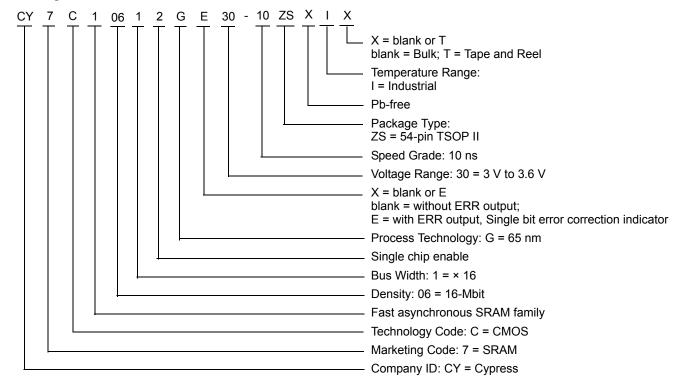

#### **Ordering Code Definitions**

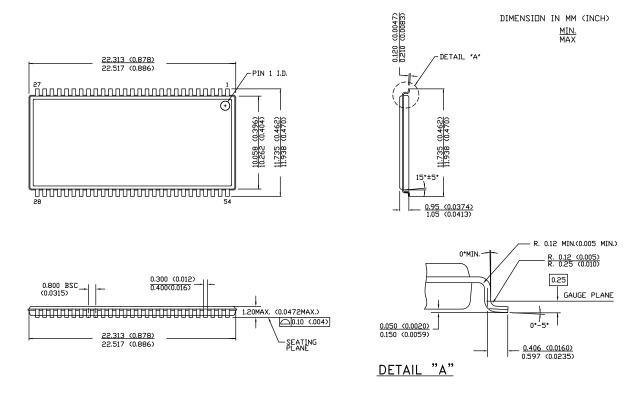

#### **Package Diagrams**

Figure 11. 54-pin TSOP II (22.4 × 11.84 × 1.0 mm) Z54-II Package Outline, 51-85160

51-85160 \*E

#### Acronyms

#### Table 1. Acronyms Used in this Document

| Acronym | Description                             |  |  |  |

|---------|-----------------------------------------|--|--|--|

| BHE     | Byte High Enable                        |  |  |  |

| BLE     | Byte Low Enable                         |  |  |  |

| CE      | Chip Enable                             |  |  |  |

| CMOS    | Complementary Metal Oxide Semiconductor |  |  |  |

| I/O     | Input/Output                            |  |  |  |

| OE      | Output Enable                           |  |  |  |

| SRAM    | Static Random Access Memory             |  |  |  |

| TSOP    | Thin Small Outline Package              |  |  |  |

| TTL     | Transistor-Transistor Logic             |  |  |  |

| WE      | Write Enable                            |  |  |  |

#### **Document Conventions**

#### Units of Measure

#### Table 2. Units of Measure

| Symbol | Unit of Measure |

|--------|-----------------|

| °C     | degree Celsius  |

| MHz    | megahertz       |

| μA     | microampere     |

| μS     | microsecond     |

| mA     | milliampere     |

| mm     | millimeter      |

| mV     | millivolt       |

| ns     | nanosecond      |

| Ω      | ohm             |

| %      | percent         |

| pF     | picofarad       |

| V      | volt            |

| W      | watt            |

## **Document History Page**

## Document Title: CY7C10612G/CY7C10612GE, 16-Mbit (1M × 16) Static RAM

| Rev. | ECN No. | Orig. of<br>Change | Submission<br>Date | Description of Change                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------|---------|--------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| *D   | 4865557 | NILE               | 07/31/2015         | Changed status from Preliminary to Final.                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| *E   | 5437839 | NILE               | 09/15/2016         | Updated Maximum Ratings:<br>Updated Note 4 (Replaced "2 ns" with "20 ns").<br>Updated DC Electrical Characteristics:<br>Removed all values corresponding to V <sub>OH</sub> parameter.<br>Included Operating Ranges "2.2 V to 2.7 V" and "2.7 V to 3.0 V" and all values<br>corresponding to V <sub>OH</sub> parameter.<br>Updated Ordering Information:<br>Updated part numbers.<br>Updated Ordering Code Definitions.<br>Updated to new template.<br>Completing Sunset Review. |

| *F   | 6011828 | AESATMP8           | 01/03/2018         | Updated logo and Copyright.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

#### Sales, Solutions, and Legal Information

#### Worldwide Sales and Design Support

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at Cypress Locations.

#### Products

| Arm <sup>®</sup> Cortex <sup>®</sup> Microcontrollers | cypress.com/arm        |

|-------------------------------------------------------|------------------------|

| Automotive                                            | cypress.com/automotive |

| Clocks & Buffers                                      | cypress.com/clocks     |

| Interface                                             | cypress.com/interface  |

| Internet of Things                                    | cypress.com/iot        |

| Memory                                                | cypress.com/memory     |

| Microcontrollers                                      | cypress.com/mcu        |

| PSoC                                                  | cypress.com/psoc       |

| Power Management ICs                                  | cypress.com/pmic       |

| Touch Sensing                                         | cypress.com/touch      |

| USB Controllers                                       | cypress.com/usb        |

| Wireless Connectivity                                 | cypress.com/wireless   |

#### PSoC<sup>®</sup> Solutions

PSoC 1 | PSoC 3 | PSoC 4 | PSoC 5LP | PSoC 6 MCU

Cypress Developer Community Community | Projects | Video | Blogs | Training | Components

Technical Support cypress.com/support

TO THE EXTENT PERMITTED BY APPLICABLE LAW, CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS DOCUMENT OR ANY SOFTWARE OR ACCOMPANYING HARDWARE, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. No computing device can be absolutely secure. Therefore, despite security measures implemented in Cypress hardware or software products, Cypress does not assume any liability arising out of any security breach, such as unauthorized access to or use of a Cypress product. In addition, the products described in these materials may contain design defects or errors known as errata which may cause the product to deviate from published specifications. To the extent permitted by applicable law, Cypress reserves the right to make changes to this document without further notice. Cypress does not assume any liability arising out of the application or use of any product or circuit described in this document. Any information provided in this document, including any sample design information or programming code, is provided only for reference purposes. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. Cypress products are not designed, intended, or authorized for use as critical components in systems designed or intended for the operation of weapons, weapons systems, nuclear installations, life-support devices or system could cause personal injury, death, or properly damage ("Unintended Uses"). A critical component is any component of a device or system whose failure to perform can be reasonably expected to cause the failure of the device or system, or to affect its safety or effectiveness. Cypress is not liable, in whole or in part, and you shall and hereby do release Cypress from any claim, damage, or other liability arising from or related to any Unintended Uses of Cypress products.

Cypress, the Cypress logo, Spansion, the Spansion logo, and combinations thereof, WICED, PSoC, CapSense, EZ-USB, F-RAM, and Traveo are trademarks or registered trademarks of Cypress in the United States and other countries. For a more complete list of Cypress trademarks, visit cypress.com. Other names and brands may be claimed as property of their respective owners.

<sup>©</sup> Cypress Semiconductor Corporation, 2013-2018. This document is the property of Cypress Semiconductor Corporation and its subsidiaries, including Spansion LLC ("Cypress"). This document, including any software or firmware included or referenced in this document ("Software"), is owned by Cypress under the intellectual property laws and treaties of the United States and other countries worldwide. Cypress reserves all rights under such laws and treaties and does not, except as specifically stated in this paragraph, grant any license under its patents, copyrights, trademarks, or other intellectual property rights. If the Software is not accompanied by a license agreement and you do not otherwise have a written agreement with Cypress governing the use of the Software, then Cypress hereby grants you a personal, non-exclusive, nontransferable license (without the right to sublicense) (1) under its copyright rights in the Software provided in source code form, to modify and reproduce the Software solely for use with Cypress hardware products, only internally within your organization, and (b) to distribute the Software in binary code form externally to end users (either directly or indirectly through resellers and distributors), solely for use on Cypress hardware product units, and (2) under those claims of Cypress's patents that are infringed by the Software (as provided by Cypress, unmodified) to make, use, distribute, and import the Software solely for use with Cypress hardware products. Any other use, reproduction, modification, translation, or compilation of the Software is prohibited.