Q

### High-Speed CMOS 4K x 9 Clocked FIFO with Output Enable

**QS7244A**

#### FEATURES/BENEFITS

- Clocked Interface FIFOs for High-Speed Systems

- Data and Flags Change on Rising Edge of Clocks

- · Fully Asynchronous Read and Write

- TTL Input and Output Level Compatible

- Very Low Power

- · Coincidental or Different Read/Write Clocks

- 66 MHz Cycle Time

- Depth and Width Expandable

- · Registered Flow-Through Architecture

- Available in 32-pin PLCC & 28-Pin SOJ Package

- Asynchronous Output Enable

- · Noise Filters on Input Control Lines

#### DESCRIPTION

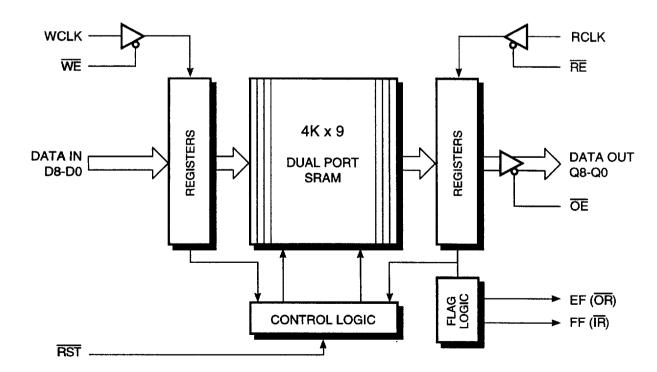

The QS7244A is a 4K x 9 clocked or synchronous FIFO. It has independent clocked interfaces for both Read and Write which minimize the potential for noise on the Read and Write to false trigger and incorrectly advance the pointers. Additional Read/Write circuitry makes interfacing at high-speed much easier as no pulse shaping is required. The part also has an empty and full flag EF and FF which can be looked upon as input ready and output ready,  $(\overline{IR} \text{ and } \overline{OR})$  for those who are familiar with that nomenclature. An output enable is provided to allow the part to be tristated. This part can be used in high-speed datacomms, data compression, image processing and graphics systems.

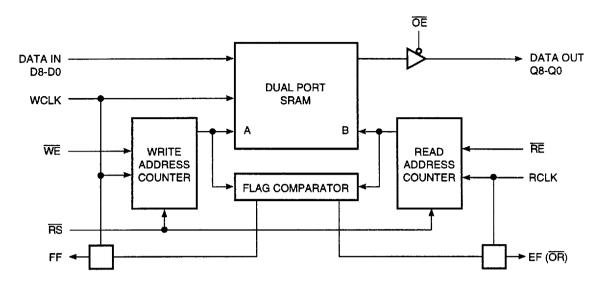

#### **FUNCTIONAL BLOCK DIAGRAM**

#### OPERATIONAL DESCRIPTION

These interfaces provide high-speed data buffering in system designs and allow symmetrical clocks at speeds to 66 MHz. The clocks are controlled by Read and Write enable lines. Write enable and Write data are accepted at the rising edge of the Write clock. Read enable is accepted at the rising edge of the Read clock and Read data changes after the Read clock edge. Flag changes occur after either the Write clock edge or the Read clock edge, depending on the operation being performed. This FIFO uses a dual-port RAM based architecture with independent Read and Write pointers. These pointers are set to zero by the reset pulse, creating an empty condition. A Write Enable causes data to be written and the Write pointer to be incremented by the rising edge of the write clock. If the FIFO was empty, the Write data will flow directly to the outputs, and the empty flag will be cleared to indicate the output data is valid. A Read Enable will cause the Read pointer to be incremented to the next word on the rising edge of the Read clock. If there was only one word in the FIFO, the empty flag will be set by this same rising edge. The flag circuitry is based on a reliable sequential design giving precise full and empty conditions. These flags also prevent the FIFO from being written into when full or being read from when empty.

#### PIN DESCRIPTIONS

| Name    | VO | Description   |

|---------|----|---------------|

| D       | ı  | Data Inputs   |

| Q       | 0  | Data Outputs  |

| RCLK    | ı  | Read Clock    |

| RE      | ļ  | Read Enable   |

| WCLK    | 1  | Write Clock   |

| WE      | ı  | Write Enable  |

| RS      | ı  | Reset         |

| EF(OR)  | 0  | Empty Fag     |

| FF (IR) | 0  | Full Flag     |

| ŌĒ      | I  | Output Enable |

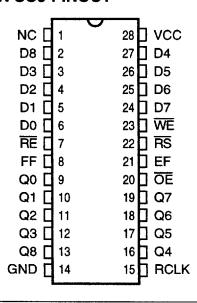

#### 28-PIN SOJ PINOUT

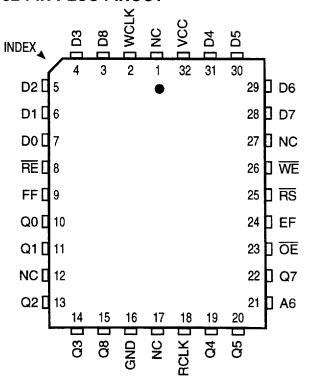

#### 32-PIN PLCC PINOUT

#### **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltage to Gound                     |                     |

|---------------------------------------------|---------------------|

| DC Output Voltage Vouт                      | –0.5 to Vcc +0.5V   |

| DC Input Voltage Vin                        | 0.5 to Vcc +0.5V    |

| AC Input Voltage (Pulse Width ≤ 20 ns)      | 3.0V                |

| DC Input Diode Current with Vin < 0         | 20 mA               |

| DC Output Diode Current with Vout < 0       | 50 mA               |

| DC Output Current with Vout > Vcc           | 50 mA               |

| DC Output Current Max. Sink Current/Pin     |                     |

| DC Output Current Max. Source Current/Pin   | –30 mA              |

| Total DC Ground Current                     | (Nxlo∟ + Mx∆lcc) mA |

| Total DC Vcc Power Supply Current           | (Nxloн + Mx∆lcc) mA |

| N = Number of outputs, M = Number of inputs |                     |

| Maximum Power Dissipation                   |                     |

| Тsтс Storage Temperature                    | 65°C to +165°C      |

Note: Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to this device resulting in functional or reliability type failures.

#### **CAPACITANCE**

Ta = 25°C, f = 1.0 MHz TQFP (TF) Package

| Name     | Description       | Conditions          | Тур | Max | Units |

|----------|-------------------|---------------------|-----|-----|-------|

| CIN/COUT | Input Capacitance | Vin = 0V, f = 1 MHz | 5   | 8   | рF    |

Note: Capacitance is guaranteed but not tested

#### DC ELECTRICAL CHARACTERISTICS OVER OPERATING RANGE

$T_A = 25^{\circ}C$  to 70°C,  $V_{CC} = 5.0V \pm 10\%$

| Symbol  | Parameter           | Test Conditions               | Min | Max      | Units |

|---------|---------------------|-------------------------------|-----|----------|-------|

| Vін     | Input HIGH Voltage  | Logic HIGH for All Conditions | 2.0 | 6.0      | V     |

| VIL     | Input LOW Voltage   | Logic LOW for All Conditions  | _   | 0.8      | V     |

| Vон     | Output HIGH Voltage | loн = −2 mA, Vcc = Min        | 2.4 | <u> </u> | V     |

| Vol     | Output LOW Voltage  | IoL = 8 mA, Vcc = Min         |     | 0.4      | V     |

| 1 lı∟ l | Input Leakage       | Vcc = Max, GND < Vin < Vcc    |     | 5        | μΑ    |

| l loz l | Output Leakage      | Vcc = 5.5V, Vo = Vcc or 0V    | _   | 10       | μа    |

#### **POWER SUPPLY CHARACTERISTICS**

$T_A = 25$ °C to 70°C,  $V_{CC} = 5.0V \pm 10$ %

|        |                                                                   | Cycle Time (ns) |     |     |     |     |       |

|--------|-------------------------------------------------------------------|-----------------|-----|-----|-----|-----|-------|

| Symbol | Parameter                                                         | -15             | -20 | -25 | -30 | -40 | Units |

| lcc1   | Operating Current Vcc = Max, Outputs Open RE = WE = VIL, f = fMAX | 165             | 150 | 140 | 140 | 135 | mA    |

| lcc2   | Standby Current  RE = WE = RS = Vcc - 2.0V  Clocks Free Running   | 15              | 15  | 15  | 15  | 15  | mA    |

MDSF-00008-04

QUALITY SEMICONDUCTOR, INC.

#### **QS7244A PRELIMINARY**

#### **SWITCHING CHARACTERISTICS OVER OPERATING RANGE**

$Vcc = 5V \pm 10\%$ , Commercial T<sub>A</sub> = 0°C to +70°C

| Symbol     | Parameter                                                                           | -15  | -20 | -25 | -30 | -40 | Units | Type |

|------------|-------------------------------------------------------------------------------------|------|-----|-----|-----|-----|-------|------|

| fac, fwc   | Read or Write Clock, MHz(2)                                                         | 66.7 | 50  | 40  | 33  | 25  | MHz   | Max  |

| trc, twc   | Read or Write Cycle Time                                                            | 15   | 20  | 25  | 30  | 40  | ns    | Min  |

| tcw        | Read or Write Clock HIGH or LOW(1)                                                  | 7    | 8   | 10  | 12  | 15  | ns    | Min  |

| ts         | Setup Time                                                                          | 5    | 5   | 6   | 10  |     | ns    | Min  |

| tн         | Hold Time                                                                           | 0    | 0   | 0   | 0   | 0   | ns    | Min  |

| tcf        | Clock to Flag Valid Output Delay                                                    | 7    | 8   | 9   | 10  | 12  | ns    | Max  |

| tcp        | Clock to Data Valid Output Delay                                                    | 9    | 10  | 11  | 12  | 14  | ns    | Min  |

| trs        | Reset Pulse Width <sup>(1)</sup>                                                    | 8    | 10  | 15  | 17  | 19  | ns    | Min  |

| tefl, tffl | Flag Latency, $\overline{RE} \rightarrow EF$ , $\overline{WE} \rightarrow FF^{(4)}$ | 17   | 18  | 20  | 22  | 25  | ns    | Min  |

| toe        | Output Enable to Data Valid                                                         | 5    | 6   | 7   | 8   | 10  | ns    | Min  |

| tolz       | Output Enable LOW to Low-Z(2)                                                       | 2    | 2   | 2   | 2   | 2   | ns    | Min  |

| trsa       | Reset Recovery Time                                                                 | 7    | 8   | 10  | 12  | 14  | ns    | Min  |

| tонz       | Output Enable HIGH to Hi-Z(2)                                                       | 8    | 9   | 10  | 12  | 14  | ns    | Max  |

Notes: These timings are measured as defined in ACTest Conditions

- 1. Pulse widths less than the specified minimum value may upset the internal pointers and are not allowed.

- 2. These values are guaranteed by design and not tested.

- 3. Minimum time to write clock edge for valid write enable to be accepted.

- 4. Time required from write clock edge to read clock edge for write to turn off empty on next clock. from read clock edge to write clock edge for read to turn off full on next clock.

Time required

5. Transition to High-Z is measured ±200 mV from prior steady state voltage.

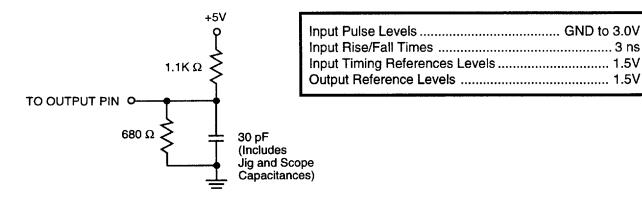

#### **AC TEST CONDITIONS**

#### OPERATIONAL DESCRIPTION

The 7244A Clocked FIFO consists of a dual port RAM, Read and Write address counters, a flag comparator, and synchronizing flip flops for the flags. A simplified block diagram of the 7244A Clocked FIFO is shown below. Note that the internal design of the 7244A Clocked FIFO is more complex than shown for maximum performance. The simplified block diagram shown is provided for understanding the operation of the FIFO. For detailed timing in formation, refer to the AC Specifications and timing diagrams.

QUALITY SEMICONDUCTOR, INC.

#### **QS7244A PRELIMINARY**

**Clocked FIFO Simplified Block Diagram**

The dual port RAM is a static RAM with two independent sets of addressing logic. Each set of addressing logic can simultaneously and independently address words in the RAM. Each combination of addressing logic and its associated data I/O is called a port, hence the name dual port RAM. In the FIFO, one port is used only for writing and one port only for reading. If both ports have the same address and data is written by one port, the same data will be read immediately by the other port. The data is said to flow through the RAM.

The Read and Write address counters address the Read and Write ports of the dual port RAM. Each is a binary counter that increments on the rising edge of the clock, and is enabled for counting by a low active enable signal. These counters are asynchronously reset by a reset pulse.

Data is written into the dual port RAM when each Write clock validated by a WE increments the Write address pointer. If the FIFO is empty, data from the write port will flow through to the read port following three write clock pulses (Fall-through mode). No RE is necessary to present the first word on to the outputs. Subsequent RCLK is validated by RE are needed to update the Read pointer and output subsequent data words. The 'flow-through' of this initial dataword happens regardless of the state of the RE input.

The flag comparator continuously compares the contents of the two address counters. If the contents of the two address counters are equal, the FIFO is empty, and the empty flag is active. This is the case immediately after a reset pulse when both counters have been reset to zero. If the Write address counter value is equal to the Read address counter value plus the depth of the RAM (e.g., 4096 for a 4K x 9 FIFO), the FIFO is full, and the full flag is active. The flag outputs from the flag comparator are synchronized in flip flops by the appropriate Read or Write clocks so they change only following the rising edge of a clock.

Read and Write enable are inhibited by the empty and full flags, respectively. If the FIFO is empty, Read enable is inhibited because there is no next word in the FIFO to step to. If the FIFO is full, both the Write enable and the Write clock to the dual port RAM are inhibited because there is no place available to Write another word. (The gates corresponding to these Read and Write enable inhibits are not shown on the simplified block diagram.) Note that when there is one word in the FIFO, Read enable is allowed because the FIFO is stepping to the another word. Write enable and Read enable can be considered as "write current word" and "read next word," respectively.

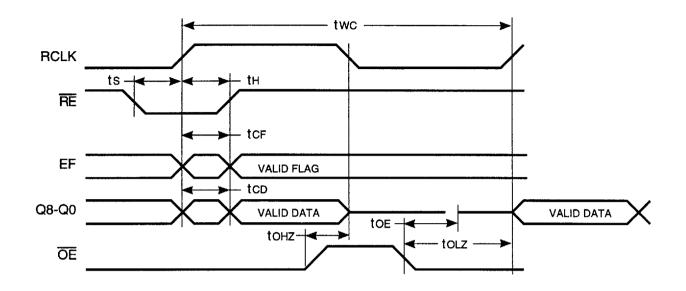

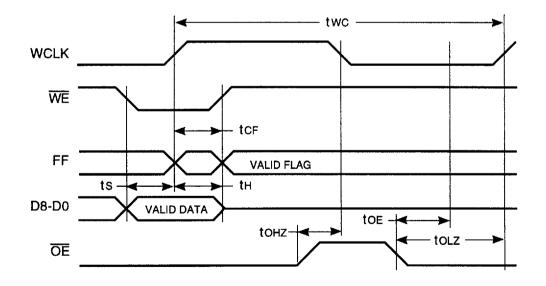

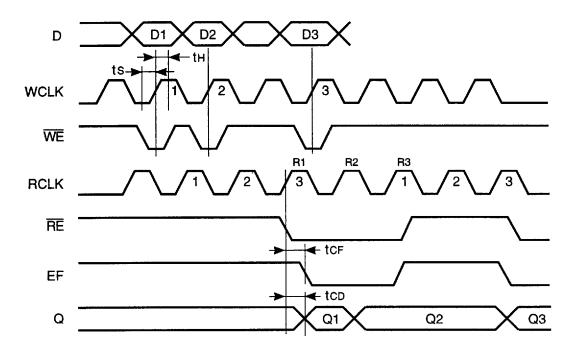

The general operation of the 7244A Clocked FIFO is shown in the following timing diagrams.

#### **QS7244A PRELIMINARY**

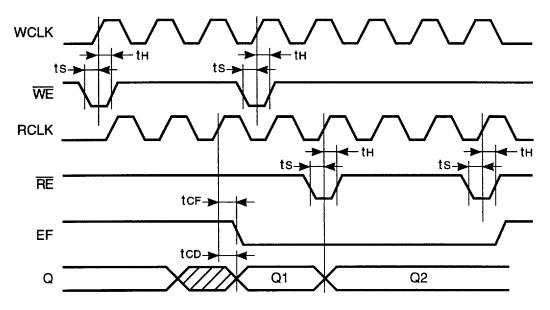

# TIMING DIAGRAMS SINGLE READ OPERATION TIMING

#### WRITE OPERATION TIMING

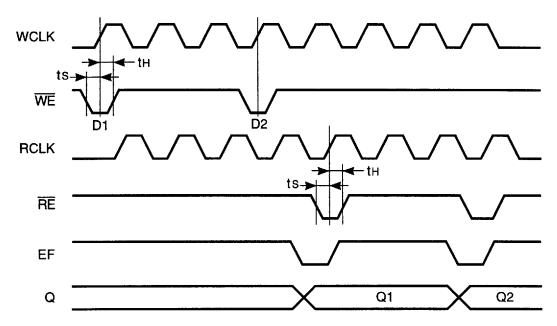

#### **OPERATION WITH NO SKEW VIOLATION**

Note: Normal operation with no skew violation on the Empty Flag boundary.

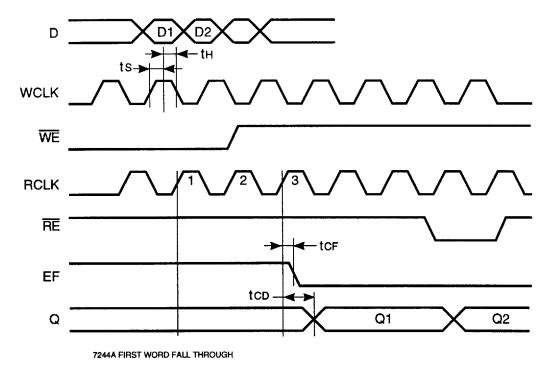

#### FLOW-THROUGH LATENCY TIMING

Note: Normal operation with no skew violation on the Empty Flag boundary.

Following a three read clock latency, valid data appears on the output bus and EF is updated. Under non tskew violations the EF and the first data word will come out relative to the third read clock. The second data written in the same cycle (the cycle in which EF goes LOW) will be available when RE goes LOW with no latency.

MDSF-00008-04

QUALITY SEMICONDUCTOR, INC.

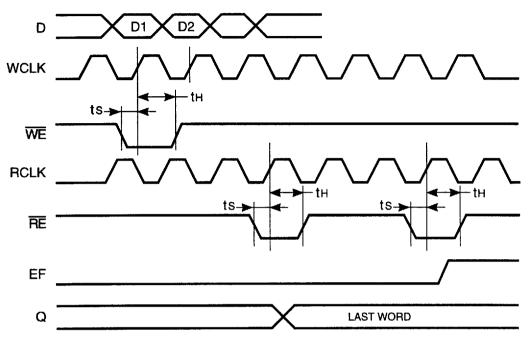

#### LAST WORD READ OPERATION

When the last word is read, valid data appears on the output bus.  $\overline{\text{RE}}$  must be asserted again to update the EF, which will inhibit further reads from the FIFO. This can occur no sooner than one cycle after the last Read.

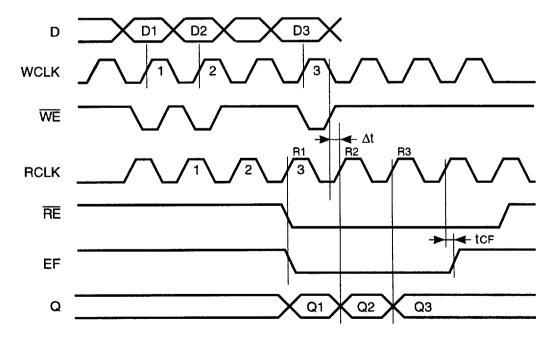

#### THREE WRITES AND THREE READS WITH ASYNCHRONOUS CLOCKS

If the  $\Delta t$  between the falling edge of WCLK3 and the rising edge of R2 is not violated the 7244A will outuall three words continuously.

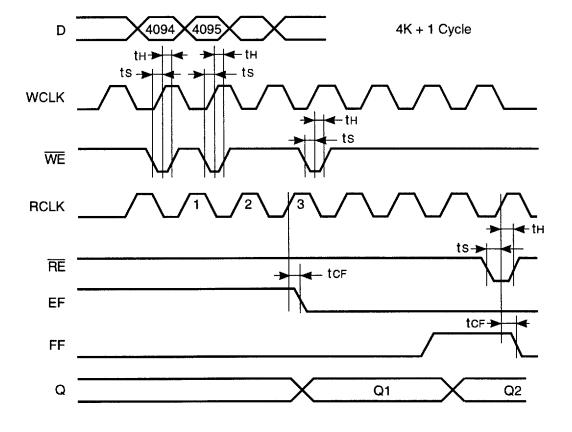

### THREE WRITES AND THREE READS WITH ASYNCHRONOUS CLOCKS fwclk < frclk $\Delta t$

If the  $\Delta t$  between the falling edge of WCLK3 and the rising edge of RCLK2 is violated, the 7244A will not have enough time to process data word three. Therefore, the 7244A will asert the EF at the next RCLK and the third data word will take another 3 clock latency to output. ( $\overline{RE}$  not needed to output this word). Word 3 is not lost and is still in sync with EF.

Under this condition the EF and the first data word will come out relative to the fourth Read clock. If a second Write operation occurs within the same cycle, the EF will go HIGH when the next  $\overline{\text{RE}}$  goes LOW. EF will then go LOW with the second data word after another latency of four cycles.

#### **tskew ON BOUNDARY CONDITIONS**

In this condition, the latency is at the boundary between meeting and violating the skew timing. The EF and first data behave the same as the example above except the second data appears with no additional latency.

#### **FULL FLAG BOUNDARY**

QUALITY SEMICONDUCTOR, INC.

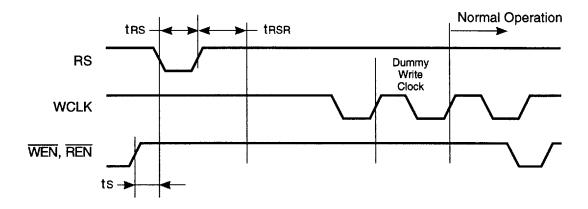

#### **RESET OPERATION**

After a reset cycle, one dummy Write clock is required before the FIFO can resume normal operation.

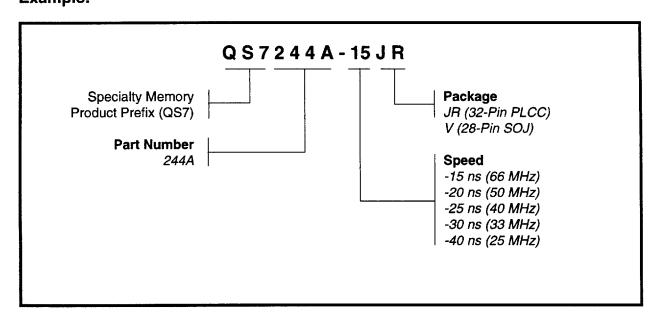

## ORDERING INFORMATION Example: