TOSHIBA CMOS Integrated Circuit Silicon Monolithic

# TC32306FTG

Single-Chip RF Transceiver for Low-Power Systems

## 1. General Description

The TC32306FTG is a single-chip RF transceiver, which provides many of the functions required for UHF-band transceiver applications. It has the most features transmitting and receiving the signal.

Furthermore, by digital processing, it can reduce significantly the number of external components and allow fine adjustments.

Various type of applications are supported by this chip as configuring various settings such as supply voltage, frequency, modulation and detection.

## 2. Applications

Remote keyless entry (remote door lock / unlock of equipment), automotive equipment applications such as tire pressure monitoring system, and remote controller, etc

## 3. Features

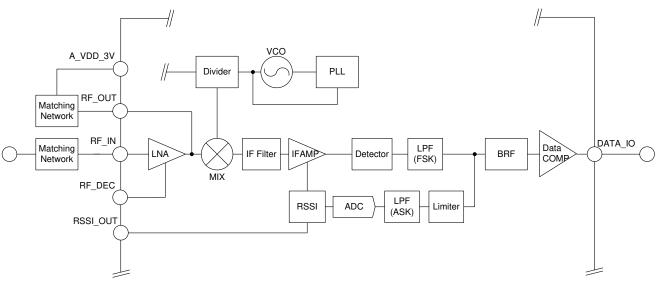

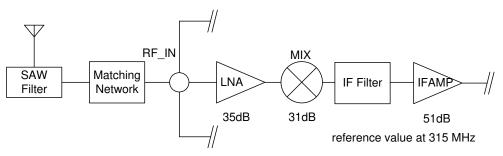

- Integrates LNA, Mixer, IF Filter, IF AMP, RSSI, Signal Detector, Bit Rate Filter, Data Comparator, PLL, VCO and PA into a single IC.

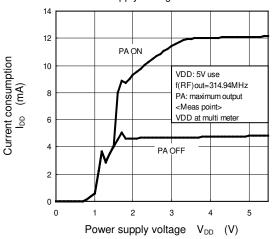

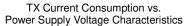

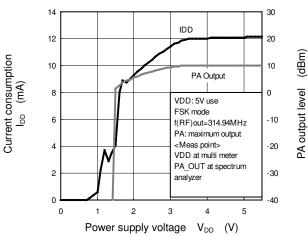

- Operating voltage range: 2.0 to 3.3 V (For 3V Use), 2.4V to 5.5V (For 5V Use)

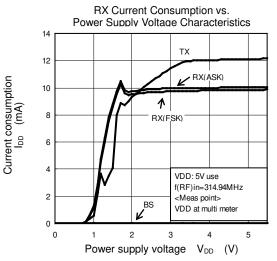

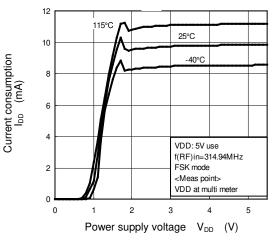

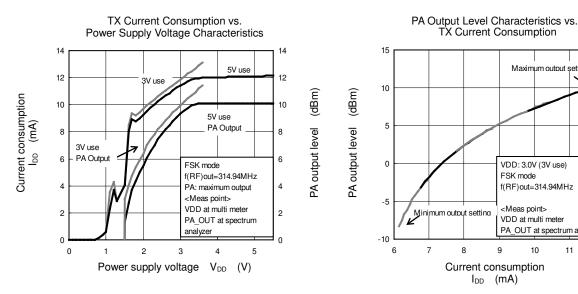

- Current consumption: TX 12 mA at +10dBm output level / RX 9.7 mA / Battery Saving 0µA (typ.)

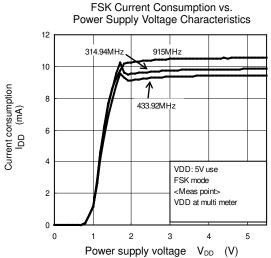

- Use for four RF Band: 315, 434, 868 / 915 MHz

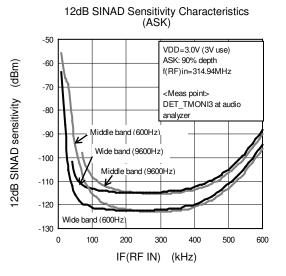

- Supported modulation: ASK / FSK

- Single conversion system

- Two IF Filter bandwidth: wide 320kHz(typ.) at IF = 230kHz / middle 270kHz(typ.) at IF = 280kHz

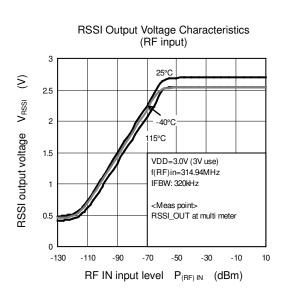

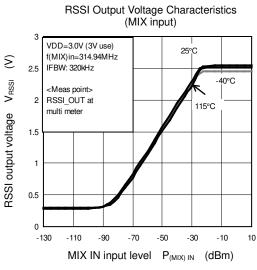

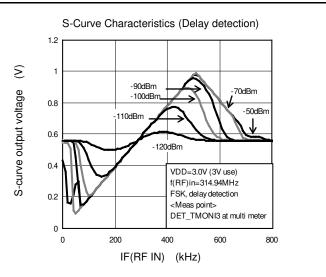

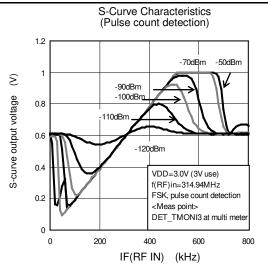

- Signal Detections: RSSI detection, Noise detection (Only for FSK), Preamble detection

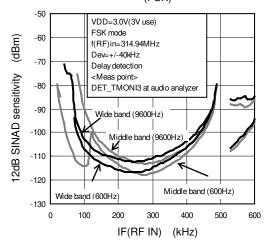

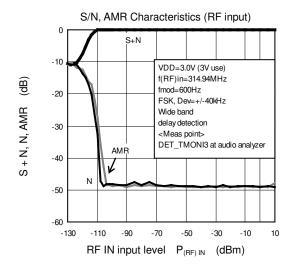

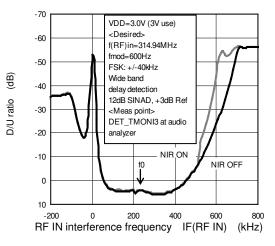

- Receiver sensitivity: under -116dBm (At IF BW = 320kHz, data rate = 600Hz, frequency deviation = +/-40kHz)

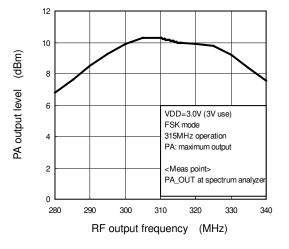

- Transmitter power: +10dBm (typ. at setting maximum output)

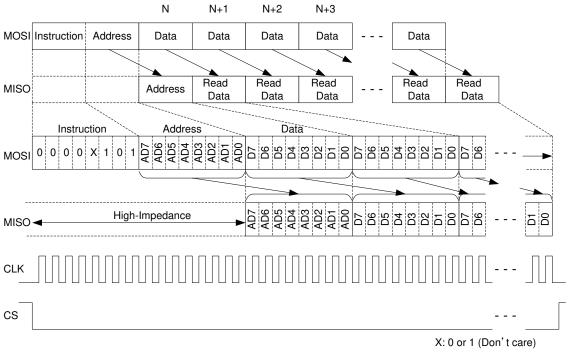

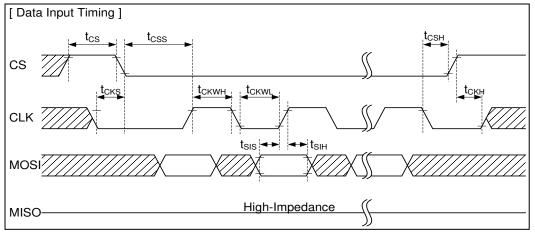

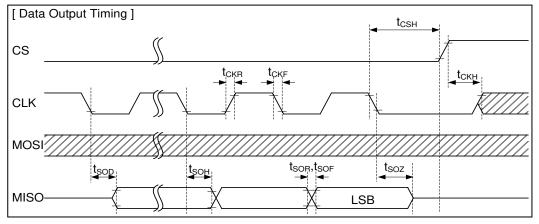

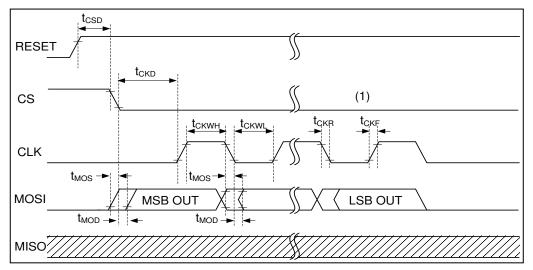

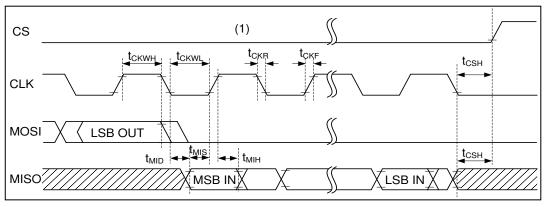

- Serial control (4 wire SPI) / EEPROM control

- Data Comparator Quick Charge / AutoOff Control / Antenna Switch Control

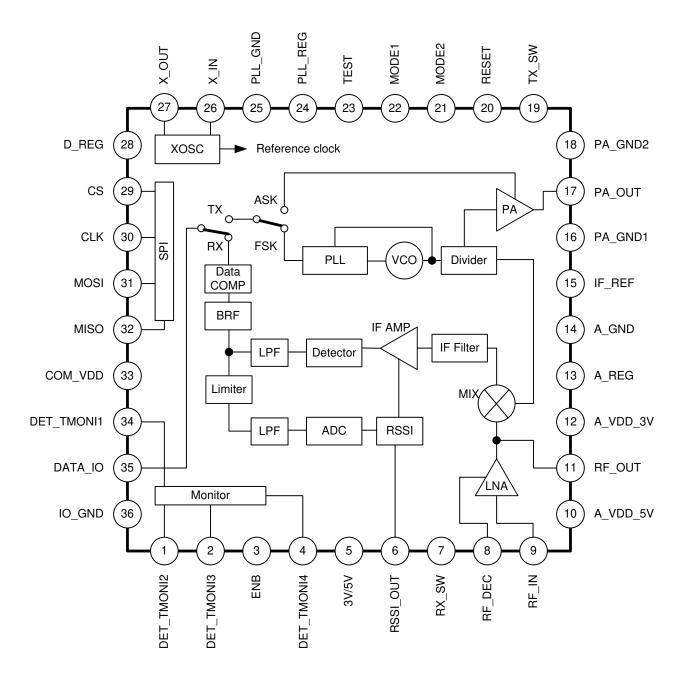

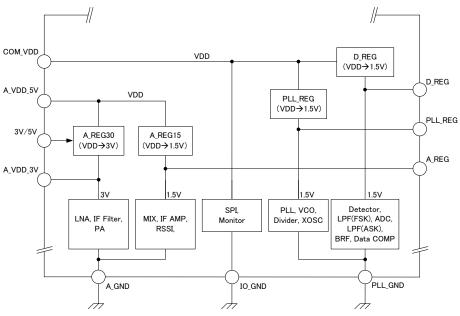

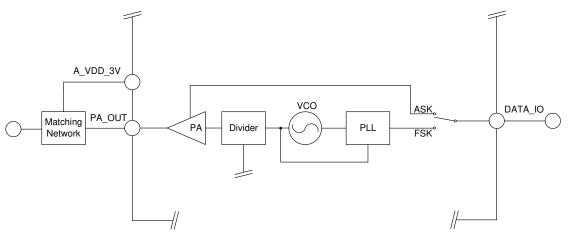

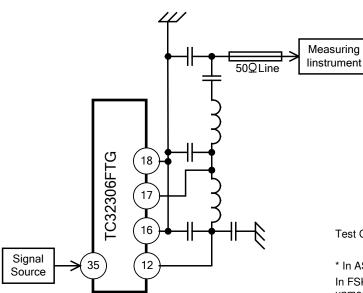

## 4. Block Diagram

Some of the functional blocks, circuits, or constants in the block diagram may be omitted or simplified for explanatory purposes.

## Fig 4-1 Block Diagram

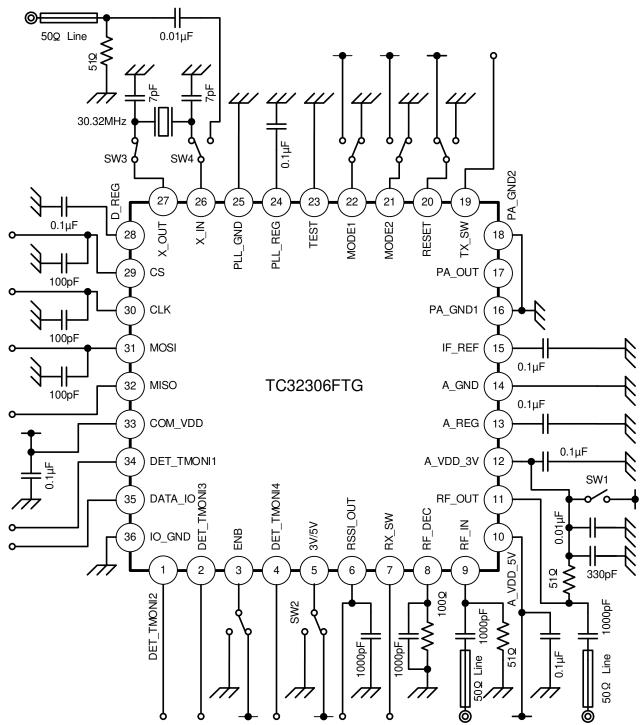

## 5. Pin Description

## 5.1 Equivalent Circuit and Function

## Table 5-1 Pin Description

All the values (resistance, capacity, etc.) shown in the internal equivalent circuit diagram are typical values.The equivalent circuit diagrams may be simplified or some parts of them may be omitted for explanatory purpose.

| Pin No. | Pin Name   | I/O               | Description                                                                                                                                                                                                                                                                                                                                                                                      | Internal Equivalent Circuit |

|---------|------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| 1       | DET_TMONI2 | Digital<br>Output | Monitor 2<br>Monitoring internal signals (digital), use<br>for system control<br>At no use, open this pin.                                                                                                                                                                                                                                                                                       | DET_TMONI2                  |

| 2       | DET_TMONI3 | Analog<br>Output  | Monitor 3<br>Monitoring internal signals (Converted to<br>analog / in User Test )<br>At no use, open this pin.<br>Notice:<br>In User Test, Supply at least 3 V to<br>COM_VDD pin to monitor the signal.<br>Lower voltage supply causes an incorrect<br>monitoring.                                                                                                                               | DET_TMONI3                  |

| 3       | ENB        | Digital<br>Input  | Enable Pin<br>Select to enable (In SPI Mode)<br>Address Setting (In EEPROM Mode)<br>Set a start address to read memory data.<br>Notice:<br>Do not supply higher voltage than the<br>level of COM_VDD. (For example, in the<br>case of too low / no power supply.) That<br>causes overcurrent at this pin, as the<br>ESD protection elements insertion<br>between the pin and the voltage source. | ENB<br>3                    |

| 4       | DET_TMONI4 | Analog<br>Output  | Monitor 4<br>Monitoring internal signals (Converted to<br>analog / in User Test)<br>At no use, open this pin.<br>Notice:<br>In User Test, Supply at least 3 V to<br>COM_VDD pin to monitor the signal.<br>Lower voltage supply causes an incorrect<br>monitoring.                                                                                                                                | DET_TMONI4                  |

| 5       | 3V/5V      | Digital<br>Input  | Supply Voltage Selector<br>Select supply voltage. Connect power<br>supply for 5V use. / Ground for 3V use.<br>Notice:<br>Do not supply higher voltage than the<br>level of COM_VDD. (For example, in the<br>case of too low / no power supply.) That<br>causes overcurrent at this pin, as the<br>ESD protection elements insertion<br>between the pin and the voltage source.                   |                             |

| Pin No. | Pin Name | I/O               | Description                                                                                                                                                                                                                                                                                                  | Internal Equivalent Circuit                                |

|---------|----------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|

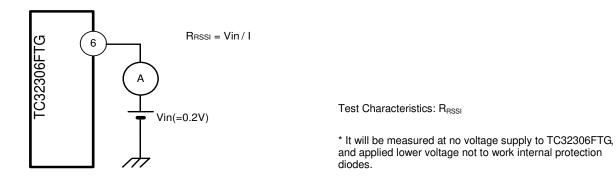

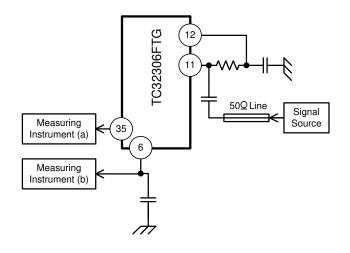

| 6       | RSSI_OUT | Analog<br>Output  | RSSI Output<br>Output RSSI (= Received Signal Strength<br>Indication) voltage. Connect ground via a<br>capacitor. This IC has another RSSI signal<br>for digital processing.<br>At no use, connect ground via a capacitor.                                                                                   | A_VDD_3V A_VDD_3V<br>RSSI_OUT<br>6<br>50kΩ                 |

|         |          | Digital<br>Output | At no use, open this pin.<br>Address Setting (In EEPROM Mode)                                                                                                                                                                                                                                                |                                                            |

| 7       | RX_SW    | Digital<br>Input  | Set a start address to read memory data.<br>Notice:<br>Do not supply higher voltage than the level<br>of COM_VDD. (For example, in the case<br>of too low / no power supply.) That causes<br>overcurrent at this pin, as the ESD<br>protection elements insertion between the<br>pin and the voltage source. | RX_SW<br>7<br>4<br>100 Ω<br>20k Ω<br>100 Ω<br>20k Ω<br>1kΩ |

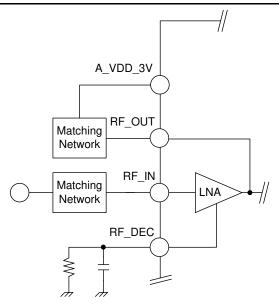

| 8       | RF_DEC   | -                 | <b>RF Decoupling Pin</b><br>Connect a decoupling capacitor.<br>At no use, open this pin.                                                                                                                                                                                                                     | A_REG A_VDD_3V<br>1kΩ<br>1kΩ<br>SpF 6kΩ<br>9<br>6kΩ        |

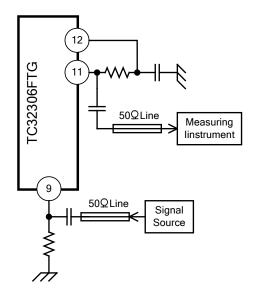

| 9       | RF_IN    | Analog<br>Input   | <b>RF Input Pin</b><br>Do not connect DC voltage except ground<br>to RF_IN pin.<br>At no use, open this pin.                                                                                                                                                                                                 | RF_DEC                                                     |

| Pin No. | Pin Name | I/O              | Description                                                                                                                                                                                                                                                              | Internal Equivalent Circuit                        |

|---------|----------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| 10      | A_VDD_5V | -                | Analog 5V Supply<br>Supply to mainly analog block.<br>- For 5V use, supply 5V (typ.).<br>- For 3V use, connect A_VDD_3V pin and<br>supply 3V (typ.).                                                                                                                     | -                                                  |

| 11      | RF_OUT   | Analog<br>Output | <b>RF Output pin</b><br>RF signal output from LNA block,<br>Open drain output. Connect A_VDD_3V<br>pin via a matching circuit.<br>At no use, open this pin.                                                                                                              | RF_OUT                                             |

| 12      | A_VDD_3V | -                | Analog 3V Supply<br>- For 3V use, supply 3V (typ.).<br>- For 5V use, voltage regulator output.<br>Connect a bypass capacitor.<br>Do not apply current or voltage on this pin<br>from outside. And do not supply to<br>external circuits except PA_OUT and<br>RF_OUT pin. | -                                                  |

| 13      | A_REG    | Analog<br>Output | Regulator Output for Analog Block<br>Supply to mainly analog block. Connect a<br>bypass capacitor.<br>Do not apply current or voltage on this pin<br>from outside. And do not supply to<br>external circuits.                                                            | A_VDD_5V A_VDD_5V<br>A_REG<br>13<br>100pF<br>150kΩ |

| 14      | A_GND    | -                | Ground (Analog)                                                                                                                                                                                                                                                          |                                                    |

| 15      | IF_REF   | -                | IF Reference<br>Connect ground via a capacitor.<br>At no use, open this pin.                                                                                                                                                                                             | IF_REF<br>15<br>100kΩ<br>100kΩ<br>100kΩ<br>105kΩ   |

| 16      | PA_GND1  | -                | Power Amplifier Ground 1<br>At no use of PA, connect ground.                                                                                                                                                                                                             | -                                                  |

| Pin No. | Pin Name | I/O                                   | Description                                                                                                                                                                                                                                                                                                                                                                                                                     | Internal Equivalent Circuit                       |

|---------|----------|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|

| 17      | PA_OUT   | Analog<br>Output                      | Power Amplifier Output Stage<br>Open drain output. Connect A_VDD_3V<br>pin via a matching circuit.<br>At no use, open this pin.                                                                                                                                                                                                                                                                                                 | PA_OUT                                            |

| 18      | PA_GND2  | -                                     | Power Amplifier Ground 2<br>At no use of PA, connect ground.                                                                                                                                                                                                                                                                                                                                                                    | -                                                 |

| 19      | TX_SW    | Digital<br>Output<br>Digital<br>Input | Artenna Switch Control for TX (In SPI<br>Mode)<br>At no use, open this pin.<br>Address Setting (In EEPROM Mode)<br>Set a start address to read memory data.<br>Notice:<br>Do not supply higher voltage than the level<br>of COM_VDD. (For example, in the case<br>of too low / no power supply.) That causes<br>overcurrent at this pin, as the ESD<br>protection elements insertion between the<br>pin and the voltage source. | A_VDD_5V<br>A_VDD_5V<br>TX_SW<br>(19)<br>20kΩ<br> |

|         |          |                                       | Reset                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                   |

| 20      | RESET    | Digital<br>Input                      | Initialize TC32306FTG.                                                                                                                                                                                                                                                                                                                                                                                                          |                                                   |

| 21      | MODE2    | Digital<br>Input                      | Mode Control<br>Select SPI Mode, SPI User Test Mode,<br>EEPROM Mode, EEPROM User Test<br>Mode.                                                                                                                                                                                                                                                                                                                                  | MODE2<br>(2)                                      |

| 22      | MODE1    | Digital<br>Input                      | Mode Control<br>Select SPI Mode, SPI User Test Mode,<br>EEPROM Mode, EEPROM User Test<br>Mode.                                                                                                                                                                                                                                                                                                                                  | MODE1<br>(22)<br>40kΩ                             |

| 23      | TEST     | Digital<br>Input                      | TEST<br>Only use for Toshiba test.<br>Connect ground.                                                                                                                                                                                                                                                                                                                                                                           | TEST<br>23<br>40kΩ                                |

| Pin No. | Pin Name | I/O              | Description                                                                                                                                                                                                     | Internal Equivalent Circuit                                      |

|---------|----------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|

| 24      | PLL_REG  | Analog<br>Output | Regulator Output for PLL<br>Supply to mainly PLL block. Connect a<br>bypass capacitor.<br>Do not supply voltage, and do not supply<br>to an external circuit.                                                   | COM_VDD<br>COM_VDD<br>Vref<br>(24)<br>Vref<br>100pF<br>150kΩ     |

| 25      | PLL_GND  | -                | Ground(Digital)                                                                                                                                                                                                 | -                                                                |

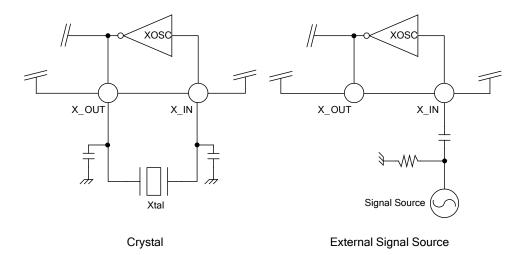

| 26      | X_IN     | Analog<br>Input  | Reference Clock Input<br>Connect crystal oscillator or external<br>signal generator.<br>Do not apply a DC bias voltage.                                                                                         |                                                                  |

| 27      | X_OUT    | Analog<br>Output | Reference Clock Output<br>Open this pin except a crystal oscillator<br>use.<br>Do not apply current or voltage on this pin<br>from outside. And do not supply the clock<br>signal to external circuits.         |                                                                  |

| 28      | D_REG    | Analog<br>Output | Regulator Output for Digital Block<br>Supply to mainly digital block. Connect a<br>bypass capacitor.<br>Do not apply current or voltage on this pin<br>from outside. And do not supply to<br>external circuits. | COM_VDD<br>COM_VDD<br>COM_VDD<br>Vref<br>100pF<br>150kΩ<br>150kΩ |

| Pin No. | Pin Name | I/O                                   | Description                                                                                                                                                                                                                                                                                                                                                                                                       | Internal Equivalent Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|---------|----------|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 29      | CS       | Digital<br>Input<br>Digital<br>Output | Chip Select Input<br>In SPI Mode / SPI User Test Mode /<br>EEPROM User Test Mode.<br>Notice:<br>Do not supply higher voltage than the level<br>of COM_VDD. (For example, in the case<br>of too low / no power supply.) That causes<br>overcurrent at this pin, as the ESD<br>protection elements insertion between the<br>pin and the voltage source.<br>Chip Select Output<br>In EEPROM Mode.                    | COM_VDD<br>CS<br>29<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD  |

| 30      | CLK      | Digital<br>Input<br>Digital           | SPI Clock Input<br>In SPI Mode / SPI User Test Mode /<br>EEPROM User Test Mode.<br>Notice:<br>Do not supply higher voltage than the level<br>of COM_VDD. (For example, in the case<br>of too low / no power supply.) That causes<br>overcurrent at this pin, as the ESD<br>protection elements insertion between the<br>pin and the voltage source.<br>SPI Clock Output                                           | COM_VDD<br>CLK<br>30<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD |

| 31      | MOSI     | Digital<br>Input<br>Digital<br>Output | In EEPROM Mode.<br>Serial Data Input<br>In SPI Mode / SPI User Test Mode /<br>EEPROM User Test Mode.<br>Notice:<br>Do not supply higher voltage than the level<br>of COM_VDD. (For example, in the case<br>of too low / no power supply.) That causes<br>overcurrent at this pin, as the ESD<br>protection elements insertion between the<br>pin and the voltage source.<br>Serial Data Output<br>In EEPROM Mode. | Control<br>MOSI<br>31<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VDD<br>COM_VD |

| 32     MISO     Serial Data Output<br>In SPI Mode / SPI User Test Mode /<br>EEPROM Mode.       32     MISO     Serial Data Input<br>In EEPROM Mode.       33     Serial Data Input<br>In EEPROM Mode.       34     DET_TMONI       35     COM_VDD       36     DET_TMONI       37     Com_vob<br>protection of an and SV.<br>Supply to mainly control block.       38     COM_VDD       39     Com_vob<br>protection of an and SV.<br>Supply to mainly control block.       30     DET_TMONI       31     DET_TMONI       32     Digital<br>Digital<br>Digital<br>Particle       34     DET_TMONI       35     DATA_JO       36     DATA_JO       37     DATA_JO       38     DATA_JO       39     DATA_JO       30     DATA_JO       30     DATA_JO       31     DATA_JO       32     DATA_JO       33     Com VDD<br>Digital<br>Input       34     DATA_JO       35     DATA_JO       36     DATA_JO       37     DATA_JO       38     DATA_JO       39     DATA_JO       39     DATA_JO       30     DATA_JO       30     DATA_JO       30     DATA_JO       30<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Pin No. | Pin Name   | I/O     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Internal Equivalent Circuit                                                                  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| 32     MISO     Serial Data Input<br>In EEPROM Mode.     Serial Data Input<br>In EEPROM Mode.       Notice:<br>Input     Notice:<br>Do not supply higher voltage than the level<br>of COM_VDD. (For example, in the case<br>overcurrent at this pin, as the ED<br>portexturent at this pin, as the ED<br>Supply to mainly control block.       33     COM_VDD     -       34     DET_TMONI1     Monitor 1<br>Digital<br>Dupta       34     DET_TMONI1     Digital<br>Dupta       34     DET_TMONI1     Digital<br>Dupta       35     DATA_IO       36     DATA_IO       37     DATA_IO       38     DATA_IO       39     DATA_IO       30     DATA_IO       31     DATA_IO       32     DATA_IO       33     DATA_IO       34     DATA_IO       35     DATA_IO       36     DATA_IO       37     DATA_IO       38     DATA_IO       39     DATA_IO       30     DATA_IO       31     DATA_IO       32     DATA_IO       33     DATA_IO       34     DATA_IO       35     DATA_IO       36     DATA_IO       37     DATA_IO <td></td> <td></td> <td></td> <td>In SPI Mode / SPI User Test Mode /</td> <td></td>                                                                                                                                                                                                                                                                                                                                                                     |         |            |         | In SPI Mode / SPI User Test Mode /                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                              |

| 33     COM_VDD     -     Use for 3V and 5V.<br>Supply to mainly control block.       34     DET_TMONI1     Digital<br>Output     Monitor 1<br>Monitoring internal signals (Digital), use<br>for system control.     COM_VDD_COM_VDD_<br>DetT_TMONI1       34     DET_TMONI1     Digital<br>Output     At no use, open this pin.       35     Data Output     Demodulated signal output at<br>RF-Receiving. Behavior of this pin is<br>different for each state of TC32306FTG<br>reset.       35     DATA_IO       36     DATA_IO       37     DATA_IO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 32      | MISO       |         | In EEPROM Mode.<br>Notice:<br>Do not supply higher voltage than the level<br>of COM_VDD. (For example, in the case<br>of too low / no power supply.) That causes<br>overcurrent at this pin, as the ESD<br>protection elements insertion between the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                              |

| 34     DET_TMONI1     Digital<br>Output     Monitoring internal signals (Digital), use<br>for system control.     Digital<br>Output     At no use, open this pin.       34     DET_TMONI1     Digital<br>Output     At no use, open this pin.     DET_TMONI1       36     Data Output<br>Demodulated signal output at<br>RF-Receiving. Behavior of this pin is<br>different for each state of TC32306FTG<br>reset.<br>See Table 5-2.     Digital<br>Output     Notice:<br>Output resistance of this pin is 10k0 when<br>the output drive setting is "Low". Select<br>proper resistance value of pull-up or pull<br>down resistor to get enough output level of<br>the pin, when the output drive setting is<br>"Low". Or select that the output drive<br>setting is "High", depending on the<br>resistance value of the resister. About<br>output drive setting is<br>"Low". Or select that the output drive<br>setting is "High", depending on the<br>resistance value of TC32306FTG<br>reset.<br>See Table 5-2.       35     DATA_IO       36     Data Input<br>Signal input for modulation at<br>RF-Transmitting. Behavior of this pin is<br>different for each state of TC32306FTG<br>reset.<br>See Table 5-2.       36     Data Input<br>Signal input for modulation at<br>RF-Transmitting. Dehavior of this pin is<br>different for each state of TC32306FTG<br>reset.<br>See Table 5-2.       Digital<br>Input     Notice:<br>Do not supply higher voltage than the level<br>of COM v/DD (For example, in the causes<br>overcurrent at this pin, as the ESD<br>protection elements insertion between the<br>pin and the voltage source. | 33      | COM_VDD    | -       | Use for 3V and 5V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | -                                                                                            |

| 35     DATA_IO     Demodulated signal output at<br>RF-Receiving. Behavior of this pin is<br>different for each state of TC32306FTG<br>reset.<br>See Table 5-2.       35     DATA_IO       36     DATA_IO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 34      | DET_TMONI1 |         | Monitoring internal signals (Digital), use for system control.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | DET_TMONI1                                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 35      | DATA_IO    | Digital | Demodulated signal output at<br>RF-Receiving. Behavior of this pin is<br>different for each state of TC32306FTG<br>reset.<br>See Table 5-2.<br>Notice:<br>Output resistance of this pin is 10kΩ when<br>the output drive setting is "Low". Select<br>proper resistance value of pull-up or pull<br>down resistor to get enough output level of<br>the pin, when the output drive setting is<br>"Low". Or select that the output drive<br>setting is "High", depending on the<br>resistance value of the resister. About<br>output drive settings, see section 6.10.5.<br><b>Data Input</b><br>Signal input for modulation at<br>RF-Transmitting. Behavior of this pin is<br>different for each state of TC32306FTG<br>reset.<br>See Table 5-2.<br>Notice:<br>Do not supply higher voltage than the level<br>of COM_VDD. (For example, in the case<br>of too low / no power supply.) That causes<br>overcurrent at this pin, as the ESD<br>protection elements insertion between the | COM_VDD<br>DATA_IO<br>35<br>COM_VDD<br>Low Drive<br>10kQ<br>Control<br>COM_VDD<br>High Drive |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 36      | IO_GND     | -       | pin and the voltage source. Ground(I/O Block)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                              |

## 5.2 Pin Behaviors at Reset and Register Initialized

Several pin behaviors of TC32306FTG depend on setting of Reset, register's initial value, or SPI Mode / EEPROM Mode (including User Test). See Table 5-2.

| Pin          | SPI Mode<br>(TC32306FTG is slave.)<br>(Including SPI User Test Mode) |                                     | EEPROM Mode<br>(TC32306FTG is master.) |                | EEPROM User Test Mode<br>(TC32306FTG is slave.) |                                     |

|--------------|----------------------------------------------------------------------|-------------------------------------|----------------------------------------|----------------|-------------------------------------------------|-------------------------------------|

|              | RESET = "L"                                                          | Register's Initial (Battery Saving) | RESET = "L"                            | Battery Saving | RESET = "L"                                     | Register's Initial (Battery Saving) |

| MODE2        | IN                                                                   | IN                                  | IN                                     | IN             | IN                                              | IN                                  |

| MODE1        | IN                                                                   | IN                                  | IN                                     | IN             | IN                                              | IN                                  |

| CS           | IN                                                                   | IN                                  | High Output                            | High Output    | IN                                              | IN                                  |

| CLK          | IN                                                                   | IN                                  | Low Output                             | Low Output     | IN                                              | IN                                  |

| MOSI         | IN                                                                   | IN                                  | Low Output                             | Low Output     | IN                                              | IN                                  |

| MISO         | Z                                                                    | Z                                   | Z                                      | Z              | Z                                               | Z                                   |

| ENB          | IN                                                                   | IN                                  | IN                                     | IN             | IN                                              | IN                                  |

| TX_SW        | Pull Down                                                            | Pull Down                           | IN                                     | IN             | IN                                              | IN                                  |

| RX_SW        | Pull Down                                                            | Pull Down                           | IN                                     | IN             | IN                                              | IN                                  |

| DATA_IO      | Z                                                                    | Low Output                          | Z                                      | Low Output     | Z                                               | Low Output                          |

| DET_TMONI1,2 | Low Output                                                           | Low Output                          | Low Output                             | Low Output     | Low Output                                      | Low Output                          |

| DET_TMONI3,4 | Z                                                                    | Z                                   | Z                                      | Z              | Z                                               | Z                                   |

Table 5-2 Pin Behaviors at Reset and Register Initialized

Z: High Impedance

Notice: In SPI Mode, TC32306FTG accepts the input of SPI settings at RESET = "L", but will not act.

In Battery Saving Status, DATA\_IO pin behavior changes to the value of register:h'0A[D5]RX\_TX. Initial value of register:h'0A[D5]RX\_TX is "0".

#### Table 5-3 DATA\_IO Pin Behavior in Battery Saving

| Pin     | h'0A[D5]RX_TX = "0"<br>(RX: Initial) | h'0A[D5]RX_TX = "1"<br>(TX) |

|---------|--------------------------------------|-----------------------------|

| DATA_IO | Low Output                           | Z                           |

Z: High Impedance

In Battery Saving Status, MISO pin changes its behavior at SPI Read when TC32306FTG is slave.

#### Table 5-4 MISO Pin Behavior in Battery Saving (TC32306FTG is slave.)

| Pin  | At SPI Read | Except SPI Read |

|------|-------------|-----------------|

| MISO | OUT         | Z               |

Z: High Impedance

## 6. Functional Description

## 6.1 Voltage Supply Settings

The voltage supply of TC32306FTG is selectable either 3V or 5V. The supply voltage is selected by setting of 3V/5V pin, and it decides pin connections. At 5V use, connect 3V/5V pin to a voltage supply, then the internal voltage regulator (A\_REG30; for analog 3V) makes 3V (typ.) for internal circuit and outputs same to A\_VDD\_3V pin for the matching of LNA and PA.

| Pin Name                                 | 3V Use           | 5V Use                                                               |

|------------------------------------------|------------------|----------------------------------------------------------------------|

| 3V/5V<br>(Behavior of A_REG30 Regulator) | GND<br>(Disable) | 5V Supply Input<br>(Enable)                                          |

| A_VDD_3V                                 | 3V Supply Input  | Output of A_REG30 Regulator<br>(Do not supply to external circuits.) |

| A_VDD_5V                                 | 3V Supply Input  | 5V Supply Input                                                      |

| COM_VDD                                  | 3V Supply Input  | 5V Supply Input                                                      |

| Table 6-1 Voltage S | Supply Pins | Connection |

|---------------------|-------------|------------|

|---------------------|-------------|------------|

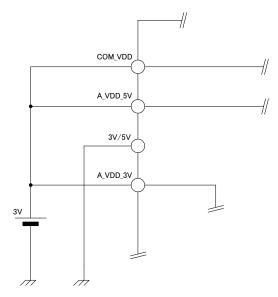

#### 6.1.1 3V Use

At 3V use, connect 3V/5V pin to ground. Connect COM\_VDD pin, A\_VDD\_3V pin and A\_VDD\_5V pin to a stable 3V supply.

#### Notice:

- Must not operate A\_REG30 regulator for 5V use.

- Must not connect COM\_VDD pin to voltage supply out of range of  $V_{DD(3V)}$  shown as Table 8-1.

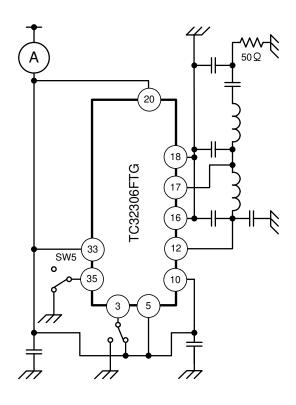

(This figure is conceptual. Select bypass capacitors in application circuits.)

#### Fig 6-1 Example of Voltage Supply Connection at 3V Use

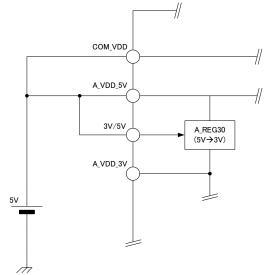

#### 6.1.2 5V Use

At 5V use, connect 3V/5V pin to the 5V supply. Connect A\_VDD\_5V pin and COM\_VDD pin to a stable 5V supply.

Notice:

- Must not connect A\_VDD\_3V pin to outside voltage supply.

- Must not connect COM\_VDD pin to voltage supply out of range of V<sub>DD(5V)</sub> shown as Table 8-1.

- Must use a voltage supply from A\_VDD\_3V pin (output of A\_REG30 regulator), for the matching circuit of LNA and PA.

(This figure is conceptual. Select bypass capacitors in application circuits.)

Fig 6-2 Example of Voltage Supply Connection at 5V Use

## 6.1.3 Supply / Ground Connections

In TC32306FTG supply / ground connections are separated for each functional block. At 5V use, some of analog functional blocks are connected internal 3V regulator (A\_REG30 regulator). At 3V use, some of analog functional blocks are connected directly 3V supply, by connecting A\_VDD\_3V / A\_VDD\_5V pin.

(This figure shows main supply / ground lines of functional blocks.)

Fig 6-3 Conceptual Supply / Ground Connection to Functional Blocks

## 6.2 Control Mode Settings

TC32306FTG has two control modes, SPI (Serial Peripheral Interface) Mode and EEPROM Mode. The control mode settings are selected by MODE2 pin. User Test Mode in each Control Mode is selected by MODE1 pin.

## Table 6-2 Mode of Control

| MODE2 Pin | MODE1 Pin | Control Mode Setting  |

|-----------|-----------|-----------------------|

| L         | L         | SPI Mode              |

| L         | Н         | SPI User Test Mode    |

| Н         | L         | EEPROM Mode           |

| Н         | Н         | EEPROM User Test Mode |

SPI Mode and EEPROM Mode have a difference about an external connection, pin functions and control signal flows. Do not change the Mode settings in the market products.

| Control Setting       | CS<br>Pin                                          | CLK<br>Pin | MOSI<br>Pin                                         | MISO Pin                                       | ENB Pin  | TX_SW<br>Pin | RX_SW<br>Pin |

|-----------------------|----------------------------------------------------|------------|-----------------------------------------------------|------------------------------------------------|----------|--------------|--------------|

| SPI Mode              | "Input"                                            |            | "Output"                                            | "Input"                                        | "Output" |              |              |

| SPI User Test Mode    | This IC is slave, controlled by MCU.               |            | This IC is slave, controlled by MCU.                | For this IC status For antenna switch control. |          |              |              |

| EEPROM Mode           | ,                                                  |            | "Input"<br>This IC is master,<br>reads EEPROM data. | "Input"                                        |          |              |              |

| EEPROM User Test Mode | "Input"<br>This IC is slave,<br>controlled by MCU. |            | "Output"<br>This IC is slave,<br>controlled by MCU. | For EEPROM configuration settings              |          | ettings      |              |

## Table 6-3 Role of Pin and Control Setting

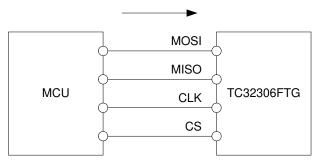

### 6.2.1 SPI Mode Setting and Connection

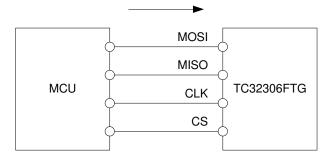

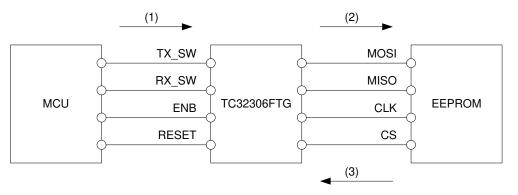

MCU and TC32306FTG are connected by SPI lines and MCU controls this IC.

Fig 6-4 Conceptual Connection MCU and TC32306FTG

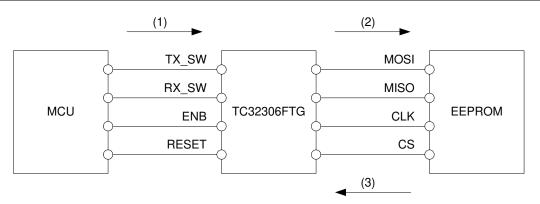

## 6.2.2 EEPROM Mode Setting and Connection

EEPROM and MCU, connect via TC32306FTG. This IC is controlled by the register data of EEPROM. Select up to 8 configuration that are made as registers from "h'0A" to "h'1C", depending on the size of EEPROM. In this mode, use of pins and external connections are different from those of SPI Mode. For example, TX\_SW / RX\_SW / ENB pin are used to select configuration of EEPROM.

## Fig 6-5 Conceptual Connection MCU, EEPROM and TC32306FTG

- In advance, write registers' values to each configuration data area of EEPROM.

- MCU commands this IC for selecting configuration data area of EEPROM. (1)

- This IC read a configuration data from EEPROM by SPI lines at the rising edge of RESET pin signal. (2)

- This IC is operated depending on EEPROM data. (3)

## 6.3 Universal Functions and Settings

### 6.3.1 Reset Status

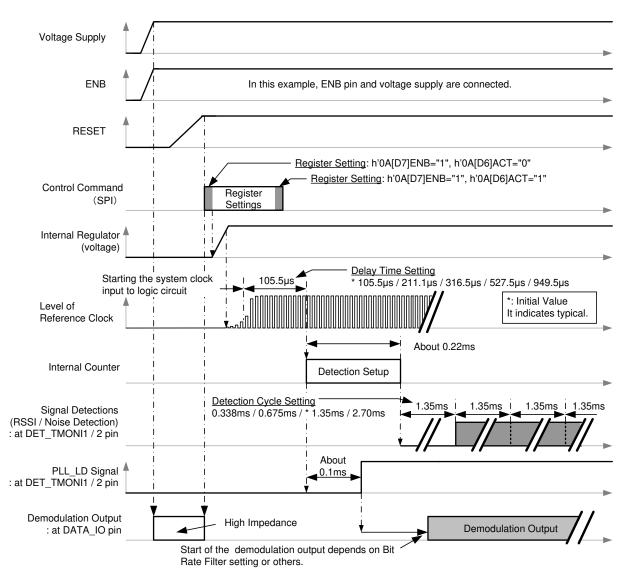

The internal condition (such as the register value) of TC32306FTG is initialized in this Status. For this IC Reset, input "L" signal to RESET pin surely during stable voltage supply. Also releasing Reset of this IC should be operated during stable voltage supply.

| RESET Pin | IC Status                                                                                                                                                                                                 |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| L         | Initialize registers and I/O behaviors. Because I/O will be<br>initialized, TC32306FTG does not accept all the settings except<br>some settings. *<br>About I/O behaviors at Reset status, see Table 5-2. |

| Н         | Battery Saving / Standby / Run by this IC settings.                                                                                                                                                       |

#### Table 6-4 RESET Pin Control

\* In EEPROM Mode, ENB pin / TX\_SW pin / RX\_SW pin are available.

Notice:

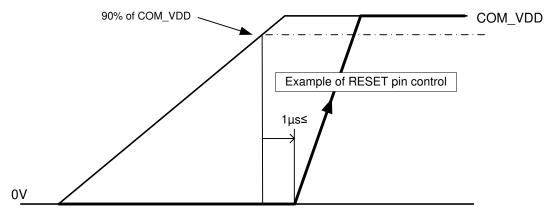

- Must be reset after voltage supply.

- The value of registers is initialized immediately after reset is released.

- See Table 5-2 of I/O behavior at the register initialized.

- In SPI Mode, TC32306FTG stays Battery Saving from Reset to register setting input, which moves to Run after reset will be released.

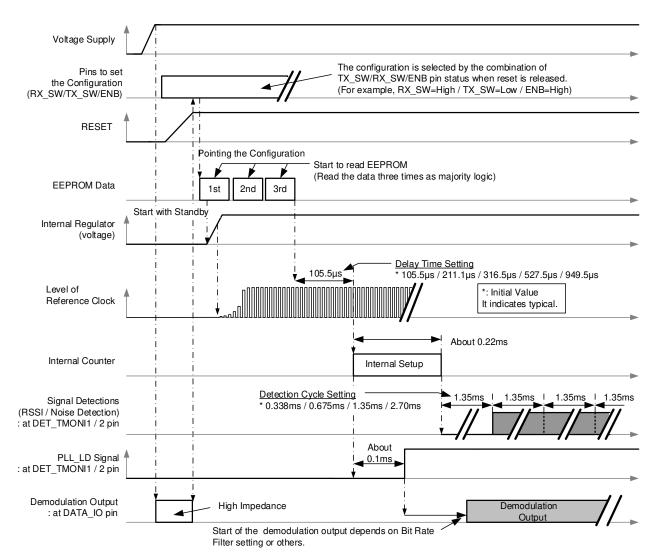

- In EEPROM Mode, the internal oscillator circuit for reading EEPROM will start after reset is released.

- Controlling to RESET pin in starting operation of this IC, keep reset status till supply voltage is over 90% of system voltage stably. Wait at least 1 microsecond after reaching that voltage level. Then reset can be released. In the transient starting operation, reset release may cause to be unexpected operation of this IC.

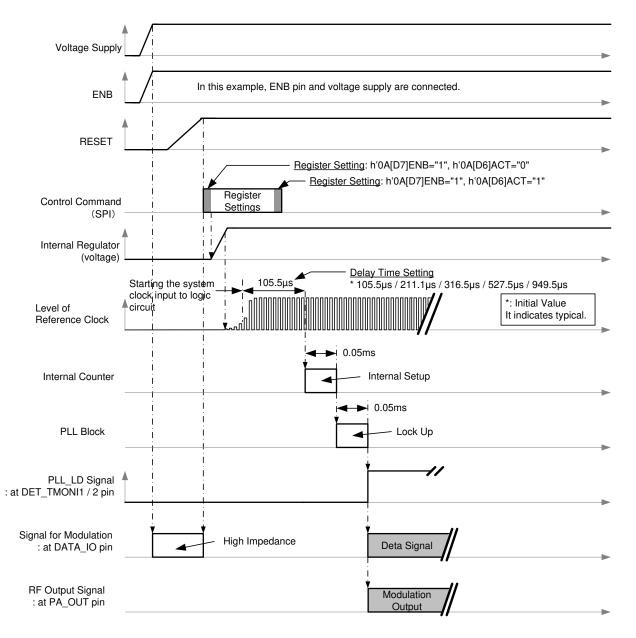

About RESET pin control in starting operation, see Fig 6-6.

#### - Software Reset

Software Reset will start after write "b'01010101" to register: h'09[D7:D0]RESET7..0. TC32306FTG will be reset as soon as the writing of Software Reset. Then the reset is released by next rising edge of CLK Signal or CS Signal, whichever is earlier. This IC will stay Battery Saving Status till the next Run / Standby command writing.

#### Table 6-5 Software Reset Command

| Software Reset Command          |

|---------------------------------|

| h'09[D7:D0]RESET70 = b'01010101 |

Notice:

- Not available in EEPROM Mode (Except EEPROM User Test Mode)

- At Software Reset, only the register will be reset.

- TC32306FTG will output "b'00000000" to read the register: h'09[D7:D0]RESET7..0.

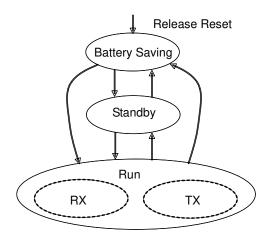

#### 6.3.2 Status Control

After reset is released, TC32306FTG has three status, Battery Saving / Standby / Run, then those status are controlled by two registers "h'OA[D7] / h'OA[D6]" and ENB pin. In EEPROM Mode, ENB pin is used for configuration setting.

| MODE2<br>Pin | ENB<br>Pin | h'0A[D7]ENB | h'0A[D6]ACT | Status  | Description                                                                                                                                                      |

|--------------|------------|-------------|-------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| L            | L          | х           | х           | Battery | The lowest current consumption status. TC32306FTG only can accept control data (register setting) and control settings                                           |

| L            | Н          | 0           | х           | Saving  | and they can be changed. The transition from this status to<br>Run will spend longer time than Standby                                                           |

| L            | н          | 1           | 0           | Standby | This IC can move from this status to Run quickly. This IC can accept control data and operate XOSC and regulators, and consume more current than Battery Saving. |

| L            | Н          | 1           | 1           | Run     | This IC can operate TX and RX. This IC current consumption and status transition time depend on the behaviors.                                                   |

## Table 6-6 IC Status in SPI Mode

X: Don't care

In SPI Mode, MODE 1 pin is unrelated to the status control of TC32306FTG. Moving to Battery Saving by AutoOff function, registers "h'0A[D7] ENB, h'0A[D6] ACT" keep the value "1".

| MODE2 Pin | h'0A[D7]ENB | h'0A[D6]ACT | Status            | Description                                                                                                                                                                            |

|-----------|-------------|-------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| н         | 0           | х           | Battery<br>Saving | The lowest current consumption status. TC32306FTG only can accept control settings and they can be changed. The transition from this status to Run will spend longer time than Standby |

| н         | 1           | 0           | Standby           | This IC can move from this status to Run quickly. This IC can accept control data and operate XOSC and regulators, and consume more current than Battery Saving.                       |

| Н         | 1           | 1           | Run               | This IC can operate TX and RX. This IC current consumption and status transition time depend on the behaviors.                                                                         |

### Table 6-7 IC Status in EEPROM Mode

X: Don't care

In EEPROM Mode, MODE1 pin "H" leads EEPROM User Test Mode. In EEPROM User Test Mode, this IC will change to be slave. In EEPROM Mode and EEPROM User Test Mode, ENB pin sets EEPROM address of configuration data and is unrelated to the status control of this IC. Moving to Battery Saving by AutoOff function, registers" h'0A[D7] ENB, h'0A[D6] ACT" keep the value "1".

### 6.3.3 Output Drive Settings

Select output drive setting at DATA\_IO pin / MISO pin / DET\_TMONI1 pin / DET\_TMONI2 pin by setting registers"h'0D[D3]DATA\_IO\_D, h'0D[D2]MISO\_D, h'0D[D1]TMONI\_D". The settings become valid when reset is released (RESET = "H").

| h'0D[D3]DATA_IO_D | DATA_IO pin drive setting                |

|-------------------|------------------------------------------|

| h'0D[D2]MISO_D    | MISO pin drive setting                   |

| h'0D[D1]TMONI_D   | DET_TMONI1, DET_TMONI2 pin drive setting |

| 0                 | Low drive setting                        |

| 1                 | High drive setting                       |

#### Table 6-8 Output Drive Settings

#### 6.3.4 Antenna Switch Control

It is a function to control external antenna switch. Set registers"h'0A[D3]TX\_SW, h'0A[D2]RX\_SW", and TC32306FTG outputs control signals from TX\_SW / RX\_SW pin. The controls become valid at Run and Standby Status. These pins cannot be available in EEPROM Mode and EEPROM User Test Mode as using for input pins.

| MODE2 Pin | Ohahaa         | h'0A[D3]TX_SW | TX_SW Pin     |

|-----------|----------------|---------------|---------------|

| MODE2 PIN | Status         | h'0A[D2]RX_SW | RX_SW Pin     |

| L         | Buttery Saving | Х             | L             |

| L         | Run / Standby  | 0             | L             |

| L         | Run / Standby  | 1             | Н             |

| Н         | х              | Х             | Input pin     |

|           |                |               | X: Don't care |

| Table 6-9 Antenna Switch Control Settings |  |

|-------------------------------------------|--|

|-------------------------------------------|--|

Notice: These pins condition "L" is pulled down through a resistor. External circuit cannot be driven in these pins condition.

## 6.3.5 Monitoring Control

Set registers"h'14[D6:D4], h'14[D2:D0]" and TC32306FTG outputs monitoring signals from DET\_TMONI1 pin / DET\_TMONI2 pin. The controls become valid at Run or Standby Status.

| Otatura        | h'14[D6]<br>MONI1_SEL2 | h'14[D5]<br>MONI1_SEL1 | h'14[D4]<br>MONI1_SEL0 | DET_TMONI1 Pin<br>Output Signal |

|----------------|------------------------|------------------------|------------------------|---------------------------------|

| Status         | h'14[D2]<br>MONI2_SEL2 | h'14[D1]<br>MONI2_SEL1 | h'14[D0]<br>MONI2_SEL0 | DET_TMON2 Pin<br>Output Signal  |

| Battery Saving | х                      | х                      | Х                      | Low level output                |

| Run / Standby  | 0                      | 0                      | 0                      | Low level output                |

| Run / Standby  | 0                      | 0                      | 1                      | DET_out                         |

| Run / Standby  | 0                      | 1                      | 0                      | Preamble_DET_out                |

| Run / Standby  | 0                      | 1                      | 1                      | RSSI_DET_out                    |

| Run / Standby  | 1                      | 0                      | 0                      | NDET_out                        |

| Run / Standby  | 1                      | 0                      | 1                      | Status_MONI                     |

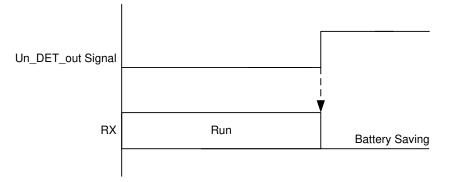

| Run / Standby  | 1                      | 1                      | 0                      | Un_DET_out                      |

| Run / Standby  | 1                      | 1                      | 1                      | PLL_LD                          |

#### Table 6-10 Monitoring Signals

X: Don't care

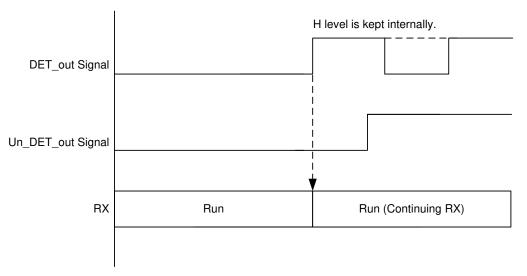

(1) DET\_out Signal

$\rm TC32306FTG$  outputs the result of overall "Detection" judgment depending on RSSI detection, Noise detection and/or Preamble detection.

L: NOT determine "Signal Detection"

H: Determine "Signal Detection"

Set register:h'10[D2]DET\_out\_cnt\_en="1", TC32306FTG holds DET\_out output level "H" after first "Signal Detection".

| h'10[D2] DET_out_cnt_en | DET_out Signal                                       |

|-------------------------|------------------------------------------------------|

| 0                       | Sequential updating                                  |