User's Guide SLAU203–February 2007

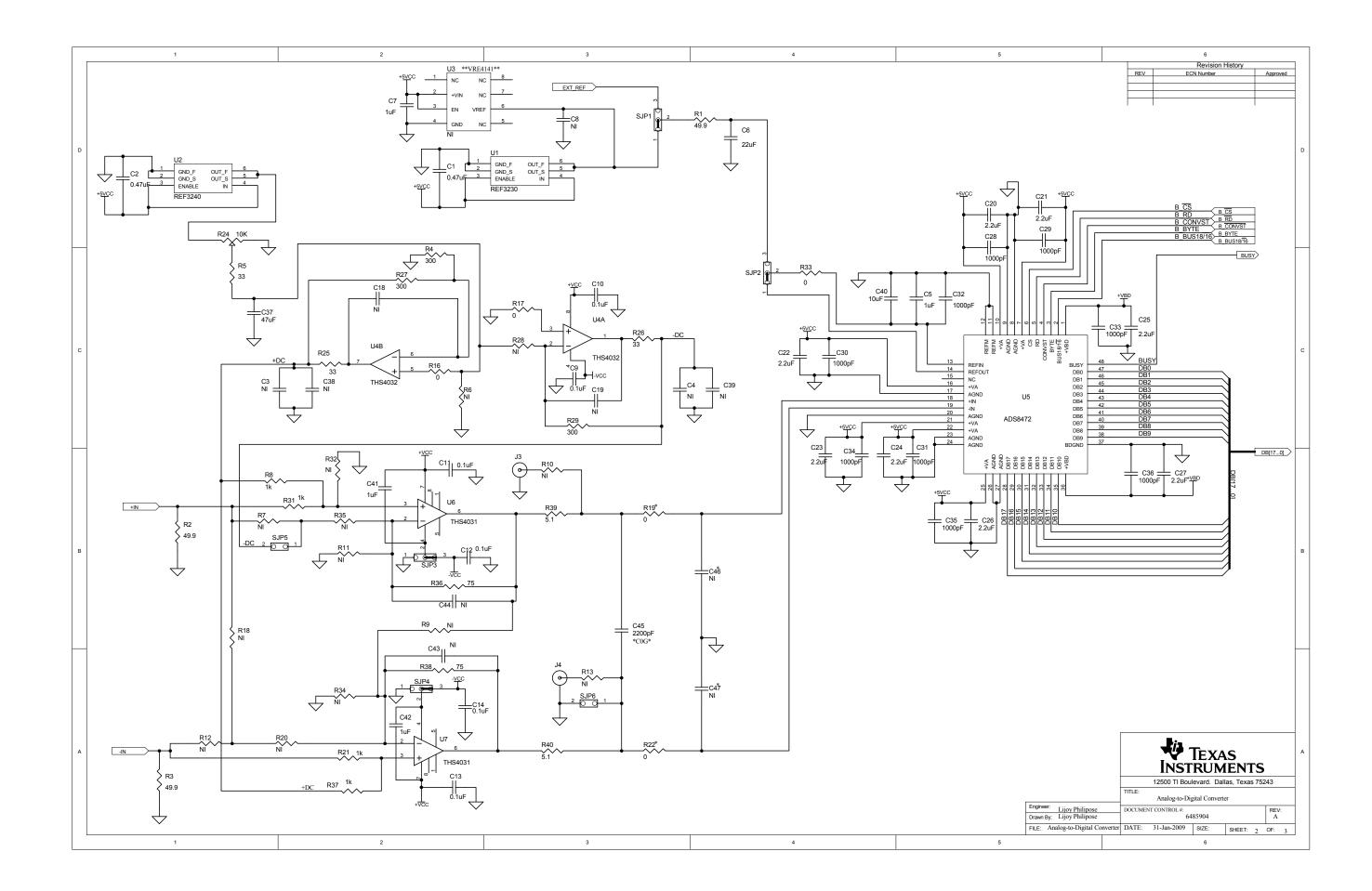

This user guide describes the characteristics, operation, and use of the ADS8472 16-bit, 1MHz parallel interface analog-to-digital converter evaluation board. A complete circuit description as well as schematic diagram and bill of materials is included.

|   | Contents             |   |

|---|----------------------|---|

| 1 | EVM Overview         | 2 |

| 2 | Introduction         | 2 |

| 3 | Analog Interface     | 2 |

| 4 | Digital Interface    |   |

| 5 | Power Supplies       |   |

| 6 | Using the ADS8472EVM |   |

| 7 | ADS8472EVM BoM       |   |

| 8 | ADS8472EVM Layout    |   |

| 9 | ADS8472EVM Schematic |   |

# List of Figures

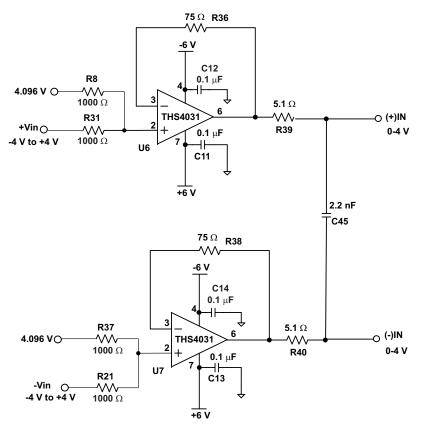

| 1 | Input Buffer, Bipolar Fully Differential Input | . 4 |

|---|------------------------------------------------|-----|

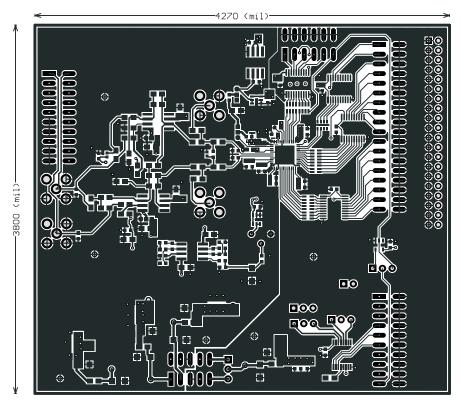

|   | Top – Layer 1                                  |     |

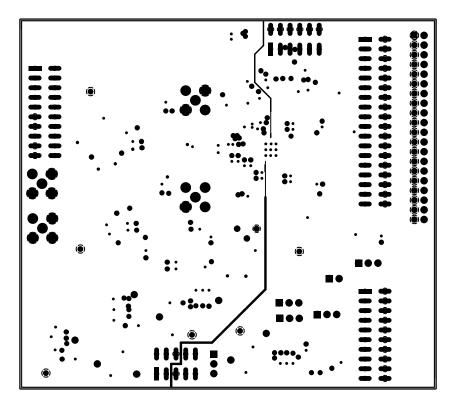

| 3 | Ground Plane – Layer 2                         | 13  |

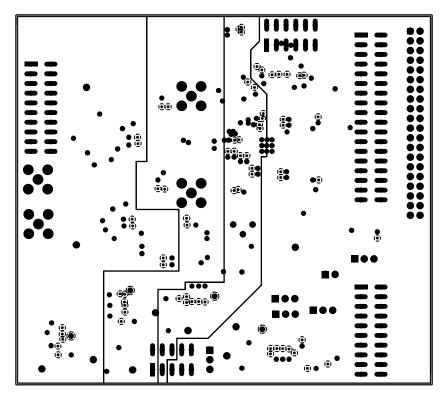

|   | Power Plane – Layer 3                          |     |

| 5 | Bottom – Layer 4                               | 14  |

| 6 | Top Overlay                                    | 14  |

| 7 | Bottom OverLay                                 | 15  |

#### List of Tables

| 1  | Analog Input Connector                      | 3  |

|----|---------------------------------------------|----|

| 2  | Analog Circuitry Jumper Configurations      | 4  |

| 3  | Pinout for Parallel Control Connector P3    | 5  |

| 4  | Jumper Settings                             | 5  |

| 5  | Data Bus Connector P2                       | 6  |

| 6  | TSW1100 Connector                           | 6  |

| 7  | Pin out for Converter Control Connector, J6 | 7  |

| 8  | Power Supply Test Points                    | 7  |

| 9  | Power Connector, J5, Pin Out                |    |

| 10 | Bill of Materials                           | 10 |

#### EVM Overview

#### 1 EVM Overview

#### 1.1 Features

- Full-featured Evaluation Board for the high-speed ADS8472 16-bit, 1MSPS single channel, parallel interface SAR type Analog to Digital Converters.

- On board signal conditioning

- On board Reference

- Input and Output Digital Buffers

- On board decoding for stacking multiple EVMs.

# 1.2 Related Documentation from Texas Instruments

To obtain a copy of any of the following TI documents, call the Texas Instruments Literature Response Center at (800) 477-8924 or the Product Information Center (PIC) at (972) 644-5580. When ordering, identify this booklet by its title and literature number. Updated documents can also be obtained through our website at www.ti.com.

| Data Sheets: | Literature Number: |

|--------------|--------------------|

| ADS8472      | <u>SLAS514</u>     |

| REF3240      | <u>SBVS058</u>     |

| REF3225      | <u>SBVS058</u>     |

| SN74AHC138   | <u>SCLS258</u>     |

| SN74AHC245   | <u>SCLS230</u>     |

| SN74AHC1G04  | <u>SCLS318</u>     |

| THS4031      | <u>SLOS224</u>     |

| THS4032      | SLOS224            |

# 2 Introduction

The ADS8472 is 16-bit, 1-MSPS analog to digital converter (ADC) with an internal 4.096V reference and a pseudo-bipolar, fully differential input. The device is a capacitor based successive approximation register (SAR) converter with an inherent sample and hold. The ADS8472 has a 16-bit and 8-bit parallel interface bus options, allowing a variety of processors to interface easily with it.

The ADS8472EVM is an evaluation and demonstration platform for the ADS8472 ADC. The board is a flexible design that allows the user to choose among many different analog signal conditioning, reference and interface modes. The standardized I/O headers not only allow the user to quickly interface to FPGAs, but also to the full line of microprocessors and digital signal processors from Texas Instruments.

# 3 Analog Interface

The analog-to-digital converter accepts a pseudo-bipolar differential input. A pseudo-bipolar differential signal is a fully differential signal that has a common-mode voltage such that the voltage on each input is always equal to or above zero volts. The common mode voltage should typically be half the reference voltage. The peak-to-peak amplitude on each input leg can be as large as the reference voltage.

The positive leg of the input signal can be applied at connector P1 pin 2 (shown in Table 1) or via center pin of SMA connector J1. Likewise the negative input signal can be applied at P1 pin1 or via center pin of SMA connector J2.

| Description Signal Name |          | Connector.Pin# |       | Signal Name | Description                 |  |  |

|-------------------------|----------|----------------|-------|-------------|-----------------------------|--|--|

| Inverting Input Channel | _        | P1.1           | P1.2  | +           | Non-inverting Input Channel |  |  |

| Reserved                | N/A      | P1.3           | P1.4  | N/A         | Reserved                    |  |  |

| Reserved                | N/A      | P1.5           | P1.6  | N/A         | Reserved                    |  |  |

| Reserved                | N/A      | P1.7           | P1.8  | N/A         | Reserved                    |  |  |

| Reserved                | N/A      | P1.9           | P1.10 | N/A         | Reserved                    |  |  |

| Pin tied to Ground      | AGND     | P1.11          | P1.12 | N/A         | Reserved                    |  |  |

| Pin tied to Ground      | AGND     | P1.13          | P1.14 | N/A         | Reserved                    |  |  |

| N/A                     | Reserved | P1.15          | P1.16 | N/A         | Reserved                    |  |  |

| Pin tied to Ground      | AGND     | P1.17          | P1.18 | N/A         | Reserved                    |  |  |

| Pin tied to Ground      | AGND     | P1.19          | P1.20 | REF+        | External Reference Input    |  |  |

Table 1. Analog Input Connector

# 3.1 Input Signal Conditioning

The analog input circuitry, consisting of the THS4031 and THS4032 operational amplifiers, allow the user to install passive components to configure it for positive or negative gains, as well as input range scaling, filtering and leveling translation (e.g., adding a DC offset). The operational amplifiers are housed in an industry standard SOIC footprint. This enables the user to replace the THS4031 with a plethora of dual and single supply amplifiers housed in an SOIC package.

When choosing the driver amplifier the user should consider the following requirements. The driving amplifier must be able to settle the input to 16-bit level within the sample time of the converter. It should have Total Harmonic Distortion(THD) characteristics comparable to or better than the ADS8472. Lastly, the noise generated by the amplifier needs to be as low as possible, so as not to degrade the SNR performance of the ADS8472.

The noise coming through the driver amplifiers are filtered by a single-pole filter using  $R = 10.2\Omega$  and C = 2.2nF with a corner frequency of 7MHz. The 5.1- $\Omega$ series resistor works with the capacitor to filter the input signal, but also isolates the amplifier from the capacitive load. The 2200-pF capacitor to ground at the input of the ADC works with the series resistor to filter the input signal, behaves like a charge reservoir, and provides a path to ground for high-frequency noise and the low small input current transient which occurs when the device switches from hold to sample mode. This external filter capacitor works with the amplifier to charge the internal sampling capacitor during sampling mode.

The supplies to the input amplifier are selectable with solder jumper pad SJP3, and SJP4. Shorting across pads 1 and 2 will ground the negative rail. Shorting across pads 2 and 3 will tie the negative supply of the amplifiers to the voltage applied at node –VCC.

When deciding on supply rails, a good rule of thumb is to add at least 2V of head room on either side to achieve optimal performance. For example, if the signal applied to the amplifier is 0–4V, then the amplifier rails should be at least –2V and +6V. At the 16-bit performance node, the amplifier introduced distortion can become significant. Be aware when reading amplifiers data sheets that they may not be specified with large amplitudes. Therefore, it may not be possible to surmise from a cursory glance how well the amplifier will behave in system.

Single-ended signal sources are readily available, but rarely allow the user to evaluate the full performance of 16-bit converters. Although the ADS8472EVM can be configured for this input configuration, the factory set configuration of the input circuitry is for a bipolar fully differential input signal. The necessary DC component to offset the signal at U7 is generated by U4. U4 is the low noise THS4032 amplifier. It can be configured to further filter the reference voltage IC, U2, and provide positive or negative gains. The ADS8472EVM leaves the factory with potentiometer, R24, set to 2.048V and set as shown in Figure 1. Table 1 indicates how the solder pad jumpers should be set to select from the various supply and input options for the analog driver circuitry. The copy of the schematic for the ADS8472EVM is attached at the end of this document.

Figure 1. Input Buffer, Bipolar Fully Differential Input

| Reference<br>Designator | 1-2                       | 2-3                       | Description                                                       |  |

|-------------------------|---------------------------|---------------------------|-------------------------------------------------------------------|--|

| SJP1                    | Installed <sup>+(1)</sup> | Not Installed             | Select onboard reference (REF3230).                               |  |

|                         | Not Installed             | Installed                 | Select user-supplied reference at P1 pin 20.                      |  |

| SJP2                    | Installed <sup>+(1)</sup> | Not Installed             | Set REFIN pin of ADS8472 to on-chip (internal) reference voltage. |  |

|                         | Not Installed             | Installed                 | Set REFIN pin of ADS8472 to reference selected by SJP1.           |  |

| SJP3                    | Installed                 | Not Installed             | Set U6 operational amplifier minus rail supply to ground.         |  |

|                         | Not Installed             | Installed <sup>†(1)</sup> | Set U6 operational amplifier minus rail supply to -VCC.           |  |

| SJP4                    | Installed                 | Not Installed             | Set U7 operational amplifier minus rail supply to ground.         |  |

|                         | Not Installed             | Installed <sup>†(1)</sup> | Set U7 operational amplifier minus rail supply to -VCC.           |  |

| SJP5                    | Not Installed             | N/A                       | Short voltage node –DC to U6 pin 2 via R35.                       |  |

| SJP6                    | Not Installed             | N/A                       | Short –IN pin of U5 to ground at C45.                             |  |

| Table 2. Analog Onculting Cumper Configurations | Table 2. Analog | Circuitry | Jumper | Configurations |

|-------------------------------------------------|-----------------|-----------|--------|----------------|

|-------------------------------------------------|-----------------|-----------|--------|----------------|

<sup>(1)</sup> † Indicates factory installed option.

# 3.2 Reference

The ADS8472 can operate with an external reference voltage in the range of 3.0V up to 4.2V. It generates an on-chip 4.096V reference voltage. The ADS8472EVM allows the user to select the external reference voltage from three sources. The first option is to use the internally generated 4.096V from the ADC. The other two options are to select from the on board reference (U1) or a user supplied voltage applied at pin 20 of P1. Refer to Table 1 for solder jumper options for selecting from the various reference sources.

The reference voltage provides the scale factor for the conversion result. The input voltage is measured against the reference voltage. It is imperative the reference voltage be clean, low noise and well decoupled.

The default configuration is to use the internal on-chip reference.

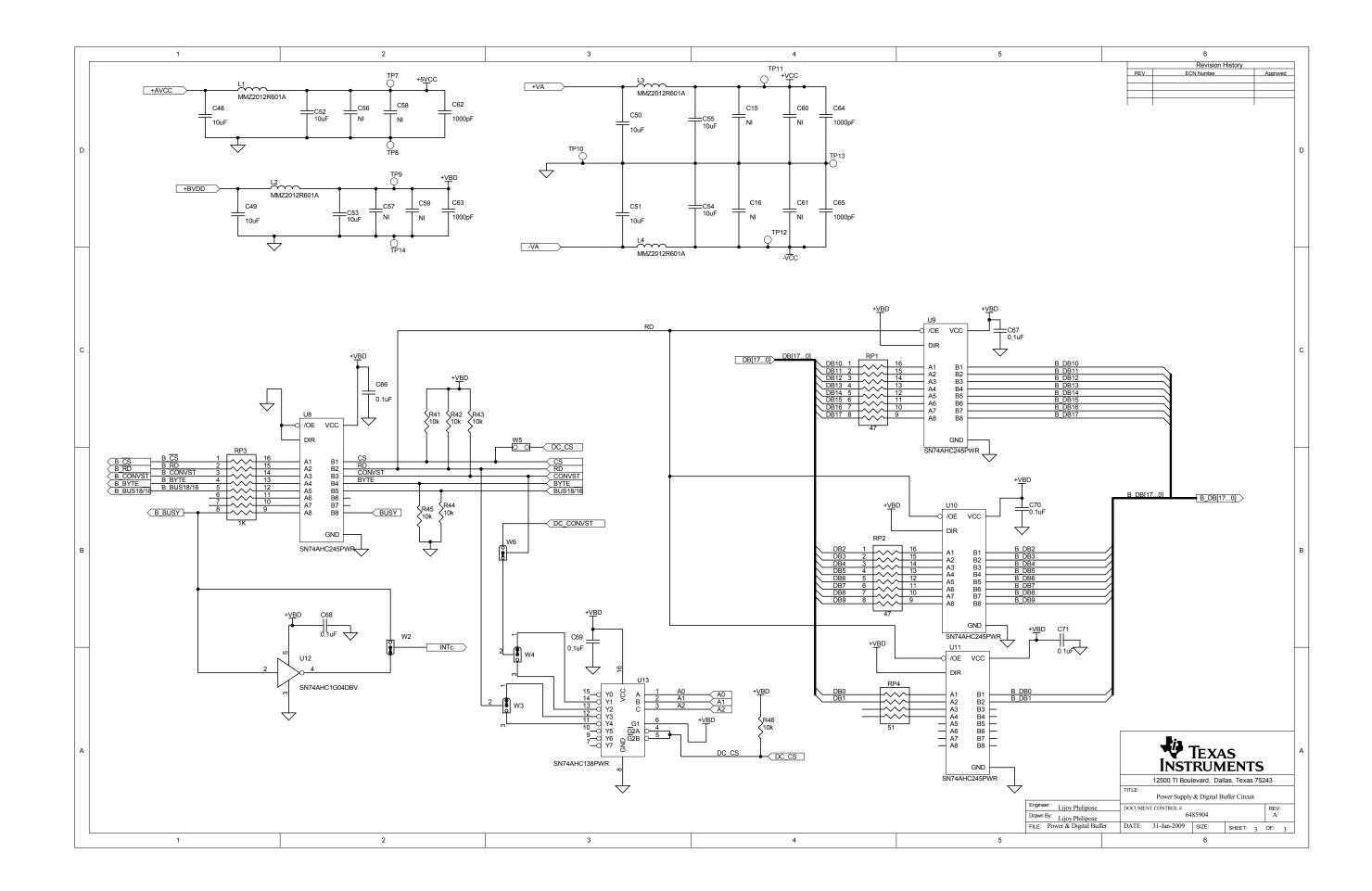

# 4 Digital Interface

The ADS8472EVM is designed for easy interfacing to multiple platforms. The digital interface input and output signals of the converter are on connectors P2, P3, J6 and J7. These are 0.1" on-centers, plug and socket connectors, allowing the user to plug the ADS8472EVM onto the various motherboard interface cards from Texas Instruments, or ribbon cable onto the user development board. The following tables list the connector pin outs.

| Description    | Signal Name | Connec | tor.Pin# | Signal Name | Description                 |

|----------------|-------------|--------|----------|-------------|-----------------------------|

| Not connected  | DC_CS       | P3.1   | P3.2     | +           | Non-inverting Input Channel |

| Reserved       | N/A         | P3.3   | P3.4     | GND         | Ground                      |

| Reserved       | N/A         | P3.5   | P3.6     | GND         | Ground                      |

| Address line 0 | A0          | P3.7   | P3.8     | GND         | Ground                      |

| Address line 1 | A1          | P3.9   | P3.10    | GND         | Ground                      |

| Address line 2 | A2          | P3.11  | P3.12    | GND         | Ground                      |

| Reserved       | N/A         | P3.13  | P3.14    | GND         | Ground                      |

| Reserved       | N/A         | P3.15  | P3.16    | GND         | Ground                      |

| Convert Start  | DC_CONVST   | P3.17  | P3.18    | GND         | Ground                      |

| Interrupt pin  | INTC        | P3.19  | P3.20    | GND         | Ground                      |

Conversions are initiated on the falling edge of the convert start signal. It is therefore critical when measuring large amplitude and/or high frequency input signals, the user provide a clean low jitter convert start pulse.

The convert start signal can be applied to the ADS8472 from the decoder outputs or from connector P3 pin 17. Address decoder SN74ACH138 is used to generate the read (RD) and conversion start (CONVST) signals to the converter. Jumpers W3 and W4 allow the user to assign these two signals to different addresses in memory. This allows for the stacking of up to two ADS8472EVMs into processor memory. See Table 3 for jumper settings. If the user applies a convert start signal directly on P3 pin 17, then be sure to short W6 pins 1-2. This will bypass the decoder output selected by position of W4.

Note, the evaluation module does not allow chip select ( $\overline{CS}$ ) line of the converter to be assigned to different memory locations. It is therefore suggested the  $\overline{CS}$  line be grounded or wired to an appropriate signal of the processor.

| Reference<br>Designator | Description                                | 1-2                        | 2-3                        |

|-------------------------|--------------------------------------------|----------------------------|----------------------------|

| W1                      | Set digital buffer supply voltage to +5V   | Installed                  | Not installed              |

|                         | Set digital buffer supply voltage to +3.3V | Not installed              | Installed † <sup>(1)</sup> |

| W2                      | Apply inverted BUSY to INTC signal         | Installed † <sup>(1)</sup> | Not installed              |

|                         | Apply BUSY signal to INTC signal           | Not installed              | Installed                  |

| W3                      | Set RD signal to add[0x3]                  | Installed                  | Not installed              |

|                         | Set RD signal to add[0x4]                  | Not installed              | Installed                  |

| W4                      | Set CONVST signal to add[0x1]              | Installed                  | Not installed              |

|                         | Set CONVST signal to add[0x2]              | Not installed              | Installed                  |

#### Table 4. Jumper Settings

<sup>&</sup>lt;sup>(1)</sup> † Indicates factory installed option.

www.ti.com

| Table 4. Jumper Settings | (continued) |

|--------------------------|-------------|

|--------------------------|-------------|

| Reference<br>Designator | Description                             | 1-2           | 2-3       |

|-------------------------|-----------------------------------------|---------------|-----------|

| W5                      | W5 Set DC_CS to CS of ADS8472           |               | N/A       |

| W6                      | Set DC_CONVST to CONVST of ADS8472      | Installed     | Installed |

|                         | Set decoder output to CONVST of ADS8472 | Not installed | Installed |

The data bus is available at connector P2, see Table 4 for pin out information.

| Description | Signal Name | Connec | tor.Pin# | Signal Name | Description |

|-------------|-------------|--------|----------|-------------|-------------|

| Reserved    | N/A         | P2.1   | P2.2     | GND         | Ground      |

| Reserved    | N/A         | P2.3   | P2.4     | GND         | Ground      |

| Data Bit 0  | DB0         | P2.5   | P2.6     | GND         | Ground      |

| Data Bit 1  | DB1         | P2.7   | P2.8     | GND         | Ground      |

| Data Bit 2  | DB2         | P2.9   | P2.10    | GND         | Ground      |

| Data Bit 3  | DB3         | P2.11  | P2.12    | GND         | Ground      |

| Data Bit 4  | DB4         | P2.13  | P2.14    | GND         | Ground      |

| Data Bit 5  | DB5         | P2.15  | P2.16    | GND         | Ground      |

| Data Bit 6  | DB6         | P2.17  | P2.18    | GND         | Ground      |

| Data Bit 7  | DB7         | P2.19  | P2.20    | GND         | Ground      |

| Data Bit 8  | DB8         | P2.21  | P2.22    | GND         | Ground      |

| Data Bit 9  | DB9         | P2.23  | P2.24    | GND         | Ground      |

| Data Bit 10 | DB10        | P2.25  | P2.26    | GND         | Ground      |

| Data Bit 11 | DB11        | P2.27  | P2.28    | GND         | Ground      |

| Data Bit 12 | DB12        | P2.29  | P2.30    | GND         | Ground      |

| Data Bit 13 | DB13        | P2.31  | P2.32    | GND         | Ground      |

| Data Bit 14 | DB14        | P2.33  | P2.34    | GND         | Ground      |

| Data Bit 15 | DB15        | P2.35  | P2.36    | GND         | Ground      |

# Table 5. Data Bus Connector P2

In addition to interfacing to the various micro controller and digital signal processors from Texas Instruments, this board also plugs into the TSW1100 card. The TSW1100 is a PC-based data capture card. J7 connector is installed to allow the user to plug the ADS8472EVM directly and collect data for analysis.

# Table 6. TSW1100 Connector

| Description | Signal Name | Connec | tor.Pin# | Signal Name | Description      |

|-------------|-------------|--------|----------|-------------|------------------|

| Ground      | Ground      | J7.1   | J7.2     | N/C         | Not Connected    |

| Ground      | Ground      | J7.3   | J7.4     | N/C         | Not Connected    |

| Ground      | Ground      | J7.5   | J7.6     | D0          | Data Bit 0 (LSB) |

| Ground      | Ground      | J7.7   | J7.8     | D1          | Data Bit 1       |

| Ground      | Ground      | J7.9   | J7.10    | D2          | Data Bit 2       |

| Ground      | Ground      | J7.11  | J7.12    | D3          | Data Bit 3       |

| Ground      | Ground      | J7.13  | J7.14    | D4          | Data Bit 4       |

| Ground      | Ground      | J7.15  | J7.16    | D5          | Data Bit 5       |

| Ground      | Ground      | J7.17  | J7.18    | D6          | Data Bit 6       |

| Ground      | Ground      | J7.19  | J7.20    | D7          | Data Bit 7       |

| Ground      | Ground      | J7.21  | J7.22    | D8          | Data Bit 8       |

| Ground      | Ground      | J7.23  | J7.24    | D9          | Data Bit 9       |

| Ground      | Ground      | J7.25  | J7.26    | D10         | Data Bit 10      |

Ground

| Description | Signal Name | Connec | tor.Pin# | Signal Name | Description   |  |

|-------------|-------------|--------|----------|-------------|---------------|--|

| Ground      | Ground      | J7.27  | J7.28    | D11         | Data Bit 11   |  |

| Ground      | Ground      | J7.29  | J7.30    | D12         | Data Bit 12   |  |

| Ground      | Ground      | J7.31  | J7.32    | D13         | Data Bit 13   |  |

| Ground      | Ground      | J7.33  | J7.34    | D14         | Data Bit 14   |  |

| Ground      | Ground      | J7.35  | J7.36    | D15         | Data Bit 15   |  |

| Ground      | Ground      | J7.37  | J7.38    | N/C         | Not Connected |  |

| Ground      | Ground      | J7.39  | J7.40    | INTc        | Trigger Clock |  |

#### Table 6. TSW1100 Connector (continued)

This evaluation module provides direct access to all the analog-to-digital converter input control and output signals via connector J6, see Table 6.

| Table 7. Fin out for Converter Control Connector, 30 |             |                |       |             |             |  |  |

|------------------------------------------------------|-------------|----------------|-------|-------------|-------------|--|--|

| Description                                          | Signal Name | Connector.Pin# |       | Signal Name | Description |  |  |

| Chip Select Signal                                   | CS          | J6.1           | J6.2  | GND         | Ground      |  |  |

| Read Signal                                          | RD          | J6.3           | J6.4  | GND         | Ground      |  |  |

| Convert Start Signal                                 | CONVST      | J6.5           | J6.6  | GND         | Ground      |  |  |

| Byte Signal                                          | BYTE        | J6.7           | J6.8  | GND         | Ground      |  |  |

| RESERVED                                             | RESERVED    | J6.9           | J6.10 | GND         | Ground      |  |  |

J6.12

GND

# Table 7 Pin out for Converter Control Connector .16

#### 5 **Power Supplies**

**Busy Signal**

The EVM accepts four power supplies.

• A dual ±VA DC supply for the dual supply op-amps. Recommend ±6VDC supply.

J6.11

- A single +5.0 V DC supply for analog section of the board (A/D + Reference). ٠

- A single +5.0V or +3.3V DC supply for digital section of the board (A/D + address decoder + buffers). ٠

There are two ways to provide these voltages.

1. Wire in the voltages at test points on the EVM. See Table 8.

BUSY

| Test Point | Signal | Description                                                 |  |  |  |

|------------|--------|-------------------------------------------------------------|--|--|--|

| TP6        | +BVDD  | Apply +3.3VDC or +5.0VDC. See ADC datasheet for full range. |  |  |  |

| TP3        | +AVCC  | Apply +5.0VDC.                                              |  |  |  |

| TP4        | +VA    | Apply +6.0VDC. Positive supply for amplifier.               |  |  |  |

| TP5        | –VA    | Apply -6.0VDC. Negative supply for amplifier.               |  |  |  |

2. Use the power connector J5, and derive the voltages elsewhere. The pinout for this connector is shown in Table 9. If using this connector, then set W1 jumper to connect +3.3VD or +5VD from connector to +BVDD. Short between pins 1-2 to select +5VD, or short between pins 2-3 to select +3.3VD as the source for the digital buffer voltage supply (+BVDD).

| Signal   | Power Con | nector – J5 | Signal    |  |  |  |

|----------|-----------|-------------|-----------|--|--|--|

| +VA(+6V) | 1         | 2           | –VA (-6V) |  |  |  |

| +5VA     | 3         | 4           | N/C       |  |  |  |

| DGND     | 5         | 6           | AGND      |  |  |  |

| N/C      | 7         | 8           | N/C       |  |  |  |

| +3.3VD   | 9         | 10          | +5VD      |  |  |  |

| Table 9. Power | Connector, | J5, Piı | n Out |

|----------------|------------|---------|-------|

|----------------|------------|---------|-------|

# 6 Using the ADS8472EVM

The ADS8472EVM serves the functions of being a reference design, a prototyping board, and finally as an software test platform.

#### 6.1 As a Reference Board

As a reference design, the ADS8472EVM contains the essential circuitry to showcase the analog-to-digital converter. This essential circuitry includes the input amplifier, reference circuit, and buffers. The ADS8472EVM analog input circuit is optimized for a wide bandwidth signal; therefore, the user may need to adjust the input buffer circuitry to better suit your needs. In AC-type applications where signal distortion is a concern, the user should use high quality capacitors such as Mica, polypropylene or COGs type capacitors in the signal path. In applications where the input is multiplexed, the A/D input resistor and capacitor may need to be adjusted further.

# 6.2 As a Prototype Board

As a prototype board, the ADS8472EVM features amplifiers in a standard 8-pin SOIC package and many resistor pads scattered around allowing the user to experiment with a host of circuits, as needed. The ADS8472EVM can be used to evaluate both dual- and single-supply amplifiers in both inverting and non-inverting configurations. The ADS8472EVM comes installed with a dual-supply amplifier which allows the user to take advantage of the full input voltage range of the converter. For applications that require signal supply operation and smaller input voltage range, the THS4031 can be replaced with the single-supply amplifier like the OPA300 or OPA350. Pad jumper SJP3 should be shorted between pads 1 and 2. This shorts the minus supply pin of the amplifier to ground. Positive supply voltage can be applied at test point TP4 or at connector J5 pin 1.

#### 6.2.1 Evaluation Board

There are two common methods to evaluate the ADS8472EVM's performance.

- 1. EVM used as a stand-alone system. The user is responsible for capturing and analyzing the data, typically via a logic analyzer and analysis software (LABView, MATLAB, etc)

- 2. EVM used in conjunction with TI's TSW1100 data capture card, http://focus.ti.com/docs/toolsw/folders/print/tsw1100.html

The following section discusses method two.

#### 6.2.2 EVM and TSW1100 Capture Card

The User's Guide for the data capture card is available at <u>http://focus.ti.com/lit/ug/slau155a/slau155a.pdf</u>. Refer to this guide for detailed information and set-up instructions.

The ADS8472EVM mates with the TSW1100 card via J7. There are two data ports available on the capture card, the reference designators are J1 and J2. The ADS8472EVM can be plugged into either port.

The TSW1100 is a data capture card and provides no control signals to the ADS8472. The <u>ADS8472</u> requires a <u>CONVST</u> pulse to begin digitizing the signal. Therefore, the user must provide a <u>CONVST</u> to the ADS8472 at P3 pin 17 or <u>at J6 pin 5</u> on the ADS8472EVM. In this case, it is recommended the ADS8472 be operated in the <u>CS</u> and <u>RD</u> tied low mode, as this requires only <u>CONVST</u> to toggle. To short this signals to ground, simply short across pins 1 and 2, and 3 and 4 of J6, respectively. The digitized data is available on the data bus at the end of every busy cycle. In this operating scheme, the inverted BUSY signal is used to trigger the TSW1100 card to read the data bus. To avoid line contention remove jumpers from W3, W4, W5, and W6 on the ADS8472EVM.

The ADS8472 EVM is supported with the TSW1100 capture card firmware release 1.x. Please use the ADS1610EVM entry as a template for acquiring data from the ADS8374EVM. Due to hardware limitations on the TSW1100 platform, data capture from the ADS8472EVM is restricted to 1MSPS minimum.

# 6.3 As a Software Test Platform

As a software test platform, connectors P1, P2, and P3 plug into the parallel interface connectors of the 5-6K interface board. The 5-6K interface board sits on the C5000 and C6000 digital signal processor starter kits (DSK). The ADS8472EVM is mapped then into the processor's memory space. The 5-6k interface board also provides an area for signal conditioning. This area can be used to install application circuit(s) for digitization by the ADS8472 analog-to-digital converter. For more information, see the 5-6K Interface Board user's guide (SLAU104).

For the software engineer, the ADS8472EVM provides a simple platform for interfacing to the converter. The EVM provides standard 0.1-inch headers and sockets to wire into prototype boards. The user need only provide three address lines (A2, A1, and A0) and address valid line (DC\_CS) to connector P3. To select which address combinations generate RD and CONVST, set jumpers as shown in Table 3. Recall that the Chip Select (CS) signal is not memory-mapped; therefore, it must be controlled by a general-purpose pin or shorted to ground at J6 pin 1. If address decoding is not required, the EVM provides direct access to converter data bus by P3 and control by J6.

# 7 ADS8472EVM BoM

The following table contains a complete Bill of Materials for the ADS8472EVM. The schematic diagram is also provided for reference. Contact the Product Information Center or e-mail <u>dataconvapps@list.ti.com</u> for questions regarding this EVM.

| QTY | Value            | REF DES                             | Footprint    | MFG                                | MFG Part No.      | Description                     |

|-----|------------------|-------------------------------------|--------------|------------------------------------|-------------------|---------------------------------|

| 3   | 0                | R16 R17 R33                         | 603          | Panasonic –<br>ECG or<br>Alternate | ERJ-3GEY0R00V     | RES 0Ω 1/16W 5% 0603 SMD        |

| 2   | 0                | R19 R22                             | 805          | Panasonic –<br>ECG or<br>Alternate | ERJ-6GEY0R00V     | RES 0.0 Ω 1/10W 5% 0805 SMD     |

| 2   | 5.1              | R39 R40                             | 805          | Panasonic –<br>ECG or<br>Alternate | ERJ-6GEYJ5R1V     | Resistor 5.1Ω 1/8W 5% 0805      |

| 3   | 33               | R5 R25 R26                          | 603          | Yageo America<br>or Alternate      | 9C06031A33R0FKHFT | RES 33.0Ω 1/10W 1% 0603 SMD     |

| 3   | 49.9             | R1–R3                               | 603          | Panasonic -<br>ECG or<br>Alternate | ERJ-3EKF49R9V     | RES 49.9 Ω 1/10W 1% 0603 SMD    |

| 2   | 75               | R36 R38                             | 805          | Yageo America<br>or Alternate      | 9C08052A75R0FKHFT | RES 75.0 Ω 1/8W 1% 0805 SMD     |

| 3   | 300              | R4 R27 R29                          | 603          | Yageo America<br>or Alternate      | RC0603FR-07300RL  | RES 300 Ω 1/10W 1% 0603 SMD     |

| 4   | 1k               | R8 R21 R31<br>R37                   | 805          | Yageo America<br>or Alternate      | 9C08052A1001JLHFT | RES 1.0kΩ 1/8W 5% 0805 SMD      |

| 5   | 10k              | R41–R45                             | 603          | Panasonic -<br>ECG or<br>Alternate | ERJ-3EKF1002V     | RES 10.0kΩ 1/10W 1% 0603 SMD    |

| 1   | 10k              | R46                                 | 805          | Panasonic -<br>ECG or<br>Alternate | ERJ-6GEYJ103V     | RES 10kΩ 1/8W 5% 0805 SMD       |

| 2   | NI               | R6 R28                              | 603          | Not Installed                      | Not Installed     |                                 |

| 11  | NI               | R7 R9–R13<br>R18 R20 R32<br>R34 R35 | 805          | Not Installed                      | Not Installed     |                                 |

| 2   | 47               | RP1 RP2                             | CTS_742      | CTS<br>Corporation                 | 742C163470JTR     | RES ARRAY 47Ω 16TERM 8RES SMD   |

| 1   | 1K               | RP3                                 | CTS_742      | CTS<br>Corporation                 | 742C163102JTR     | RES ARRAY 1kΩ 16TERM 8RES SMD   |

| 1   | 51               | RP4                                 | CTS_742_4RES | CTS<br>Corporation                 | 742C083510JTR     | RES ARRAY 51Ω 8TERM 4RES SMD    |

| 1   | 10K              | R24                                 | BOURNS_3296Y | Bourns Inc.                        | 3296Y-1-103       | POT 10kΩ 3/8" SQ CERM SL MT     |

| 4   | MMZ2012<br>R601A | L1–L4                               | 805          | TDK<br>Corporation                 | MMZ2012R601A      | FERRITE CHIP 600Ω 500MA 0805    |

| 13  | 1000pF           | C28–C36<br>C62–C65                  | 603          | TDK<br>Corporation or<br>Alternate | C1608X7R1H102K    | CAP CER 1000pF 50V XR7 10% 0603 |

| 1   | 2200pF           | C45                                 | 603          | TDK<br>Corporation or<br>Alternate | C1608C0G1H222J    | CAP CER 2200pF 50V C0G 5% 0603  |

| 6   | 0.1µF            | C66–C71                             | 603          | TDK<br>Corporation or<br>Alternate | C1608X7R1E104K    | CAP CER 0.10µF 25V X7R 10% 0603 |

| 6   | 0.1µF            | C9–C14                              | 805          | TDK<br>Corporation or<br>Alternate | C2012X7R1H104K    | CAP CER 0.10µF 50V X7R 10% 0805 |

| 2   | 0.47µF           | C1 C2                               | 603          | TDK<br>Corporation or<br>Alternate | C1608X5R1A474K    | CAP CER 0.47µF 10V X5R 10% 0603 |

| 2   | 1μF              | C5 C7                               | 603          | TDK<br>Corporation or<br>Alternate | C1608X5R1A105KT   | CAP CER 1.0µF 10V X5R 10% 0603  |

#### Table 10. Bill of Materials

| QTY | Value                                     | REF DES                                           | Footprint                     | MFG                                | MFG Part No.       | Description                                                         |

|-----|-------------------------------------------|---------------------------------------------------|-------------------------------|------------------------------------|--------------------|---------------------------------------------------------------------|

| 2   | 1μF                                       | C41 C42                                           | 805                           | TDK<br>Corporation or<br>Alternate | C2012X7R1E105K     | CAP CER 1.0µF 25V X7R 0805 T/R                                      |

| 8   | 2.2µF                                     | C20–C27                                           | 603                           | TDK<br>Corporation or<br>Alternate | C1608X5R1A225MT    | CAP CER 2.2µF 6.3V X5R 20% 0603                                     |

| 1   | 10µF                                      | C40                                               | 805                           | TDK<br>Corporation or<br>Alternate | C2012X5R0J106M     | CAP CER 10µF 6.3V X5R 20% 0805                                      |

| 8   | 10µF                                      | C48–C55                                           | 1206                          | TDK<br>Corporation or<br>Alternate | C3216X5R1C106M     | CAP CER 10µF 16V X5R 20% 1206                                       |

| 1   | 22µF                                      | C6                                                | 805                           | TDK<br>Corporation or<br>Alternate | C2012X5R0J226M     | CAP CER 22µF 6.3V X5R 20% 0805                                      |

| 1   | 47µF                                      | C37                                               | 1206                          | TDK<br>Corporation or<br>Alternate | C3216X5R0J476M     | CAP CER 47µF 6.3V X5R 20% 1206                                      |

| 15  | NI                                        | C3 C4 C8 C15<br>C16 C18 C19<br>C46 C47<br>C56–C61 | 603                           | Not Installed                      | Not Installed      | Multilayer Ceramic                                                  |

| 4   | NI                                        | C38 C39 C43<br>C44                                | 805                           | Not Installed                      | Not Installed      | 1/10W 0805 Chip Resistor                                            |

| 1   | REF3230                                   | U1                                                | 6-SOT(DBV)                    | Texas<br>Instruments               | REF3230AIDBVR      | 3.0V 4ppm/°C, 100µA SOT23-6 Series<br>(Bandgap) Voltage Reference   |

| 1   | REF3240                                   | U2                                                | 6-SOT(DBV)                    | Texas<br>Instruments               | REF3240AIDBVR      | 4.096V 4ppm/°C, 100µA SOT23-6 Series<br>(Bandgap) Voltage Reference |

| 1   | NI                                        | U3                                                | 8-SOP(D)                      | Not Installed                      | Not Installed      | SOIC reference alternate                                            |

| 1   | THS4032                                   | U4                                                | 8-SOP(D)                      | Texas<br>Instruments               | THS4032CD          | 100-MHz Low Noise Voltage-Feedback<br>Amplifier, Dual               |

| 1   | ADS8472                                   | U5                                                | 48-QFN(RGZ)                   | Texas<br>Instruments               | ADS8472IBRGZR      | ADS8472 16-bit 1MSPS A/D                                            |

| 2   | THS4031                                   | U6 U7                                             | 8-SOP(D)                      | Texas<br>Instruments               | THS4031IDR         | 100-MHz Low-noise high-speed amplifier                              |

| 4   | SN74AHC<br>245PWR                         | U8–U11                                            | 20-TSSOP(PW)                  | Texas<br>Instruments               | SN74AHC245PWR      | Octal Bus Transceiver, 3-State                                      |

| 1   | SN74AHC<br>1G04DBV                        | U12                                               | 5-SOT(DBV)                    | Texas<br>Instruments               | SN74AHC1G04DBVR    | Single Inverter Gate                                                |

| 1   | SN74AHC<br>138PWR                         | U13                                               | 16-TSSOP(PW)                  | Texas<br>Instruments               | SN74AHC138PWR      | 3-Line to 8-Line Decoder / Demultiplexer                            |

| 2   | SMA_PCB<br>_MT                            | J1 J2                                             | SMA_JACK                      | Johnson<br>Components<br>Inc.      | 142-0701-301       | Right Angle SMA Connector                                           |

| 2   | NI                                        | J3 J4                                             | SMA_JACK                      | Not Installed                      | Not Installed      | MaCom #5002-5003-10/Amphenol #901-144                               |

| 1   | 5X2X.1                                    | J5                                                | 5X2X.1_SMT_SOCKET             | Samtec                             | SSW-105-22-S-D-VS  | 0.025" SMT Socket – Bottom side of PWB                              |

| 1   |                                           |                                                   |                               | Samtec                             | TSM-105-01-T-D-V-P | 0.025" SMT Plug - Top side of PWB                                   |

| 1   | 6X2X.1                                    | J6                                                | 6X2X.1_SMT_PLUG_<br>&_SOCKET  | Samtec                             | TSM-105-01-T-D-V-P | 0.025" SMT Plug - Top side of PWB                                   |

| 1   | 40-PIN<br>Header                          | J7                                                | 20X2X.1                       | Tyco<br>Electronics/Am<br>p        | 4-103149-0-20      | CONN HEADR BRKWAY 0.100 40POS R/A                                   |

| 2   | 10X2X.1                                   | P1 P3                                             | 10X2X.1_SMT_PLUG_<br>& SOCKET | Samtec                             | SSW-110-22-S-D-VS  | 0.025" SMT Socket - Bottom side of PWB                              |

| 1   | 18X2X.1_<br>SMT_PLU<br>G_<br>&_SOCKE<br>T | P2                                                | 18X2.1_SMT_PLUG_<br>&_SOCKET  | Samtec                             | SSW-118-22-S-D-VS  | 0.025" SMT Socket - Bottom side of PWB                              |

| 1   |                                           |                                                   |                               | Samtec                             | TSM-118-01-T-D-V-P | 0.025" SMT Plug - Top side of PWB                                   |

| 2   | SJP2                                      | SJP5 SJP6                                         | SJP2                          | NOT<br>INSTALLED                   | NOT INSTALLED      |                                                                     |

| 4   | SJP3                                      | SJP1-SJP4                                         | SJP3                          | NOT<br>INSTALLED                   | NOT INSTALLED      | NOT INSTALLED NOT INSTALLED                                         |

|     | T               | i .                              | T           | i                       |                |                                  |

|-----|-----------------|----------------------------------|-------------|-------------------------|----------------|----------------------------------|

| QTY | Value           | REF DES                          | Footprint   | MFG                     | MFG Part No.   | Description                      |

| 5   | 3POS_JU<br>MPER | W1–W4 W6                         | 3pos_jump   | Samtec                  | TSW-103-07-L-S | 3 Position Jumper _ 0.1" spacing |

| 1   | 2POS_JU<br>MPER | W5                               | 2pos_jump   | Samtec                  | TSW-102-07-L-S | 2 Position Jumper _ 0.1" spacing |

| 8   | TP_0.025        | TP3–TP7 TP9<br>TP11 TP12         | test_point2 | Keystone<br>Electronics | 5000K-ND       | TEST POINT PC MINI 0.040"D RED   |

| 6   | TP_0.025        | TP1 TP2 TP8<br>TP10 TP13<br>TP14 | test_point2 | Keystone<br>Electronics | 5001K–ND       | TEST POINT PC MINI 0.040"D BLACK |

Table 10. Bill of Materials (continued)

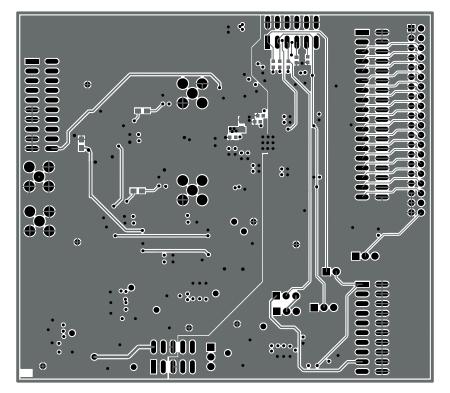

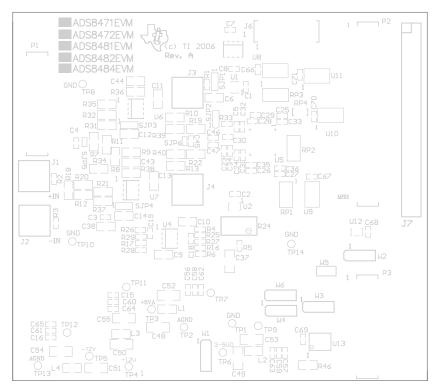

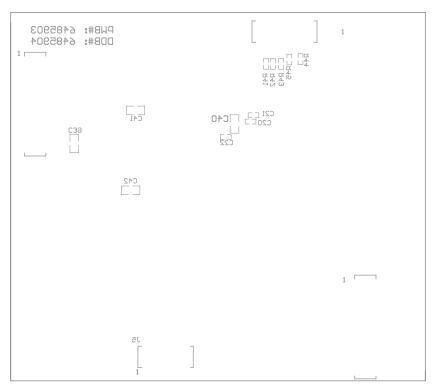

# 8 ADS8472EVM Layout

This section contains the EVM layout.

Figure 2. Top – Layer 1

Figure 3. Ground Plane – Layer 2

Figure 4. Power Plane – Layer 3

Figure 5. Bottom – Layer 4

Figure 6. Top Overlay

Figure 7. Bottom OverLay

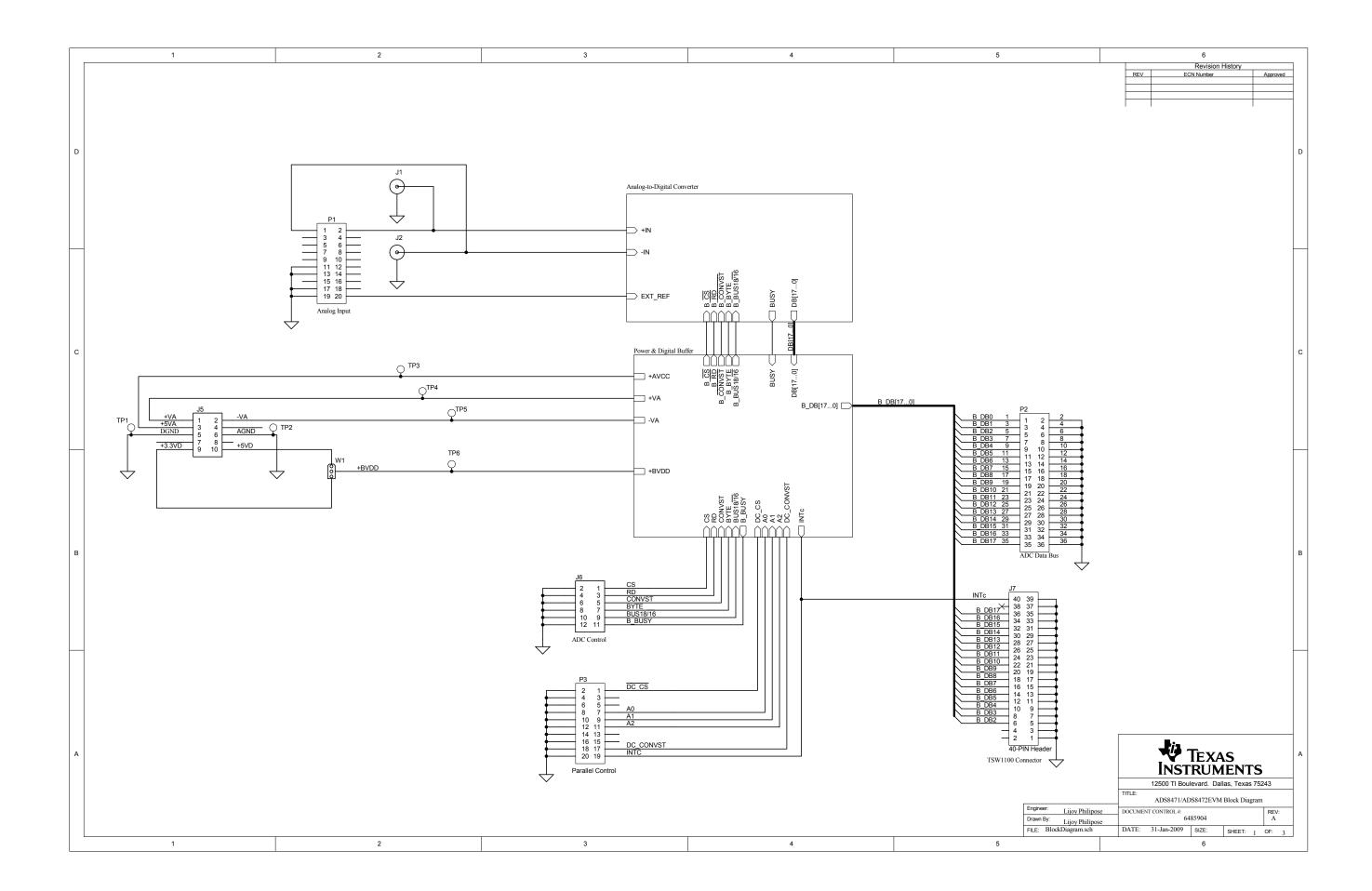

# 9 ADS8472EVM Schematic

Schematic diagram pages are appended to this user's guide.

#### **EVALUATION BOARD/KIT IMPORTANT NOTICE**

Texas Instruments (TI) provides the enclosed product(s) under the following conditions:

This evaluation board/kit is intended for use for **ENGINEERING DEVELOPMENT, DEMONSTRATION, OR EVALUATION PURPOSES ONLY** and is not considered by TI to be a finished end-product fit for general consumer use. Persons handling the product(s) must have electronics training and observe good engineering practice standards. As such, the goods being provided are not intended to be complete in terms of required design-, marketing-, and/or manufacturing-related protective considerations, including product safety and environmental measures typically found in end products that incorporate such semiconductor components or circuit boards. This evaluation board/kit does not fall within the scope of the European Union directives regarding electromagnetic compatibility, restricted substances (RoHS), recycling (WEEE), FCC, CE or UL, and therefore may not meet the technical requirements of these directives or other related directives.

Should this evaluation board/kit not meet the specifications indicated in the User's Guide, the board/kit may be returned within 30 days from the date of delivery for a full refund. THE FOREGOING WARRANTY IS THE EXCLUSIVE WARRANTY MADE BY SELLER TO BUYER AND IS IN LIEU OF ALL OTHER WARRANTIES, EXPRESSED, IMPLIED, OR STATUTORY, INCLUDING ANY WARRANTY OF MERCHANTABILITY OR FITNESS FOR ANY PARTICULAR PURPOSE.

The user assumes all responsibility and liability for proper and safe handling of the goods. Further, the user indemnifies TI from all claims arising from the handling or use of the goods. Due to the open construction of the product, it is the user's responsibility to take any and all appropriate precautions with regard to electrostatic discharge.

EXCEPT TO THE EXTENT OF THE INDEMNITY SET FORTH ABOVE, NEITHER PARTY SHALL BE LIABLE TO THE OTHER FOR ANY INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES.

TI currently deals with a variety of customers for products, and therefore our arrangement with the user is not exclusive.

# TI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein.

Please read the User's Guide and, specifically, the Warnings and Restrictions notice in the User's Guide prior to handling the product. This notice contains important safety information about temperatures and voltages. For additional information on TI's environmental and/or safety programs, please contact the TI application engineer or visit <u>www.ti.com/esh</u>.

No license is granted under any patent right or other intellectual property right of TI covering or relating to any machine, process, or combination in which such TI products or services might be or are used.

#### **FCC Warning**

This evaluation board/kit is intended for use for **ENGINEERING DEVELOPMENT, DEMONSTRATION, OR EVALUATION PURPOSES ONLY** and is not considered by TI to be a finished end-product fit for general consumer use. It generates, uses, and can radiate radio frequency energy and has not been tested for compliance with the limits of computing devices pursuant to part 15 of FCC rules, which are designed to provide reasonable protection against radio frequency interference. Operation of this equipment in other environments may cause interference with radio communications, in which case the user at his own expense will be required to take whatever measures may be required to correct this interference.

#### **EVM WARNINGS AND RESTRICTIONS**

It is important to operate this EVM within the input voltage range of -6 VDC to +6 VDC, and the output voltage range of 0 to 4 VDC.

Exceeding the specified input range may cause unexpected operation and/or irreversible damage to the EVM. If there are questions concerning the input range, please contact a TI field representative prior to connecting the input power.

Applying loads outside of the specified output range may result in unintended operation and/or possible permanent damage to the EVM. Please consult the EVM User's Guide prior to connecting any load to the EVM output. If there is uncertainty as to the load specification, please contact a TI field representative.

During normal operation, some circuit components may have case temperatures greater than 70°C. The EVM is designed to operate properly with certain components above 70°C as long as the input and output ranges are maintained. These components include but are not limited to, switching transistors, inductor, and IC. These types of devices can be identified using the EVM schematic located in the EVM User's Guide. When placing measurement probes near these devices during operation, please be aware that these devices may be very warm to the touch.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright = 2007, Texas Instruments Incorporated

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products                    |                        | Applications       |                           |

|-----------------------------|------------------------|--------------------|---------------------------|

| Amplifiers                  | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters             | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DLP® Products               | www.dlp.com            | Broadband          | www.ti.com/broadband      |

| DSP                         | dsp.ti.com             | Digital Control    | www.ti.com/digitalcontrol |

| Clocks and Timers           | www.ti.com/clocks      | Medical            | www.ti.com/medical        |

| Interface                   | interface.ti.com       | Military           | www.ti.com/military       |

| Logic                       | logic.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Power Mgmt                  | power.ti.com           | Security           | www.ti.com/security       |

| Microcontrollers            | microcontroller.ti.com | Telephony          | www.ti.com/telephony      |

| RFID                        | www.ti-rfid.com        | Video & Imaging    | www.ti.com/video          |

| RF/IF and ZigBee® Solutions | www.ti.com/lprf        | Wireless           | www.ti.com/wireless       |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2009, Texas Instruments Incorporated