SLES201E - JANUARY 2007 - REVISED MARCH 2011

# DIGITAL AUDIO PROCESSOR WITH ANALOG INTERFACE

Check for Samples: TAS3208

# **FEATURES**

- Digital Audio Processor

- Fully Programmable With Graphical, Drag-and-Drop PurePath Studio<sup>™</sup> Software **Development Environment**

- 135-MHz Operation

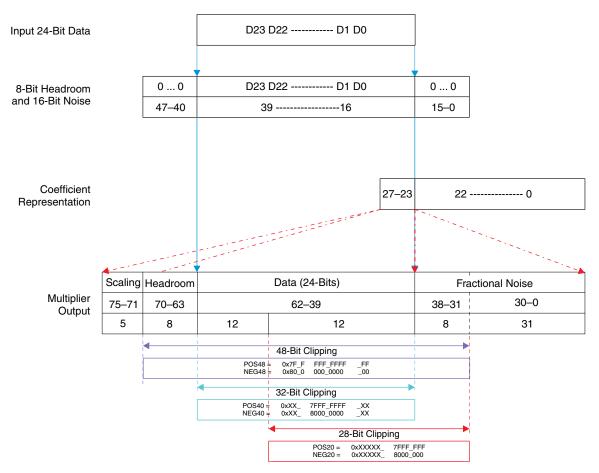

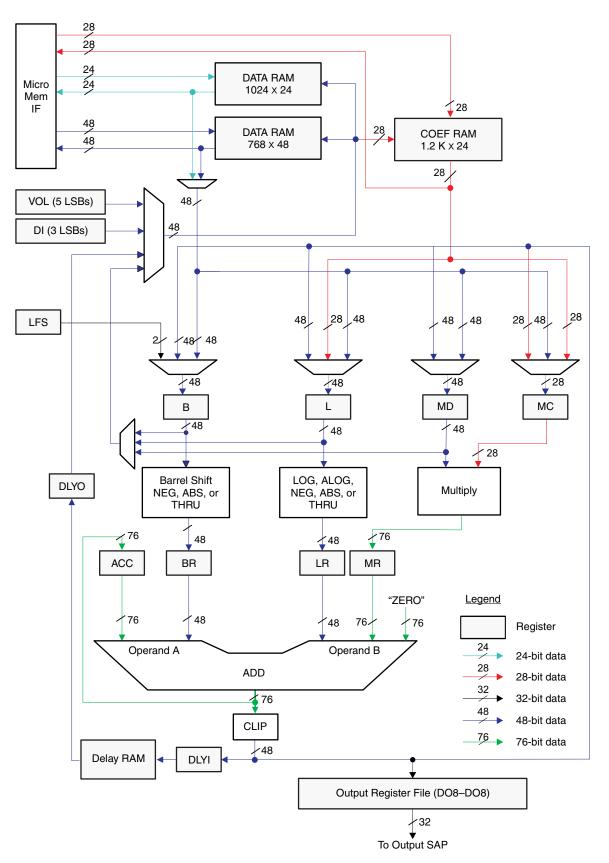

- 48-Bit Data Path With 76-Bit Accumulator

- Hardware Single-Cycle Multiplier (28 × 48)

- **Five Simultaneous Operations Per Clock Cycle**

- Usable 768 Words Data RAM (48 Bit), Usable 1K Coefficient RAM (28 Bit)

- Usable 2.5K Program RAM

- 360 ms at 48 kHz, 17K Words 24-Bit Delay Memory

- Slave Mode F<sub>s</sub> is 44.1 kHz and 48 kHz

- Master Mode F<sub>s</sub> is 48 kHz

- Analog Audio Input/Output

- 10:1 Stereo Analog Input MUX

- Stereo Analog Pass-Through Channel

- Stereo, Single-Ended ADC (93 dB DNR Typical)

- Six Single-Ended DACs (97 dB DNR Typical)

- Stereo Headphone Amplifier, 24-mW Power Output into 16  $\Omega$ , 100 pF

- **Digital Audio Input/Output**

- **Three Synchronous Serial Audio Inputs** (Six Channels)

- Two Synchronous Serial Audio Outputs (Four Channels)

- Input and Output Data Formats: 16-, 20-, or 24-Bit Data Left, Right, and I<sup>2</sup>S

- SPDIF Transmitter

- System Control Processor

- Embedded 8051 WARP Microprocessor

- Programmable Using Standard 8051 C Compilers

- Four Programmable GPIO Pins

- **General Features**

- Two I<sup>2</sup>C Ports for Slave or Master Download

- Single 3.3-V Power Supply

- Integrated Regulators

# APPLICATIONS

- Flat-Screen TVs

- MP3 Players/Music Phone Docks

- **Speaker Bars** •

- **Mini/Micro Component Systems** ٠

- ٠ **Automotive Head Units**

- **Musical Instruments**

# DESCRIPTION

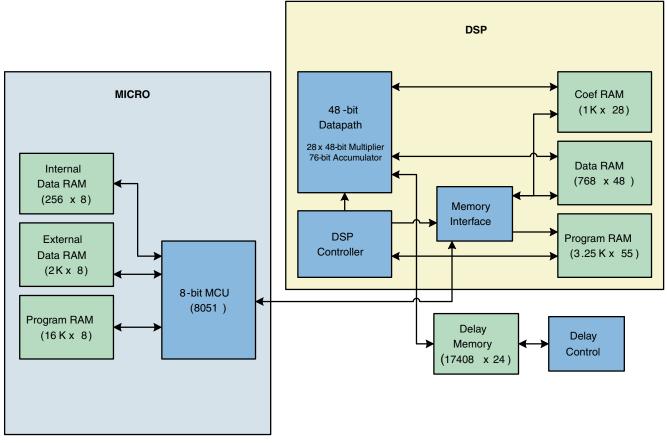

The TAS3208 is a highly-integrated audio system-on-chip (SOC) consisting of a fully-programmable 48-bit digital audio processor, 10:1 stereo analog input MUX, stereo ADC, six DACs, and other analog functionality. The TAS3208 is programmable with the graphical PurePath Studio<sup>™</sup> suite of DSP code development software. PurePath Studio is a highly intuitive, drag-and-drop development environment that minimizes software development effort while allowing the end user to utilize the power and flexibility of the TAS3208's digital audio processing core.

TAS3208 processing capability includes speaker equalization and cross over, volume/bass/treble control, signal mixing/MUXing/splitting, delay compensation, dynamic range compression, and many other basic audio functions. Audio functions such as matrix decoding, stereo widening, surround sound virtualization and psychoacoustic bass boost are also available with either third party or TI royalty-free algorithms.

The TAS3208 contains a custom-designed, fully-programmable 135-MHz, 48-bit digital audio processor. A 76-bit accumulator ensures that the high precision necessary for quality digital audio is maintained during arithmetic operations. A stereo, 93-dB DNR ADC and six 97-dB DNR DACs ensure that high-quality audio is maintained through the whole signal chain.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. PurePath Studio. PowerPAD are trademarks of Texas Instruments.

# TAS3208

SLES201E - JANUARY 2007 - REVISED MARCH 2011

TEXAS INSTRUMENTS

www.ti.com

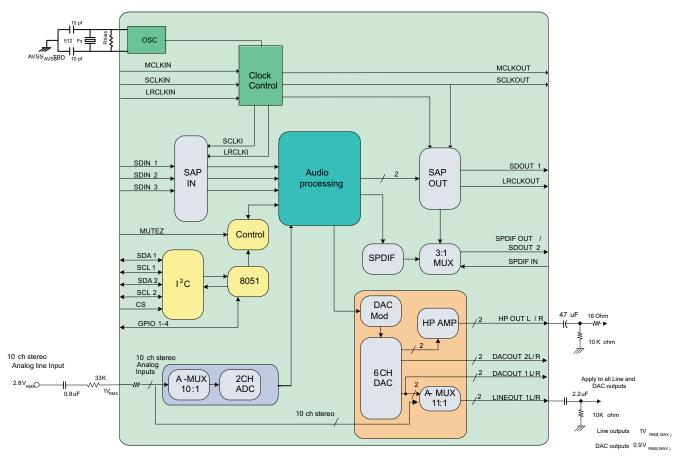

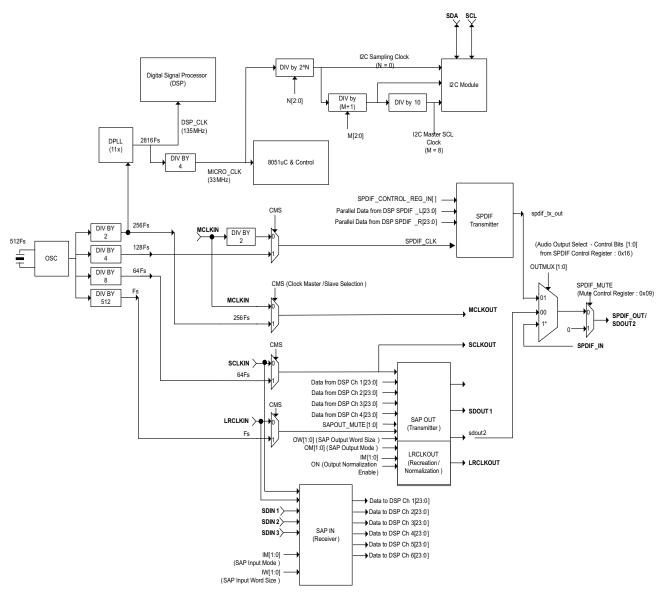

The TAS3208 is composed of seven functional blocks:

- Clock and serial data interface

- · Analog input and output

- M8051 WARP controller, serial control interface, and device control

- Audio DSP digital audio processing

- Power supply

- Internal references

Figure 1 shows the functional structure of the TAS3208.

Figure 1. Block Diagram

SLES201E - JANUARY 2007 - REVISED MARCH 2011

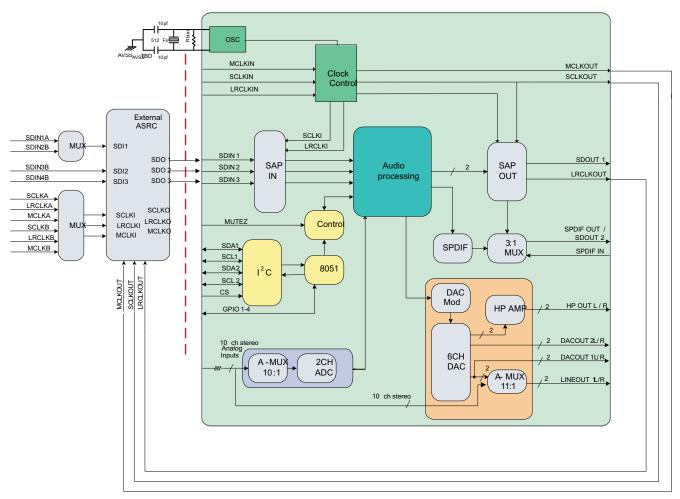

The TAS3208 may be used with an external asynchronous sample rate converter (ASRC) to accommodate asynchronous serial inputs at different sampling rates (see Figure 2).

Figure 2. Interface to External ASRC

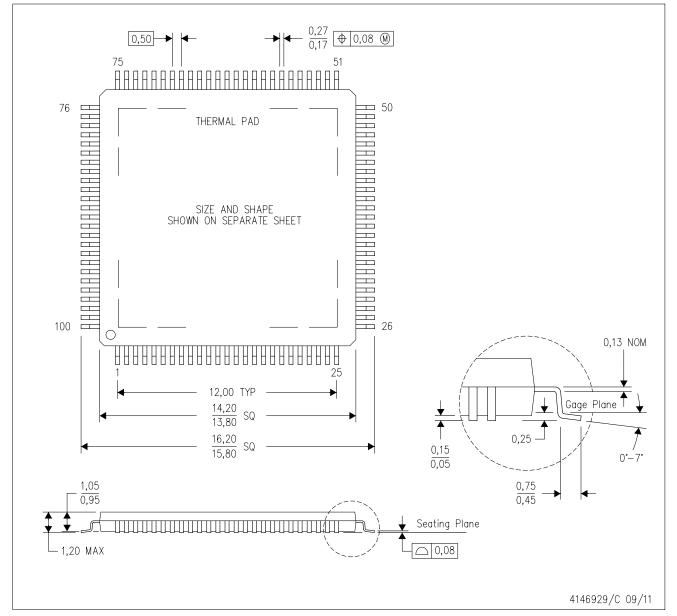

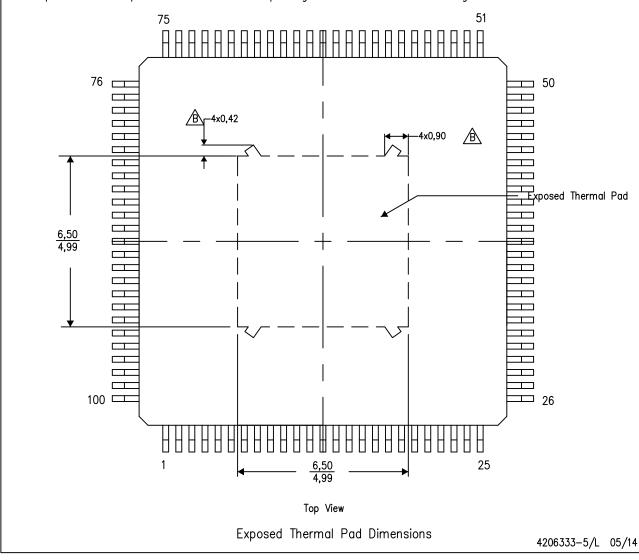

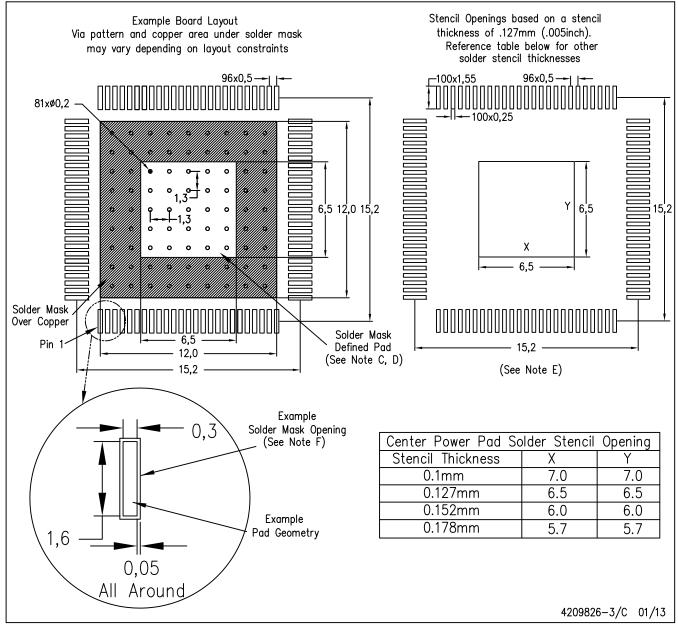

### **Table 1. ORDERING INFORMATION**

| T <sub>A</sub> | PACKAGE <sup>(1)</sup> <sup>(2)</sup> |               | ORDERABLE PART NUMBER | TOP-SIDE MARKING |

|----------------|---------------------------------------|---------------|-----------------------|------------------|

| –40°C to 85°C  |                                       |               | TAS3208IPZP           |                  |

| -40 C 10 65 C  | 7050 070                              | Tape and reel | TAS3208IPZPR          | TAS3208IPZP      |

| 0000 1- 7000   | – TQFP – PZP                          |               | TAS3208PZP            | TA 00000 DZD     |

| –20°C to 70°C  |                                       | TAS3208PZPR   | TAS3208PZP            |                  |

<sup>(1)</sup> Package drawings, thermal data, and symbolization are available at www.ti.com/packaging.

<sup>(2)</sup> For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI website at www.ti.com.

SLES201E - JANUARY 2007 - REVISED MARCH 2011

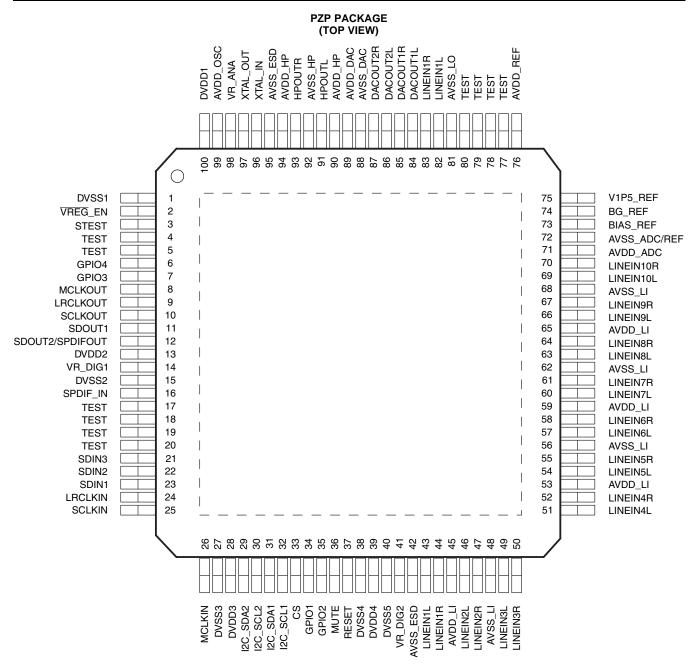

## **Table 2. TERMINAL FUNCTIONS**

| Т                          | TERMINAL             |     | TERMINATION <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                 |  |  |

|----------------------------|----------------------|-----|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NO.                        | NAME                 | I/O |                            | DESCRIPTION                                                                                                                                                                 |  |  |

| 1                          | DVSS1                | Р   |                            | Digital ground                                                                                                                                                              |  |  |

| 2                          | VREG_EN              | DI  |                            | Voltage regulator enable                                                                                                                                                    |  |  |

| 3                          | STEST                | DI  | Pulldown                   | Test pin to reconfigure pins                                                                                                                                                |  |  |

| 4, 5,<br>17, 18,<br>19, 20 | TEST                 | _   | Pulldown                   |                                                                                                                                                                             |  |  |

| 6                          | GPIO4                | DIO | Pulldown                   | General-purpose input/output 4                                                                                                                                              |  |  |

| 7                          | GPIO3                | DIO | Pulldown                   | General-purpose input/output 3                                                                                                                                              |  |  |

| 8                          | MCLKOUT              | DO  |                            | Master clock output                                                                                                                                                         |  |  |

| 9                          | LRCLKOUT             | DO  |                            | Left/right (frame) clock output                                                                                                                                             |  |  |

| 10                         | SCLKOUT              | DO  |                            | Serial audio data clock output                                                                                                                                              |  |  |

| 11                         | SDOUT1               | DO  |                            | Serial digital audio data output 1                                                                                                                                          |  |  |

| 12                         | SDOUT2/<br>SPDIF_OUT | DO  |                            | Serial digital audio data out 2/SPDIF output                                                                                                                                |  |  |

| 13                         | DVDD2                | Р   |                            | 3.3-V digital power                                                                                                                                                         |  |  |

| 14                         | VR_DIG1              | Р   |                            | Pinout of internal regulator. A 4.7-µF low-ESR capacitor should be connected between this pin and digital ground. This terminal must not be used to power external devices. |  |  |

| 15                         | DVSS2                | Р   |                            | Digital ground                                                                                                                                                              |  |  |

| 16                         | SPDIF_IN             | DI  |                            | SPDIF input                                                                                                                                                                 |  |  |

| 21                         | SDIN3                | DI  |                            | Serial digital audio data input 3                                                                                                                                           |  |  |

| 22                         | SDIN2                | DI  |                            | Serial digital audio data input 2                                                                                                                                           |  |  |

| 23                         | SDIN1                | DI  |                            | Serial digital audio data input 1                                                                                                                                           |  |  |

| 24                         | LRCLKIN              | DI  |                            | Left/right (frame) clock input                                                                                                                                              |  |  |

| 25                         | SCLKIN               | DI  |                            | Serial audio data clock input                                                                                                                                               |  |  |

| 26                         | MCLKIN               | DI  |                            | Master clock input                                                                                                                                                          |  |  |

| 27                         | DVSS3                | Р   |                            | Digital ground                                                                                                                                                              |  |  |

| 28                         | DVDD3                | Р   |                            | 3.3-V digital power master                                                                                                                                                  |  |  |

| 29                         | I2C_SDA2             | DIO |                            | I <sup>2</sup> C serial data master                                                                                                                                         |  |  |

| 30                         | I2C_SCL2             | DIO |                            | I <sup>2</sup> C serial clock slave                                                                                                                                         |  |  |

| 31                         | I2C_SDA1             | DIO |                            | I <sup>2</sup> C serial data slave                                                                                                                                          |  |  |

| 32                         | I2C_SCL1             | DIO |                            | l <sup>2</sup> C serial clock                                                                                                                                               |  |  |

| 33                         | CS                   | DI  |                            | Chip select                                                                                                                                                                 |  |  |

| 34                         | GPIO1                | DIO |                            | General-purpose input/output 1                                                                                                                                              |  |  |

| 35                         | GPIO2                | DIO |                            | General-purpose input/output 2                                                                                                                                              |  |  |

| 36                         | MUTE                 | DI  | Pullup                     | Mute device                                                                                                                                                                 |  |  |

| 37                         | RESET                | DI  | Pullup                     | Reset                                                                                                                                                                       |  |  |

| 38                         | DVSS4                | Р   |                            | Digital ground                                                                                                                                                              |  |  |

| 39                         | DVDD4                | Р   |                            | 3.3-V digital power                                                                                                                                                         |  |  |

| 40                         | DVSS5                | Р   |                            | 3.3-V digital power                                                                                                                                                         |  |  |

| 41                         | VR_DIG2              | Р   |                            | Pinout of internal regulator. A 4.7-µF low-ESR capacitor should be connected between this pin and digital ground. This terminal must not be used to power external devices. |  |  |

| 42                         | AVSS_ESD             | Р   |                            | Analog ESD ground                                                                                                                                                           |  |  |

| 43                         | LINEIN1L             | AI  |                            | Left-channel analog input 1                                                                                                                                                 |  |  |

(1) All pullups are 20-µA weak pullups, and all pulldowns are 20-µA weak pulldowns (166 kΩ). The pullups and pulldowns are included to ensure proper input logic levels if the terminals are left unconnected (pullups at logic 1 input; pulldowns at logic 0 input). Devices that drive inputs with pullups must be able to sink 20 µA while maintaining a logic 0 drive level. Devices that drive inputs with pulldowns must be able to source 20  $\mu A$  while maintaining a logic 1 drive level.

|                   |              | •   |                            | MINAL FUNCTIONS (continued)                                             |  |  |

|-------------------|--------------|-----|----------------------------|-------------------------------------------------------------------------|--|--|

|                   |              | I/O | TERMINATION <sup>(1)</sup> | DESCRIPTION                                                             |  |  |

| NO.<br>44         | LINEIN1R     | AI  |                            | Right-channel analog input 1                                            |  |  |

| 45, 53,           | AVDD LI      | P   |                            | 3.3-V analog power                                                      |  |  |

| 59, 65            |              |     |                            |                                                                         |  |  |

| 46                | LINEIN2L     | AI  |                            | Left-channel analog input 2                                             |  |  |

| 47<br>48, 56,     | LINEIN2R     | AI  |                            | Right-channel analog input 2                                            |  |  |

| 62, 68            | AVSS_LI      | Р   |                            | Analog ground                                                           |  |  |

| 49                | LINEIN3L     | AI  |                            | Left-channel analog input 3                                             |  |  |

| 50                | LINEIN3R     | AI  |                            | Right-channel analog input 3                                            |  |  |

| 51                | LINEIN4L     | AI  |                            | Left-channel analog input 4                                             |  |  |

| 52                | LINEIN4R     | AI  |                            | Right-channel analog input 4                                            |  |  |

| 54                | LINEIN5L     | AI  |                            | Left-channel analog input 5                                             |  |  |

| 55                | LINEIN5R     | AI  |                            | Right-channel analog input 5                                            |  |  |

| 57                | LINEIN6L     | AI  |                            | Left-channel analog input 6                                             |  |  |

| 58                | LINEIN6R     | AI  |                            | Right-channel analog input 6                                            |  |  |

| 60                | LINEIN7L     | AI  |                            | Left-channel analog input 7                                             |  |  |

| 61                | LINEIN7R     | AI  |                            | Right-channel analog input 7                                            |  |  |

| 63                | LINEIN8L     | AI  |                            | Left-channel analog input 8                                             |  |  |

| 64                | LINEIN8R     | AI  |                            | Right-channel analog input 8                                            |  |  |

| 66                | LINEIN9L     | AI  |                            | Left-channel analog input 9                                             |  |  |

| 67                | LINEIN9R     | AI  |                            | Right-channel analog input 9                                            |  |  |

| 69                | LINEIN10L    | AI  |                            | Left-channel analog input 10                                            |  |  |

| 70                | LINEIN10R    | AI  |                            | Right-channel analog input 10                                           |  |  |

| 71                | AVDD_ADC     | Р   |                            | 3.3-V analog power                                                      |  |  |

| 72                | AVSS_ADC/REF | Р   |                            | Analog ground                                                           |  |  |

| 73                | BIAS_REF     | AO  |                            | Pin should be tied to analog ground with 22 k $\Omega \pm 1\%$ .        |  |  |

| 74                | BG_REF       | AO  |                            | Band-gap output. Must be tied to ground with 1-µF low-ESR capacitor.    |  |  |

| 75                | V1P5_REF     | AO  |                            | Common-mode output. Must be tied to ground with 1-µF low-ESR capacitor. |  |  |

| 76                | AVDD_REF     | Р   |                            | 3.3-V analog power                                                      |  |  |

| 77, 78,<br>79, 80 | TEST         | -   |                            |                                                                         |  |  |

| 81                | AVSS_LO      | Р   |                            | Analog ground                                                           |  |  |

| 82                | LINEOUT1L    | AO  |                            | Left-channel analog output 1                                            |  |  |

| 83                | LINEOUT1R    | AO  |                            | Right-channel analog output 1                                           |  |  |

| 84                | DACOUT1L     | AO  |                            | Left-channel digital-to-analog converter output 1                       |  |  |

| 85                | DACOUT1R     | AO  |                            | Right-channel digital-to-analog converter output 1                      |  |  |

| 86                | DACOUT2L     | AO  |                            | Left-channel digital-to-analog converter output 2                       |  |  |

| 87                | DACOUT2R     | AO  |                            | Right-channel digital-to-analog converter output 2                      |  |  |

| 88                | AVSS_DAC     | Р   |                            | Analog ground                                                           |  |  |

| 89                | AVDD_DAC     | Р   |                            | 3.3-V analog power                                                      |  |  |

| 90                | <br>AVDD_HP  | Р   |                            | 3.3-V analog power                                                      |  |  |

| 91                | HPOUTL       | AO  |                            | Left-channel headphone output                                           |  |  |

| 92                | AVSS_HP      | Р   |                            | Analog ground                                                           |  |  |

| 93                | HPOUTR       | AO  |                            | Right-channel headphone output                                          |  |  |

| 94                | AVDD_HP      | P   |                            | 3.3-V analog power                                                      |  |  |

| 95                | AVSS_ESD     | P   |                            | Analog ground                                                           |  |  |

| 95                |              |     |                            |                                                                         |  |  |

www.ti.com

Submit Documentation Feedback

6

www.ti.com

# Table 2. TERMINAL FUNCTIONS (continued)

| TERMINAL |          | TERMINATION <sup>(1)</sup> | DESCRIPTION                                                                                                                                                            |                         |  |

|----------|----------|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|--|

| NO.      | NAME     | I/O                        | TERMINATION                                                                                                                                                            | DESCRIPTION             |  |

| 97       | XTAL_OUT | DO                         |                                                                                                                                                                        | External crystal output |  |

| 98       | VR_ANA   | Р                          | Pinout of internal regulator. A 4.7-µF low-ESR capacitor should be connected between this pin and digital ground. This terminal must n used to power external devices. |                         |  |

| 99       | AVDD_OSC | Р                          | 3.3-V analog power                                                                                                                                                     |                         |  |

| 100      | DVDD1    | Р                          |                                                                                                                                                                        | 3.3-V digital power     |  |

INSTRUMENTS

Texas

# Clocks

The TAS3208 can be configured as either the clock master or clock slave depending on the settings in the clock configuration register. By default, the TAS3208 is configured as the clock master. Figure 3 shows the block diagram of the TAS3208 clocks.

Figure 3. Clocking System

# **Digital Audio Interface**

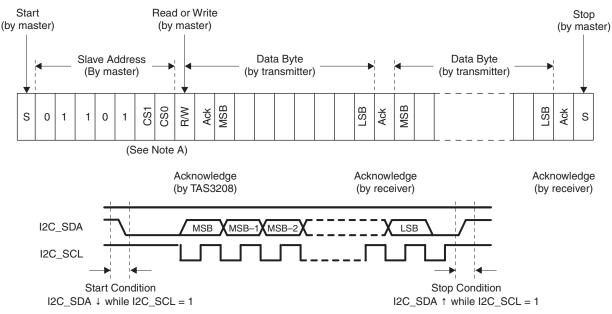

The TAS3208 has three digital inputs that accept discrete I<sup>2</sup>S, discrete left-justified, and discrete right-justified PCM data.

The TAS3208 has two digital outputs that provide discrete I<sup>2</sup>S, discrete left-justified, and discrete right-justified PCM data. The second digital output can also be configured to provide SPDIF encoded PCM data.

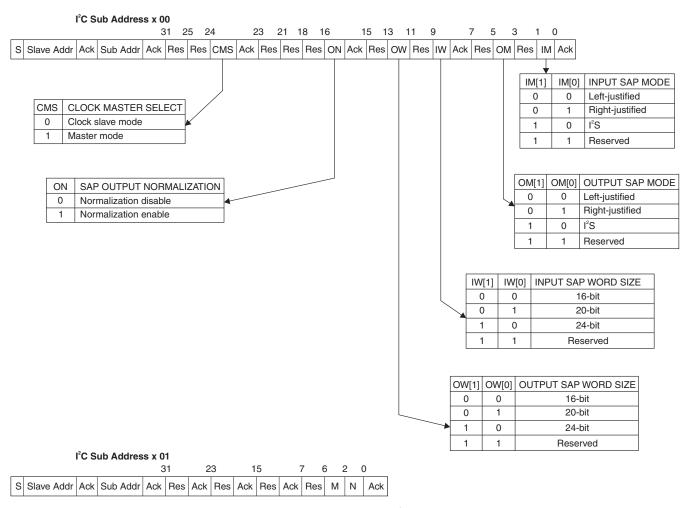

The TAS3208 has a SPDIF input that is capable of routing an SPDIF-encoded signal through the device. This input is not processed by the digital audio processor (DAP). The clocking system for the device is shown in Figure 4.

#### SLES201E – JANUARY 2007 – REVISED MARCH 2011

Figure 4. Clocking System I<sup>2</sup>C Mapping

### **Clock Master Operation**

When configured as the device clock master, an external crystal is used as a reference to an internal oscillator. In this mode of operation, all internal clocks are generated by the oscillator.

- LRCLKOUT is fixed at 48 kHz (Fs).

- SCLKOUT is fixed at 64 × Fs.

- MCLKOUT is fixed 256 × Fs.

### **Clock Slave Operation**

When configured as the device clock slave, the DAP, MCU, and I<sup>2</sup>C interface are derived from the external crystal. However, the digital audio clocks are supplied externally.

Internal analog clocks for the analog-to-digital converter (ADC) and digital-to-analog converter (DAC) are derived from the MCLKIN input. As a result, analog performance depends on the quality of MCLKIN.

Degradation in analog performance is to be expected, depending on the quality of MCLKIN.

The TAS3208 device does not include any internal clock error or click/pop detection/management. The muting of the outputs at updating of sample-rate-dependent coefficients must be initiated by the host system controller.

MCLKOUT, SCLKOUT, and LRCLKOUT are passed through from the clock inputs MCLKIN, SCLKIN, and LCLKIN.

- MCLKIN 256 × Fs is supplied externally.

- SCLKIN 64 × Fs is supplied externally.

- LRCLKIN Fs is supplied externally.

## NOTE

In slave mode, all incoming serial audio data must be synchronous to an incoming LRCLKIN of 32, 44.1, or 48 kHz. The TAS3208 does not support the use of an external (i.e., 24-MHz) clock input into XTALI.

# Digital Audio Data Formats

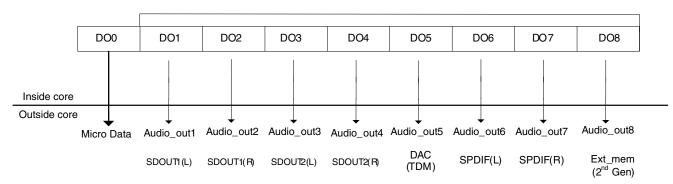

Serial data is input on pins SDIN3–SDIN1 on the TAS3208, allowing up to six channels of digital audio input. The TAS3208 supports 16-, 20-, or 24-bit data in left, right, or I<sup>2</sup>S serial data format. By default, all TAS3208 serial digital inputs are configured in the 24-bit I<sup>2</sup>S format. The serial data input format is configurable via the SAP/Clock Settings register.

Serial data is output on pins SDOUT1 and SDOUT2, allowing up to four channels of digital audio output. By default, the SDOUT data format is 24-bit I<sup>2</sup>S format at the same data rate as the input. The SDOUT1 and SDOUT2 outputs use SCLKOUT and LRCLKOUT signals to provide synchronization. SDOUT2 is multiplexed with an SPDIF output.

#### NOTE

To avoid audio artifacts, I<sup>2</sup>C commands to reconfigure the serial audio port (SAP) should not be issued as stand-alone commands, rather they should be accompanied by mute and unmute commands.

The TAS3208 uses the SCLK as a reference for both input and output samples. The negative edge of SCLK is used to output a new data bit, whereas the positive edge of SCLK is used to sample incoming serial data.

### Discrete *P*S Timing

I<sup>2</sup>S timing uses an LRCLK to define when the data being transmitted is for the left channel and when it is for the right channel. The LRCLK is LOW for the left channel and HIGH for the right channel. A bit clock running at 64 × Fs is used to clock in the data. There is a delay of one bit clock from the time the LRCLK signal changes state to the first bit of data on the data lines. The data is written most significant bit (MSB) first and is valid on the rising edge of bit clock. The TAS3208 will mask unused trailing data bit positions.

| 1  | 2-Channel I <sup>2</sup> S (Philips Format) Stereo Input     | 1                                                   |

|----|--------------------------------------------------------------|-----------------------------------------------------|

|    |                                                              | ◀ 32 clks                                           |

|    | LRCLK (note reversed phase) Left Channel                     | Right Channel                                       |

|    |                                                              |                                                     |

| N  | ISB LSB                                                      | MSB LSB                                             |

| L  | 24-Bit Mode<br>@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@          | @@@@@@@@@%%%%%%%%%%%%%%%%%%%%%%%%%%%%%%             |

|    | 20-Bit Mode<br>(19/19/17/19/13/12/11/19/9/8/7/6/3/4/3/2/1/0) | (19/19/17/19/15/14/13/12/11/10/9/8/7/6/5/4/3/2/1/0) |

| L. | 16-Bit Mode<br>(15/13/13/12/11/10/9/8/7/6/5/4/3/2/1/0)       | (15/13/13/13/11/10/9/8/7/6/5/4/3/2/1/0)             |

A. All data are presented in 2s-complement form with MSB first.

# Figure 5. SAP I<sup>2</sup>S 64 × Fs Format

#### www.ti.com

# Discrete Left-Justified (LJ) Timing

Left-justified timing uses an LRCLK to define when the data being transmitted is for the left channel or right channel. The LRCLK is HIGH for the left channel and LOW for the right channel. A bit clock running at 64 × Fs is used to clock in the data. The first bit of data appears on the data lines at the same time the LRCLK toggles. The data is written MSB first and is valid on the rising edge of bit clock. The TAS3208 will mask unused trailing data bit positions.

| 2-Channel Left-Justi                         | fied Stereo Input                 |     |                                                               |   |

|----------------------------------------------|-----------------------------------|-----|---------------------------------------------------------------|---|

| •                                            | 32 clks                           |     | <b>∢</b> 32 clks                                              | ► |

| LRCLK                                        | Left Channel                      |     | Right Channel                                                 |   |

|                                              |                                   |     |                                                               | ſ |

| MSB                                          |                                   | LSB | MSB LS                                                        | в |

| 24-Bit Mode<br>23X22X21X20X19X18X17X16X15X1  | 4\13\12\11\10\9\8\7\6\5\4\3\2\1\0 |     | 23/22/21/20/19/19/17/19/15/13/13/12/11/10/9/8/7/6/5/4/3/2/1/0 |   |

| 20-Bit Mode<br>(19/18/17/16/15/14/13/12/11/1 | 0\9\8\7\6\5\4\3\2\1\0             |     | (19X19X17X19X15X13X12X11X19X9X8X7X6X5X4X3X2X1X0)              |   |

| 16-Bit Mode<br>15/14/13/12/11/10/9/8/7/      | 6\5\4\3\2\1\0                     |     | (5)(1)(1)(1)(1)(1)(1)(1)(1)(1)(1)(1)(1)(1)                    |   |

A. All data are presented in 2's complement form with MSB first.

#### Figure 6. SAP Left-Justified 64 × Fs Format

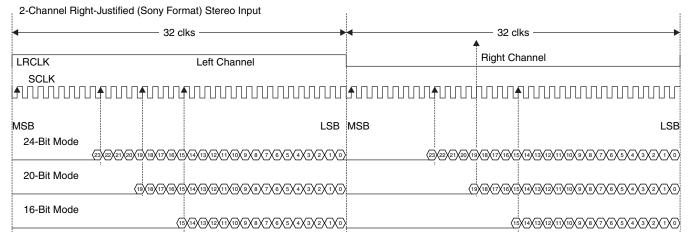

### Discrete Right-Justified (RJ) Timing

Right-justified timing uses an LRCLK to define when the data being transmitted is for the left channel or right channel. The LRCLK is HIGH for the left channel and LOW for the right channel. A bit clock running at 64 × Fs is used to clock in the data. The first bit of data appears on the data 8-bit clock periods (for 24-bit data) after L/RCLK toggles. In RJ mode, the LSB of data is always clocked by the last bit clock before L/RCLK transitions. The data is written MSB first and is valid on the rising edge of bit clock. The TAS3208 will mask unused leading data bit positions.

A. All data are presented in 2s-complement form with MSB first.

### Figure 7. SAP Right-Justified 64 × Fs Format

#### www.ti.com

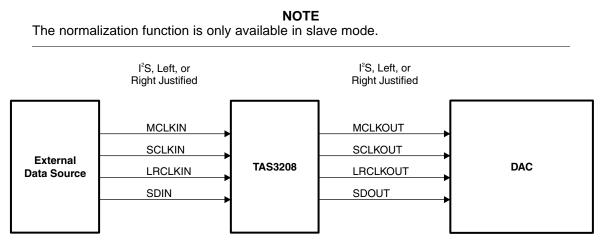

### **SAP Input and Output Normalization**

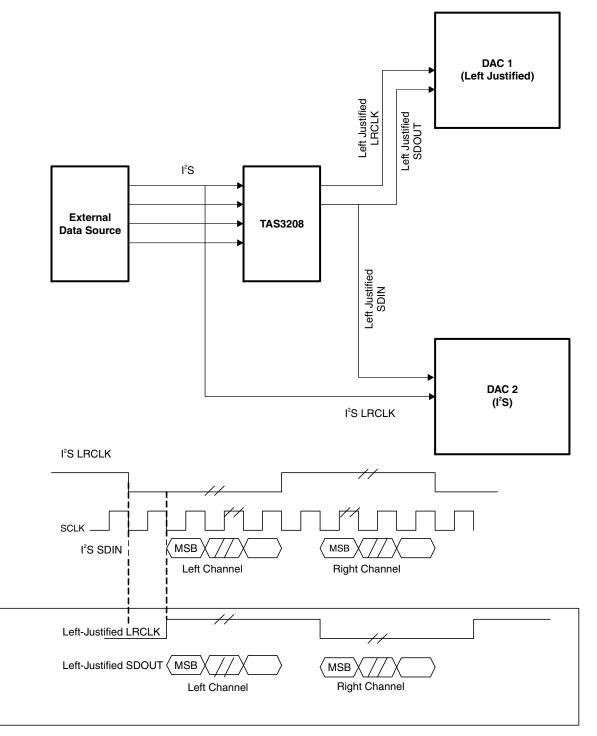

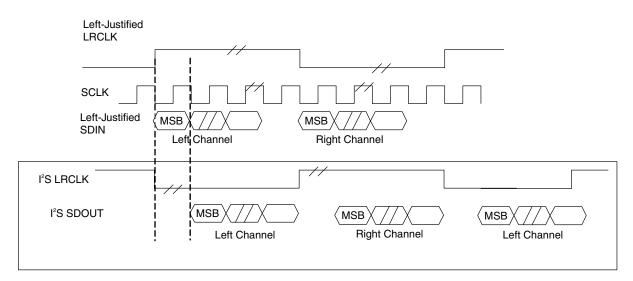

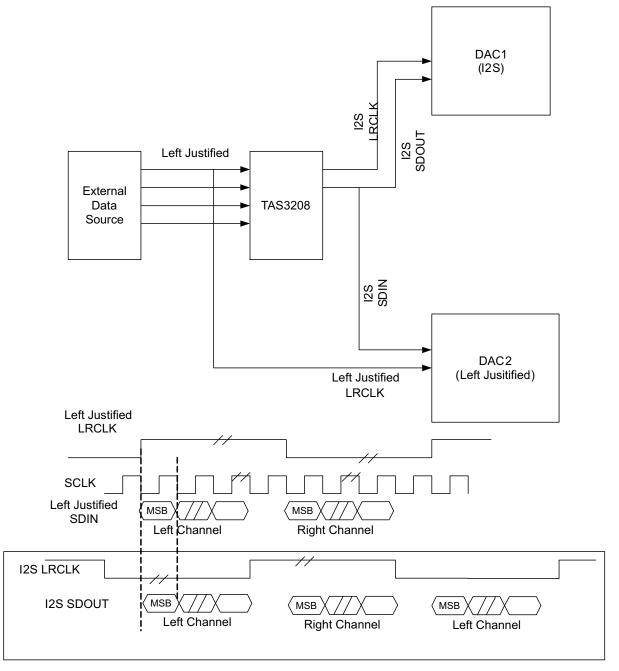

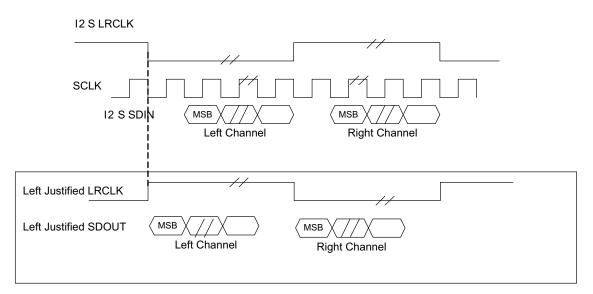

The TAS3208 supports SAP input and SAP output normalization. This supports simultaneous output to left-justified and I<sup>2</sup>S devices.

Figure 8. SAP Output Normal Configuration (No Normalization)

EXAS

**ISTRUMENTS**

Figure 9. SAP Output Configuration (I<sup>2</sup>S to Left Normalization ON)

**NSTRUMENTS**

ÈXAS

SLES201E - JANUARY 2007 - REVISED MARCH 2011

Figure 10. SAP Output Configuration (I<sup>2</sup>S to Left Normalization OFF)

EXAS

NSTRUMENTS

Figure 11. SAP Output Configuration (Left to I<sup>2</sup>S Normalization ON)

**ISTRUMENTS**

EXAS

SLES201E - JANUARY 2007-REVISED MARCH 2011

Figure 12. SAP Output Configuration (Left to I<sup>2</sup>S Normalization OFF)

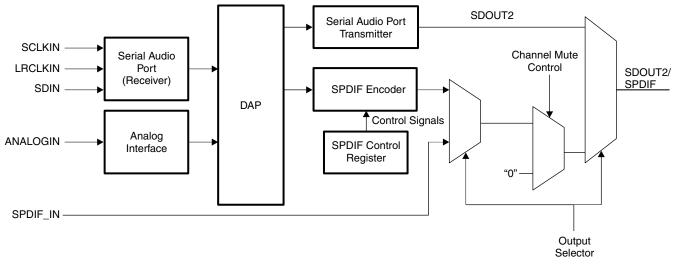

# SPDIF Encoder

The SPDIF encoder is a digital audio transmitter designed for use in consumer audio applications. Transmit data rates up to 48 kHz are supported. The SPDIF encoder complies with the IEC 60958 interface standard.

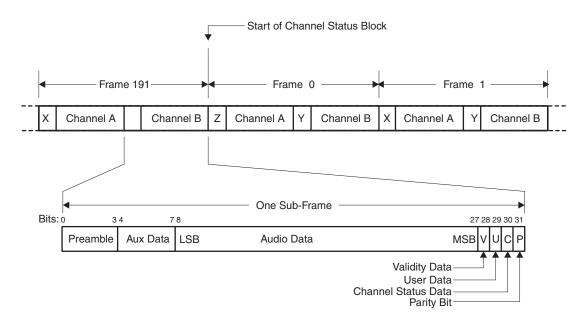

The SPDIF encoder creates a multiplexed bit stream containing audio, status, and user data. The multiplexed data format is shown in Figure 14. The data is then biphase mark encoded and output.

The hardware architecture of the SPDIF encoder is shown in Figure 13.

Figure 13. SPDIF Encoder Hardware Architecture

SLES201E – JANUARY 2007 – REVISED MARCH 2011

Figure 14. SPDIF Frame Format

# SPDIF Encoder Operation

The SPDIF encoder performs the multiplexing of audio, channel status, user, and validity flag. It also performs biphase mark encoding of the multiplexed data stream. Audio data for both left and right channels from the DAP are latched at the rising edge of the internal LRCLK, which marks the beginning of next sample cycle. The SPDIF encoder then multiplexes these samples with internally-generated preambles, channel status, user data, validity flag, and parity. The channel status and validity flag are generated based on the settings in the SPDIF control registers, while the user data is fixed to all zero. The biphase mark-encoded signal is then output starting at the next rising edge of the internal LRCLK. The generated SPDIF stream is fixed to consumer-mode linear audio PCM format.

While the RESET input is low, the transmitter output (SPDIF\_OUT) is forced to logic low level. Upon setting RESET high, the SPDIF encoder remains inactive until the module reset is removed by writing 0 to the RST bit of the control register. Then this module will wait for synchronization with the internal frame clock and start encoding audio data. It is recommended to set all other SPDIF control register bits before releasing the module reset.

### Transmitter Control Register

Table 3 shows the M8051 SFR register map for the SPDIF module control.

| ADDR | 7          | 6 | 5            | 5 4 3 2 1 |         |  |  | 0   |

|------|------------|---|--------------|-----------|---------|--|--|-----|

| xx00 | RST        |   |              |           | CP      |  |  | EMP |

| xx01 | CATEGORY L |   |              |           |         |  |  | L   |

| xx10 | SR         |   | VL VR SRCNUM |           |         |  |  |     |

| xx11 |            |   | CLKAC        |           | WORDLEN |  |  |     |

### Table 3. M8051 SFR Register Map

The relationship of the M8051 SFR register map with I<sup>2</sup>C registers is described in Table 4.

www.ti.com

STRUMENTS

ÈXAS

# Table 4. Relationship of M8051 SFR Register Map With I<sup>2</sup>C Registers

| RST     Module reset       0     Normal operation       1     Reset SPDIF TX module (default)       CP     Copy permit       0     Copy porthit (default)       1     Copy permit       EMP     Preemphasis (default)       1     50-/15-us 2-channel preemphasis       CATEGORY     Category code 7-bit device category code (default "0101010") (digital sound processor)       L     Generation status       0     Generation of higher (default)       1     Original       SR     Sampling rate       00     44.1 kHz       1     Served       1     Served       1     Served       1     Left-channel data is valid (default)       1     Right-channel data is valid (default)       1     Right-channel data is invalid       VR     Validity for right channel       0     Left-channel data is valid (default)       1     Right-channel data is invalid       SRCNUM     Source channel number       '0000'     Not specified       '001' <td< th=""><th></th><th>Table 4. Relationship of mooor of R Register map with 1 o Registers</th></td<> |                            | Table 4. Relationship of mooor of R Register map with 1 o Registers                    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|----------------------------------------------------------------------------------------|

| 0       Copy prohibit (default)         1       Copy permit         EMP       Preemphasis         0       No preemphasis (default)         1       50/15-ys 2-channel preemphasis         CATEGORY       Category code 7-bit device category code (default "0101010") (digital sound processor)         L       Generation 1 or higher (default)         0       Generation 1 or higher (default)         1       Original         SR       Sampling rate         00       44.1 kHz         01       48 kHz (default)         10       Reserved         11       32 kHz         VL       Validity for left channel         0       Left-channel data is valid (default)         1       Left-channel data is invalid         VR       Validity for right channel         0       Right-channel data is invalid         VR       Validity for right channel         0       Right-channel data is invalid         VR       Validity for right channel         0       Right-channel data is invalid         SRCNUM       Source channel number         '0000*       Z (default)         '001*       1         1001*       2 (default) <td>0</td> <td>Normal operation</td>                                                                                            | 0                          | Normal operation                                                                       |

| 0         No preemphasis (default)           1         50-/15-µs 2-channel preemphasis           CATEGORY         Category code 7-bit device category code (default "0101010") (digital sound processor)           L         Generation status           0         Generation 1 or higher (default)           1         Original           SR         Sampling rate           00         44.1 kHz           01         48 kHz (default)           10         Reserved           11         32 kHz           VL         Validity for left channel           0         Left-channel data is valid (default)           1         Left-channel data is valid (default)           1         Kight-channel data is invalid           VR         Validity for right channel           0         Right-channel data is invalid           SRCNUM         Source channel number           "0000"         Not specified           "0001"         1           "1000"         8           CLKAC         Clock accuracy           "00"         Level II, 100 ppm           "01"         Level II, 100 ppm           "01"         Level II, 100 ppm           "000"         8      <                                                                                                | 0                          | Copy prohibit (default)                                                                |

| L       Generation status         0       Generation 1 or higher (default)         1       Original         SR       Sampling rate         00       44.1 kHz         01       48 kHz (default)         10       Reserved         11       32 kHz         VL       Validity for left channel         0       Left-channel data is valid (default)         1       Left-channel data is valid (default)         1       Right-channel data is valid         0       Right-channel data is valid         1       Right-channel data is valid         0       Right-channel data is valid         1       Right-channel data is valid         0001"       1         Right-channel data is valid       1         10000"       1         11       Right-channel data is valid         12       2 (default)         100001"       1         1       8         CLKAC       Clock accuracy         100"       Level II, variable pitch shift                                                                                                                                                                | 0                          | No preemphasis (default)                                                               |

| 0       Generation 1 or higher (default)         1       Original         SR       Sampling rate         00       44.1 kHz         01       48 kHz (default)         10       Reserved         11       32 kHz         VL       Validity for left channel         0       Left-channel data is valid (default)         1       Left-channel data is invalid         VR       Validity for right channel         0       Right-channel data is valid (default)         1       Right-channel data is valid         SRCNUM       Source channel number         "0000"       Not specified         "0001"       1         "1000"       8         CLKAC       Clock accuracy         "00"       Level II, 1000 ppm         "1"       Reserved         WORDLEN       Sample bit size         "0000:       24 bits (default)                                                                                                                                                                                                                                                                                                                                                                                                                                               | CATEGORY                   | Category code 7-bit device category code (default "0101010") (digital sound processor) |

| 00       44.1 kHz         01       48 kHz (default)         10       Reserved         11       32 kHz         VL       Validity for left channel         0       Left-channel data is valid (default)         1       Right-channel data is invalid         SRCNUM       Source channel number         "0000"       Not specified         "0001"       2 (default)         "0010"       2 (default)         "1000"       8         CLKAC       Clock accuracy         "00"       Level II, 1000 ppm         "01"       Level II, 1000 ppm         "10"       Level II, 1000 ppm         "10"       Level II, 50 ppm (default)         "11"       Reserved         WORDLEN       Sample bit                                                                                                                              | 0                          | Generation 1 or higher (default)                                                       |

| 0       Left-channel data is valid (default)         1       Left-channel data is invalid         VR       Validity for right channel         0       Right-channel data is valid (default)         1       Right-channel data is invalid         SRCNUM       Source channel number         "0000"       Not specified         "0001"       1         "0010"       2 (default)         "0011"       3         :       :         "1000"       8         CLKAC       Clock accuracy         "00"       Level II, 1000 ppm         "01"       Level III, variable pitch shifted         "10"       Level II, 50 ppm (default)         "11"       Reserved         WORDLEN       Sample bit size         "0000:       24 bits (default)         "0001"       23 bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 00<br>01<br>10             | 44.1 kHz<br>48 kHz (default)<br>Reserved                                               |

| 0       Right-channel data is valid (default)         1       Right-channel data is invalid         SRCNUM       Source channel number         "0000"       Not specified         "0001"       1         "0010"       2 (default)         "0011"       3             "1000"       8         CLKAC       Clock accuracy         "00"       Level II, 1000 ppm         "01"       Level II, 1000 ppm         "10"       Level II, so ppm (default)         "11"       Reserved         WORDLEN       Sample bit size         "0000:       24 bits (default)         "0001"       23 bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0                          | Left-channel data is valid (default)                                                   |

| "0000"         Not specified           "0001"         1           "0010"         2 (default)           "0011"         3           :         :           "1000"         8           CLKAC         Clock accuracy           "00"         Level II, 1000 ppm           "01"         Level II, variable pitch shifted           "10"         Level II, so ppm (default)           "11"         Reserved           WORDLEN         Sample bit size           "0000:         24 bits (default)           "0001"         23 bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0                          | Right-channel data is valid (default)                                                  |

| CLKAC       Clock accuracy         "00"       Level II, 1000 ppm         "01"       Level III, variable pitch shifted         "10"       Level I, 50 ppm (default)         "11"       Reserved         WORDLEN       Sample bit size         "0000:       24 bits (default)         "0001"       23 bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | "0000"<br>"0001"<br>"0010" | Not specified<br>1<br>2 (default)                                                      |

| "00"       Level II, 1000 ppm         "01"       Level III, variable pitch shifted         "10"       Level I, 50 ppm (default)         "11"       Reserved         WORDLEN       Sample bit size         "0000:       24 bits (default)         "0001"       23 bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | "1000"                     | 8                                                                                      |

| "0000:         24 bits (default)           "0001"         23 bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | "00"<br>"01"<br>"10"       | Level II, 1000 ppm<br>Level III, variable pitch shifted<br>Level I, 50 ppm (default)   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | "0000:<br>"0001"           | 24 bits (default)<br>23 bits                                                           |

| "0100" 20 bits<br>:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | :                          |                                                                                        |

| Others Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                            | Reserved                                                                               |

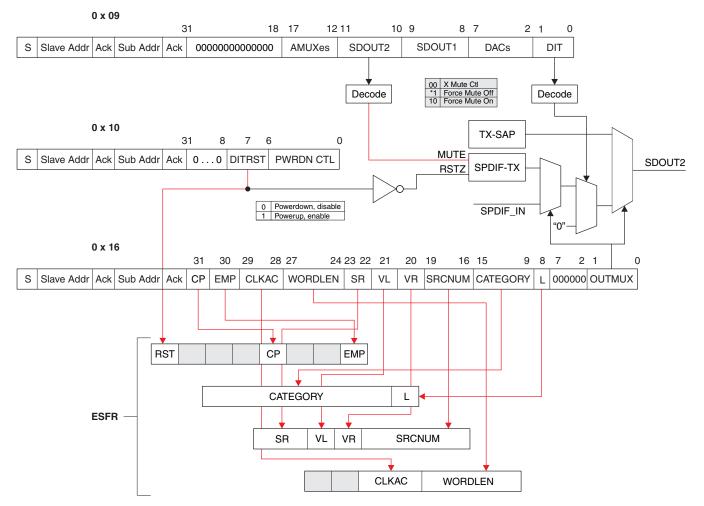

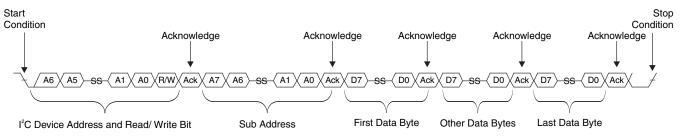

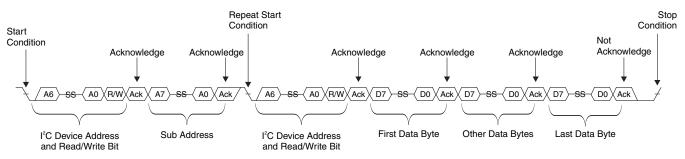

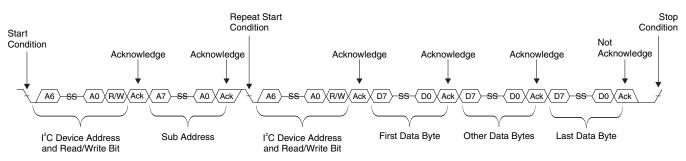

### PC Register Map for SPDIF

Figure 15 shows system-accessible I<sup>2</sup>C register mapping for controlling the SPDIF module. The mute control (MTE) uses the same control bits for controlling SDOUT2 mute at subaddress 0x09, and the module reset (RST) is mapped to subaddress 0x10 together with other power-down control bits. Other control bits are mapped to subaddress 0x16.

Figure 15. I<sup>2</sup>C Register to EFSR and Hardware Connection Map

TEXAS INSTRUMENTS

www.ti.com

# **Specification Coverage**

The TAS3208 is covered by the following specifications:

- IEC 60956-1: Second Edition, 2004-03

- IEC 60956-3: Second Edition, 2003-01

- IEC 958-2: First Edition, 1994-07

Specification coverage details can be found in Table 5.

# Table 5. TAS3208 Specification Coverage<sup>(1)</sup>

| SPECIFICATION | SECTION                                                                         | SUPPORTED                | REMARKS                                                                                                                                               |

|---------------|---------------------------------------------------------------------------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

|               | Interface Format (4)                                                            | Yes                      | Auto frame formatting                                                                                                                                 |

| IEC 60958-1   | Channel Status (5)                                                              |                          | First two bits fixed to 00 (consumer, linear PCM)                                                                                                     |

| IEC 958-2     | Mode 1 (software info delivery using b32–191 of channel stat) (4.2.2.1–4.2.2.3) | No                       | Bits 28–191 fixed to all zero                                                                                                                         |

|               | Channel Status – General (5.1)                                                  | Yes                      | First channel status bit fixed to 0                                                                                                                   |

|               |                                                                                 |                          | b0–1: Fixed (00)                                                                                                                                      |

|               | Channel Status – Application (5.2.1) –                                          | Yes                      | b2: Register settable                                                                                                                                 |

|               | Byte0 (control)                                                                 | res                      | b3–5: Register settable                                                                                                                               |

|               |                                                                                 |                          | b6–7: Fixed (00)                                                                                                                                      |

|               | Channel Status – Application (5.2.2) –<br>Byte1 (category)                      | Yes,<br>with restriction | Category code is register settable, with default value 0101010L (digital sound processor), but user data is fixed to all zero.                        |

|               | Channel Status – Application (5.2.2) –                                          | Yes                      | b16–19: Register settable                                                                                                                             |

| IEC 60958-3   | Byte2 (source and channel number)                                               |                          | b20-23: H/W auto set (1 for left, 2 for right channel)                                                                                                |

|               | Channel Status – Application (5.2.2) –<br>Byte3 (sampling freq and clock        | Yes,                     | b24–27: Register settable (32, 44.1, 48 kHz only)                                                                                                     |

|               | accuracy)                                                                       | with restriction         | b28–29: Register settable                                                                                                                             |

|               | Channel Status – Application (5.2.2) –<br>Byte4 (word length, original sampling | Yes,                     | b32–35<br>: H/W auto set according to register setting,<br>24-bit original output sample truncated to the<br>specified word length                    |

|               | rate, Byte0, b1, 6, 7 = "0")                                                    | partially                | b36–39<br>: Fixed to all zero (not indicated)                                                                                                         |

|               | Category Code Groups (5.3.2)                                                    | Yes,<br>with restriction | Specifying categories other than 0101010L (digital sound processor), especially those requiring nonzero user data is not recommended.                 |

|               | User Data (6)                                                                   | All zero                 |                                                                                                                                                       |

|               | Timing Accuracy (7.2.1)                                                         | Yes                      | Clock accuracy indication is register settable. Expected to set level I (50 ppm) for master mode (XTAL source) or level II (1000 ppm) for slave mode. |

|               | Line Driver Characteristics (7.3.2)                                             | No                       | Standard output buffer. Needs external SPDIF driver (e.g., optical driver).                                                                           |

(1) Other sections of the specification not mentioned here are either considered irrelevant or covered elsewhere. IEC 60958-4 is specific for professional applications and, thus, irrelevant.

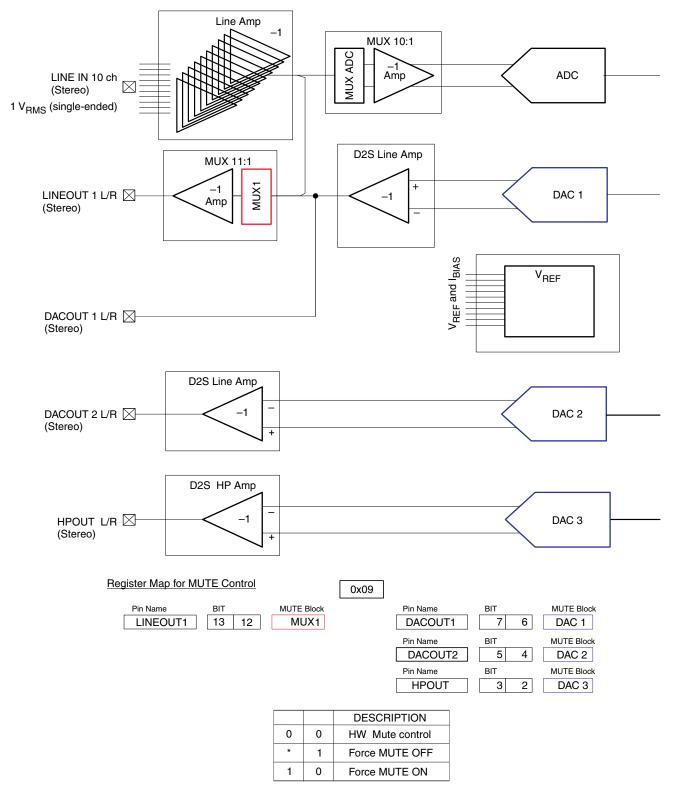

#### **Analog Audio Interface**

The TAS3208 is has ten analog stereo inputs that are multiplexed to one ADC. Additionally, the TAS3208 has one line output that can source any of the ten analog stereo inputs.

The TAS3208 has three stereo DACs. The outputs of of DAC3 are designed to be used as a 24-mW headphone amplifier or line driver. The other two DAC outputs are configured as stereo line drivers.

Both the ADC and DAC blocks can be placed in power down when not used.

Figure 16 shows a block diagram of the analog interface.

#### Stereo Analog-to-Digital Converter (ADC)

The TAS3208 has an analog 10:1 input multiplexer and an 11:1 output multiplexer. These can accept analog stereo inputs up to 1 Vrms. The outputs of the multiplexers are the stereo ADC and the line output.

The ADC supports a sampling rate of 48 kHz in clock master mode. In clock slave mode, 32-, 44.1-, and 48-kHz sampling frequencies are supported, based on the master clock frequency.

#### Stereo Digital-to-Analog Converters (DACs)

The TAS3208 has three stereo DACs. Each DAC can operate a maximum of 48 kHz. The DACs provide a 48-kHz sampling frequency in master mode. In slave mode, 32-, 44.1-, and 48-kHz sampling frequencies are supported, based on the master clock frequency. Two of the DACs are configured for providing line outputs. One of the stereo DACs has the capability to drive either a line out or to be used as a headphone (HP) amplifier.

The stereo HP amplifier is designed to drive up to 24 mW per channel into a headphone speaker load of 16  $\Omega$ . The headphone output is a single-ended configuration using series 16- $\Omega$  resistors and ac-coupling capacitors.

The TAS3208 includes a multiplexed stereo line driver output. The input can be selected to use the output of the stereo DAC or one of the ten sets of analog inputs. The line driver is capable of driving up to a  $10-k\Omega$  load.

NSTRUMENTS

Texas

www.ti.com

Figure 16. Analog Input/Output

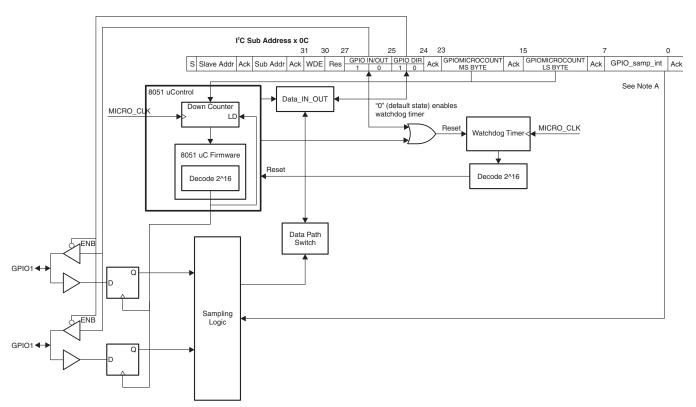

### Embedded M8051 WARP Microcontroller

The embedded M8051 WARP microcontroller provides the overall control for the TAS3208 device. This control includes device initialization, memory loading, I<sup>2</sup>C transactions, control-pin operations, and participation in most processing tasks requiring multiframe processing cycles.

The microcontroller has its own data RAM for storing intermediate values and queuing I<sup>2</sup>C commands, a fixed boot program ROM, and a programmable program RAM. The microprocessor's boot program cannot be altered. The microcontroller has specialized hardware for a master and slave interface operation, volume updates, and a programmable interval timer interrupt.

### M8051 Addressing Modes

The 256 bytes of internal data memory address space are accessible using indirect addressing instructions (including stack operations). However, only the lower 128 bytes are accessible using direct addressing. The upper 128 bytes of direct address data memory space are used to access external special function data registers (ESFRs).

#### Register Banks

There are four directly addressable register banks, only one of which may be selected at one time. The register banks occupy Internal data memory addresses from 00 hex to 1F hex.

### Bit Addressing

The 16 bytes of internal data memory that occupy addresses from 20 hex to 2F hex are bit addressable. ESFRs that have addresses in the form 1XXXX000 binary are also bit addressable.

#### Scratch Pad

Internal data memory occupying direct addresses from 30 hex to 7F hex can be used as scratch-pad registers or for the stack.

#### External Data Memory

External data RAM occupies a 64K address space. This space contains ESFRs. ESFRs permit access and control of the hardware features and internal interfaces of the TAS3208 DSP.

#### M8051 Boot-Up Sequence

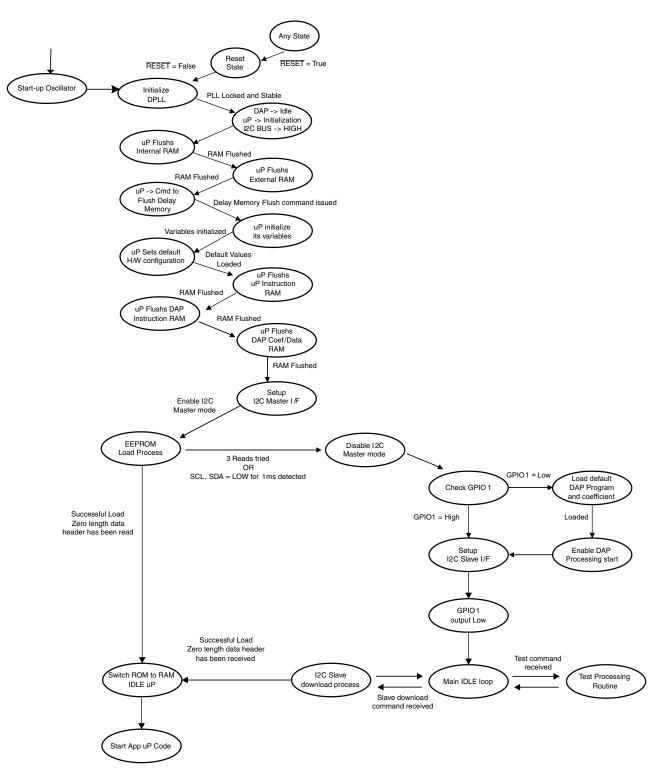

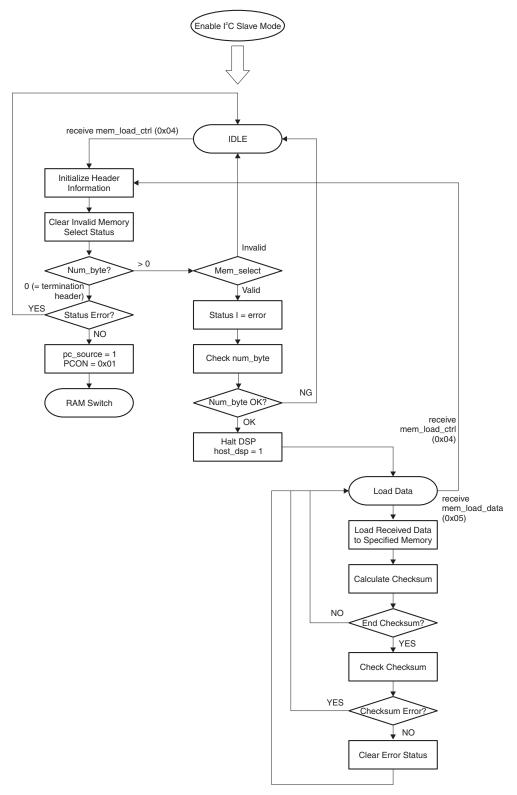

Figure 17 shows the boot-up sequence. M8051 MCU ROM code follows this sequence after device reset release. After the micro completes the boot-up application code (RAM code), the microcontroller switches the program counter from ROM to RAM code by pc\_source(esfr - 0xFD).

TEXAS INSTRUMENTS

www.ti.com

Detailed information about the boot-up sequence is given in Table 6.

www.ti.com

# Table 6. Process Description

|                                                                                                                                                                            | ESFR                      |      | DESCRIPTION                                                                                                            |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|------|------------------------------------------------------------------------------------------------------------------------|

| PROCESS STATE                                                                                                                                                              | ESFR                      |      | DESCRIPTION                                                                                                            |

| $\begin{array}{l} \text{DSP} \rightarrow \text{idle} \\ \text{uP} \rightarrow \text{initialization} \\ \text{l}^2\text{C} \text{ bus} \rightarrow \text{high} \end{array}$ |                           |      |                                                                                                                        |

| uP flush internal RAM                                                                                                                                                      |                           |      | Clear micro internal RAM (256 byte)                                                                                    |

| uP flush external RAM                                                                                                                                                      |                           |      | Clear micro external RAM (2048 byte)                                                                                   |

| uP command to flush delay memory                                                                                                                                           | clr_dly_ram (0xc0 bit(3)) | 1    |                                                                                                                        |

| uP initialize variables                                                                                                                                                    |                           |      | Initialize variables                                                                                                   |

|                                                                                                                                                                            | mute0_t                   | 0    |                                                                                                                        |

|                                                                                                                                                                            | mute1_t                   | 0    | Default mutez control                                                                                                  |

|                                                                                                                                                                            | mute2_t                   | 0    |                                                                                                                        |

|                                                                                                                                                                            | reset_dac_mod             | 0xff |                                                                                                                        |

|                                                                                                                                                                            | reset_adc_sinc            | 0x03 |                                                                                                                        |

| uP set default H/W configuration                                                                                                                                           | clock_control1            | 0x0a |                                                                                                                        |

|                                                                                                                                                                            | clock_delay_control2      | 0x05 |                                                                                                                        |

|                                                                                                                                                                            | clock_delay_sel           | 0x80 |                                                                                                                        |

|                                                                                                                                                                            | i2s_word_byte             | 0x22 |                                                                                                                        |

|                                                                                                                                                                            | i2c_mode_byte             | 0x22 | IW/OW: 24 bit<br>IM/OM: I <sup>2</sup> S                                                                               |

|                                                                                                                                                                            | sap_en                    | 1    |                                                                                                                        |

| uP flush uP instruction RAM                                                                                                                                                | mem_sel                   | 0x02 | Clear uP instruction RAM (16384 byte)                                                                                  |

| uP flush DSP instruction RAM                                                                                                                                               | mem_sel                   | 0x01 | Clear DSP instruction RAM (3328 W)                                                                                     |

| uP flush DSP lower coefficient/data RAM                                                                                                                                    | mem_sel                   | 0x00 | Clear DSP lower coefficient RAM (1024 W) and data<br>(48 bit) RAM (768 W)                                              |

| Enable I <sup>2</sup> C master interface                                                                                                                                   |                           |      | Setup I <sup>2</sup> C master interface mode (enable interrupt 10)                                                     |

| EEPROM load                                                                                                                                                                |                           |      |                                                                                                                        |

| Disable I <sup>2</sup> C master mode and enable slave interface                                                                                                            | i2c_ms_ctl                | 0    | Switch control MUX to slave I <sup>2</sup> C port                                                                      |