Click here to ask an associate for production status of specific part numbers.

## 5.5V to 60V, 6A Current-Limiter with OV, UV, Reverse Protection, and Power Limit

## MAX17526A/MAX17526B/ MAX17526C

#### **General Description**

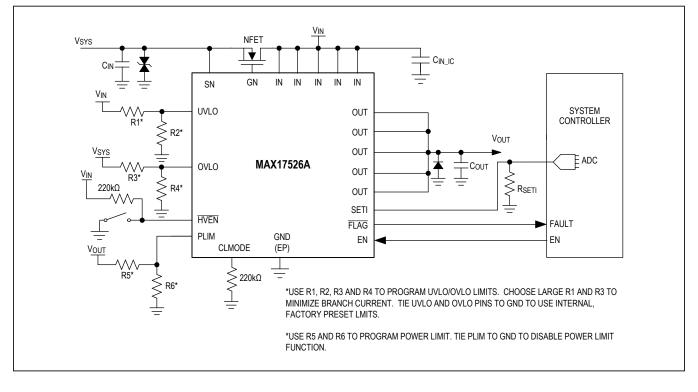

The Olympus series of ICs are the industry's smallest and robust integrated system protection solutions. The MAX17526A adjustable power limiter offers a unique feature to limit power drawn from supplies or delivered to loads, amongst a host of protection features. These protection features include adjustable input overvoltage and undervoltage protection, positive and negative input voltage protection, overcurrent protection, reverse-current protection and overtemperature protection. The device features a built-in low  $R_{ON}$  (30m $\Omega$  typ) NFET, and an integrated gate drive for an optional external NFET.

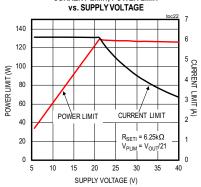

The device highlights a power limit feature that allows programmed reduction in current limit, as an inverse function of an external voltage. Input or output power limit is achieved by limiting the current through the device as a function of input or output voltages.

Input undervoltage protection level is adjustable between 5.5V and 24V, and input overvoltage protection level is adjustable between 6V and 40V. The input undervoltage lockout (UVLO) threshold and overvoltage lockout (OVLO) threshold are adjusted using external resistors. The device offers a factory preset internal UVLO and OVLO thresholds at 12.4V (typ) and 36.2V (typ) respectively. The factory preset levels can be invoked by connecting the UVLO and/or the OVLO pins to GND.

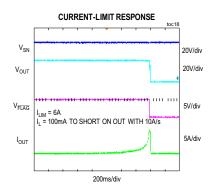

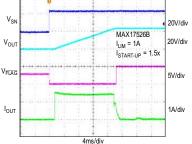

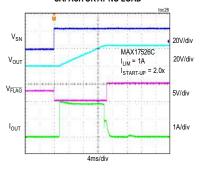

The device features programmable current limit protection up to 6A. Current limit threshold is programmed by connecting a resistor from the SETI pin to GND. When the device current reaches the programmed threshold, the controller inside the device prevents further increase in current by modulating the internal NFET resistance. The device offers three different behavioral modes under current limited operation: Continuous mode, Autoretry mode, and Latch-off mode. The continuous current limit feature offers control of inrush current at startup while charging high capacitances at the output side. Two additional part options that feature a dual-stage current-limit mode, in which the current is continuously limited to 1.5x (MAX17526B) and 2.0x (MAX17526C), the programmed limits, are available upon request. The power limit feature is disabled in the MAX17526B/C part options. The voltage appearing on the SETI pin is proportional to the instantaneous current flowing through the device, and can be read by the supervisory system.

MAX17526A also offers reverse-current protection and input reverse voltage polarity protection when deployed with an external NFET, and built-in overtemperature protection. It is available in a 20-pin 5mm x 5mm TQFN-EP package. The device operates over -40°C to +125°C extended temperature range.

#### **Benefits and Features**

- Robust Protection Reduces System Downtime

- Wide Input-Supply Range: +5.5V to +60V

- Active Power Limit to Protect Supply or Load (MAX17526A)

- Programmable Input Overvoltage Setting up to 40V

- Negative Input Fault Tolerant (with External NFET)

- Reverse Current Protection (with External NFET)

- Low R<sub>ON</sub> Internal NFET (30mΩ typ)

- Dual-Stage Current Limiting

- 1.0x Startup Current (MAX17526A)

- 1.5x Startup Current (MAX17526B)

- 2.0x Startup Current (MAX17526C)

- Fast Startup and Brownout Recovery

- Continuous Current-Limit During Startup

- Thermal Foldback Current-Limit

- Flexible Design to Maximize Reuse and Minimize Requalification

- · Adjustable UVLO and OVLO Thresholds

- Programmable Forward-Current Limit: 0.2A to 0.6A with ±10% Accuracy and 0.6A to 6.0A with ±8.5% Accuracy Over Full Temperature Range

- Programmable Overcurrent Response: Continuous, Autoretry, and Latch-Off Modes

- Logic Level and High-Voltage Enable Inputs (EN and HVEN)

- Protected External NFET Gate Drive

- Reduced Solution Footprint

- 20-Pin 5mm x 5mm TQFN-EP Package

- Integrated NFET for Common-Use Protection Requirements

#### **Applications**

- Industrial Power Distribution Systems

- Control and Automation

- Motion Control Drives

- Human Machine Interfaces

Ordering Information appears at end of data sheet.

19-100358; Rev 4; 9/22

## 5.5V to 60V, 6A Current-Limiter with OV, UV, Reverse Protection, and Power Limit

### **Typical Operating Circuit**

## 5.5V to 60V, 6A Current-Limiter with OV, UV, Reverse Protection, and Power Limit

#### **Absolute Maximum Ratings**

| IN to GND (Note 1)            | 0.3V to +64V                            |

|-------------------------------|-----------------------------------------|

| OUT to GND                    | 0.3V to V <sub>IN</sub> + 0.3V          |

| HVEN to GND (Note 1)          | 0.3V to V <sub>IN</sub> + 0.3V          |

| SN to GND                     | 62V to +64V                             |

| GN to GND                     | (SN - 0.3V) to (SN + 6V)                |

| UVLO, OVLO, PLIM, FLAG to GND | 0.3V to (V <sub>IN</sub> + 0.3V)        |

| EN, CLMODE to GND             | 0.3V to 6V                              |

| SETI to GND0                  | .3V to min (V <sub>IN</sub> + 0.3V, 6V) |

| IN Current (DC)                                       | 6.51A          |

|-------------------------------------------------------|----------------|

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ , | TQFN derate    |

| 34.5mW/°C above +70°C.)                               | 2758mW         |

| Operating Temperature Range                           | 40°C to +125°C |

| Junction Temperature                                  | 40°C to +150°C |

| Storage Temperature Range                             | 65°C to +150°C |

| Lead Temperature (soldering, 10s)                     | +300°C         |

| Soldering Temperature (reflow)                        | +260°C         |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Note 1: An external NFET or diode is required to achieve negative input protection.

#### **Package Information**

| PACKAGE TYPE: 20-PIN TQFN             |                |  |  |  |

|---------------------------------------|----------------|--|--|--|

| Package Code                          | T2055+6C       |  |  |  |

| Outline Number                        | <u>21-0140</u> |  |  |  |

| Land Pattern Number                   | <u>90-0010</u> |  |  |  |

| THERMAL RESISTANCE, FOUR-LAYER BOARD: |                |  |  |  |

| Junction to Ambient ( $\theta_{JA}$ ) | 29°C/W         |  |  |  |

| Junction to Case $(\theta_{JC})$      | 2°C/W          |  |  |  |

For the latest package outline information and land patterns (footprints), go to <u>www.maximintegrated.com/packages</u>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to www.maximintegrated.com/thermal-tutorial.

# 5.5V to 60V, 6A Current-Limiter with OV, UV, Reverse Protection, and Power Limit

## **Electrical Characteristics**

$(V_{IN} = 5.5V \text{ to } 60V, T_A = -40^{\circ}C \text{ to } +125^{\circ}C, \text{ unless otherwise noted. Typical values are at } V_{IN} = 24V, T_A = +25^{\circ}C)$  (Note 2)

| PARAMETER                           | SYMBOL                | CONDITIONS                                                                             | MIN  | TYP  | MAX  | UNITS |  |

|-------------------------------------|-----------------------|----------------------------------------------------------------------------------------|------|------|------|-------|--|

| POWER SUPPLY                        |                       | ·                                                                                      |      |      |      |       |  |

| IN Voltage Range                    | V <sub>IN</sub>       |                                                                                        | 5.5  |      | 60.0 | V     |  |

| 0                                   |                       | $V_{EN} = 0V, V_{\overline{HVEN}} = 5V, V_{IN} = V_{SN} = 24V$                         |      | 9.9  | 17.0 |       |  |

| Shutdown Input Current              | ISHDN                 | $V_{EN} = 0V, V_{\overline{HVEN}} = 5V, V_{IN} = V_{SN} = 40V$                         |      | 16   | 28   | - μΑ  |  |

| Shutdown Output Current             | I <sub>OFF</sub>      | $V_{EN} = 0V, V_{\overline{HVEN}} = 5V, V_{SN} = V_{IN} = V_{OUT} = 40V$               |      | 80   | 170  | μA    |  |

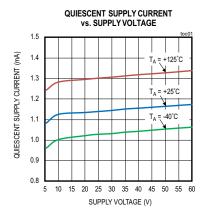

| Supply Current                      | I <sub>IN</sub>       | $V_{SN} = V_{IN} = V_{OUT} = 24V, V_{HVEN} = 0V$                                       |      | 1.26 | 1.90 | mA    |  |

| UVLO, OVLO                          |                       |                                                                                        |      |      |      |       |  |

| Internal Undervoltage-Trip          |                       | V <sub>IN</sub> rising, UVLO connected to GND                                          | 11.9 | 12.4 | 13.0 |       |  |

| Level                               | V <sub>UVLO</sub>     | V <sub>IN</sub> falling, UVLO connected to GND                                         | 11.5 | 12.0 | 12.5 | - V   |  |

| UVLO Threshold Hysteresis           |                       |                                                                                        |      | 3    |      | %     |  |

|                                     |                       | V <sub>SN</sub> rising, OVLO connected to GND                                          | 34.7 | 36.2 | 37.6 |       |  |

| Internal Overvoltage-Trip Level     | V <sub>OVLO</sub>     | V <sub>SN</sub> falling, OVLO connected to GND                                         | 32.2 | 34.1 | 35.8 | - V   |  |

| OVLO Threshold Hysteresis           |                       |                                                                                        |      | 6    |      | %     |  |

| Undervoltage-Trip Level on          |                       | V <sub>OUT</sub> rising                                                                | 12.2 | 12.8 | 13.4 |       |  |

| Output                              | VUVLO_OUT             | V <sub>OUT</sub> falling, UVLO trip point                                              | 11.9 | 12.4 | 12.9 | - V   |  |

|                                     | V <sub>SET_UVLO</sub> | UVLO rising                                                                            | 1.20 | 1.26 | 1.33 | - V   |  |

| External UVLO Set Voltage           |                       | UVLO falling                                                                           | 1.18 | 1.22 | 1.27 |       |  |

| External UVLO Select Voltage        | V <sub>UVLO SEL</sub> |                                                                                        | 0.15 | 0.38 | 0.50 | V     |  |

| External UVLO Leakage<br>Current    | IUVLO_LEAK            |                                                                                        | -250 |      | +250 | nA    |  |

|                                     | V <sub>SET_OVLO</sub> | OVLO rising                                                                            | 1.18 | 1.22 | 1.27 | - V   |  |

| External OVLO Set Voltage           |                       | OVLO falling                                                                           | 1.09 | 1.15 | 1.20 |       |  |

| External OVLO Select Voltage        | V <sub>OVLO_SEL</sub> |                                                                                        | 0.15 | 0.38 | 0.50 | V     |  |

| External OVLO Leakage<br>Current    | IOVLO_LEAK            |                                                                                        | -250 |      | +250 | nA    |  |

| External UVLO Adjustment<br>Range   |                       | (Note 3)                                                                               | 5.5  |      | 24.0 | V     |  |

| External OVLO Adjustment<br>Range   |                       | (Note 3)                                                                               | 6    |      | 40   | V     |  |

| GN, SN                              |                       |                                                                                        |      |      |      |       |  |

| External NFET Gate Drive<br>Voltage | V <sub>GN-SN</sub>    | V <sub>IN</sub> < 8V, V <sub>EN</sub> = 5V, no reverse<br>condition                    | 3.9  | 4.2  | 5.5  | V     |  |

| vollaye                             |                       | V <sub>EN</sub> = 5V, no reverse condition                                             | 4.98 | 5.25 | 5.60 |       |  |

| Gate Active Pullup Current          |                       | $V_{EN}$ = 5V, $V_{GN}$ = $V_{SN}$ , no reverse condition                              | 9    | 18   | 28   | μA    |  |

| Gate Active Pulldown<br>Resistance  |                       | V <sub>EN</sub> = 5V, reverse condition                                                |      | 140  |      | mΩ    |  |

| Shutdown Gate Pulldown              |                       | V <sub>EN</sub> = 0V, V <sub>HVEN</sub> = 5V, V <sub>GN</sub> - V <sub>SN</sub> = 1.5V |      | 2.7  | 6.1  | kΩ    |  |

| Resistance                          |                       | $V_{\rm EN} = 0V, V_{\rm HVEN} = 5V, V_{\rm GN} - V_{\rm SN} = 0.5V$                   |      | 3.9  | 8.0  | ΜΩ    |  |

# 5.5V to 60V, 6A Current-Limiter with OV, UV, Reverse Protection, and Power Limit

### **Electrical Characteristics (continued)**

$(V_{IN} = 5.5V \text{ to } 60V, T_A = -40^{\circ}C \text{ to } +125^{\circ}C, \text{ unless otherwise noted. Typical values are at } V_{IN} = 24V, T_A = +25^{\circ}C)$  (Note 2)

| PARAMETER                                         | SYMBOL                  | CONDITIONS                                                                                          | MIN                     | ТҮР   | MAX                             | UNITS |  |

|---------------------------------------------------|-------------------------|-----------------------------------------------------------------------------------------------------|-------------------------|-------|---------------------------------|-------|--|

| INTERNAL FETs                                     |                         |                                                                                                     |                         |       |                                 |       |  |

| Internal FETs On-Resistance                       | R <sub>ON</sub>         | I <sub>LOAD</sub> = 100mA, V <sub>IN</sub> ≥ 10V, T <sub>A</sub> = +25°C                            |                         | 30    | 42                              | mΩ    |  |

| Current-Limit Adjustment<br>Range                 | ILIM                    |                                                                                                     | 0.2                     |       | 6.0                             | A     |  |

|                                                   |                         | $0.6A \le I_{LIM} \le 6A (T_A = +25^{\circ}C), V_{PLIM} < V_{PLIM}$ TH                              | -6                      |       | +6                              |       |  |

| Current-Limit Accuracy                            | ILIM_ACC                |                                                                                                     | -10                     |       | +10                             | %     |  |

|                                                   |                         | $0.6A \le I_{LIM} \le 6A, V_{PLIM} < V_{PLIM}_{TH}$                                                 | -8.5                    |       | +8.5                            | 1     |  |

| Overcurrent Protection<br>Threshold               | I <sub>OCP</sub>        | (Note 8)                                                                                            | 15.0                    | 24.0  | 34.5                            | A     |  |

| FLAG Assertion Drop-Voltage<br>Threshold          | V <sub>FA</sub>         | Increase in (V <sub>IN</sub> - V <sub>OUT</sub> ) drop until<br>FLAG asserts, V <sub>IN</sub> = 24V |                         | 490   |                                 | mV    |  |

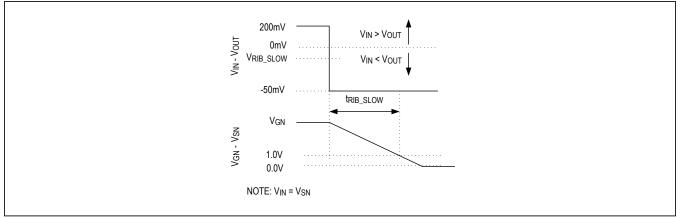

| Slow Reverse-Current-Blocking Threshold           | V <sub>RIB_SLOW</sub>   | V <sub>IN</sub> - V <sub>OUT</sub> , falling                                                        | -0.5                    | -5.4  | -10.5                           | mV    |  |

| Slow Reverse-Current-Blocking Response Time       | <sup>t</sup> RIB_SLOW   | (Note 4)                                                                                            |                         | 17    | 30                              | μs    |  |

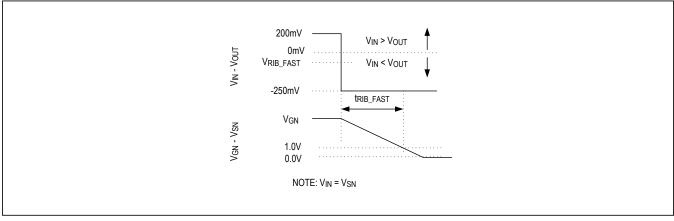

| Fast Reverse-Current-Blocking<br>Threshold        | V <sub>RIB_FAST</sub>   | V <sub>IN</sub> - V <sub>OUT</sub> , falling                                                        | -78                     | -98   | -118                            | mV    |  |

| Fast Reverse-Current-Blocking       Response Time |                         | (Note 5, Note 8), C <sub>GS</sub> = 10nF                                                            |                         | 108   | 135                             | ns    |  |

| Reverse-Current-Blocking<br>Rising Threshold      | V <sub>RIB_RISING</sub> | V <sub>SN</sub> - V <sub>OUT</sub> , rising                                                         | 65                      | 100   | 135                             | mV    |  |

| Reverse Output Current                            | IOUT_REV                | $V_{SN}$ = 0V, $V_{OUT}$ = 24V, IN floating                                                         |                         | 3.20  | 5.11                            | mA    |  |

| PLIM                                              |                         |                                                                                                     |                         |       |                                 |       |  |

| PLIM Limit Threshold Voltage                      | V <sub>PLIM_TH</sub>    |                                                                                                     | 0.867                   | 1.009 | 1.151                           | V     |  |

| PLIM Limit Operation Range                        |                         |                                                                                                     | V <sub>PLIM</sub><br>TH |       | 3 x<br>V <sub>PLIM_</sub><br>TH |       |  |

| SETI                                              |                         |                                                                                                     |                         |       |                                 |       |  |

| R <sub>SETI</sub> x I <sub>LIM</sub>              | V <sub>RI</sub>         | V <sub>PLIM</sub> < V <sub>PLIM_TH</sub>                                                            |                         | 1.5   | _                               | V     |  |

| Current-Mirror Output Ratio                       | CIRATIO                 |                                                                                                     |                         | 25000 |                                 | A/A   |  |

| LOGIC INPUT (HVEN, CLMODI                         | E, EN)                  |                                                                                                     |                         |       |                                 |       |  |

| HVEN Threshold Voltage                            | \/ <del></del>          | HVEN rising                                                                                         | 1.05                    | 2.00  | 3.30                            | v     |  |

| TVEN THESHOLD VOILage                             | V <sub>HVEN</sub> _TH   | HVEN falling                                                                                        | 1.0                     | 1.9   | 2.8                             | V     |  |

| HVEN Threshold Hysteresis                         |                         |                                                                                                     |                         | 5     |                                 | %     |  |

| HVEN Input Leakage Current                        | IHVEN_LEAK              | V <sub>HVEN</sub> = 60V                                                                             |                         | 51    | 72                              | μA    |  |

| EN Input-Logic High                               | V <sub>IH</sub>         |                                                                                                     | 1.4                     |       |                                 | V     |  |

| EN Input-Logic Low                                | VIL                     |                                                                                                     |                         |       | 0.4                             | V     |  |

| EN Input Leakage Current                          | I <sub>EN_LEAK</sub>    | V <sub>EN</sub> = 0V, 5V                                                                            | -1                      |       | +1                              | μA    |  |

## 5.5V to 60V, 6A Current-Limiter with OV, UV, Reverse Protection, and Power Limit

### **Electrical Characteristics (continued)**

$(V_{IN} = 5.5V \text{ to } 60V, T_A = -40^{\circ}C \text{ to } +125^{\circ}C, \text{ unless otherwise noted. Typical values are at } V_{IN} = 24V, T_A = +25^{\circ}C)$  (Note 2)

| PARAMETER                                    | PARAMETER SYMBOL CONDITIONS |                                                                                                                                              | MIN  | TYP  | MAX  | UNITS |

|----------------------------------------------|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| CLMODE Input-Logic High                      | V <sub>CLMODE_IH</sub>      |                                                                                                                                              | 3.59 | 4.00 | 4.52 | V     |

| CLMODE Input-Logic Low                       | VCLMODE_IL                  |                                                                                                                                              | 0.49 | 0.78 | 1.01 | V     |

| CLMODE Pullup Current                        |                             |                                                                                                                                              | 5.3  | 10.0 | 14.6 | μA    |

| LOGIC OUTPUT (FLAG)                          |                             |                                                                                                                                              |      |      |      |       |

| Logic-Low Voltage                            |                             | I <sub>SINK</sub> = 1mA                                                                                                                      |      |      | 0.4  | V     |

| Input Leakage Current                        |                             | V <sub>IN</sub> = 5.5V, FLAG open drain off                                                                                                  |      |      | 1    | μA    |

| FLAG Protection Current                      |                             | FLAG open drain on                                                                                                                           | 4    |      |      | mA    |

| TIMING CHARACTERISTICS (I                    | NOTE 6)                     |                                                                                                                                              |      |      |      |       |

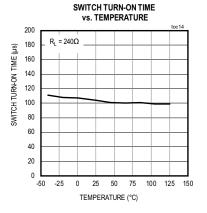

| Switch Turn-On Time                          | t <sub>ON</sub>             | $V_{IN}$ = 24V, switch OFF to ON, $R_{LOAD}$ = 240 $\Omega$ , $I_{LIM}$ = 1A, $C_{OUT}$ = 4.7 $\mu$ F, $V_{OUT}$ from 20% to 80% of $V_{IN}$ |      | 68   |      | μs    |

| Fault Recovery nFET Turn-On<br>Time          | tON_NFET                    | Turn-on delay after fault timers expired                                                                                                     |      | 200  | 500  | μs    |

| Fault Recovery External NFET<br>Turn-On Time | ton_exnfet                  | V <sub>OUT</sub> > V <sub>UVLO_OUT</sub> , turn-on delay of<br>external NFET after fault timers expired                                      | 1.09 | 1.20 | 1.32 | ms    |

| OVP Switch Response Time                     | t <sub>OVP_RES</sub>        |                                                                                                                                              |      | 3    |      | μs    |

| Overcurrent Protection<br>Response time      | t <sub>OCP_RES</sub>        | $I_{LIM}$ = 5A, $I_{OUT}$ step from 3A to 30A.<br>Time to turn the switch off.                                                               | A. 3 |      |      | μs    |

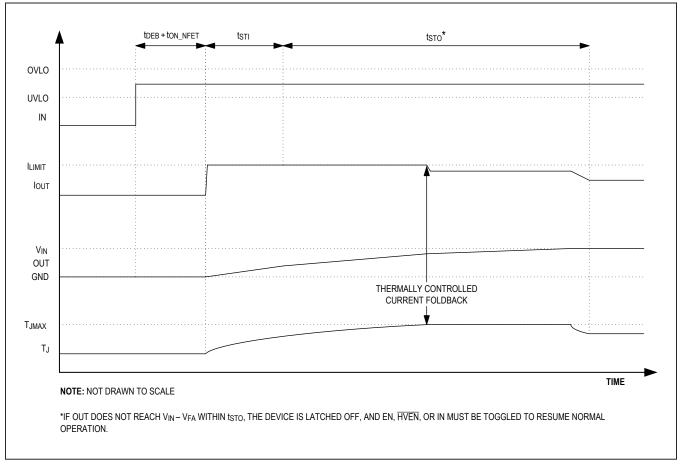

| Startup Timeout                              | t <sub>STO</sub>            | Initial start current-limit foldback timeout (Figure 5)                                                                                      | 1090 | 1200 | 1320 | ms    |

| Startup Initial Time                         | t <sub>STI</sub>            | (Figure 5)                                                                                                                                   | 21.8 | 24.0 | 26.4 | ms    |

| IN Debounce Time                             | t <sub>DEB</sub>            | Additional turn-on delay if V <sub>OUT</sub> <<br>V <sub>UVLO_OUT</sub> , see Figures 5–8                                                    | 1.09 | 1.20 | 1.32 | ms    |

| Blanking Time                                | t <sub>BLANK</sub>          | Figures 7 and 8                                                                                                                              | 21.8 | 24.0 | 26.4 | ms    |

| Autoretry Time                               | t <sub>RETRY</sub>          | Figure 7 (Note 7)                                                                                                                            | 654  | 720  | 792  | ms    |

| THERMAL PROTECTION                           |                             |                                                                                                                                              |      |      |      |       |

| Thermal Foldback                             | T <sub>J(FB)</sub>          |                                                                                                                                              |      | 150  |      | °C    |

| Thermal Shutdown                             | TJ                          |                                                                                                                                              |      | 165  |      | °C    |

| Thermal Shutdown Hysteresis                  | T <sub>J(HYS)</sub>         |                                                                                                                                              |      | 10   |      | °C    |

**Note 2:** All devices are 100% production-tested at T<sub>A</sub> = +25°C. Limits over the operating-temperature range are guaranteed by design; not production tested.

Note 3: Not production-tested, user-adjustable. See the Overvoltage Lockout (OVLO) and Undervoltage Lockout (UVLO) sections.

Note 4: Time from  $V_{IN}$  -  $V_{OUT}$  voltage transition from 200mV to -50mV until GN pin voltage falls to  $V_{SN}$  + 1V (Figure 1).

Note 5: Time from V<sub>IN</sub> - V<sub>OUT</sub> voltage transition from 200mV to -250mV until GN pin voltage falls to V<sub>SN</sub> + 1V (Figure 2).

Note 6: All timing is measured using 20% and 80% levels, unless otherwise specified.

**Note 7:** The autoretry time-to-blanking time ratio is fixed and is equal to 30.

Note 8: Guaranteed by design, not production tested.

## 5.5V to 60V, 6A Current-Limiter with OV, UV, Reverse Protection, and Power Limit

Figure 1. Slow Reverse-Current-Blocking Response Time

Figure 2. Fast Reverse-Current-Blocking Response Time

## 5.5V to 60V, 6A Current-Limiter with OV, UV, Reverse Protection, and Power Limit

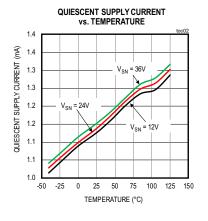

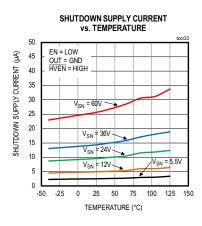

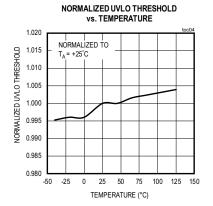

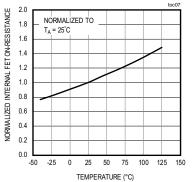

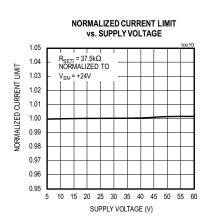

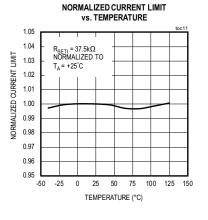

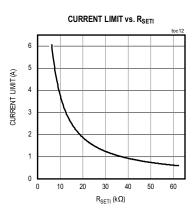

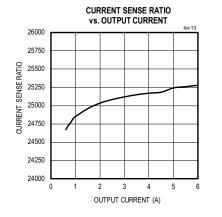

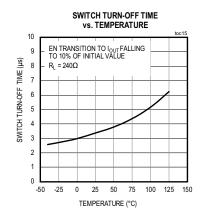

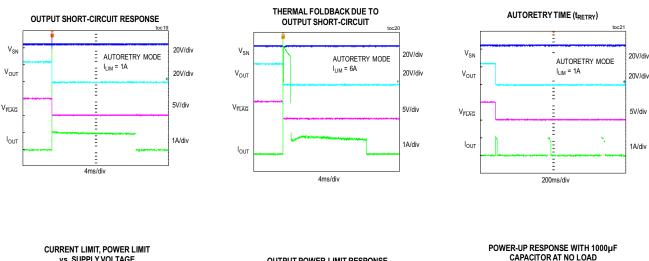

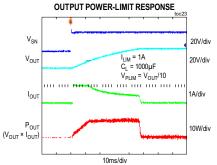

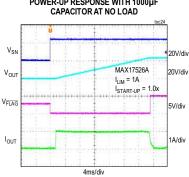

### **Typical Operating Characteristics**

(V<sub>IN</sub> = 24V, C<sub>IN</sub> = 1 $\mu$ F, C<sub>OUT</sub> = 1 $\mu$ F, T<sub>A</sub> = +25°C, unless otherwise noted.)

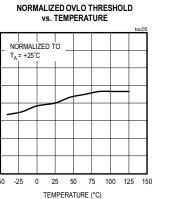

NORMALIZED INTERNAL FET ON-RESISTANCE vs. TEMPERATURE

vs. TEMPERATURE 1.020 NORMALIZED TO 1.015 T<sub>A</sub> = +25°C NORMALIZED OVLO THRESHOLD 1.010 1.005 1.000 0.995 0.990 0.985 0.980 -50 0 100 125 150

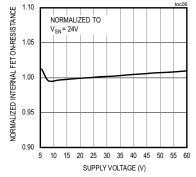

NORMALIZED INTERNAL FET ON-RESISTANCE vs. SUPPLY VOLTAGE

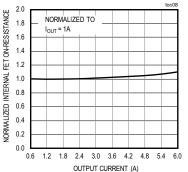

NORMALIZED INTERNAL FET **ON-RESISTANCE vs. OUTPUT CURRENT**

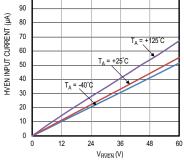

HVEN INPUT CURRENT vs. V<sub>HVEN</sub>

100

## 5.5V to 60V, 6A Current-Limiter with OV, UV, Reverse Protection, and Power Limit

### **Typical Operating Characteristics (continued)**

(V<sub>IN</sub> = 24V, C<sub>IN</sub> = 1 $\mu$ F, C<sub>OUT</sub> = 1 $\mu$ F, T<sub>A</sub> = +25°C, unless otherwise noted.)

## 5.5V to 60V, 6A Current-Limiter with OV, UV, Reverse Protection, and Power Limit

### **Typical Operating Characteristics (continued)**

(V<sub>IN</sub> = 24V, C<sub>IN</sub> = 1 $\mu$ F, C<sub>OUT</sub> = 1 $\mu$ F, T<sub>A</sub> = +25°C, unless otherwise noted.)

## 5.5V to 60V, 6A Current-Limiter with OV, UV, Reverse Protection, and Power Limit

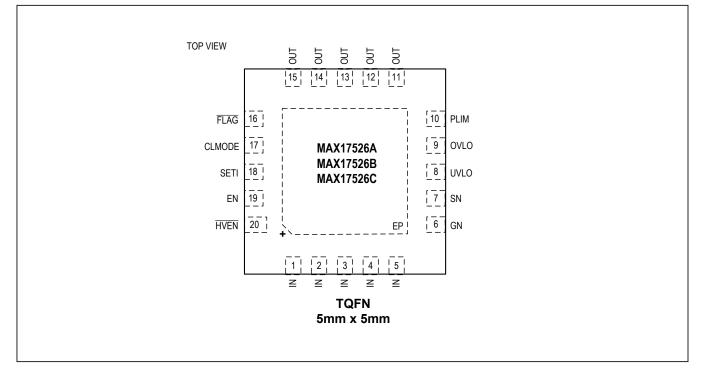

### **Pin Configuration**

# 5.5V to 60V, 6A Current-Limiter with OV, UV, Reverse Protection, and Power Limit

## **Pin Description**

| PIN   | NAME   | FUNCTION                                                                                                                                                                                                                                                                                                                                    |

|-------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1–5   | IN     | Input Pins. Bypass IN to GND with a 1µF cermic capacitor. For Hot Plug-In applications, see the <i>Applications Information</i> section.                                                                                                                                                                                                    |

| 6     | GN     | Gate Driver Output for External NFET.                                                                                                                                                                                                                                                                                                       |

| 7     | SN     | Return for External NFET Gate Drive and Input Voltage Sense Pin. Connect to source of external NFET as shown in the <i>Typical Operating Circuit</i> . Bypass SN to GND with a 4.7µF capacitor. SN serves as the undervoltage/overvoltage sensed input when preprogrammed UVLO/OVLO is used. Connect SN to IN if external NFET is not used. |

| 8     | UVLO   | UVLO Adjustment Pin. Connect UVLO to GND to use the default internal UVLO threshold. Connect resis-<br>tive potential divider from SN/IN to GND to set the UVLO threshold externally and override the preset<br>internal UVLO threshold.                                                                                                    |

| 9     | OVLO   | OVLO Adjustment Pin. Connect OVLO to GND to use the default internal OVLO threshold. Connect re-<br>sistive potential divider from SN/IN to GND to set the OVLO threshold externally and override the preset<br>internal OVLO threshold.                                                                                                    |

| 10    | PLIM   | Power Limit Adjustment Pin. Connect PLIM to an external resistive potential divider to define a threshold at which the power limit feature starts reducing the current-limit threshold. Connect PLIM to GND to disable this feature and have the current-limit set only by the resistor placed on SETI.                                     |

| 11-15 | OUT    | Output Pins. For a long output cable or inductive load, see the <u>Applications Information</u> section.                                                                                                                                                                                                                                    |

| 16    | FLAG   | <ul> <li>Open-Drain, Fault Indicator Output. FLAG goes low when:</li> <li>The (V<sub>IN</sub> - V<sub>OUT</sub>) voltage exceeds V<sub>FA</sub>.</li> <li>Thermal shutdown is active.</li> <li>Input voltage falls below UVLO threshold or rises above OVLO threshold.</li> <li>R<sub>SETI</sub> is less than 3.2kΩ.</li> </ul>             |

| 17    | CLMODE | Current-Limit Mode Selector Pin. Leave CLMODE unconnected for Continuous mode. Connect CLMODE to GND for Autoretry mode. Connect a $220k\Omega$ resistor between CLMODE and GND for Latch-off mode.                                                                                                                                         |

| 18    | SETI   | Overcurrent Limit Adjustment Pin and Current Monitoring Output. Connect a resistor from SETI to GND to set overcurrent limit. See the <u>Setting the Current-Limit Threshold</u> section. Do not connect more than 30pF to SETI.                                                                                                            |

| 19    | EN     | Active-High Enable Input. See <u>Table 1</u> .                                                                                                                                                                                                                                                                                              |

| 20    | HVEN   | 60V Capable Active-Low Enable Input. See <u>Table 1</u> .                                                                                                                                                                                                                                                                                   |

| -     | GND/EP | Ground/Exposed Pad. Connect GND/EP to a large GND plane with several thermal vias for best thermal performance. Refer to the MAX17526A EV kit data sheet for a reference layout design.                                                                                                                                                     |

## 5.5V to 60V, 6A Current-Limiter with OV, UV, Reverse Protection, and Power Limit

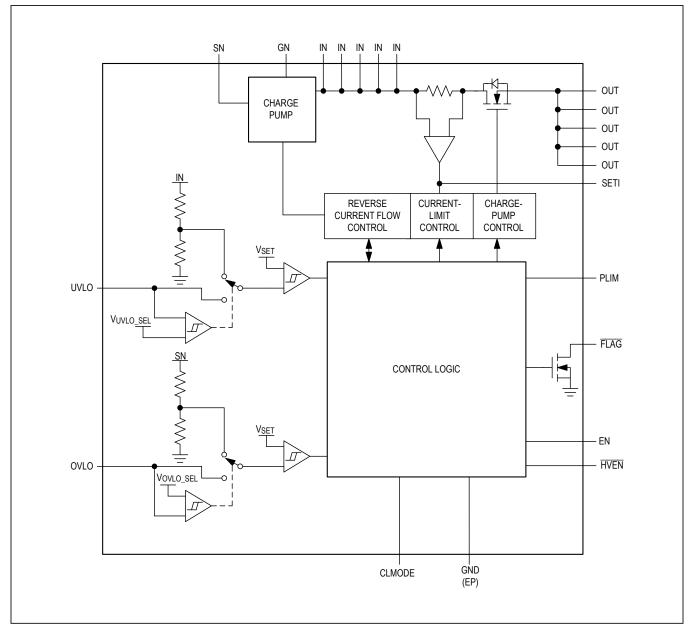

### **Functional Diagrams**

#### **Detailed Description**

The MAX17526A offers adjustable protection boundaries for systems against input voltage faults, and overcurrent fault, in addition to a programmable power limiting function. Input voltage faults (with positive polarity) are protected up to +60V, by an internal NFET featuring low ON-resistance ( $30m\Omega$  typ). The device features fixed or programmable overvoltage lockout (OVLO) and undervoltage lockout (UVLO) thresholds by using internal or external voltage-dividers. Factory preset internal fixed thresholds may be invoked by connecting the OVLO and/ or UVLO pin(s) to GND. Input undervoltage protection can be programmed between 5.5V and 24V, while the overvoltage protection can be independently programmed between 6V and 40V.

Input reverse polarity protection is realized using an external NFET that is controlled by MAX17526A. The magnitude of reverse polarity voltage protection is dependent on the operating load bus voltage ( $V_{OUT}$ ) and the voltage blocking capability of the external NFET. Example: for protection down to -55V input range with  $V_{OUT}$  = 30V, an external NFET rated at 85V is needed. The external NFET is also needed for the optional reverse-current protection. If reverse polarity protection and reverse-current protection are not needed, SN must be connected to IN and GN must be left floating.

The current-limit of the device is programmed by connecting a resistor from the SETI pin to GND. The current limit can be programmed from 0.2A to 6.0A. When the current through the device reaches or exceeds the set current limit, the resistance of the internal NFET is modulated to limit the current. The device offers three current limit behavioral modes: Continuous, Auto-retry, and Latch-off modes.

The SETI pin presents a current proportional to the device current, under normal operation. Together with the current limit program resistor (between SETI and GND), the SETI pin presents a voltage that is proportional to the device current. This voltage may be read by a monitoring system for recording instantaneous current of the device.

Power limit function is realized either at the input supply side or output load side, by sampling the input or output voltage, through a potential divider connecting to the PLIM pin. The power limit feature reduces the programmed current limit when the external voltage increases above the programmed threshold.

## 5.5V to 60V, 6A Current-Limiter with OV, UV, Reverse Protection, and Power Limit

The device can be turned On or Off through two independent enable inputs, EN and  $\overline{\text{HVEN}}$ , by a master supervisory system. This allows the master supervisory system to Turn On or Off power delivery to connected loads.

The device offers a status announcement signal ( $\overline{FLAG}$ ) to indicate operational and fault signals.  $\overline{FLAG}$  is an open drain pin, and requires an external pullup resistor to the appropriate system interface voltage. The device also offers internal thermal shutdown protection against excessive power dissipation.

#### Undervoltage Lockout (UVLO)

The device has a 12.4V (typ) preset UVLO threshold on the IN pin when the voltage at the UVLO pin is less than the external UVLO select threshold ( $V_{UVLO\_SEL}$ ). Connect the UVLO pin to GND to select the preset UVLO threshold. If the voltage at the UVLO pin rises above  $V_{UVLO\_SEL}$ , the device enters adjustable UVLO mode. The device has a UVLO adjustment range from 5.5V to 24V. Connect an external resistive potential divider to the UVLO pin as shown in the *Typical Operating Circuit* to adjust the UVLO threshold voltage. Use the following equation to adjust the UVLO threshold. The recommended value of R1 is 2.2MΩ.

$$V_{\text{UVLO}} = V_{\text{SET}} \times \left[1 + \frac{\text{R1}}{\text{R2}}\right]$$

where  $V_{SET}$  = 1.22V.

Alternatively, R2 can be calculated using the following equation:

$$R2 = \frac{R1}{\left(\frac{V_{UVLO}}{V_{SET}} - 1\right)}$$

When the voltage on the UVLO pin is below V<sub>SET</sub>, the internal NFET remains turned Off and  $\overline{FLAG}$  is asserted. When the UVLO condition is removed, the device takes input debounce time (t<sub>DEB</sub>) to start the switch turn-on process if V<sub>OUT</sub> is below the V<sub>UVLO\_OUT</sub> threshold. The internal NFET is turned on after fault recovery internal NFET turn-on time (t<sub>ON\_NFET</sub>), and the external NFET is turned on after fault recovery external NFET turn-on time (t<sub>ON\_EXTNFET</sub>) and FLAG is deasserted.

## 5.5V to 60V, 6A Current-Limiter with OV, UV, Reverse Protection, and Power Limit

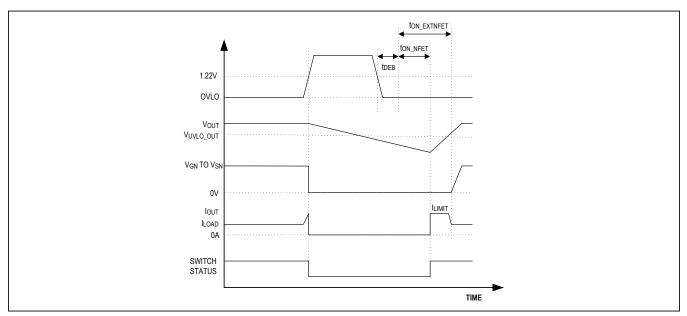

#### **Overvoltage Lockout (OVLO)**

The device has a 36.2V (typ) preset OVLO threshold on the SN pin when the voltage at the OVLO pin is less than the external OVLO select threshold (V<sub>OVLO\_SEL</sub>). Connect the OVLO pin to GND to select the preset OVLO threshold. If the voltage at the OVLO pin rises above V<sub>OVLO\_SEL</sub>, the device enters adjustable OVLO mode. The device has an OVLO adjustment range from 6V to 40V. Connect an external resistive potential divider to the OVLO pin as shown in the <u>Typical Operating Circuit</u> to adjust the OVLO threshold voltage. Use the following equation to adjust the OVLO threshold. The recommended value of R3 is 2.2MΩ.

$$V_{OVLO} = V_{SET} \times \left[1 + \frac{R3}{R4}\right]$$

where  $V_{SET} = 1.22V$ .

Alternatively, R4 can be calculated using the following equation:

$$R4 = \frac{R3}{\left(\frac{V_{OVLO}}{V_{SET}} - 1\right)}$$

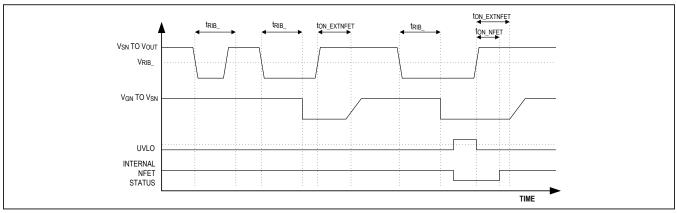

The OVLO reference voltage (V<sub>SET</sub>) is set at 1.22V. If the voltage at the OVLO pin exceeds V<sub>SET</sub>, the switch is turned off and FLAG is asserted. When the OVLO condition is removed, the device takes input debounce time (t<sub>DEB</sub>) to start the switch turn-on process if V<sub>OUT</sub> is below the V<sub>UVLO\_OUT</sub> threshold. The internal NFET is turned on after fault recovery internal NFET turn-on time (t<sub>ON\_NFET</sub>), and the external NFET is turned on after fault recovery external NFET is turned on after fault recovery external NFET turn-on time (t<sub>ON\_EXTNFET</sub>) and the FLAG is deasserted. Figure 3 depicts typical behavior in overvoltage conditions.

Figure 3. Overvoltage-Fault Timing Diagram

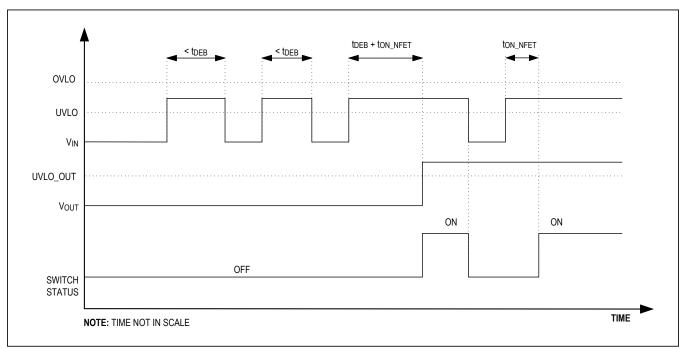

#### **Input Debounce Protection**

The device features input debounce protection. The device starts operation (turn on the internal NFET) only if the input voltage is higher than the UVLO threshold for a period greater than the debounce time ( $t_{DEB}$ ). In case the voltage at IN falls below the UVLO threshold before  $t_{DEB}$  has passed, the switch remains off. If the voltage at OUT is already above the undervoltage trip level on output ( $V_{UVLO}_{OUT}$ ) when the device is turned on through UVLO/OVLO conditions, there is no  $t_{DEB}$  time. This is due to the device already being out of the power-on reset POR condition with OUT above  $V_{UVLO}_{OUT}$ . When the device is turned on through EN or HVEN, the  $t_{DEB}$  time is always present. Figure 4 depicts typical debounce timing diagram.

#### **Switch Control**

The device is enabled or disabled through two independent enable inputs, HVEN and EN. HVEN is a high-

## 5.5V to 60V, 6A Current-Limiter with OV, UV, Reverse Protection, and Power Limit

voltage-capable input, accepting signals up to 60V or V<sub>IN</sub>, whichever is lower. EN is a low-voltage input, accepting a maximum voltage of 5.5V. The device can be used to turn on or off power delivery to connected loads using the EN or HVEN pins. Toggling HVEN or EN resets the fault condition once a short circuit is detected and the device shuts down. Table 1 shows the truth table of the enable inputs to control the switch turn on or off status.

#### **Table 1. Enable Inputs**

| HVEN | EN | SWITCH STATUS |

|------|----|---------------|

| 0    | 0  | ON            |

| 0    | 1  | ON            |

| 1    | 0  | OFF           |

| 1    | 1  | ON            |

Figure 4. Debounce Timing Diagram

## 5.5V to 60V, 6A Current-Limiter with OV, UV, Reverse Protection, and Power Limit

#### **Startup Control**

The device features a startup sequence that continuously limits the current to the set current limit during the startup initial time ( $t_{STI}$ ), allowing large capacitors present on the output of the switch to be rapidly charged. If the temperature of device rises to the thermal foldback threshold ( $T_{J(FB)}$ ), the device enters power-limiting mode. In this mode, the device thermally regulates the current through the switch to protect itself while still delivering as much

current as possible to the output regardless of the currentlimit type selected. If the output is not charged within the startup timeout period ( $t_{STO}$ ), the switch turns off and IN, EN, or  $\overline{HVEN}$  must be toggled to resume normal operation. The  $t_{STO}$  timeout period is also applied when there is a restart after a turn-off event caused by UVLO or OVLO. If the output is not charged to ( $V_{IN} - V_{FA}$ ) level during this time, the device turns off and IN, EN, or  $\overline{HVEN}$  must be toggled to resume normal operation.

Figure 5. Startup Timing Diagram

#### Setting the Current-Limit Threshold

Connect a resistor between SETI and GND to program the current-limit threshold in the device. Use the following equation to calculate current-limit setting resistor:

$$R_{\text{SETI}} (k\Omega) = \frac{37500}{I_{\text{LIM}} (\text{mA})}$$

where ILIM is the desired current limit in mA.

Do not use a  $R_{SETI}$  smaller than  $6k\Omega$ . Table 2 shows current-limit thresholds for different resistor values.

The device read-out of the current flowing into the IN pin. A current mirror, with a ratio of  $C_{IRATIO}$ , is implemented, using a current-sense auto-zero operational amplifier. The mirrored current flows out through the SETI pin, into the

## Table 2. Current-Limit Threshold vs.SETI-Resistor Values

| R <sub>SETI</sub> (kΩ) | CURRENT LIMIT (A) |

|------------------------|-------------------|

| 187.50                 | 0.2               |

| 62.50                  | 0.6               |

| 37.50                  | 1.0               |

| 25.00                  | 1.5               |

| 18.75                  | 2.0               |

| 15.00                  | 2.5               |

| 12.50                  | 3.0               |

| 10.71                  | 3.5               |

| 9.37                   | 4.0               |

| 8.33                   | 4.5               |

| 7.50                   | 5.0               |

| 6.82                   | 5.5               |

| 6.25                   | 6.0               |

## 5.5V to 60V, 6A Current-Limiter with OV, UV, Reverse Protection, and Power Limit

external current-limit resistor. The voltage on the SETI pin provides information about the IN current with the following relationship:

$$I_{IN-OUT}$$

(mA) =  $\frac{V_{SETI}}{R_{SETI}}$  (k $\Omega$ ) ×  $C_{IRATIO}$

If SETI is left unconnected,  $V_{SETI} \ge 1.5V$ . The current regulator does not allow any current to flow. The device performs a check on the SETI pin for the first time it exits a shutdown condition. If the resistor placed on SETI is below  $3.2k\Omega$ , the switch remains off and the FLAG pin asserts. For best damped measurement, the capacitance on the SETI pin shall be limited to 30pF.

#### **Current-Limit Type Select**

The MAX17526A features three selectable current-limiting modes. During power-up, the device defaults to continuous mode and follows the procedure defined in the <u>Startup Control</u> section. Once the part has been successfully powered on and t<sub>STO</sub> has expired, the device senses the condition of CLMODE. The CLMODE pin is used to program the overcurrent response of the device in one of the following three modes:

- Autoretry mode: CLMODE is connected to GND

- Continuous mode: CLMODE pin is left unconnected

- Latch-off mode: a 220kΩ resistor is connected between CLMODE and GND

In addition to the selectable current-limit modes, the device has a protection feature against a severe overload condition. If the output current exceeds the overcurrent protection threshold ( $I_{OCP}$ ) of 24A (typ), the device turns off the internal and external NFETs. The off duration depends on the fault condition that occurs after the FETs turn off, with the shortest one being < 500µs ( $I_{ON\_NFET}$  max) that occurs if there is no fault and  $V_{OUT} > V_{OUT\_UVLO}$ . If the overload is still present when the device turns on in current-limit, it behaves according to the current-limit type selected.

## 5.5V to 60V, 6A Current-Limiter with OV, UV, Reverse Protection, and Power Limit

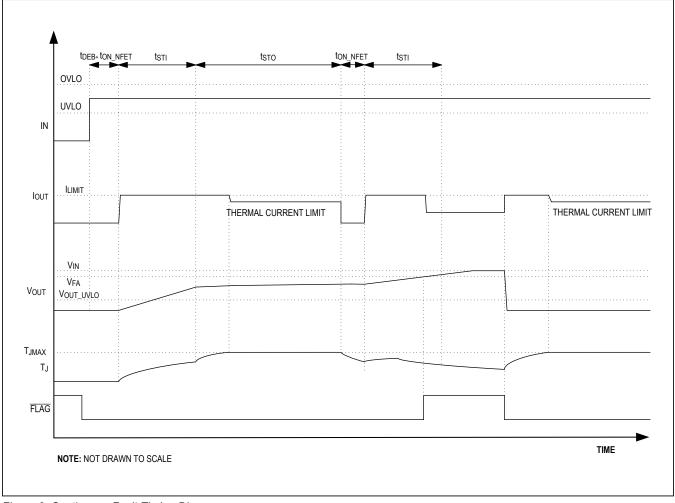

#### **Continuous Current Limit**

In continuous current-limit mode, when current through the device reaches the current limit threshold, the device limits the current to the programmed current limit. The FLAG

pin asserts when the voltage drop across the switch rises above V<sub>FA</sub>, and deasserts when it falls below V<sub>FA</sub>.. Figure 6 depicts typical behavior in continuous current-limit mode.

Figure 6. Continuous-Fault Timing Diagram

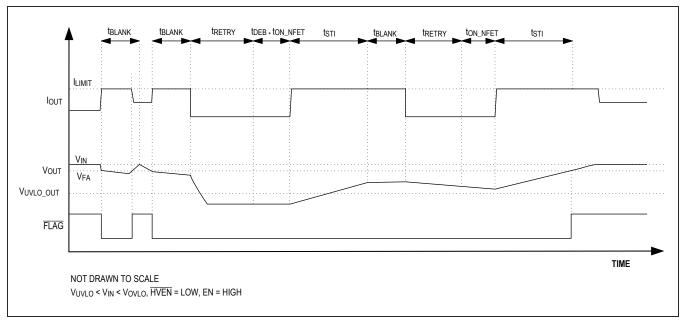

#### **Autoretry Current Limit**

In autoretry current-limit mode, when current through the device reaches the current-limit threshold, the  $t_{BLANK}$  timer begins counting. The FLAG pin asserts when the voltage drop across the switch rises above V<sub>FA</sub> and deasserts when it falls below V<sub>FA</sub>. The timer resets if the over-current condition resolves before  $t_{BLANK}$  has elapsed. A retry time delay ( $t_{RETRY}$ ) starts immediately after  $t_{BLANK}$  has elapsed. During  $t_{RETRY}$  time, the switch remains off. Once  $t_{RETRY}$  has elapsed, the switch is turned back on again. If the fault still exists, the cycle is repeated and the FLAG pin remains asserted. If the overcurrent condition is resolved, the switch stays on.

The autoretry feature reduces system power in case of overcurrent or short-circuit conditions. When the switch is on during  $t_{BLANK}$  time, the supply current is held at the current-limit. During  $t_{RETRY}$  time, there is no current

## 5.5V to 60V, 6A Current-Limiter with OV, UV, Reverse Protection, and Power Limit

through the switch. Thus, output current is much less than the programmed current-limit. Calculate the average output current using the following equation:

$$I_{\text{LOAD}} = I_{\text{LIM}} \left[ \frac{t_{\text{BLANK}} + t_{\text{STI}} \times K}{t_{\text{BLANK}} + t_{\text{RETRY}} + t_{\text{STI}}} \right]$$

where,

K = 1 for MAX17526A,

K = 1.5 for MAX17526B, and

K = 2 for MAX17526C

With a 24ms (typ)  $t_{BLANK}$ , 24ms (typ)  $t_{STI}$ , K = 1 and 720ms (typ)  $t_{RETRY}$ , the duty cycle is 6.25%, resulting in 93.75% power reduction when compared to the switch being on the entire time. Figure 7 depicts typical behavior in the autoretry current-limit mode.

Figure 7. Autoretry-Fault Timing Diagram

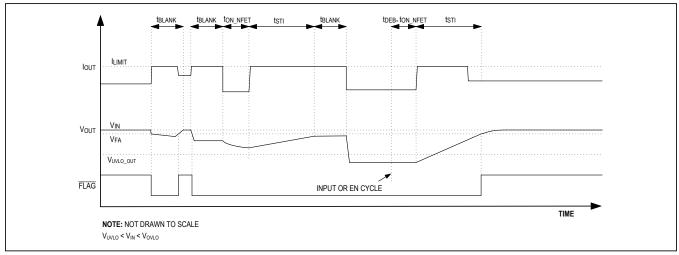

#### Latch-Off Current Limit

In latch-off current-limit mode, when current through the device reaches the current-limit threshold, the  $t_{BLANK}$  timer begins counting. The FLAG pin asserts when the voltage drop across the switch rises above V<sub>FA</sub> and deasserts when it falls below V<sub>FA</sub>. The timer resets if the over-current condition disappears before  $t_{BLANK}$  has elapsed. The switch turns off and stays off if the overcurrent condition continues beyond  $t_{BLANK}$ . To reset the switch, either toggle the control logic (EN or HVEN) or cycle the input voltage. Figure 8 depicts typical behavior in latch-off current-limit mode.

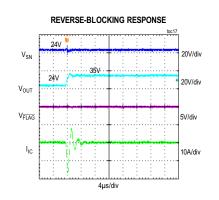

#### **Reverse Current Protection**

In the device, the reverse current-protection feature is enabled when used with external NFET and it prevents reverse current flow from OUT to IN pins.

## 5.5V to 60V, 6A Current-Limiter with OV, UV, Reverse Protection, and Power Limit

If a reverse current condition is detected (( $V_{IN} - V_{OUT}$ ) <  $V_{RIBRISING}$ ), the external NFET is turned off. When the reverse current condition no longer exists (( $V_{SN} - V_{OUT}$ ) >  $V_{RIBRISING}$ ), the external NFET is turned back ON after ton\_EXTNFET. If the reverse current condition is the only fault (no UVLO, no thermal fault, no forward overcurrent fault), then the internal NFET is kept ON, otherwise the internal NFET is also turned OFF. Figure 9 depicts typical behavior in slow or fast reverse current condition.

The device contains two reverse-current thresholds with slow (<  $17\mu$ s) and fast (< 108ns) response time for reverse current protection. The threshold values for slow reverse is 5.4mV (typ) whereas for fast reverse, it is 100mV (typ). This feature results in robust operation in a noisy environment, while still delivering fast protection for severe fault, such as input short-circuit or hot plug-in at the OUT pins.

Figure 8. Latchoff-Fault Timing Diagram

Figure 9. Reverse-Current-Fault Timing Diagram

#### **Power Limit**

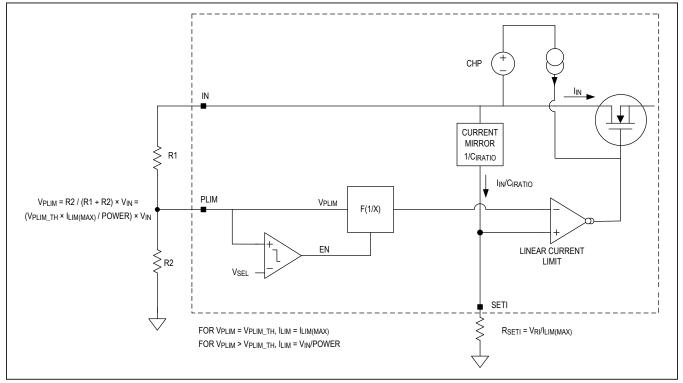

The device features a unique Power Limit feature that allows the set current limit to be modified automatically based on an external voltage ( $V_{EXT}$ ). The device monitors a fraction of this external voltage on the PLIM pin and dynamically adjusts the current limit set by the SETI pin resistor based on the below relationship:

when  $V_{PLIM} \leq V_{PLIM}$  TH,

Current is limited to ILIM value set by RSETI

when

$$V_{PLIM} > V_{PLIM}_{TH}$$

,

Current is limited to  $\frac{I_{LIM} \times V_{PLIM}_{TH}}{V_{PLIM}}$

Assuming the resistor-divider ratio of K for the resistors R5, R6 configured as shown in the <u>Typical Operating</u> <u>Circuit</u>, the above algorithm limits the power (P) delivered by the external voltage source as shown below:

$$V_{PLIM} = V_{EXT} \times K$$

$$P = \frac{V_{EXT} \times I_{LIM} \times V_{PLIM} TH}{V_{PLIM}}$$

Hence, P =  $\frac{I_{\text{LIM}} \times V_{\text{PLIM}}TH}{K}$ , where  $I_{\text{LIM}}$ , K and  $V_{\text{PLIM}}TH$

are essentially constants with tolerances dictated by the design. The device is designed for  $\pm 14\%$  V<sub>PLIM\_TH</sub> accuracy for the range V<sub>PLIM\_TH</sub> < V<sub>PLIM</sub> < 3 × V<sub>PLIM\_TH</sub>, which covers a 3x variation of external voltage (V<sub>EXT</sub>).

In an input Power Limit application VIN is equal to VEXT, and the PLIM resistor divider is set to determine the input voltage at which the current limit starts decreasing. By setting this voltage and setting the maximum current limit, the maximum "Input Power Limit" for the application is set. The current limit can also be dynamically modified based on the output voltage by using VOUT equal to VEXT. This feature implements an "Output Power Limit" function that potentially allows larger output currents to be delivered to charge the output reservoir capacitors at low output voltage conditions experienced after input power returns after an "Outage," provided there are no thermal limitations due to excessive power dissipation. The Power Limit feature is disabled by connecting the PLIM pin to GND. A simplified Block diagram of the PLIM feature is shown below in Figure 10.

Figure 10. Power Limit Circuit

#### Fault Output

The device has an open-drain fault-indicator output,  $\overline{FLAG}$ . It requires an external pullup resistor to a DC supply.  $\overline{FLAG}$  is held low when any of the following conditions occur:

- $V_{IN} V_{OUT} > V_{FA}$ .

- Die temperature exceeds +165°C.

- R<sub>SETI</sub> is less than 3.2kΩ (max).

- Input voltage falls below the UVLO threshold.

- Input voltage rises above the OVLO threshold.

The below table describes the status of the FETs along with various fault condition. The  $\overline{FLAG}$  pin is also 60V tolerant and when the open drain is on, it has a current protection that turns off the open drain if the current exceeds 4mA. The open drain is then turned back on if the fault condition is cycled.

#### Thermal Shutdown Protection

The device has a thermal shutdown feature to protect against overheating. The device turns off and the  $\overline{FLAG}$  pin asserts when the junction temperature exceeds +165°C (typ). The device exits thermal shutdown and resumes normal operation after the junction temperature cools by 10°C (typ), except in latch-off mode when the device remains latched off.

5.5V to 60V, 6A Current-Limiter with OV,

UV, Reverse Protection, and Power Limit

The thermal limit behaves similarly to current limit. In autoretry mode, the thermal limit works with the autoretry timer. When the junction temperature falls below the falling thermal shutdown threshold, the device turns on after the  $t_{RETRY}$ . In latch-off mode, the device latches off until the power cycled or one of the enable pins is toggled. In continuous mode, the device is only disabled while the temperature is over the limit and turns back on after  $t_{DEB}$  when the temperature reaches the falling thermal shutdown threshold. There is no blanking time for thermal protection. Figure 6, Figure 7, and Figure 8 depict typical behavior under different current limit modes.

| CONDITION                                            | INTERNAL NFET STATUS | EXTERNAL NFET STATUS | FLAG STATUS |

|------------------------------------------------------|----------------------|----------------------|-------------|

| No Fault                                             | ON                   | ON                   | HIGH        |

| UVLO                                                 | OFF                  | OFF                  | LOW         |

| OVLO                                                 | OFF                  | OFF                  | LOW         |

| Reverse with No Other Fault                          | ON                   | OFF                  | HIGH        |

| Overcurrent Protection<br>(I <sub>OCP</sub> , 24A)   | OFF                  | OFF                  | LOW         |

| Thermal Shutdown                                     | OFF                  | OFF                  | LOW         |

| SETI Grounded*                                       | OFF                  | OFF                  | LOW         |

| V <sub>IN</sub> - V <sub>OUT</sub> > V <sub>FA</sub> | X**                  | X**                  | LOW         |

#### **Table 3. FETs Status During Faults**

\*this condition is checked only at the first power on.

\*\*the status of the FETs in this condition depends on the timing and the current limit mode selected.

### **Applications Information**

#### **IN Capacitor**

A 1µF capacitor from the IN pin to EP/GND is recommended to hold input voltage during sudden load-current changes.

#### Hot Plug-In at IN Terminal

In many powering applications, an input-filtering capacitor is required to lower the radiated emission and enhance the ESD capability. In hot plug-in applications, parasitic cable inductance along with the input capacitor causes overshoot and ringing when a live power cable is connected to the input terminal.

This effect causes the protection device to see almost twice the applied voltage. A transient voltage suppressor (TVS) is often used in industrial applications to protect the system from these conditions. A TVS that is capable of limiting surge voltage to 60V (max) should be placed close to the input terminal for enhanced protection.

#### Input Hard Short to Ground

In many system applications, an input short-circuit protection is required. The device detects reverse current entering at the OUT pin and flowing out of the IN pin and turns off the external NFET. The magnitude of the reverse current depends on the inductance of input circuitry and any capacitance installed near the IN pins.

#### **OUT Capacitor**

The maximum capacitive load ( $C_{MAX}$ ) that can be connected is a function of current-limit setting ( $I_{LIM}$  in A), the startup initial time ( $t_{STI}$  in ms) and startup timeout ( $t_{STO}$  in ms) and the input voltage. The  $C_{MAX}$  is calculated using the following relationship:

$$C_{MAX}$$

(mF) = I<sub>LIM</sub> (A) ×  $\left[\frac{t_{STI} (ms) + t_{STO} (ms)}{V_{IN} (V)}\right]$

For example, for  $V_{IN}$  = 24V,  $t_{STO}$  (typ) = 1200ms,  $t_{STI}$  (typ) = 24ms, and  $I_{LIM}$  = 3A,  $C_{MAX}$  is 153mF.

Output capacitor values in excess of  $C_{MAX}$  can trigger false overcurrent conditions. Note that above expression assumes no load current is drawn from the OUT pins. Any load current drawn would offset the capacitor charging

## 5.5V to 60V, 6A Current-Limiter with OV, UV, Reverse Protection, and Power Limit

current resulting in a large charging period; hence, the possibility of a false overcurrent condition.

In practical applications, the  $C_{MAX}$  value is limited by the thermal performance of the PCB. Poor thermal design can cause the thermal foldback current-limiting function of the device to kick in too early, which can further limit the maximum capacitance that can be charged. Therefore, good thermal PCB design is imperative to charge large capacitor banks.

#### Hot Plug-In at OUT Terminal

In some applications, there might be a possibility of applying an external voltage at the OUT terminal of the devices with or without the presence of an input voltage. During these conditions, devices detect any reverse current entering at the OUT pin and flowing out of the IN pin and turn off the external NFET. Parasitic cable inductance along with input and output capacitors cause overshoot and ringing when an external voltage is applied at the OUT terminal. This causes the protection devices to see up to twice the applied voltage, which can damage the devices. It is recommended to maintain overvoltages such that the voltages at the pins do not exceed the absolute maximum ratings.

## OUT Freewheeling Diode for Inductive Hard Short to Ground

In applications that require protection from a sudden short to ground with an inductive load or a long cable, a schottky diode between the OUT terminal and ground is recommended. This is to prevent a negative spike on the OUT due to the inductive kickback during a short-circuit event.

#### Layout and Thermal Dissipation

To optimize the switch response to output short-circuit conditions, it is important to reduce the effect of undesirable parasitic inductance by keeping all traces as short as possible. Place input and output capacitors as close as possible to the device (no more than 5mm). IN and OUT must be connected with wide short traces to the power bus. During steady-state operation, the power dissipation is typically low and the package temperature change is usually minimal. PCB layout designs need to meet two challenges: high-current input and output paths and important heat dissipation.

Maxim recommends the use of 2oz copper on an FR4 isolator in a four-layer configuration. The layer stack needs to be Top (routing), GND (plane), Power (plane, connected to V<sub>OUT</sub>), and Bottom (routing), in this order, from top to bottom. Install the IC on an exposed pad landing of minimum 100 mils x 100 mils, with at least five through vias to the GND plane. The vias should be 32mils in diameter, with a 16mils plated hole. The hole plating needs to be at least 0.5oz copper. Provide a minimum of 1in x 1in area of copper plane on all four layers. It is important to remember that the inner planes do not contribute much to heat dissipation due to FR4 isolation, but are important from an electrical point of view. If possible, keep the top and bottom copper areas clear of solder mask, as this greatly improves heat dissipation. Use a similarly large copper area connected directly to the OUT pins. A dimension of 1in x 1in is also recommended. This might look oversized for current path requirements, but is essential for heat dissipation. Keep in mind that heat is generated at the drain junction of the internal nMOS pass FET, which is then eliminated through the five OUT pins and needs to be dissipated on this same copper area.

Connect all five IN pins to a copper area that is at least 150mils wide. Using 2oz copper can reduce this requirement to 100mils. Remember to provide the same copper trace width on the source connection, when using the external NMOS pass FET (with the source connected to the IN pins). Use extreme caution when placing the decoupling capacitors to the IN and OUT pins. The tendency to go as close as possible to the IC pins might interfere with the minimum requirement of the tracewidth above. It is important to note that the return load current does not flow through the IC; therefore, it is important to provide an external ground trace of at least the same width as the input/output one. Maxim recommends the use of a GND plane. Connect the input and output grounds to this plane using at least four plated vias each. The vias should be 84mils in diameter (or 60mils x 60mils, if square) with a 35mils plated hole.

#### **ESD** Protection

No capacitor is required for  $\pm 2kV$  (HBM) (typ) ESD on IN. All pins have  $\pm 2kV$  (HBM) ESD protection. In applications

## 5.5V to 60V, 6A Current-Limiter with OV, UV, Reverse Protection, and Power Limit

in which an external NFET is used, see the <u>IN Capacitor</u> section.

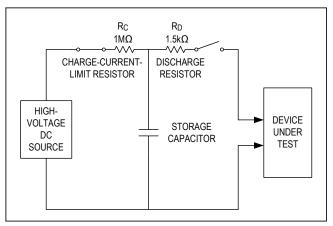

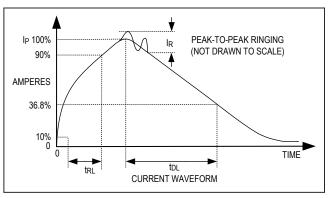

<u>Figure 11</u> shows the Human Body Model and <u>Figure 12</u> shows the current waveform it generates when discharged into low impedance. This model consists of a 100pF capacitor charged to the ESD voltage of interest, which is then discharged into the device through a  $1.5k\Omega$  resistor.

Figure 11. Human Body ESD Test Model

Figure 12. Human Body Current Waveform

## 5.5V to 60V, 6A Current-Limiter with OV, UV, Reverse Protection, and Power Limit

### **Ordering Information**

| PART             | TEMP RANGE      | PIN-PACKAGE | INITIAL CURRENT LIMIT | POWER LIMIT FEATURE |

|------------------|-----------------|-------------|-----------------------|---------------------|

| MAX17526AATP+    | -40°C to +125°C | 20 TQFN-EP* | 1.0x                  | Enabled             |

| MAX17526AATP+T   | -40°C to +125°C | 20 TQFN-EP* | 1.0x                  | Enabled             |

| MAX17526BATP+**  | -40°C to +125°C | 20 TQFN-EP* | 1.5x                  | Disabled            |

| MAX17526BATP+T** | -40°C to +125°C | 20 TQFN-EP* | 1.5x                  | Disabled            |

| MAX17526CATP+**  | -40°C to +125°C | 20 TQFN-EP* | 2.0x                  | Disabled            |

| MAX17526CATP+T** | -40°C to +125°C | 20 TQFN-EP* | 2.0x                  | Disabled            |

+Denotes a lead(Pb)-free/RoHS-compliant package.

T = Tape and reel.

\*EP = Exposed pad.

\*\*Future product—contact factory for availability.

## 5.5V to 60V, 6A Current-Limiter with OV, UV, Reverse Protection, and Power Limit

### **Revision History**

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION                                                                                                                                                                                                                                                                                                                           | PAGES<br>CHANGED                |

|--------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| 0                  | 6/18             | Initial release                                                                                                                                                                                                                                                                                                                       | —                               |

| 1                  | 11/18            | Updated Benefits and Features, Electrical Characteristics, Reverse Current Protec-<br>tion, and Power Limit sections                                                                                                                                                                                                                  | 1, 4–5<br>21–22                 |

| 2                  | 7/20             | Updated Typical Operating Circuit, Electrical Characteristics, Pin Description, Functional Diagram, Detailed Description, Setting the Current-Limit Threshold, Current-Limit Type Select, Continuous Current Limit, Autoretry Current Limit, Latch-Off Current Limit, Fault Output and the Ordering Information sections, and Table 3 | 2, 4–5, 12–14,<br>18–21, 23, 26 |

| 3                  | 11/21            | Updated <i>Benefits and Features</i> , <i>Electrical Characteristics</i> table, <i>Detailed Description</i> , and Table 2                                                                                                                                                                                                             | 1, 5<br>14, 18                  |

| 4                  | 9/22             | Updated Power Limit section                                                                                                                                                                                                                                                                                                           | 22                              |

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implicationor otherwise under any patent or patent rights of Analog Devices. Trademarks andregistered trademarks are the property of their respective owners.