**TI CONFIDENTIAL**

SWRS031A-OCTOBER 2005-REVISED DECEMBER 2005

# Fully Integrated Analog Front-End Dual Receiver Base Unit for 27-MHz Wireless Mouse and Keyboard Systems

### FEATURES

- 23 Discrete Components Intgrated Into One Chip

- Only External Components are Bypass and Filter Capacitors, and One Crystal

- RF Tuner, Mixer, Transistors, Passives, Coils, and SAW Filter Functionality All on One Chip

- Integrated Phase Locked Loop

- 8 User-Selectable Frequencies

- Each Channel (Mouse and Keyboard) Can Independently Select Any of the Available Frequencies

- Internally Generated 6-MHz Clock to Drive

USB Microcontroller

- High Data Throughput Rate

- 5-kHz Square Wave Simultaneously per Channel

- 10 kbps Miller Encoded Data

- I<sup>2</sup>C Control Interface

- Received Signal Strength Indicator (4-Blt)

- 5-V, 52 mA Supply

- Available in 28-Pin TSSOP (PW) Package

### APPLICATIONS

- 27-MHz Wireless Mouse and Keyboard Systems

- Human Interface Devices

- Wireless Control

- Remote Control Toys

- Wireless Headset

- Remote instrumentation

### DESCRIPTION

The TRF7900A is a dual integrated RF transceiver designed for Human Interface Devices (HID). Operating at 27 MHz, it integrates multiple components (PLL, RF mixer, simulated SAW filter, tuning circuit, and miscellaneous passive components) to provide frequency selection from 8 discrete channels. This integration lowers component, manufacturing and system costs.

The TRF7900A simplifies system design by reducing system component count and manual circuit tuning. By integrating the PLL, SAW filter, and RF mixer, the TRF7900A eliminates the manual tuning of RLC circuits required in traditional implementations.

The receiver also generates 8 frequencies that can be programmatically selected via the I<sup>2</sup>C interface bus for both the mouse channel and/or the keyboard channel. Another 6-MHz clock is internally generated to clock the USB microcontroller; this enables a single crystal to be used to supply the clock needs for the receiver channels and the microcontroller.

The optimized receiver design enables simultaneous reception on both parallel channels up to 5 kHz (10 kbps Miller encoding) per channel. A receive strength signal indicator register can be read via the l<sup>2</sup>C bus to determine if the transmit signal is too weak (weak battery or too far), or if there is too much noise on the selected channel in the user's area.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

#### **ORDERING INFORMATION**

| PACKAGED DEVICES | PACKAGE TYPE | TRANSPORT MEDIA, QUANTITY |

|------------------|--------------|---------------------------|

| TRF7900APW       | TSSOP - 28   | Rails, 50                 |

| TRF7900APWR      | 1330F - 26   | Tape and Reel, 2000       |

#### ABSOLUTE MAXIMUM RATINGS

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                        |                                                                                          | VALUE                        | UNIT |

|----------------------------------------|------------------------------------------------------------------------------------------|------------------------------|------|

| V <sub>S</sub> - to<br>V <sub>S+</sub> | Supply voltage                                                                           | 5.5                          | V    |

| VI                                     | Input voltage                                                                            | ±V <sub>S</sub> ± 0.5        | V    |

| V <sub>ID</sub>                        | Differential input voltage                                                               | ±2                           | V    |

|                                        | Continuous power dissipation                                                             | See Dissipation Rating Table |      |

| TJ                                     | Maximum junction temperature, any condition <sup>(2)</sup>                               | 150                          | °C   |

| TJ                                     | Maximum junction temperature, continuous operation, long term reliability <sup>(2)</sup> | 125                          | °C   |

| T <sub>stg</sub>                       | Storage temperature range                                                                | -65 to 150                   | °C   |

|                                        | Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds                             | 300                          | °C   |

|                                        | ESD ratings: Human Body Model                                                            | 4000                         | V    |

|                                        | ESD ratings: Charged Device Model                                                        | 1500                         | V    |

|                                        | ESD ratings: Machine Model                                                               | 200                          | V    |

(1) The absolute maximum ratings under any condition is limited by the constraints of the silicon process. Stresses above these ratings may cause permanent damage. Exposure to absolute maximum conditions for extended periods may degrade device reliability. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those specified is not implied.

(2) The maximum junction temperature for continuous operation is limited by package constraints. Operation above this temperature may result in reduced reliability and/or lifetime of the device.

#### **DISSIPATION RATINGS**

| PACKAGE | 0    | θ <sub>JA</sub> (1) | POWER F               | RATING <sup>(2)</sup> |

|---------|------|---------------------|-----------------------|-----------------------|

| FACRAGE | Alc  |                     | T <sub>A</sub> ≤ 25°C | T <sub>A</sub> = 85°C |

| PW (28) | 13.7 | 56.5                | 1.77 W                | 708 mW                |

(1) This data was taken using the JEDEC standard high-K test PCB.

(2) Power rating is determined with a junction temperature of 125°C. This is the point where distortion starts to substantially increase. Thermal management of the final PCB should strive to keep the junction temperature at or below 125°C for best performance and long term reliability.

#### **RECOMMENDED OPERATING CONDITIONS**

over operating free-air temperature range (unless otherwise noted)

|                              |                       | MIN | NOM | MAX | UNIT |

|------------------------------|-----------------------|-----|-----|-----|------|

| $\rm V_{S-}$ to $\rm V_{S+}$ | Suppy voltage, analog | 4.0 |     | 5.5 | V    |

### ELECTRICAL CHARACTERISTICS

$V_{s} = 5$  V, over operating free-air temperature range (unless otherwise noted)

|                | PARAMETER                                         | TEST CONDITIONS                                                                                           |                                       | MIN | TYP    | MAX | UNIT |

|----------------|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------|---------------------------------------|-----|--------|-----|------|

| RF SPE         | CIFICATIONS <sup>(1)(2)(3)</sup>                  |                                                                                                           |                                       |     |        | #   |      |

|                | Precision of required external 12-MHz crystal     | $T_A = -40^{\circ}C$ to $85^{\circ}C$                                                                     |                                       |     |        | 50  | ppm  |

|                | Channel spacing                                   |                                                                                                           |                                       |     | 50     |     | kHz  |

|                |                                                   | $T_A = 25^{\circ}C$                                                                                       |                                       |     | 26.995 |     | MHz  |

|                |                                                   |                                                                                                           |                                       |     | 27.045 |     | MHz  |

|                |                                                   |                                                                                                           |                                       |     | 27.095 |     | MHz  |

|                |                                                   |                                                                                                           |                                       |     | 27.145 |     | MHz  |

|                | Communication spacing                             |                                                                                                           |                                       |     | 27.195 |     | MHz  |

|                |                                                   |                                                                                                           |                                       |     | 27.295 |     | MHz  |

|                |                                                   | Optional channel                                                                                          |                                       |     | 27.245 |     | MHz  |

|                |                                                   | Optional channel                                                                                          |                                       |     | 26.945 |     | MHz  |

|                | Carrier stability of the transmitter and receiver |                                                                                                           |                                       |     | ±120   |     | ppm  |

|                |                                                   | DC Differential                                                                                           |                                       |     | <100   |     | kΩ   |

|                | Antenna input resistance                          | 27 MHz                                                                                                    |                                       |     | 5      |     | kΩ   |

|                | Antenna input capacitance                         | T <sub>A</sub> = 25°C                                                                                     |                                       |     | 5      |     | pF   |

| ۲ <sub>0</sub> | Output resistance, Out_1 and Out_2                | $T_A = 25^{\circ}C$                                                                                       |                                       |     | 1.2    | 2.0 |      |

|                |                                                   | $T_A = 0^{\circ}C$ to $70^{\circ}C$                                                                       |                                       |     |        | 2.0 | kΩ   |

|                |                                                   | $T_A = -40^{\circ}C$ to $85^{\circ}C$                                                                     |                                       |     |        | 2.0 |      |

|                |                                                   | Differential voltage<br>on antenna inputs<br>$50 \Omega$ to input 5 k $\Omega$<br>Impedance-<br>transform | т огоо                                | 20  | 14     |     | μV   |

|                |                                                   |                                                                                                           | $T_A = 25^{\circ}C$                   | -98 | -102   |     | dBm  |

|                | Sensitivity <sup>(1)</sup>                        |                                                                                                           | $T_A = 0^{\circ}C$ to $70^{\circ}C$   | -98 |        |     | dBm  |

|                |                                                   |                                                                                                           | $T_A = -40^{\circ}C$ to $85^{\circ}C$ | -98 |        |     | dBm  |

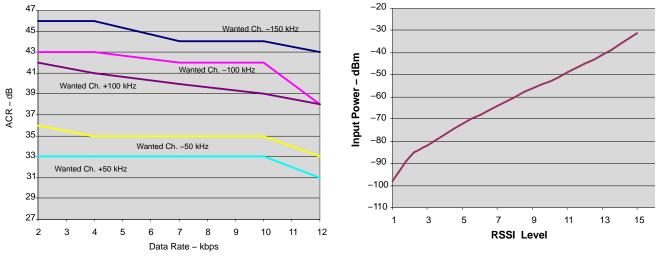

|                | Adjacent channel rejection (2)                    | Offset = 50 kHz                                                                                           | $T_A = 25^{\circ}C$                   | 30  | 34     |     | dB   |

|                |                                                   |                                                                                                           | $T_A = 0^{\circ}C$ to $70^{\circ}C$   | 30  |        |     | dB   |

|                |                                                   |                                                                                                           | $T_A = -40^{\circ}C$ to $85^{\circ}C$ | 30  |        |     | dB   |

|                |                                                   | Offset = 100 kHz or                                                                                       | $T_A = 25^{\circ}C$                   | 43  | 38     |     | dB   |

|                |                                                   | 150 kHz                                                                                                   | $T_A = 0^{\circ}C$ to $70^{\circ}C$   | 43  |        |     | dB   |

|                |                                                   |                                                                                                           | $T_A = -40^{\circ}C$ to $85^{\circ}C$ | 43  |        |     | dB   |

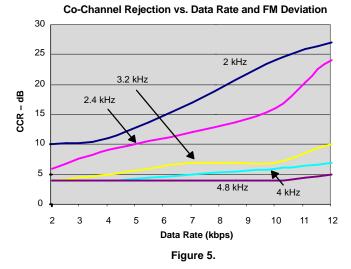

|                |                                                   |                                                                                                           | $T_A = 25^{\circ}C$                   | 5   | 5      |     | dB   |

|                |                                                   | 2.5 kbaud                                                                                                 | $T_A = 0^{\circ}C$ to $70^{\circ}C$   | 5   |        |     | dB   |

|                | Co-channel rejection (3)                          |                                                                                                           | $T_A = -40^{\circ}C$ to $85^{\circ}C$ | 5   |        |     | dB   |

|                | Co-channel rejection (*)                          |                                                                                                           | $T_A = 25^{\circ}C$                   | 9   | 7      |     | dB   |

|                |                                                   | 5 kbaud                                                                                                   | $T_A = 0^{\circ}C$ to $70^{\circ}C$   | 9   |        |     | dB   |

|                |                                                   |                                                                                                           | $T_A = -40^{\circ}C$ to $85^{\circ}C$ | 9   |        |     | dB   |

|                |                                                   | $T_A = 25^{\circ}C$                                                                                       |                                       |     | 25     |     | dB   |

|                | Spurious rejection                                | $T_A = 0^{\circ}C$ to $70^{\circ}C$                                                                       |                                       | 25  |        |     | dB   |

|                |                                                   | $T_A = -40^{\circ}C$ to $85^{\circ}C$                                                                     |                                       | 25  |        |     | dB   |

|                | Dynamic range                                     | $T_A = 25^{\circ}C$                                                                                       |                                       |     | 60     |     | dB   |

|                | Number of bits on RSSI                            | $T_A = 25^{\circ}C$                                                                                       |                                       |     | 4      |     | bits |

|                | RSSI update time                                  | T <sub>A</sub> = 25°C                                                                                     |                                       |     | 100    |     | ms   |

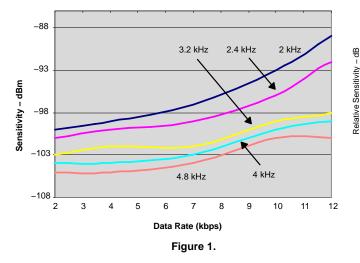

(1) FM deviation =  $\pm 3.2$  kHz, Data rate = 2.5 kbaud, PER < 0.08%.

(2) FM deviation = ±3.2 kHz, Data rate = 2.5 kbaud, PER < 0.08%. Unwanted signal is FM modulated using sine wave 1 kHz and ±3.2 kHz FM modulation depth.

(3) FM deviation = ±3.2 kHz, Data rate = 2.5 kbaud, PER < 0.08%. Co-channel signal is FM modulated using sine wave 1 kHz and ±3.2 kHz FM modulation depth.</p>

### **ELECTRICAL CHARACTERISTICS (continued)**

$V_{S}$  = 5 V, over operating free-air temperature range (unless otherwise noted)

|      | PARAMETER                   | TEST CONDITIONS                                           |                                                | MIN | TYP      | MAX | UNIT  |

|------|-----------------------------|-----------------------------------------------------------|------------------------------------------------|-----|----------|-----|-------|

| SK M | ODULATION                   |                                                           |                                                |     |          |     |       |

|      | Frequency deviation         | $T_A = 25^{\circ}C$                                       |                                                |     | 3.2      |     | kHz   |

|      | Data rate                   |                                                           |                                                |     | 5000     |     | bit/s |

|      | Preamble length             |                                                           |                                                |     | 6        |     | ms    |

| OWE  | R SUPPLY                    |                                                           |                                                |     |          |     |       |

|      |                             |                                                           | $T_A = 25^{\circ}C$                            | 4.0 | 5        | 5.5 |       |

|      |                             | Analog                                                    | $T_A = 0^{\circ}C$ to $70^{\circ}C$            | 4.0 |          | 5.5 | V     |

|      |                             |                                                           | $T_A = -40^{\circ}C$ to $85^{\circ}C$          | 4.0 |          | 5.5 |       |

|      |                             | Digital (CCL and                                          | $T_A = 25^{\circ}C$                            |     | 5        | 3.6 |       |

|      | Operating voltage           | Digital (SCL and SDA input logic                          | $T_A = 0^{\circ}C$ to $70^{\circ}C$            |     |          | 3.6 | V     |

|      |                             | HIGH)                                                     | $T_A = -40^{\circ}C \text{ to } 85^{\circ}C$   |     |          | 3.6 |       |

|      |                             | Digital (SCL and                                          | $T_A = 25^{\circ}C$                            | 3.1 | 5        |     |       |

|      |                             | SDA input logic                                           | $T_A = 0^{\circ}C$ to $70^{\circ}C$            | 3.1 |          |     | V     |

|      |                             | LOW)                                                      | $T_A = -40^{\circ}C$ to $85^{\circ}C$          | 3.1 |          |     |       |

|      |                             | $T_A = 25^{\circ}C$                                       |                                                | 38  | 50       | 65  | mA    |

|      | Normal mode supply current  | $T_A = 0^{\circ}C$ to $70^{\circ}C$                       |                                                | 38  |          | 65  |       |

|      |                             | $T_A = -40^{\circ}C \text{ to } 85^{\circ}C$              |                                                | 38  |          | 65  |       |

|      |                             | Both receivers<br>powered down,<br>oscillator active, and | $T_A = 25^{\circ}C$                            |     | 0.9      | 1.2 |       |

|      | Power-down supply current   |                                                           | $T_A = 0^{\circ}C$ to $70^{\circ}C$            |     |          | 1.2 | mA    |

|      |                             |                                                           | $T_A = -40^{\circ}C \text{ to } 85^{\circ}C$   |     |          | 1.2 |       |

|      |                             |                                                           | $T_A = 25^{\circ}C$                            |     | 3.3      | 3.6 |       |

|      | Internal supply volltage    | VPOS1, VPOS2,<br>VDIG, VPOS_LO1,                          | $T_A = 0^{\circ}C$ to $70^{\circ}C$            |     |          | 3.6 | V     |

|      | references                  | VPOS_LO2                                                  | $T_A = -40^{\circ}C \text{ to } 85^{\circ}C$   |     |          | 3.6 |       |

|      |                             |                                                           | $T_A = 25^{\circ}C$                            |     | 1.6      | 1.7 |       |

|      | Internal Mid-rail reference | MDR                                                       | $T_A = 0^{\circ}C$ to $70^{\circ}C$            |     |          | 1.7 | V     |

|      |                             |                                                           | $T_{A} = -40^{\circ}C \text{ to } 85^{\circ}C$ |     |          | 1.7 | -     |

| JAR  | TZ XTAL AND PROGRAMMING     |                                                           |                                                |     |          |     |       |

|      | Frequency                   | Fundimental mode operation                                | T <sub>A</sub> = 25°C                          | 12  | 2.000000 |     | MHz   |

|      | Frequency tolerance         |                                                           | $T_A = 25^{\circ}C$                            |     | ±50      |     | ppm   |

|      | Shunt capacitance           |                                                           | $T_A = 25^{\circ}C$                            |     | 7.0      |     | pF    |

|      | Aging                       |                                                           | $T_A = 25^{\circ}C$                            |     | <5       |     | ppm/y |

|      | Power-up settling time      | Time prior to I <sup>2</sup> C<br>programming<br>command  | $T_A = 25^{\circ}C$                            |     | 20       |     | ms    |

## TRF7900A

#### SWRS031A-OCTOBER 2005-REVISED DECEMBER 2005

Sensitivity vs. Data Rate & FM Deviation

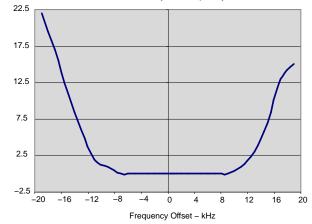

Relative Sensitivity vs. Frequency Offset

### Figure 2. **RSSI Level vs. Input Power**

Adjacent Channel Rejection vs. Data Rate and Frequency Distribution

Figure 4.

5

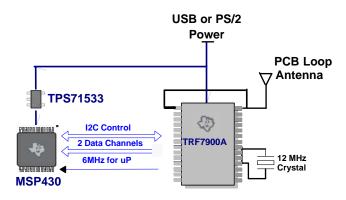

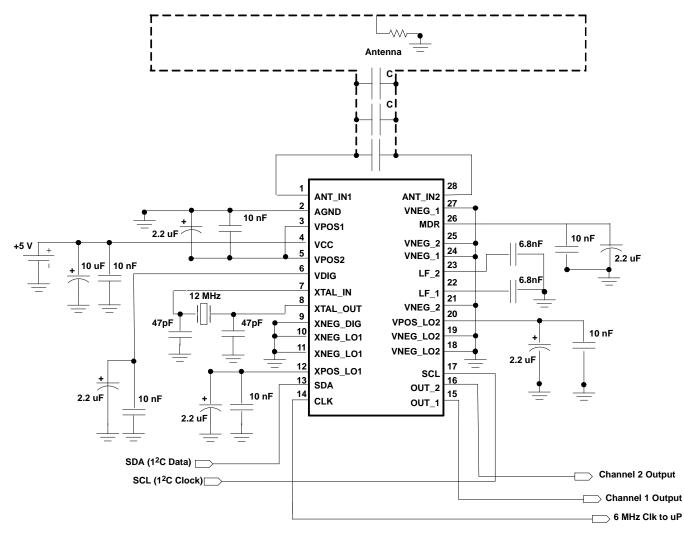

#### **APPLICATION SCHEMATIC**

### **DEVICE INFORMATION**

#### **TERMINAL FUNCTIONS**

| TERMINAL |     | 1/0 |                                           | RECOMMENDED EXTERNAL                 |

|----------|-----|-----|-------------------------------------------|--------------------------------------|

| NAME     | NO. | 1/0 | DESCRIPTION                               | COMPONENTS                           |

| ANT_IN1  | 1   | I   | Antenna input #1                          | Antenna input                        |

| AGND     | 2   |     | Analog ground                             |                                      |

| VPOS1    | 3   |     | Positive internal analog supply #1        | Cap. 2.2 μF and 10 nF to AGND        |

| VCC      | 4   |     | External positive supply                  | Cap. 10 μF and 10 nF to AGND         |

| VPOS2    | 5   |     | Positive internal analog supply #2        | Cap. 2.2 μF and 10 nF to AGND        |

| VDIG     | 6   |     | Positive internal digital supply          | Cap. 2.2 $\mu F$ and 10 nF to AGND   |

| XTAL_IN  | 7   | I   | 12-MHz quartz oscillator input            | Xtal input and 47 pF load capacitor  |

| XTAL_OUT | 8   | 0   | 12-MHz quartz oscillator output           | Xtal output and 47 pF load capacitor |

| VNEG_DIG | 9   |     | Negative internal digital supply          |                                      |

| VNEG_LO1 | 10  |     | Negative internal supply LO 1             |                                      |

| VNEG_LO1 | 11  |     | Negative internal supply LO 1             |                                      |

| VPOS_LO1 | 12  |     | Positive internal supply LO 1             | Cap. 2.2 $\mu$ F and 10 nF to AGND   |

| SDA      | 13  | I   | I <sup>2</sup> C data                     |                                      |

| CLK      | 14  | 0   | 6-MHz clock output                        |                                      |

| OUT_1    | 15  | 0   | Channel #1 output                         |                                      |

| OUT_2    | 16  | 0   | Channel #2 output                         |                                      |

| SCL      | 17  | I   | I <sup>2</sup> C clock                    |                                      |

| VNEG_LO2 | 18  |     | Negative internal supply LO 2             |                                      |

| VNEG_LO2 | 19  |     | Negative internal supply LO 2             |                                      |

| VPOS_LO2 | 20  |     | Positive internal supply LO 2             | Cap. 2.2 $\mu F$ and 10 nF to AGND   |

| VNEG_2   | 21  |     | Negative internal analog supply #2        |                                      |

| LF_1     | 22  | I   | Loop filter input for local oscillator #1 | Cap. 6.8 nF to AGND                  |

| LF_2     | 23  | I   | Loop filter input for local oscillator #2 | Cap. 6.8 nF to AGND                  |

| VNEWG_1  | 24  |     | Negative internal supply FM demod. #1     |                                      |

| VNEG_2   | 25  |     | Negative internal supply FM demod. #2     |                                      |

| MDR      | 26  |     | Mid rail reference voltage                | Cap. 2.2 µF and 10 nF to AGND        |

| VNEG_1   | 27  |     | Negative internal analog #1 supply        |                                      |

| ANT_IN2  | 28  | I   | Antenna input #2                          | Antenna input                        |

#### FUNCTIONAL DESCRIPTION

#### **Reference and Supply Block**

The REFERNCE block generates the reference voltage MDR. The MDR voltage is an internally generated voltage reference and has nominal level of 1.6 V. The MDR voltage output requires external capacitors for RF filtering and noise reduction. In low power mode the current supply of this block is reduced so that the reference maintains its functionality.

The five internal supply regulators (VPOS1, VPOS2, VDIG, VPOS\_LO1, VPOS\_LO2) use the MDR as a reference for supply voltage regulation. The regulated supply voltages are nominally 3.4V. The recommended filter capacitors are 10  $\mu$ F in parallel with 10 nF for VCC (pin 4). However, the 5 internal supply regulator filter capacitors can be decreased to 2.2  $\mu$ F in parallel with 10nF and still maintain functionality. In low power mode, the current requirements for these blocks are reduced but they still maintain functionality.

#### **Crystal Oscillator and Internal Divider**

The TRF7900 utilizes an external 12 MHz quartz crystal oscillator to generate the system clock and ensure proper synchronization between the components of the system. The 12 MHz clock is utilized by the local oscillator PLL system for internal reference frequency generation. This clock is also divided by 2 within the TRF7900 to provide a 6MHz output (CLK) that can be utilized by the external micro-controller. This ensures that all aspects of the system are continuously synchronized and eliminates the need for added external components. The internal oscillator and the divider blocks are constantly active, even when in power down mode.

#### PLL and VCO

The internal LO/PLL is capable of providing two LO signals for the receiver mixers. The desired frequency is synthesized from the 12MHz signal reference generated within the crystal oscillator. The desired channel is defined by a three-bit code for each of the two channels. The channel selection data is sent via the I<sup>2</sup>C protocol.

The TRF7900 incorporates two fully integrated voltage controlled oscillators. The only external components required in the two PLL and VCO systems are the shunt loop filter capacitors. Theses capacitors are connected to LF\_1 and LF\_2 pins on the TRF7900A. They should be placed in close proximity to the pins of the device.

Since the LO signals are not present at any of the output pins of the device, the possibility of LO leakage to the antenna is minimized. This simplifies board design and eases concerns relating to ECM emissions.

| I2C CODE | CHANNEL<br>FREQUENCY | UNIT |

|----------|----------------------|------|

| 000      | 26.995               | MHz  |

| 001      | 27.045               | MHz  |

| 010      | 27.095               | MHz  |

| 011      | 27.145               | MHz  |

| 100      | 27.195               | MHz  |

| 101      | 27.245               | MHz  |

| 110      | 27.295               | MHz  |

| 111      | 26.945               | MHz  |

The table below presents the programmable channels that can be selected via the I<sup>2</sup>C code.

#### RECEIVER

Two separate receivers are utilized within the TRF7900 for the two output channels. They are super heterodyne receivers composed of low noise amplifiers, mixers, IF filters and IF amplifiers followed by two FSK demodulators. This down conversion process converts the dual 27 MHz signals to two individual output data streams for the micro controller for processing.

#### LNA and Mixer

The integrated low noise amplifier is a multi stage amplifier operating at 27 MHz. The differential antenna input impedance of the part is greater than 5 k $\Omega$ , which allows for the utilization of a high Q antenna. The mixers are driven by the internal LO signals generated within the PLL and VCO sections.

#### IF Filter and Amplifier

The IF filter and amplifier stages are completely integrated in the TRF7900A. The selectivity of the IF filter allow for optimum reception and attenuation of adjacent channel interferer signals (≥50 kHz out of the center frequency).

#### **FSK Demodulator**

There are two completely integrated PLL based FSK demodulators. The analog signal generated in the receiver chain is digitized and used as the reference clock to the PLL. The FM demodulated signal is available to the PLL loop filter signal in controlling the VCO. The VCO control signal is digitized and results in a digital signal which is displayed at the output (OUT\_1 and OUT\_2). The demodulator is designed for a nominal frequency deviation of 3.2 kHz and data rate of 5 kbps (Miller coded).

#### **RSSI Block**

The signal level before and after the IF filters is measured. Signal levels on both sides of the filter are used to calculate actual RSSI level. The RSSI levels are indicated by a 4 bit representation each with a 4dB step size. The dynamic range is 64 dB. The RSSI level for both channels can be read via the I<sup>2</sup>C interface.

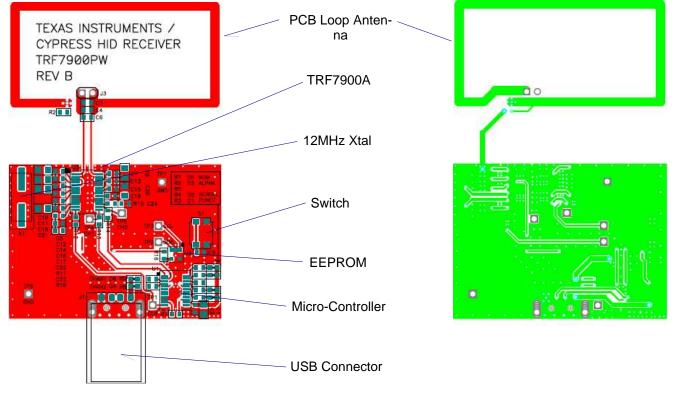

Figure 6. TI Desktop Reference Design

#### I<sup>2</sup>C INTERFACE DESCRIPTION AND PROGRAMMING

The TRF7900A IC communicates with the micro-controller using a standard I<sup>2</sup>C interface. It receives commands (channel selection and power-down) from the micro-controller and sends the RSSI information back to the controller. The micro-controller behaves as the master and the TRF7900A behaves as the slave in this aspect of operation. The I<sup>2</sup>C interface on the board uses 7-bit addressing mode and single byte write and read operation. The 7-bit I<sup>2</sup>C address used for the TRF7900A is 1101100. The TRF7900A is capable of communication with

## TRF7900A

SWRS031A-OCTOBER 2005-REVISED DECEMBER 2005

normal speeds up to 100kbps and in Fast I2C mode with transfer rates of up to 400 kbps. However, the maximum speed of the I<sup>2</sup>C communication in the TRF7900A is externally limited to 30kbps by the filters on the SDA and SCL lines. This is to help minimize the high-frequency overtones from the signals which could couple to the antenna and degrade the system sensitivity. With proper considerations in the PCB layout, the transfer rate could be increased.

#### NOTE:

At initial startup/reset, the micro-controller should allow a minimum of 20 ms for the quartz crystal to stabilize prior to programming the TRF7900A via the  $I^2C$ .

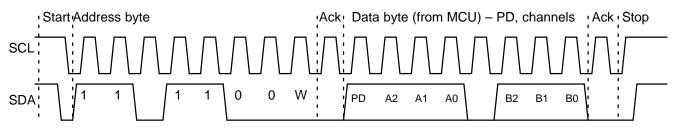

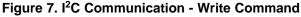

#### I<sup>2</sup>C Write Operation

The *write* command can be utilized to set the receiving frequencies for both channels of the TRF7900A. The SDA data stream should be as follows with respect to the clock or SCL.

Where:

Start = Start bit

Address byte = Address of TRF7900A (1101100)

W = Write command (logic level LOW)

Ack = acknowledge bit from the slave (slave pulls SDA low)

PD =Power Down bit (0 = normal mode, 1 = power down mode)

Data byte = Frequency selection bits for Channel 1 and 2 (see table below)

A0 to A2 = Channel 1 frequency selection

B0 to B2 = Channel 2 frequency selection

B3 =reserved bit which should be set to 0

Ack = acknowledge bit from the master (master pulls SDA low)

Stop = Stop bit

| CH          | CHANNEL SELECTION BITS |             |                           |  |  |  |

|-------------|------------------------|-------------|---------------------------|--|--|--|

| BIT 2 (MSB) | BIT 1                  | BIT 0 (LSB) | FREQUENCY                 |  |  |  |

| 0           | 0                      | 0           | 26.995 MHz                |  |  |  |

| 0           | 0                      | 1           | 27.045 MHz                |  |  |  |

| 0           | 1                      | 0           | 27.095 MHz                |  |  |  |

| 0           | 1                      | 1           | 27.145 MHz                |  |  |  |

| 1           | 0                      | 0           | 27.195 MHz                |  |  |  |

| 1           | 0                      | 1           | 27.245 MHz                |  |  |  |

| 1           | 1                      | 0           | 27.295 MHz <sup>(1)</sup> |  |  |  |

| 1           | 1                      | 1           | 26.945 MHz <sup>(1)</sup> |  |  |  |

(1) Not used in the EVM

#### I<sup>2</sup>C Read Operation

The *read* command is similar to the *write* command. It is utilized to read the RSSI level from the TRF7900A and communicate it to the micro-controller for processing. The SDA data stream with respect to the clock or SCL is as follows.

Figure 8. I<sup>2</sup>C Communication - Read Command

Where:

Start = Start bit

Address byte = Address of TRF7900A (1101100)

R = Read command (logic level HIGH)

Ack = acknowledge bit from the slave (slave pulls SDA low)

Data byte = RSSI data from TRF7900A

A0 to A3 = Channel 1 RSSI level (A3=MSB, A0=LSB)

B0 to B3 = Channel 2 RSSI level (B3=MSB, B0=LSB)

Ack (MCU) = acknowledge bit from the master (master pulls SDA low)

Stop = Stop bit

#### Peamble

The preamble has to be long enough to ensure proper settling of the FM demodulator in the receiver. The preamble length is typically set to 10 msec. This allows enough time for the FM demodulator to settle and prevents any loss of data from the transmitter.

#### Antenna Considerations

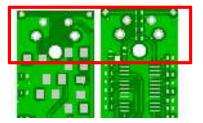

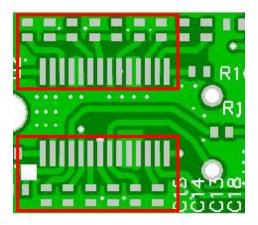

Antennas are used as the primary method of detecting the transmit signal from the Transmit source. The type of antenna, layout, location and size of the antenna plays an important role in the reception. There are a variety of different types of antennas available but two types are commonly used for HID applications, wire wound coils and PCB etched on antennas.

The wire wound coil antennas are made of copper that is coated with a thin insulative film. The wire is wound in a rectangular or oval manner to a certain length that represents a certain inductance value. It is then connected to the differential inputs of the TRF7900A along with some parallel capacitors. The combination of the inductive coil and capacitance provide for a resonance at the desired frequency of operation which is chosen to be centered at 27.1 MHz. It is recommended that special care be taken in the selection of the antenna coil and their tuning capacitors. The antenna coil and tuning capacitors should be designed such that it will have an input impedance of 5kohm and maintain a high quality factor (Q) value between 60-80. The Q is defined as (center frequency)/(3 dB band width). If the desired impedance can not be achieved, then an impedance matching circuit should be utilized to match the antenna to the antenna inputs of theTRF7900. This will ensure sufficient antenna reception and efficient selectivity of the desired signal.

The next type of antenna is the PCB etched on antenna. This type of antenna is similar to the wire wound in functionality but differs in that it is made up of a trace that is etched into the same PCB that the receiver circuitry is on. One advantage of this method is that the manual placement of a through-hole wire-wound coil antenna is eliminated and the cost associated with the coil. The PCB etched on antenna is typically more repeatable since its tolerances are tightly maintained by the PCB manufacturer. The PCB etched on antenna behaves similarly to the coil in that it is looped around the board or at the end of the board and provides for a certain inductance.

## **TRF7900A**

SWRS031A-OCTOBER 2005-REVISED DECEMBER 2005

When doing a PCB antenna, please take special care in the placement of the active circuitry and ground plane near the antenna as it will affect the performance of the antenna. It is also recommended (for multilayer boards) to place the traces on multiple layers directly on top of each other and also to follow the same direction. The items that impact the performance of the antenna include proximity of uP and active circuitry, area, width and thickness of the antenna trace. Slight improvements can also been achieved by leaving off the solder resist on the antenna traces. The user should design their antenna to maximize the available area such that the design is done to utilize area is is going to be a key in

#### NOTE:

When connecting the antenna to the TRF7900A and input tuning capacitors, it is important to remove all the ground directly under the input antenna traces all the way to the input of the TRF7900A. Otherwise, the trace and ground combination will create a transmission line with a specific impedance characteristics and frequency dependences. This is undesirable and will decrease the performance of the system.

### TYPICAL APPLICATION AND RESULTS

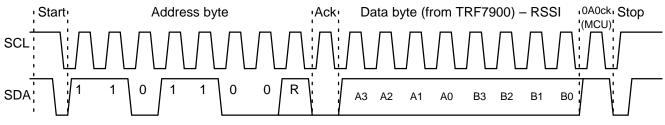

The TRF7900A can be used in many applications requiring single/dual channel capabilities that utilize the 27 MHz band. One of the common applications is its use in HID designs where wireless mice and/or keyboards are used. The TRF7900A can be utilized with a programmed micro-controller, EEPROM and some passive components to receive signals transmitted by the source. Below is a sample of an evm dongle that was designed for the TRF7900A.

The TRF7900A when initially powered on, starts off in a low current mode (inactive) and each of the channel selection bits default to 000-state (26.995 MHz). The TRF7900A can be made active only when the proper commands from the micro-controller are sent to the chip. Upon power-up or reset, the micro-controller should allow a minimum of 20ms of startup time prior to sending a command to the TRF7900A. This allows the quartz oscillator enough time to settle and stabilize before the receiver is powered. This ensures optimal functionality of the receiver.

### QUARTZ CRYSTAL SELECTION AND OUTPUT CLOCK (CLK)

The TRF7900A requires a 12 MHz crystal for synchronization and proper functionality. This reference is utilized by the internal VCO's and PLL's to provide a robust frequency reference for the receiver as selected by the I<sup>2</sup>C. The reference is also used to provide the 6MHz output clock which can be utilized by the external mico-controller or USB converter for USB synchronization.

It is encouraged that the CLK output of the TRF7900A be utilized to clock the microcontroller. If not, there is a chance that the instability caused by the internal clock can degrade system sensitivity and performance. This occurs when the harmonics, generated by the microcontrollers internal reference, spread over the broad receive frequency range of the TRF7900A. This dominant mechanism is magnetic in nature and its coupling is related to the current surges on the micro controllers input supply. For this reason it is extremely important that the lengths of the input supply traces be minimized and decoupling capacitors be situated as close to the pins as possible.

| PARAMETER            | SPECIFICATION |

|----------------------|---------------|

| Frequency            | 12.000000 MHz |

| Mode of operation    | Fundamental   |

| Frequency Tolerance  | ±50ppm        |

| Shunt Capacitance    | 7.0 pF max    |

| Aging                | < 5 ppm/year  |

| Operation Temp Range | –20°C to 70°C |

The reference crystal should have the following characteristics.

### ELIMINATING NOISE AND INCREASING PERFORMANCE

There are many methods to reduce noise (conductive and radiated) and increase performance. This includes parts placement considerations and also layout considerations. First, is the parts placement.

The TRF7900A receiver system utilizes ceramic capacitors at key nodes to help filter out low and high frequency noise. It is recommended that the placement of these components be kept as close to pins on the device as possible on the supply pins of both the TRF7900A and the micro-controller. This is done by minimizing the trace lengths to the capacitors and also having ground vias as close to the capacitors as possible when connecting to the ground plane. This helps to minimize ground loops and conductive noise. When possible, it is also recommended that ground planes be utilized to minimize the impedance associated with the return path to ground.

It is also recommended that a similar decoupling scheme be used for the micro controller to minimize its conducted emissions

The second type of method relates to the overall PCB layout. When doing layout, the designer is encouraged to pay close attention to the noise contributors and the sensitive circuits. The micro controller is typically considered the main noise contributor and the TRF7900A receiver as the noise sensitive circuit in this application. It is recommended that the *noisy* components not be kept in close proximity of the receiver. This can be achieved by isolating the two types by proximity. Either the components can be kept on opposite ends of the PCB (top side assembly only) or opposite sides of the PCB (top and bottom assembly). For example, the TRF7900A and quartz crystal can be placed together with minimum trace lengths and the micro controller can be placed away such that the digital signal transitions do not interfere with the receiver. It is recommended that the crossing of sensitive traces such as DC, control, crystal and data lines be kept to a minimum if at all possible during the layout process. Any crossing of these traces on different layers could cause noise to couple on the sensitive lines and in turn impact the performance of the receiver and the system.

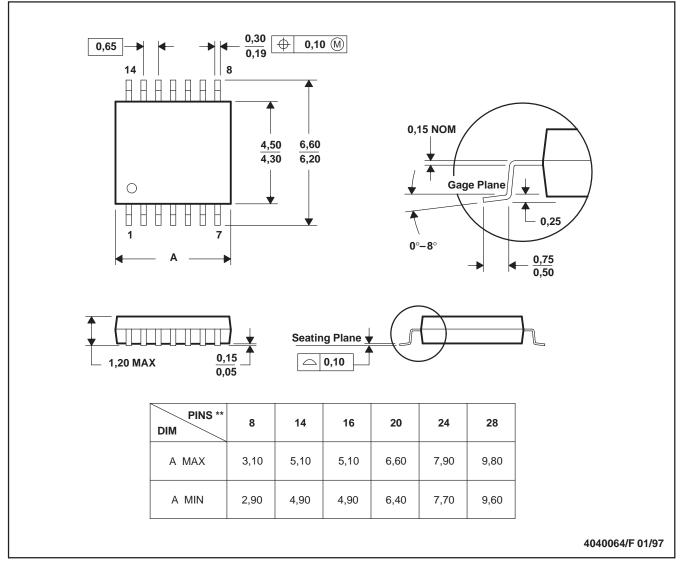

## **MECHANICAL DATA**

MTSS001C - JANUARY 1995 - REVISED FEBRUARY 1999

# PW (R-PDSO-G\*\*)

#### PLASTIC SMALL-OUTLINE PACKAGE

14 PINS SHOWN

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusion not to exceed 0,15.

- D. Falls within JEDEC MO-153

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 1999, Texas Instruments Incorporated