# MP62040/MP62041

1.7V – 5.5V, Ultra-Small, Single-Channel 2A Current-Limited Power Distribution Switch

The Future of Analog IC Technology

#### **DESCRIPTION**

The MP62040/MP62041 Power Distribution Switch is designed for high-side load switch. The switch operates from 1.7V to 5.5V nominal input voltage and includes an  $85m\Omega$  power MOSFET to handle up to 2A continuous load.

The MP62040/MP62041 has slew rate control with 115 $\mu$ s rising time to limit inrush current when enabling the switch.

The built-in level shift function allows a logic signal on enable input that may be different from the supply voltage to switch the high side P-channel MOSFET ON or OFF.

The MP62040/MP62041 is available in an ultrasmall UTQFN4 package, with ultra-low height (0.55mm typ).

#### **FEATURES**

- 2A Continuous Current

- 1.7V to 5.5V Supply Range

- Soft Start: 115µs

- 1µA Shutdown Current

- 85mΩ MOSFET

- Active High & Active Low Options

- Space saving 1.6x1.2 mm UTQFN4 Package (0.55mm Height)

#### **APPLICATIONS**

- Load switch in portable applications

- Battery switch-over circuits

- Level translator

For MPS green status, please visit MPS website under Quality Assurance. "MPS" and "The Future of Analog IC Technology" are Registered Trademarks of Monolithic Power Systems, Inc.

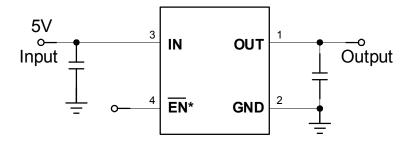

#### TYPICAL APPLICATION

MP62040 / MP62041

(\*: EN is active high for MP62041)

Single-Channel

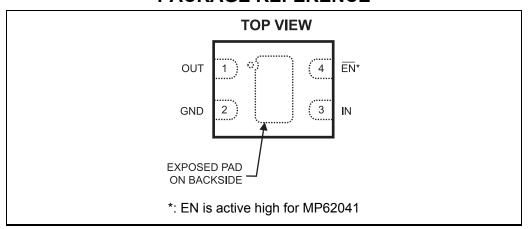

#### PACKAGE REFERENCE

| Part Number   | Enable      | Switch | Maximum<br>Continuous Load<br>Current | Package | Top<br>Marking | Free Air Temperature (T <sub>A</sub> ) |

|---------------|-------------|--------|---------------------------------------|---------|----------------|----------------------------------------|

| MP62040DQFU*  | Active Low  | Single | 2.4                                   | UTQFN4  | AGY            | -40°C to +85°C                         |

| MP62041DQFU** | Active High | Single | 2A                                    | UTQFN4  | AEY            | -40°C t0 +65°C                         |

\* For Tape & Reel, add suffix -Z (e.g. MP62040DQFU-Z).

For RoHS compliant packaging, add suffix -LF (e.g. MP62040DQFU-LF-Z)

\*\* For Tape & Reel, add suffix -Z (e.g. MP62041DQFU-Z).

For RoHS compliant packaging, add suffix –LF (e.g. MP62041DQFU-LF–Z)

## **PACKAGE REFERENCE**

# ABSOLUTE MAXIMUM RATINGS (1)

| INEN, OUT to GND                         |                 |

|------------------------------------------|-----------------|

| Continuous Power Dissipation             |                 |

| UTQFN4                                   |                 |

| Continuous Drain Current                 |                 |

| T <sub>A</sub> = +25°C                   | ±2A             |

| T <sub>A</sub> = +85°C                   | ±1.4A           |

| Pulsed Drain Current (3)                 | ±6A             |

| Continuous Diode Current (4)             | 50mA            |

| Junction Temperature                     | 150°C           |

| Lead Temperature                         | 260°C           |

| Storage Temperature                      | -65°C to +150°C |

| Maximum Junction Temp. (T <sub>J</sub> ) | +125°C          |

| Thermal Resistance (5) | $oldsymbol{	heta}_{JA}$ | $oldsymbol{	heta}_{JC}$ |  |

|------------------------|-------------------------|-------------------------|--|

| UTQFN4                 | 173                     | 127 °C/W                |  |

#### Notes:

- 1) Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature T<sub>J</sub>(MAX), the junction-to-ambient thermal resistance θ<sub>JA</sub>, and the ambient temperature TA. The maximum allowable continuous power dissipation at any ambient temperature is calculated by PD(MAX)=(T<sub>J</sub>(MAX)-TA)/θ<sub>JA</sub>. Exceeding the maximum allowable power dissipation will cause excessive die temperature, and the regulator will go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- 3) Pulse width <300µs and duty cycle < 2%

- Continuous body diode conduction (reverse conduction) is not recommended.

- 5) Measured on JESD51-7, 4-layer PCB.

# **ELECTRICAL CHARACTERISTICS** (6)

V<sub>IN</sub>=3.6V, T<sub>A</sub>=+25°C, unless otherwise noted.

| Parameter                                           | Symbol                                         | Condition                                       | Min | Тур | Max | Units |

|-----------------------------------------------------|------------------------------------------------|-------------------------------------------------|-----|-----|-----|-------|

| IN Voltage Range                                    | V <sub>IN</sub>                                |                                                 | 1.7 |     | 5.5 | V     |

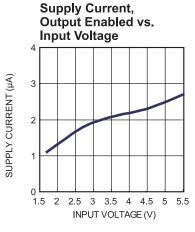

| Supply Current                                      |                                                | Device active, I <sub>OUT</sub> =0              |     | 2   |     | μA    |

| Shutdown Current                                    |                                                |                                                 |     |     | 1   | μA    |

|                                                     |                                                | V <sub>IN</sub> =1.7V, I <sub>OUT</sub> =100mA  |     | 165 | 225 | mΩ    |

|                                                     |                                                | V <sub>IN</sub> =1.8V, I <sub>OUT</sub> =100mA  |     | 155 | 215 | mΩ    |

| FET On_Resistance                                   |                                                | $V_{IN}$ =2.5V, $I_{OUT}$ =100mA                |     | 130 | 200 | mΩ    |

|                                                     |                                                | $V_{IN}$ =3.6V, $I_{OUT}$ =100mA                |     | 100 | 140 | mΩ    |

|                                                     | V <sub>IN</sub> =4.5V, I <sub>OUT</sub> =100mA |                                                 |     | 85  | 115 | mΩ    |

| EN Input Logic High Voltage                         |                                                | $V_{IN}$ = 1.7V to 4.5V, $I_{D}$ = -250 $\mu$ A | 1.2 |     |     | V     |

| EN Input Logic Low Voltage                          |                                                | $V_{IN}$ = 1.7V to 4.5V, $I_{D}$ = -250 $\mu$ A |     |     | 0.4 | V     |

| EN Input Current                                    |                                                | Device active, V <sub>IN</sub> = 5.5V           |     | 2   | 4   | μA    |

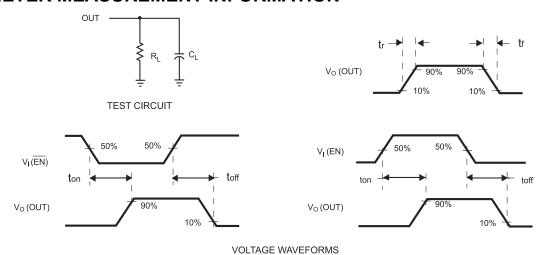

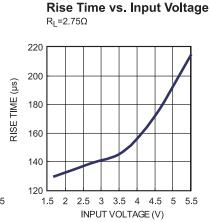

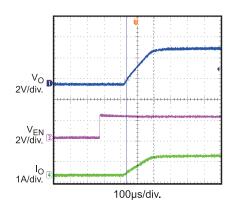

| <b>V</b> <sub>OUT</sub> Rising Time <sup>(7)</sup>  | Tr                                             | V <sub>IN</sub> =3.6V, I <sub>OUT</sub> =100mA  | 75  | 115 | 200 | μs    |

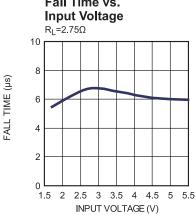

| <b>V</b> <sub>OUT</sub> Falling Time <sup>(8)</sup> | Tf                                             | V <sub>IN</sub> =3.6V, I <sub>OUT</sub> =100mA  | 65  | 75  | 100 | μs    |

| Turn On_Time (9)                                    | Ton                                            | V <sub>IN</sub> =3.6V, I <sub>OUT</sub> =100mA  |     | 235 | 350 | μs    |

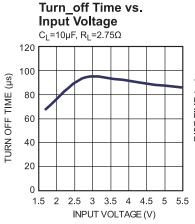

| Turn Off_Time (10)                                  | Toff                                           | V <sub>IN</sub> =3.6V, I <sub>OUT</sub> =100mA  |     | 100 | 200 | μs    |

#### Notes:

- 6) Production test at +25°C. Specifications over the temperature range are guaranteed by design and characterization.

- 7) Measured from 10% to 90%.

- 8) Measured from 90% to 10%.

- 9) Measured from (50%) EN signal to (90%) output signal.

- 10) Measured from (50%) EN signal to (10%) output signal.

## **PIN FUNCTIONS**

| UTQFN | Name | Description                                                               |  |  |

|-------|------|---------------------------------------------------------------------------|--|--|

| 1     | OUT  | IN-to-OUT Power-Distribution Output                                       |  |  |

| 2     | GND  | Ground and the thermal pad should both be connected to electrical ground. |  |  |

| 3     | IN   | Input Voltage. Accepts 1.7V to 5.5V input.                                |  |  |

| 4     | EN   | Active Low: (MP62040), Active High: (MP62041)                             |  |  |

## PARAMETER MEASUREMENT INFORMATION

Figure1 — Definition of Tr, Tf, Ton, and Toff

4

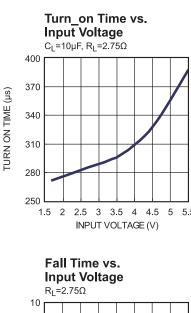

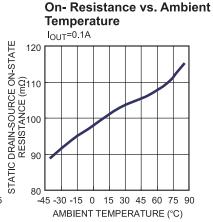

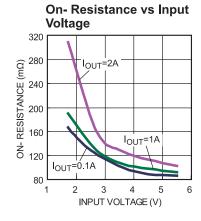

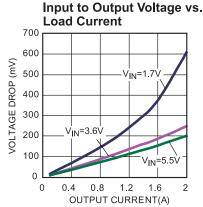

## TYPICAL PERFORMANCE CHARACTERISTICS

$V_{IN} = V_{EN} = 3.6V$ ,  $C_L = 1\mu F$ ,  $T_A = +25$ °C, unless otherwise noted.

# TYPICAL PERFORMANCE CHARACTERISTICS (continued)

$V_{IN} = V_{EN} = 3.6V$ ,  $C_L = 1\mu F$ ,  $T_A = +25$ °C, unless otherwise noted.

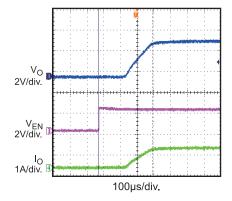

Turn\_on Delay and Rise Time with  $1\mu F$  Load  $R_I = 3.6\Omega$

Turn\_on Delay and Rise Time with 10µF Load

$C_{OUT} = 10\mu F$ ,  $R_L = 3.6\Omega$

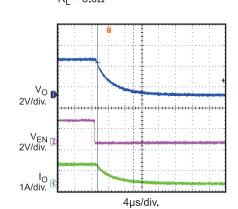

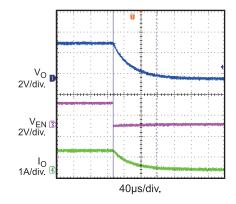

Turn\_off Delay and Fall Time with  $1\mu F$  Load  $R_I = 3.6\Omega$

Turn\_off Delay and Fall Time with 10µF Load

$C_{OUT} = 10 \mu F, R_L = 3.6 \Omega$

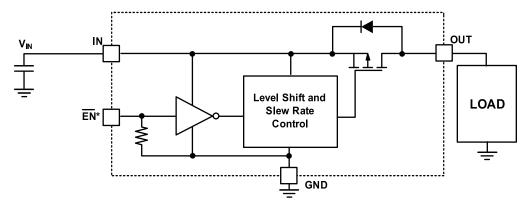

## **FUNCTION BLOCK DIAGRAM**

(\*: EN is active high for MP62041)

Figure 2 — Functional Block Diagram

#### DETAILED DESCRIPTION

The MP62040/MP62041 Power Distribution Switch is designed for high-side load switch. The switch operates from 1.7V to 5.5V nominal input voltage and can handle up to 2A continuous load.

#### **Enable**

The logic pin disables the switch to reduce overall supply current .Once the EN pin reaches logic enable threshold, the MP62040/MP62041 is enabled and the supply current is very small, only  $2\mu A$ .

#### APPLICATION INFORMATION

#### **Power-Supply Considerations**

Over  $10\mu F$  capacitor between IN and GND is recommended. This precaution reduces power-supply transients that may cause ringing on the input.

In order to achieve smaller output load transient ripple, placing a high-value electrolytic capacitor on the output pin(s) is recommended when the load is heavy.

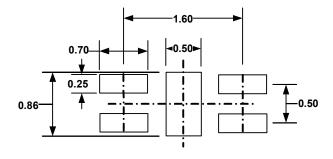

#### **PACKAGE INFORMATION**

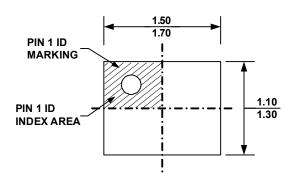

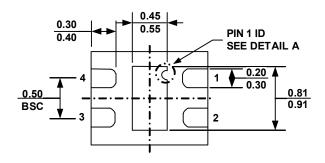

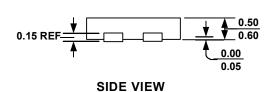

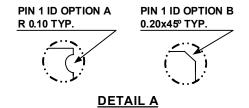

## **UTQFN (1.6x1.2mm)**

**TOP VIEW**

**BOTTOM VIEW**

#### NOTE:

- 1) ALL DIMENSIONS ARE IN MILLIMETERS

- 2) EXPOSED PADDLE SIZE DOES NOT INCLUDE MOLD FLASH

- 3) LEAD COPLANARITY SHALL BED.10 MILLIMETER MAX

- 4) JEDEC REFERENCE IS MO-229.

- 5) DRAWING IS NOT TO SCALE

#### RECOMMENDED LAND PATTERN

**NOTICE:** The information in this document is subject to change without notice. Users should warrant and guarantee that third party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.