## DESCRIPTION

The MP4688 is a high voltage input step-down switching regulator to deliver a constant current of up to 1A to high power LEDs. It integrates a highside high voltage power MOSFET with a current limit of 3.2A (typical value). The wide 4.5V to 80V input range accommodates a variety of step-down applications, making it ideal for automotive, industry and general lighting applications. Hysteresis current mode control is applied for very fast response, which makes the 20kHz dimming frequency possible. MPS's proprietary feedback control scheme minimizes the number of external components while delivering a LED current with typical ±5% accuracy.

The switching frequency is up to 2MHz, thus allowing for small component size. The thermal shut down, short circuit protection, and optional output voltage limitation provide reliable, fault tolerant operations. A 170µA quiescent current allows its use in battery-powered applications.

The MP4688 is available in SOIC8 and SOIC8 with exposed pad packages.

# **FEATURES**

- Wide 4.5V to 80V Operating Input Range

- No Output Capacitor Required

- ±5% LED Current Accuracy

- Hysteretic Control: No Compensation

- Up to 2MHz Switching Frequency

- Up to 20kHz Dimming Frequency

- Dedicated PWM Dimming Control Input

- Short circuit protection with integrated high side MOSFET

- Thermal shut down

- 200mV reference voltage for high efficiency

- Up to 95% Efficiency

- 170µA Quiescent Current

- Available in SOIC8 and SOIC8 with Exposed Pad Packages

## APPLICATIONS

- High Power LED Driver

- Automotive, Industry and General Lighting

- Constant Current Source

All MPS parts are lead-free and adhere to the RoHS directive. For MPS green status, please visit MPS website under Quality Assurance.

"MPS" and "The Future of Analog IC Technology" are Registered Trademarks of Monolithic Power Systems, Inc.

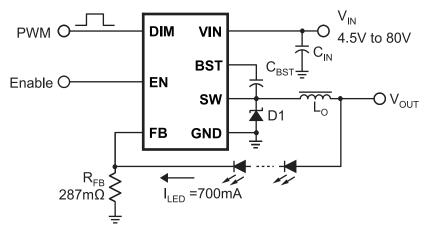

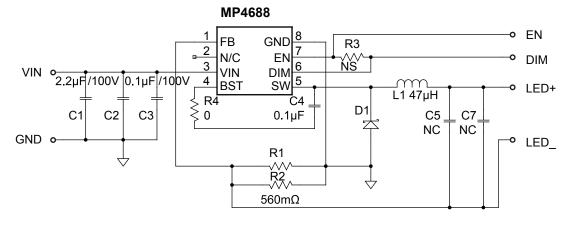

# TYPICAL APPLICATION

# ORDERING INFORMATION

| Part Number* | Package | Top Marking | Free Air Temperature (T <sub>A</sub> ) |

|--------------|---------|-------------|----------------------------------------|

| MP4688DN     | SOIC8E  | MP4688DN    | –40°C to +85°C                         |

| MP4688DS     | SOIC8   | MP4688DS    | –40°C to +85°C                         |

\* For Tape & Reel, add suffix –Z (e.g. MP4688DN–Z);

For RoHS compliant packaging, add suffix –LF (e.g. MP4688DN–LF–Z)

\* For Tape & Reel, add suffix –Z (e.g. MP4688DS–Z);

For RoHS compliant packaging, add suffix –LF (e.g. MP4688DS–LF–Z)

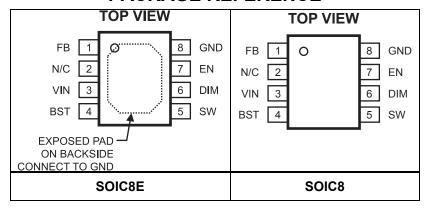

# PACKAGE REFERENCE

# **ABSOLUTE MAXIMUM RATINGS (1)**

| Supply Voltage (V <sub>IN</sub> ) | 0.3V to +80V                   |

|-----------------------------------|--------------------------------|

| Switch Voltage (V <sub>SW</sub> ) | $-0.5V$ to $V_{IN} + 0.5V$     |

| BST to SW                         | 0.3V to +6V                    |

| All Other Pins                    | –0.3V to +6V                   |

| Junction Temperature              |                                |

| Continuous Power Dissipatio       | n $(T_A = +25^{\circ}C)^{(2)}$ |

| SOIC8E (Exposed Pad)              | 2.5W                           |

| SOIC8                             | 1.3W                           |

| Lead Temperature                  | 260°C                          |

| Storage Temperature               | –65°C to +150°C                |

| Recommended Operating             | g Conditions <sup>(3)</sup>    |

| Supply Voltage V <sub>IN</sub>    |                                |

| EN and DIM Voltages               |                                |

| Operating Junct. Temp             | –40°C to +125°C                |

| Thermal Resistance (4) | $oldsymbol{	heta}_{JA}$ | $oldsymbol{	heta}_{JC}$ |     |

|------------------------|-------------------------|-------------------------|-----|

| SOIC8E (Exposed Pad)   | 50                      | 10°                     | C/W |

| SOIC8                  | 96                      | 45°                     | C/W |

#### Notes:

- 1) Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature T<sub>J</sub>(MAX), the junction-to-ambient thermal resistance θ<sub>JA</sub>, and the ambient temperature T<sub>A</sub>. The maximum allowable continuous power dissipation at any ambient temperature is calculated by P<sub>D</sub>(MAX)=(T<sub>J</sub>(MAX)-T<sub>A</sub>)/θ<sub>JA</sub>. Exceeding the maximum allowable power dissipation will cause excessive die temperature, and the regulator will go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- The device is not guaranteed to function outside of its operating conditions.

- 4) Measured on JESD51-7 4-layer board.

# **ELECTRICAL CHARACTERISTICS**

$V_{IN}$  = 60V,  $T_A$ = +25°C, unless otherwise noted. Specifications over temperature are guaranteed by design and characterization.

| Parameter                              | Symbol              | Condition                                                                       | Min  | Тур  | Max | Units    |

|----------------------------------------|---------------------|---------------------------------------------------------------------------------|------|------|-----|----------|

| VIN UVLO Threshold                     |                     |                                                                                 | 3.6  | 4.0  | 4.4 | V        |

| VIN UVLO Hysteresis                    |                     |                                                                                 |      | 0.4  |     | V        |

| Shutdown Supply Current                |                     | $V_{EN} = 0V$                                                                   |      | 2    | 5   | μA       |

| Quiescent Supply Current               |                     | No load, V <sub>FB</sub> = 250mV                                                |      | 170  | 220 | μA       |

| Upper Switch On Resistance (5)         | R <sub>DS(ON)</sub> | $V_{BST} - V_{SW} = 5V$                                                         |      | 360  |     | mΩ       |

| Upper Switch Leakage Current           | I <sub>SWLK</sub>   | $V_{EN} = 0V$ , $V_{SW} = 0V$                                                   |      | 0.01 | 1   | μΑ       |

| Current Limit                          | $I_{PK}$            | V <sub>FB</sub> = 0.15V                                                         | 2.5  | 3.2  |     | Α        |

| EN Up Threshold                        | $V_{ENH}$           |                                                                                 | 1.4  | 1.55 | 1.7 | V        |

| EN Threshold Hysteresis                | $V_{ENHY}$          |                                                                                 |      | 320  |     | mV       |

| EN Input Current                       | I <sub>ENI</sub>    | V <sub>EN</sub> =5V                                                             |      | 0.01 | 1   | μΑ       |

| EN Sinking Current                     | I <sub>ENS</sub>    | V <sub>EN</sub> =2V                                                             |      | 2    | 3   | μΑ       |

| DIM Up Threshold                       | $V_{DIMH}$          |                                                                                 | 0.8  | 1.15 | 1.5 | <b>V</b> |

| DIM Threshold Hysteresis               | $V_{DIMHY}$         |                                                                                 |      | 300  |     | mV       |

| DIM Input Current                      | $I_{DIM}$           | V <sub>DIM</sub> =5V or 0V                                                      | -1   |      | 1   | μΑ       |

| DIM On Propagation Delay               | $T_{DIMDH}$         | $V_{FB}$ =0V, $V_{DIM}$ Rising edge to $V_{SW}$ Rising Edge                     |      | 50   |     | ns       |

| DIM Off Propagation Delay              | $T_{DIMDL}$         | $V_{FB}$ =0V, $V_{DIM}$ Falling edge to $V_{SW}$ Falling Edge                   |      | 50   |     | ns       |

| Feedback Voltage Threshold High (5)    | $V_{FBH}$           | $4.5V < V_{IN} < 75V$ , $V_{FB}$ rising from 0V until $V_{SW} < 30V$            |      | 215  |     | mV       |

| Feedback Voltage Threshold Low (5)     | $V_{FBL}$           | $4.5V < V_{IN} < 75V$ , $V_{FB}$ falling from 0.25V until $V_{SW} > 30V$        |      | 185  |     | mV       |

| Feedback Average Voltage               | $V_{FB}$            |                                                                                 | 190  | 200  | 210 | mV       |

| FB Pin Input Current                   | I <sub>FB</sub>     | V <sub>FB</sub> =5V or 0V                                                       | -300 |      | 300 | nA       |

| FB Propagation Delay to Output<br>High | $T_{FBDH}$          | Falling edge of $V_{\text{FB}}$ from 0.25V to 0V to $V_{\text{SW}}$ rising edge |      | 100  |     | ns       |

| FB Propagation Delay to Output<br>High | $T_{FBDL}$          | Rising edge of V <sub>FB</sub> from 0V to 0.25V to V <sub>SW</sub> falling edge |      | 100  |     | ns       |

| Thermal Shutdown                       |                     | Hysteresis = 20°C                                                               |      | 150  |     | °C       |

#### Note:

5) Guaranteed by design.

# **PIN FUNCTIONS**

| SOIC8E<br>Pin # | SOIC8<br>Pin # | Name                   | Description                                                                                                                                                                                                                                |

|-----------------|----------------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1               | 1              | FB                     | Feedback. This is the input to hysteretic comparators. An external current sensing resistor is connected in series with the LEDs to GND. The feedback voltage is connected to this pin and is regulated at +200mV with 15% current ripple. |

| 2               | 2              | N/C                    | Not connected                                                                                                                                                                                                                              |

| 3               | 3              | VIN                    | Input Supply. This supplies power to all the internal control circuitry, both BS regulators and the high-side switch. A decoupling capacitor to ground must be placed close to this pin to minimize switching spikes.                      |

| 4               | 4              | BST                    | Bootstrap. This is the positive power supply for the internal floating high-side MOSFET driver. Connect a bypass capacitor between this pin and SW pin.                                                                                    |

| 5               | 5              | SW                     | Switch Node. This is the output from the high-side switch. A low $V_{\text{F}}$ Schottky rectifier to ground is required. The rectifier must be close to the SW pins to reduce switching spikes.                                           |

| 6               | 6              | DIM                    | PWM Dimming Input. Pulling this pin below the specified threshold for dimming off. Pulling it up above the specified threshold for dimming on. If there is no need for dimming function, connect DIM and EN pins together.                 |

| 7               | 7              | EN                     | Enable Input. Pulling this pin below the specified threshold shuts the chip down. Pulling it up above the specified threshold or leaving it floating enables the chip.                                                                     |

| 8               | 8              | GND,<br>Exposed<br>pad | Ground. It should be connected as close as possible to the output capacitor avoiding the high current switch paths. Connect exposed pad to GND plane for optimal thermal performance.                                                      |

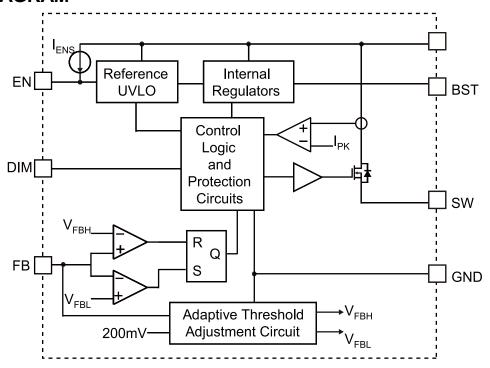

# **BLOCK DIAGRAM**

Figure 1—Function Block Diagram

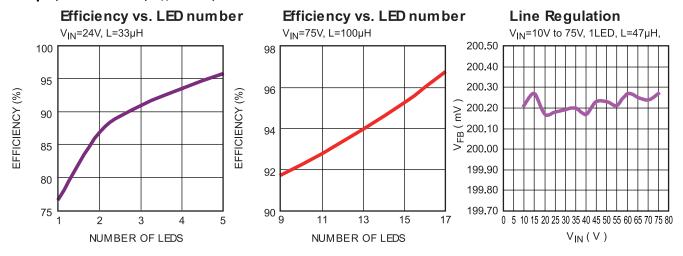

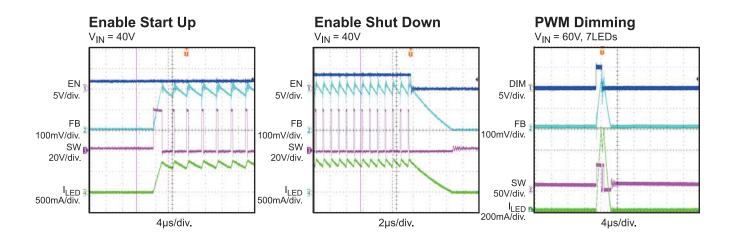

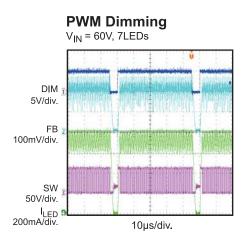

# TYPICAL PERFORMANCE CHARACTERISTICS

L=47μH, 1 LED Load, T<sub>A</sub>=25 °C, unless otherwise noted.

## **OPERATION**

# Hysteresis Current Control with Adaptive Threshold Adjustment

MP4688 operates in a hysteresis current control mode to regulate the LED current accurately. FB pin is the sensed voltage of LED current across the sensing resistor. The power MOSFET is turned on and remains on until FB pin rises to 215mV. The power MOSFET is turned off and remains off until FB pin falls to 185mV. The two thresholds of 215mV and 185mV are adaptive adjusted to compensate all the circuit delays so that the LED current is regulated very accurately with 200mV average value at FB pin.

#### **Enable Control**

The MP4688 has a dedicated enable control pin (EN) with the positive logic. Its falling threshold is a precision 1.2V, and its rising threshold is 1.5V (300mV higher).

When floating, EN is pulled up to about 3.0V by an internal  $1\mu A$  current source so it is enabled. To pull it down, over  $1\mu A$  current capability is needed.

#### Floating Driver and Bootstrap Charging

The floating power MOSFET driver is powered by an external bootstrap capacitor. This floating driver has its own UVLO protection. This UVLO's rising threshold is 2.2V with a threshold of 150mV.

The bootstrap capacitor is charged and regulated to about 5V by the dedicated internal bootstrap regulator.

In case the internal circuit does not have sufficient voltage and the bootstrap capacitor is not well charged, extra external circuitry can be used to ensure the bootstrap voltage is in the normal operational region. Refer to *External Bootstrap Diode* in Application section.

# **Under-Voltage Lockout (UVLO)**

Under-voltage lockout (UVLO) is implemented to protect the chip from operating at insufficient supply voltage. The UVLO rising threshold is about 4.0V while its falling threshold is a consistent 3.65V.

#### Thermal Shutdown

Thermal shutdown is implemented to prevent the chip from operating at exceedingly high temperatures. When the silicon die temperature is higher than its upper threshold, it shuts down the whole chip. When the temperature is lower than its lower threshold, the chip is enabled again.

#### **LED Short Protection**

The LED current is well regulated with FB pin voltage at 200mV. As long as the LED sensing resistor is not failed, the output current is within limitation. If the LED sensing resistor is failed or the output is shorted to GND directly, the FB pin voltage is low even the power MOSFET is turned on. The power MOSFET will be shut off if such failure time is longer than 10us. MP4688 will retry the operation after about 300us delay.

The power MOSFET current is also accurately sensed via a current sense MOSFET. If the current is over 3.2A, the IC is shut down. This offers extra protection under output short conditions.

# **APPLICATION INFORMATION**

#### **COMPONENT SELECTION**

## **Setting the LED Current**

The LED current  $I_{LED}$  is set using a sensing resistor  $R_{FB}$ , which is in series with the LEDs and connected to GND. The voltage on the sensing resistor  $R_{FB}$  is connected to FB pin.

$$I_{LED} = \frac{V_{FB}}{R_{FB}}$$

For example, for a 700mA LED current,  $R_{FB}$  is  $287m\Omega$ .

# **Inductor Selection and Frequency Setting**

The inductor  $L_O$  is required to supply a constant current to the LED. The inductor value is related to the switching frequency  $f_s$  setting:

$$f_s = \frac{V_{\text{OUT}} \cdot \left(V_{\text{IN}} - V_{\text{OUT}}\right)}{V_{\text{IN}} \cdot \left(8 \cdot 10^{-8} \cdot V_{\text{IN}} + L \cdot 15\% \cdot I_{\text{LED}}\right)}$$

Where,  $V_{\text{IN}}$  is the input voltage,  $V_{\text{OUT}}$  is the output voltage to drive the LEDs. A larger value inductor will result in smaller switching frequency.

The peak inductor current is about:

$$I_{LP} = I_{LED} \cdot \left( \frac{4 \cdot 10^{-8} \cdot V_{IN}}{L \cdot I_{LED}} + 1.075 \right)$$

Choose an inductor that will not saturate under the maximum inductor peak current.

#### **Output Rectifier Diode**

The output rectifier diode supplies the current to the inductor when the high-side switch is off. To reduce losses due to the diode forward voltage and recovery times, use a Schottky diode.

The RMS current through the diode is about:

$$I_{D} = I_{LED} \cdot \sqrt{1 - \frac{V_{OUT}}{V_{IN}}}$$

Choose a diode whose maximum reverse voltage rating is greater than the maximum input voltage, and whose current rating is greater than the maximum diode current.

# Input Capacitor C<sub>IN</sub>

The input current to the step-down converter is discontinuous, therefore a capacitor is required to supply the AC current to the step-down converter while maintaining the DC input voltage. Use low ESR capacitors for the best performance especially under high switching frequency applications.

The RMS current through the input capacitor is about:

$$I_{\text{D}} = I_{\text{LED}} \cdot \sqrt{\frac{V_{\text{OUT}}}{V_{\text{IN}}}},$$

With low ESR capacitors, the input voltage ripple can be estimated by:

$$\Delta V_{\text{IN}} = \frac{I_{\text{LED}}}{f_{\text{s}} \times C_{\text{IN}}} \times \frac{V_{\text{OUT}}}{V_{\text{IN}}} \times \left(1 - \frac{V_{\text{OUT}}}{V_{\text{IN}}}\right)$$

Choose the input capacitor with enough RMS current rating and enough capacitance for small input voltage ripple.

When electrolytic or tantalum capacitors are applied, a small, high quality ceramic capacitor, i.e.  $0.1\mu F$ , should be placed as close to the IC as possible.

# **Output Capacitor Cout**

The output capacitor ( $C_{\text{OUT}}$ ) is not necessary for MP4688. The LED current ripple (peak-to-peak value) is about 15% of the LED DC current. Output capacitor can be used to further reduce the LED current ripple. Low ESR capacitors are preferred to keep the output voltage ripple low so that the AC ripple current through the LEDs is small. The output voltage ripple can be estimated by:

$$\Delta V_{\text{OUT}} = \frac{V_{\text{OUT}}}{f_{\text{S}} \times L_{\text{O}}} \times \left(1 - \frac{V_{\text{OUT}}}{V_{\text{IN}}}\right) \times \left(R_{\text{ESR}} + \frac{1}{8 \times f_{\text{S}} \times C_{\text{OUT}}}\right)$$

Where  $R_{ESR}$  is the equivalent series resistance (ESR) value of the output capacitor.

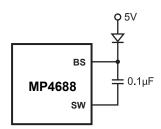

#### **External Bootstrap Diode**

An external bootstrap diode may enhance the efficiency of the LED driver. In below cases, an external BST diode is recommended from the 5V to BST pin:

- There is a 5V rail available in the system;

- VIN is no greater than 5V;

- VOUT is between 3.3V and 5V;

This diode is also recommended for high duty cycle operation (when  $V_{OUT}/V_{IN}>65\%$ ) and very high frequency (over 1.5MHz) applications.

The bootstrap diode can be a low cost one such as IN4148 or BAT54.

Figure 2—External Bootstrap Diode

#### **Layout Consideration**

It is essential to place the input decoupling capacitor, catch diode and the MP4688 (VIN pin, SW pin and PGND) as close as possible, with traces that are very short and fairly wide. This can help to greatly reduce the voltage spike on SW node, and lower the EMI noise level as well.

Try to run the feedback trace as far from the inductor and noisy power traces as possible. It is often a good idea to run the feedback trace on the side of the PCB opposite of the inductor with a ground plane separating the two.

To help to improve the thermal conduction, a grid of thermal vias can be created right under the exposed pad. It is recommended that they be small (15mil barrel diameter) so that the hole is essentially filled up during the plating process, thus aiding conduction to the other side. Too large a hole can cause 'solder wicking' problems during the reflow soldering process. The pitch (distance between the centers) of several such thermal vias in an area is typically 40mil.

# Reference design

Street lighting and flat panel lighting are transiting to more efficient sources of light. LED light source will become the trend in the near future. This reference design provides a flexible solution for street lighting and flat panel lighting application by utilizing MP4688 featuring high reliability, high efficiency, and accurate current regulation.

## **Specifications**

| Parameter                  | Symbol           | Value     | Units |

|----------------------------|------------------|-----------|-------|

| Input Voltage              | VIN              | 4.5 to 75 | V     |

| Enable/Dimming             | EN/DIM           | 5         | V     |

| LED Current                | I <sub>LED</sub> | 730       | mA    |

| Over Current<br>Protection | OCP              | 3.2       | Α     |

## Reference schematic

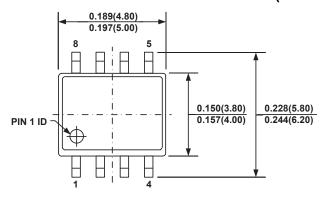

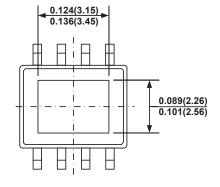

# PACKAGE INFORMATION

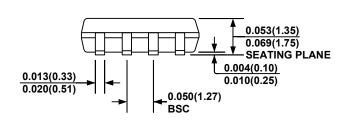

# **SOIC8E (EXPOSED PAD)**

**TOP VIEW**

**BOTTOM VIEW**

**FRONT VIEW**

RECOMMENDED LAND PATTERN

**←** 0.138(3.51) **▶**

**DETAIL "A"**

#### NOTE:

- 1) CONTROL DIMENSION IS IN INCHES. DIMENSION IN BRACKET IS IN MILLIMETERS.

- 2) PACKAGE LENGTH DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS.

- 3) PACKAGE WIDTH DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSIONS.

- 4) LEAD COPLANARITY (BOTTOM OF LEADS AFTER FORMING) SHALL BE 0.004" INCHES MAX.

- 5) DRAWING CONFORMS TO JEDEC MS-012, VARIATION BA.

- 6) DRAWING IS NOT TO SCALE.

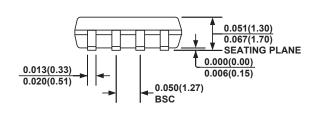

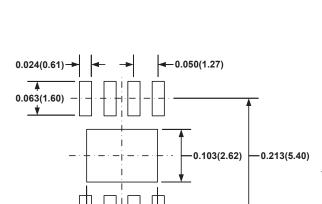

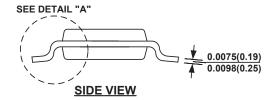

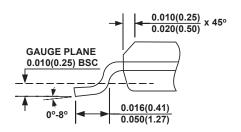

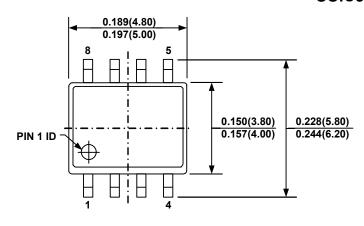

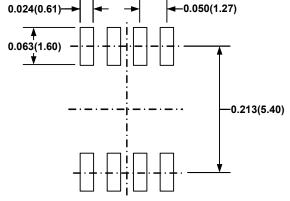

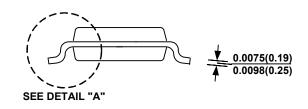

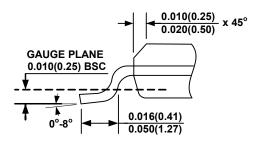

#### SOIC8

**TOP VIEW**

**RECOMMENDED LAND PATTERN**

**FRONT VIEW**

**SIDE VIEW**

**DETAIL "A"**

#### **NOTE:**

- 1) CONTROL DIMENSION IS IN INCHES. DIMENSION IN BRACKET IS IN MILLIMETERS.

- 2) PACKAGE LENGTH DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS.

- 3) PACKAGE WIDTH DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSIONS.

- 4) LEAD COPLANARITY (BOTTOM OF LEADS AFTER FORMING) SHALL BE 0.004" INCHES MAX.

- 5) DRAWING CONFORMS TO JEDEC MS-012, VARIATION AA.

- 6) DRAWING IS NOT TO SCALE.

**NOTICE:** The information in this document is subject to change without notice. Users should warrant and guarantee that third party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.