# National Semiconductor is now part of Texas Instruments.

Search <a href="http://www.ti.com/">http://www.ti.com/</a> for the latest technical information and details on our current products and services.

# SCAN926260 Six 1 to 10 Bus LVDS Deserializers with IEEE 1149.1 and At-Speed BIST

## **General Description**

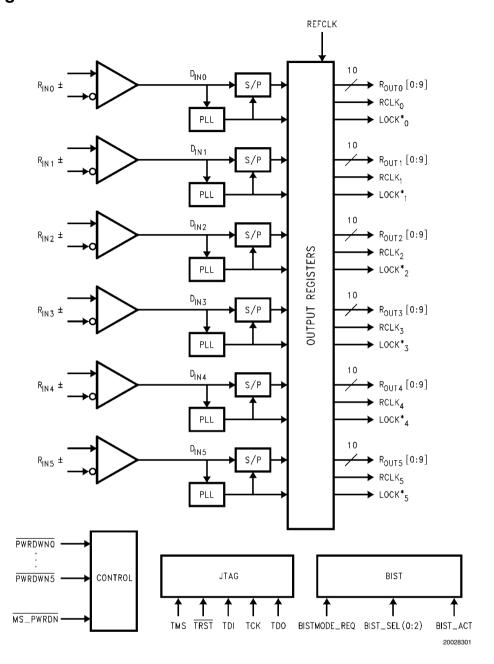

The SCAN926260 integrates six 10-bit deserializer devices into a single chip. The SCAN926260 can simultaneously deserialize up to six data streams that have been serialized by National Semiconductor's 10-bit Bus LVDS serializers. In addition, the SCAN926260 is compliant with IEEE standard 1149.1 and also features an At-Speed Built-In Self Test (BIST). For more details, please see the sections titled "IEEE 1149.1 Test Modes" and "BIST Alone Test Modes."

Each deserializer block in the SCAN926260 has it's own powerdown pin (PWRDWN[n]) and operates independently with its own clock recovery circuitry and lock-detect signaling. In addition, a master powerdown pin (MS\_PWRDWN) which puts all the entire device into sleep mode is provided.

The SCAN926260 uses a single +3.3V power supply and consumes 1.2W at 3.3V with a PRBS-15 pattern on all channels at 660Mbps.

#### **Features**

- Deserializes one to six Bus LVDS input serial data streams with embedded clocks

- IEEE 1149.1 (JTAG) Compliant and At-Speed BIST test modes

- Parallel clock rate 16-66MHz

- On chip filtering for PLL

- High impedance inputs upon power off (V<sub>cc</sub> = 0V)

- Single power supply at +3.3V

- 196-pin LBGA package (Low-profile Ball Grid Array) package

- Industrial temperature range operation: -40°C to +85°C

- ROUTn[0:9] and RCLKn default high when channel is not locked

- Powerdown per channel to conserve power on unused channels

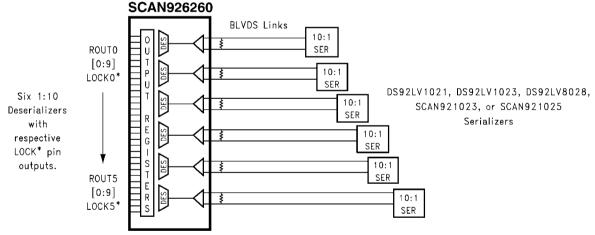

# **Typical Application**

20028302

# **Ordering Information**

| Order Number   | Function                              | Package                 |

|----------------|---------------------------------------|-------------------------|

| SCAN926260TUF  | Six Channel 10-bit BLVDS Deserializer | UJB196A (Trays)         |

|                | with IEEE 1149.1 and At-Speed BIST    |                         |

| SCAN926260TUFX | Six Channel 10-bit BLVDS Deserializer | UJB196A (Tape and Reel) |

|                | with IEEE 1149.1 and At-Speed BIST    |                         |

TRI-STATE® is a registered trademark of National Semiconductor Corporation

# **Absolute Maximum Ratings** (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

Supply Voltage ( $V_{DD}$ ) -0.3 to 3.8V

BLVDS Input Voltage (Rin ±) -0.3V to +3.9V

Maximum Package

Power Dissipation 3.7W

Capacity @ 25°C

Package Thermal Resistance

θ<sub>JA</sub> 196 LBGA: 34°C/W θ<sub>JC</sub> 196 LBGA: 8°C/W

Storage Temp. Range -65°C to +150°C

Junction Temperature +125°C Lead Temperature +225°C

>2KV

>250V

(Soldering 10 Seconds)

ESD Ratings:

Human Body Model

Machine Model

# Recommended Operating Conditions

Supply Voltage ( $V_{DD}$ ) 3.0V to 3.6V Operating Free Air -40°C to +85°C

Temperature (T<sub>A</sub>)

**Electrical Characteristics** Over recommended operating supply and temperature ranges unless otherwise specified. (Note 2)

| Symbol          | Parameter                              | Conditions                                                       | Pin/Freq.                        | Min   | Тур   | Max             | Units |

|-----------------|----------------------------------------|------------------------------------------------------------------|----------------------------------|-------|-------|-----------------|-------|

| LVCMOS/L        | VTTL DC Specification                  | s:                                                               |                                  |       |       |                 |       |

| V <sub>IH</sub> | High Level Input<br>Voltage            |                                                                  |                                  | 2.0   |       | V <sub>cc</sub> | V     |

| J <sub>IL</sub> | Low Level Input<br>Voltage             |                                                                  | REN, REFCLK, PWRDWNn ,           | GND   |       | 0.8             | V     |

| √ <sub>CL</sub> | Input Clamp Voltage                    |                                                                  | MS_PWRDWN                        |       | -0.87 | -1.5            | V     |

| IN              | Input Current                          | V <sub>in</sub> = 0 or 3.6V                                      |                                  | -10   |       | +10             | uA    |

| IN              | Input Current                          | V <sub>in</sub> = 0 or 3.6V                                      | TRST, TMS, TDI,<br>BIST_SEL[0:2] | -20   |       | +20             | uA    |

| V <sub>OH</sub> | High Level Output<br>Voltage           | I <sub>OH</sub> = -6mA                                           |                                  | 2     | 3     | V <sub>CC</sub> | ٧     |

| V <sub>OL</sub> | Low Level Output<br>Voltage            | I <sub>OL</sub> = 6mA                                            | ROUT,                            | GND   | 0.18  | 0.5             | ٧     |

| os              | Output short Circuit<br>Current        | V <sub>out</sub> = 0V                                            | RCLK,<br>LOCKn                   | -15   | -46   | -85             | mA    |

| oz              | TRI-STATE Output<br>Current            | MS_PWRDWN or REN = 0.8V V <sub>out</sub> = 0V or V <sub>CC</sub> |                                  | -10   | ±0.2  | +10             | μА    |

| V <sub>OH</sub> | High Level Output<br>Voltage           | I <sub>OH</sub> = -12mA                                          |                                  | 2     |       | V <sub>CC</sub> | ٧     |

| V <sub>OL</sub> | Low Level Output<br>Voltage            | I <sub>OL</sub> = 12mA                                           | TDO                              | GND   |       | 0.5             | ٧     |

| os              | TRI-STATE Output<br>Current            | V <sub>out</sub> = 0V                                            |                                  | -15   |       | -120            | mA    |

| Bus LVDS        | DC specifications                      |                                                                  |                                  |       |       |                 |       |

| / <sub>TH</sub> | Differential Threshold<br>High Voltage | VCM = 0.025,                                                     |                                  |       | +3    | +50             | mV    |

| / <sub>TL</sub> | Differential Threshold<br>Low Voltage  | 1.250, 2.375V<br>(V <sub>RI+</sub> -V <sub>RI-</sub> )           | B. B.                            | -50mV | -2    |                 | mV    |

| IN              | Input Current                          | $V_{in} = +2.4V,$<br>$V_{cc} = 3.6 \text{ or } 0V$               | RI+, RI-                         | -10   | ±1    | +10             | μΑ    |

|                 |                                        | V <sub>in</sub> =0V,<br>V <sub>cc</sub> = 3.6 or 0V              |                                  | -10   | ±1    | +10             | μΑ    |

| Symbol                              | Parameter                                             | Conditions                                        | Pin/Freq.      | Min                      | Тур                      | Max                       | Units    |

|-------------------------------------|-------------------------------------------------------|---------------------------------------------------|----------------|--------------------------|--------------------------|---------------------------|----------|

| Supply Cu                           | rrent                                                 |                                                   |                |                          |                          |                           |          |

| 1                                   | Total Supply Current                                  | Checker Board<br>Pattern,<br>C <sub>L</sub> =15pF | 66 MHz         |                          | 500                      | 600                       | mA       |

| I <sub>CCR</sub>                    | Total Supply Current                                  | PRBS-15<br>Pattern,<br>C <sub>L</sub> =15pF       | 66 MHz         |                          | 385                      |                           | mA       |

| ΔI <sub>CCR</sub>                   | Reduction in Supply<br>Current per Channel            | Checker Board<br>Pattern                          | 66 MHz         | 55                       | 77                       | 100                       | mA       |

| I <sub>CCXR</sub>                   | Total Supply Current when Powered Down                | MS_PWRDN=<br>0.8V,<br>(Note 4)                    |                |                          | 1.5                      | 2.2                       | mA       |

| Timing Re                           | quirements for REFCLE                                 | (                                                 |                |                          |                          |                           |          |

| t <sub>RFCP</sub>                   | REFCLK Period                                         |                                                   |                | 15.15                    |                          | 62.5                      | ns       |

| t <sub>RFDC</sub>                   | REFCLK Duty Cycle                                     |                                                   |                | 30                       | 50                       | 70                        | %        |

| t <sub>RFCP</sub> /t <sub>TCP</sub> | Ratio of REFCLK to TCLK                               |                                                   |                | 0.95                     |                          | 1.05                      |          |

| t <sub>RFTT</sub>                   | REFCLK Transition Time                                |                                                   |                |                          |                          | 8                         | ns       |

| Deserialize                         | er Switching Characteri                               | stics                                             |                | •                        |                          | •                         |          |

| t <sub>RCP</sub>                    | RCLK Period                                           |                                                   |                | 15.15                    |                          | 62.5                      | ns       |

| t <sub>RDC</sub>                    | RCLK Duty Cycle                                       | (Note 5)                                          | RCLK           | 41                       | 50                       | 55                        | %        |

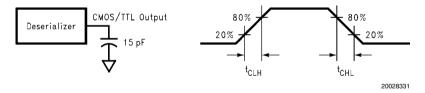

| t <sub>CLH</sub>                    | LVCMOS/LVTTL Low-<br>to-High Transition Time          | C <sub>L</sub> = 15pF,                            |                | 1.3                      | 1.8                      | 2.2                       | ns       |

| t <sub>CHL</sub>                    | LVCMOS/LVTTL High-<br>to-Low Transition Time          | Figure 3,<br>(Note 6)                             |                | 1.0                      | 1.5                      | 2.0                       | ns       |

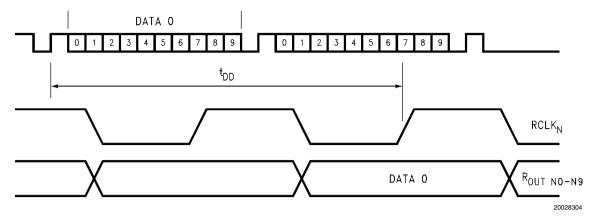

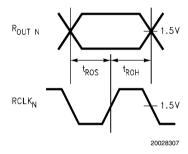

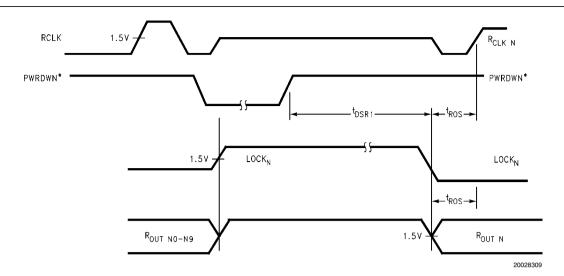

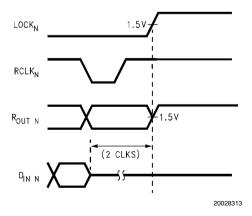

| t <sub>ROS</sub>                    | Rout Data Valid before RCLK                           | Figure 2                                          |                | 0.4*t <sub>RCP</sub>     |                          |                           | ns       |

| t <sub>ROH</sub>                    | Rout Data Valid after RCLK                            | Figure 2                                          | LOCK,<br>RCLK, | -0.4*t <sub>RCP</sub>    |                          |                           | ns       |

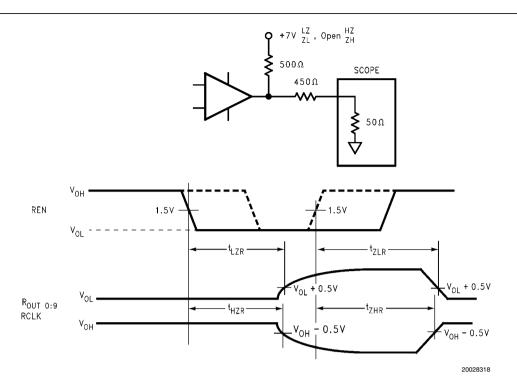

| t <sub>HZR</sub>                    | High to TRI-STATE<br>Delay                            |                                                   | ROUT           |                          |                          | 10                        | ns       |

| t <sub>LZR</sub>                    | Low to TRI-STATE<br>Delay                             | Figure 7                                          |                |                          |                          | 10                        | ns       |

| t <sub>ZHR</sub>                    | TRI-STATE to High<br>Delay                            | i iguio /                                         |                |                          |                          | 12                        | ns       |

| t <sub>ZLR</sub>                    | TRI-STATE to Low<br>Delay                             |                                                   |                |                          |                          | 12                        | ns       |

| t <sub>DD</sub>                     | Deserializer Delay                                    | Figure 1<br>(All Cases)                           | RCLK           | 1.75*t <sub>RCP</sub> +5 | 1.75*t <sub>RCP</sub> +7 | 1.75*t <sub>RCP</sub> +10 | ns       |

|                                     |                                                       | 66 MHz Only                                       |                | 1.75*t <sub>RCP</sub> +6 | 1.75*t <sub>RCP</sub> +7 | 1.75*t <sub>RCP</sub> +9  | ns       |

| t <sub>DSR1</sub>                   | Deserializer PLL LOCK Time from PWRDNn (with SYNCPAT) | Figure 4 -<br>(Note 7)                            | 66MHz<br>16MHz |                          |                          | 2.5<br>7.0                | μs<br>μs |

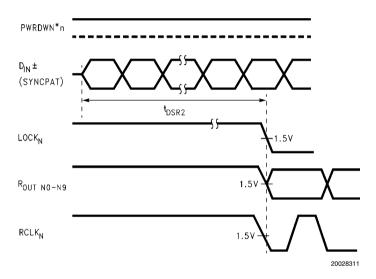

|                                     | Deserializer PLL Lock                                 | Figure 5                                          | 66MHz          | 1                        |                          | 1.1                       | μs       |

| t <sub>DSR2</sub>                   | Time from SYNCPAT                                     | (Note 7)                                          | 16MHz          | +                        |                          | 4.5                       | μs       |

|                                     | Deserializer Right                                    | (13.57)                                           | 66MHz          | 400                      | 500                      | 7.0                       | ps ps    |

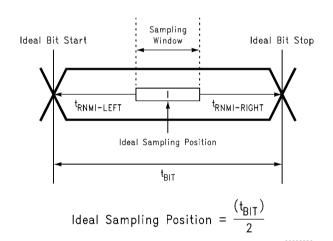

| $t_{\text{RNMI-RIGHT}}$             | Noise Margin                                          | Figure 8                                          | 16MHz          | 1.3                      | 2.51                     |                           | ns       |

|                                     | Deserializer Left Noise                               | (Note 8)                                          | 66MHz          | 440                      | 600                      |                           | ps       |

| t <sub>RNMI-LEFT</sub>              | Margin                                                | ` ' - '                                           | 16MHz          | 1.4                      | 2.59                     |                           | ns       |

- **Note 1:** "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. They are not meant to imply that the devices should be operated at these limits. The table of "Electrical Characteristics" specifies conditions of device operation.

- Note 2: Typical values are given for VDD = 3.3V and TA =25°C

- Note 3: Current into the device pins is defined as positive. Current out of device pins is defined as negative. Voltages are referenced to ground except VTH and VTL which are differential voltages.

- Note 4: Total Supply Current when Powered Down (I<sub>CCXR</sub>) is higher than previous six channel devices because previous devices asserted ROUTn and RCLKn into TRI-STATE upon loss-of-lock, whereas the SCAN926260 now asserts ROUTn and RCLKn HIGH upon loss-of-lock.

- Note 5: t<sub>RDC</sub> was specified by measuring the positive pulse on the RCLK and dividing this number by the ideal pulse width.

- Note 6: t<sub>CLH</sub> and t<sub>CHI</sub> are Guranteed by Statistical Analysis (GBSA). Please see Figure 3 for a graphical representation.

- Note 7: For the purpose of specifying deserializer PLL performance, t<sub>DSR1</sub> and t<sub>DSR2</sub> are specified with the REFCLK running and stable, and specific conditions of the incoming data stream (SYNCPATs). t<sub>DSR1</sub> is the time required for the deserializer to indicate lock upon power-up or when leaving the power-down mode. t<sub>DSR2</sub> is the time required to indicate lock for the powered-up and enabled deserializer when the input (RI+ and RI-) conditions change from not receiving data to receiving synchronization patterns (SYNCPATs). The time to lock to random data is dependent upon the incoming data and is not specified.

- Note 8: t<sub>RNMI-LEFT</sub> and t<sub>RNMI-RIGHT</sub> are a measure of how much phase noise (jitter) the deserializer can tolerate in the incoming data stream before bit errors occur. The Deserializer noise margin specification does not include transmitter jitter and is Guaranteed By Statistical Analysis (GBSA). Please see Figure 8 for a graphical representation.

#### **SCAN Circuitry Timing Requirements**

| Symbol           | Parameter                      | Conditions                     | Min  | Тур  | Max | Units |

|------------------|--------------------------------|--------------------------------|------|------|-----|-------|

| f <sub>MAX</sub> | Maximum TCK Clock<br>Frequency | $R_L = 500\Omega, C_L = 35 pF$ | 25.0 | 50.0 |     | MHz   |

| t <sub>S</sub>   | TDI to TCK, H or L             |                                | 2.0  |      |     | ns    |

| t <sub>H</sub>   | TDI to TCK, H or L             |                                | 1.0  |      |     | ns    |

| t <sub>S</sub>   | TMS to TCK, H or L             |                                | 2.5  |      |     | ns    |

| t <sub>H</sub>   | TMS to TCK, H or L             |                                | 1.0  |      |     | ns    |

| t <sub>W</sub>   | TCK Pulse Width, H or L        |                                | 10.0 |      |     | ns    |

| t <sub>W</sub>   | TRST Pulse Width, L            |                                | 2.5  |      |     | ns    |

| t <sub>REC</sub> | Recovery Time, TRST to TCK     |                                | 2.0  |      |     | ns    |

# **Timing Diagrams**

FIGURE 1. Deserializer Delay  $t_{\rm DD}$

FIGURE 2. Output Timing  $t_{\text{ROS}}$  and  $t_{\text{ROH}}$  (Data Valid)

FIGURE 3. Deserializer CMOS/LVTTL Output Load and Transition Times

5

FIGURE 4. Locktime from PWRDNn t<sub>DSR1</sub>

FIGURE 5. Locktime to SYNCPAT  $t_{\rm DSR2}$

FIGURE 6. Loss of Lock

FIGURE 7. Deserializer TRI-STATE Test Circuit and Timing

Note: For an explanation of Ideal Crossing Point and Noise Margin, please see the Application Information section.

FIGURE 8. Deserializer Noise Margin and Sampling Window

# **Block Diagram**

# **Functional Description**

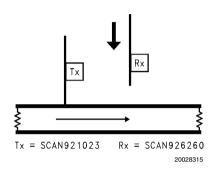

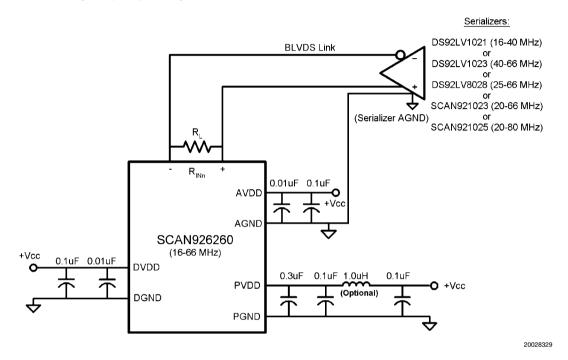

The SCAN926260 combines six 1:10 deserializers into a single chip. Each of the six deserializers accepts a Bus LVDS data stream from National Semiconductor's DS92LV1021, DS92LV1023, DS92LV8028, SCAN921023, or SCAN921025 Serializer. The deserializers then recover the clock and data to deliver the resulting 10-bit wide words to the outputs.

Each of the six channels acts completely independent of each other. Each independent channel has outputs for a 10-bit wide data word, a recovered clock output, and a lock-detect output.

The SCAN926260 has three operating states: Initialization, Data Transfer, and Resynchronization. In addition, there are two passive states: Powerdown and TRI-STATE. During normal operation, the SCAN6260 also has the capability of utilizing the IEEE 1149.1 test modes (JTAG) or the Built-In Self Test mode (BIST).

The following sections describe each operating mode, passive states, and the JTAG and BIST modes.

#### Initialization

Before the SCAN926260 receives and deserializes data, it and the transmitting Serializer must initialize the link. Initialization refers to synchronizing the Serializer's and the Deserializer's PLL's to local clocks. The local clocks must be within  $\pm 5\%$  of the incoming transmitter clock frequency. After all devices synchronize to local clocks, the Deserializer synchronizes to the Serializer as the second and final initialization step.

Step 1: After applying power to the Deserializer, the outputs are held high and the on-chip Power-on Reset (POR) circuitry disables the internal circuits. When  $V_{\rm cc}$  reaches  $V_{\rm cc}$ OK (2.1V), the PLL in each deserializer begins locking to the local clock (REFCLK). A local on-board oscillator or other source that provides the specified clock input to the REFCLK pin.

Step 2: The Deserializer PLL must synchronize to the Serializer to complete the initialization. Refer to the Serializer data sheet for proper operation during the Initialization State. The Deserializer identifies the rising clock edge in a synchronization pattern or pseudo-random data and after 80 clock cycles will synchronize to the data stream from the Serializer. At the point where the Deserializer's PLL locks to the embedded clock, the LOCKn pin goes low and valid data appears at the outputs.

#### **Data Transfer**

After initialization, the Serializer transfers data to the Deserializer. The serial data stream includes a start and stop bit appended by the serializer, which frames the ten data bits. The start bit is always high and the stop bit is always low. The start and stop bits also function as clock bits embedded in the serial stream.

The Serializer transmits the data and clock bits (10+2 bits) at 12 times the TCLK frequency. For example, if TCLK is 40 MHz, the serial rate is 40 X 12 = 480 Mbps. Since only 10 bits are from input data, the serial 'payload' rate is 10 times the TCLK frequency. For instance, if TCLK = 40 MHz, the payload data is 40 X 10 = 400 Mbps. TCLK is provided by the data source and must be in the range of 16MHz to 66MHz.

When one of six Deserializer channels synchronizes to the input from a Serializer, it drives its  $\overline{\mathsf{LOCKn}}$  pin low and synchronously delivers valid data at its outputs. The Deserializer locks to the embedded clock, uses it to generate multiple internal data strobes, and drives the embedded clock to the RCLKn pin. The RCLKn pin is synchronous to the data on the ROUTn[0:9] pins. While  $\overline{\mathsf{LOCKn}}$  is low, data on ROUTn[0:9] is valid. Otherwise, ROUTn[0:9] and RCLKn are high.

All ROUT,  $\overline{\text{LOCK}}$ , and RCLK signals will drive a minimum of three CMOS input gates (15pF load) with a 66 MHz clock. This amount of drive allows bussing outputs of two Deserializers and a destination ASIC. REN controls TRI-STATE of all the outputs.

The Deserializer input pins are high impedance during Powerdown ( $\overline{PWRDNn}$  or  $\overline{MS\_PWRDN}$  low) and power-off ( $V_{cc}$  = 0V).

## Resynchronization

Whenever one of the six Deserializers loses lock, it will automatically try to resynchronize. For example, if the embedded clock edge is not detected two times in succession, the PLL loses lock and the  $\overline{LOCKn}$  pin is driven high. The system must monitor the  $\overline{LOCKn}$  pin to determine when data is valid.

The user has the choice of allowing the deserializer to re-sync to the data stream or to force synchronization by asserting the Serializer SYNC1 or SYNC2 pin high. This scheme is left up to user discretion. One recommendation is to provide a feedback loop using the  $\overline{\text{LOCKn}}$  pin itself to control the sync request of the Serializer (SYNC1 or SYNC2). Dual SYNC pins are provided for local or remote control..

#### **Powerdown**

The Powerdown state is a low power sleep mode that the Deserializer typically occupies while waiting for initialization or to reduce power consumption when no data is transferred. While in Powerdown Mode, the PLL stops and RCLK and ROUTn[0:9] are high, which reduces the supply current for each channel by approximately 80mA. Each channel has a powerdown (PWRDWNn) pin that puts the respective channel into sleep mode when asserted low. In addition, the SCAN926260 has a master powerdown (MS\_PWRDWN) pin that overrides each individual powerdown pin and puts the entire device into sleep mode when asserted low (This same condition can be replicated by asserting all six individual powerdown pins low.). The powerdown pins are internally pulled low which defaults the device into sleep mode. Active operation requires asserting a high on MS\_PWRDWN and the selected channel's PWRDWNn pin.

Upon exiting Powerdown, the Deserializer enters the Initialization state. The system must then allow time to Initialize before data transfer can begin.

#### **TRI-STATE®**

When the system drives the REN pin low, the Deserializer enters TRI-STATE. This will TRI-STATE the receiver output pins (ROUTn[0:9]) and RCLK[0:5]. When the system drives REN high, the Deserializer will return to the previous state as long as all other control pins remain static ( $\overline{PWRDWN}$ ),  $\overline{MS\_PWRDWN}$ ). The  $\overline{LOCKn}$  pin is not affected by REN and continues to be active, signalling  $\overline{LOCK}$  status. This allows the system to be sure the channel is locked before enabling the data outputs.

# **SCAN926260 Control Signal Truth Table**

|                                         | SCAN Mode Internal Signals INPUTS |           |           |           |     | OUTPUTS |            |         |  |  |

|-----------------------------------------|-----------------------------------|-----------|-----------|-----------|-----|---------|------------|---------|--|--|

| STATE                                   | SCAN_HIZB                         | SCAN_BIST | MS_PWRDWN | PWRDWN[n] | REN | LOCK[n] | ROUTn[0:9] | RCLK[n] |  |  |

| SCAN<br>(Note 1)                        | 0                                 | х         | х         | х         | Х   | Z       | 10 @ Z     | Z       |  |  |

| SCAN<br>(Note 1)                        | 1                                 | 1         | х         | x         | Х   | Z       | 10 @ Z     | Z       |  |  |

| Powerdown<br>(Note 2)                   | 1                                 | 0         | 0         | х         | Х   | 1       | 10 @ 1     | 1       |  |  |

| Powerdown<br>(Note 3)                   | 1                                 | 0         | 1         | All 6 @ 0 | Х   | 1       | 10 @ 1     | 1       |  |  |

| Normal,<br>Not Locked<br>(Note 5)       | 1                                 | 0         | 1         | 1         | 1   | 1       | 10 @ 1     | 1       |  |  |

| Normal,<br>Locked<br>(Note 5)           | 1                                 | 0         | 1         | 1         | 1   | 0       | data       | clock   |  |  |

| REN = Low,<br>Not Locked<br>(Note 4, 6) | 1                                 | 0         | 1         | 1         | 0   | 1       | 10 @ Z     | Z       |  |  |

| REN = Low,<br>Locked<br>(Note 4, 6)     | 1                                 | 0         | 1         | 1         | 0   | 0       | 10 @ Z     | Z       |  |  |

| De                                      | fault State (Note                 | 6)        | 0         | 0         | 0   | 1       | 10 @ 1     | 1       |  |  |

#### Key:

- Z = High Impedance X = Don't Care

- 10 @ Z = All 10 ROUT for the respective Channel are High Impedance

- 1 = High Voltage Level

- 0 = Low Voltage Level

- SCAN\_HIZB = the internal control signal from the HighZ command at the TAP Controller

- SCAN\_BIST = the internal control signal from the BIST command at the TAP Controller

- 1) JTAG/SCAN has the highest priority. SCAN HIZB is active low and SCAN BIST is active high. If either control is active, the outputs will be in TRI-STATE. 2) MS\_PWRDWN has the second highest priority. When MS\_PWRDWN is low, the entire chip enters sleep mode and all outputs (ROUTn[0:9], RCLK[n], and

- 3) PWRDWN[n] are the six individual power-down pins. Each will power down the respective channel. A special case occurs when all six PWRDWN[n] pins are low-the common bias circuits will also be powered down. This state is equivalent to the case when MS\_PWRDWN is low.

- 4) REN has a lower priority than PWRDWN[n]. When REN is low, the output data (ROUTn[0:9] and RCLK[n]) will be in TRI-STATE. The LOCK[n] signal's output is not affected by REN.

- 5) During normal operation mode (no SCAN, no Power-down, and REN high),  $\overline{LOCK[n]}$  controls the ROUTn[0:9] and RCLK[n] outputs. When  $\overline{LOCK[n]}$  is high (unlocked), all outputs will be 1, and when  $\overline{LOCK[n]}$  is low (locked), both data and clock will be valid at the outputs. BIST-ALONE mode is considered part of normal operation and can be overriden by any of the above priorities.

6) There are internal pull-downs on the REN, PWRDWNn and MS\_PWRDWN pins. Active operation requires asserting these pins high.

#### IEEE 1149.1 Test Modes

The SCAN926260 features interconnect test access that is compliant to the IEEE 1149.1 Standard for Boundary Scan Test (JTAG). All digital TTL I/O's on the device are accessible using IEEE 1149.1, and entering this test mode will override all input control cases including power down and REN. In addition to the four required Test Access Port (TAP) signals of TMS, TCK, TDI, and TDO, TRST is provided for test reset.

To supplement the test coverage provided by the IEEE 1149.1 test access to the digital TTL pins, the SCAN926260 has two instructions to test the LVDS interconnects. The first is EXTEST. This is implemented at LVDS levels and is only intended as a go no-go test (e.g. missing cables). The second method is the RUNBIST instruction. It is an "at-system-speed" interconnect test. It is executed in approximately 33ms with a system clock speed of 66MHz. There are 12 bits in the RX BIST data register for notification of PASS/FAIL and TEST\_COMPLETE, with two bits for each of the six channels. The RX BIST register is defined as (from MSB to LSB):

**RX BIST Register**

| TIX BIGT Tiegister           |  |  |  |  |  |

|------------------------------|--|--|--|--|--|

| Description                  |  |  |  |  |  |

| BIST COMPLETE for Channel 6  |  |  |  |  |  |

| BIST PASS/FAIL for Channel 6 |  |  |  |  |  |

| BIST COMPLETE for Channel 5  |  |  |  |  |  |

| BIST PASS/FAIL for Channel 5 |  |  |  |  |  |

| BIST COMPLETE for Channel 4  |  |  |  |  |  |

| BIST PASS/FAIL for Channel 4 |  |  |  |  |  |

| BIST COMPLETE for Channel 3  |  |  |  |  |  |

| BIST PASS/FAIL for Channel 3 |  |  |  |  |  |

| BIST COMPLETE for Channel 2  |  |  |  |  |  |

| BIST PASS/FAIL for Channel 2 |  |  |  |  |  |

| BIST COMPLETE for Channel 1  |  |  |  |  |  |

| BIST PASS/FAIL for Channel 1 |  |  |  |  |  |

|                              |  |  |  |  |  |

A "pass" indicates that the BER (Bit-Error-Rate) is better than 10-7. This is a minimum test, so a "fail" indication means that the BER is higher than 10-7.

The BIST features of the SCAN926260 six channel deserializer are compatible with the BIST features on the DS92LV8028, the SCAN921023 and the SCAN921025 Serializers.

An important detail is that once both devices have the RUN-BIST instruction loaded into their respective instruction registers, both devices must move into the RTI state within 4K system clocks (At a system CLK of 66MHz and TCK of 1MHz this allows for 66 TCK cycles). This is not a concern when both devices are on the same scan chain or LSP. However, it can be a problem with some multi-drop devices. This test mode has been simulated and verified using National's Enhanced SCAN Bridge (SCANSTA111).

#### **BIST Alone Test Modes**

The SCAN926260 also supports a BIST Alone feature which can be run without enabling the JTAG TAP controller. This feature provides the ability to run continuous BER testing on all channels, or on individual channels without affecting live traffic on other channels. The ability to run the BERT (Bit-Error-Rate-Test) while adjacent channels are carrying normal traffic is a useful tool to determine how normal traffic will affect the BER on any given channel.

The BIST Alone features can be accessed using the 5 pins defined as BIST\_SEL0, BIST\_SEL1, BIST\_SEL2, BIST\_ACT, and BISTMODE\_REQ.

BIST\_ACT activates the BIST Alone mode. The BIST Alone mode will continue until deactivated by the BIST\_ACT pin. The BIST\_ACT input must be high or low for four or more clock cycles in order to activate or deactivate the BIST Alone mode. The BIST\_ACT input is pulled low internally.

BISTMODE\_REQ is used to select either gross error reporting or a specific output error report. When the BIST Alone mode is active, the LOCKn output for all channels running BIST Alone will go low and the respective ROUTn(0:9) output will report any errors. When BISTMODE\_REQ is low, the error reporting is set to Gross Mode, and whenever a bit contains one or more errors, ROUT(0:9) for that channel goes high and stays high until deactivation by the BIST\_ACT input. When BISTMODE\_REQ is high, the output error reporting is set to Bit Error mode. Whenever any data bit contains an error, the data output for that corresponding bit goes high. The default setting is Gross Error mode.

The three BIST\_SELn inputs determine which channel is in BIST Alone mode according to the following table:

#### **BIST Alone Mode Selection**

| BIST_ACT | BIST_SEL2 | BIST_SEL1 | BIST_SEL0 | BIST for Channel |

|----------|-----------|-----------|-----------|------------------|

| 1        | 0         | 0         | 0         | 0                |

| 1        | 0         | 0         | 1         | 1                |

| 1        | 0         | 1         | 0         | 2                |

| 1        | 0         | 1         | 1         | 3                |

| 1        | 1         | 0         | 0         | 4                |

| 1        | 1         | 0         | 1         | 5                |

| 1        | 1         | 1         | 0         | All Channels     |

| 1        | 1         | 1         | 1         | IDLE             |

| 0        | Х         | Х         | Х         | IDLE             |

# **Application Information**

#### **USING THE SCAN926260**

The SCAN926260 combines six 1:10 deserializers into a single chip. Each of the six deserializers accepts a BusLVDS data stream up to 660 Mbps from one of National Semiconductor's 10-Bit Serializers. The Deserializers then recover the embedded two clock bits and data to deliver the resulting 10-bit wide words to the output. The Deserializer uses a separate reference clock (REFCLK) and an on-board PLL to extract the clock information from the incoming data stream and then deserialize the data. The Deserializer monitors the incoming clock information, determines lock status, and asserts the LOCKn output high when loss of lock occurs.

#### **POWER CONSIDERATIONS**

An all CMOS design of the Deserializer makes it an inherently low power device.

#### **POWERING UP THE DESERIALIZER**

The SCAN926260 can be powered up at any time. The REFCLK input can be running before the Deserializer powers up, and it must be running in order for the Deserializer to lock to incoming data. The Deserializer outputs (ROUTn[0:9]), the recovered clock (RCLKn), and  $\overline{LOCKn}$  are high until the Deserializer detects data transmission at its inputs and locks to the incoming data stream.

#### **DATA TRANSFER**

Once the Deserializer powers up, it must be phase locked to the transmitter to transfer data. Phase locking occurs when the Deserializer locks to incoming data or when the Serializer sends sync patterns. The Serializer sends SYNC patterns whenever the SYNC1 or SYNC2 inputs are high. The LOCKn output of the Deserializer remains high until it has locked to the incoming data stream. Connecting the LOCKn output of the Deserializer to one of the SYNC inputs of the Serializer will guarantee that enough SYNC patterns are sent to achieve Deserializer lock.

The Deserializer can also lock to incoming data by simply powering up the device and allowing the "lock to pseudo random data" circuitry to find and lock to the data stream.

While the Deserializer LOCKn output is low, data at the respective channel's Deserializer outputs (ROUTn[0:9]) is valid, except for the specific case when loss of lock occurs during transmission which is further discussed in the "Recovering from LOCK Loss" section below.

#### **NOISE MARGIN**

The Deserializer noise margin is the amount of input jitter (phase noise) that the Deserializer can tolerate and still reliably receive data. Various environmental and systematic factors include:

Serializer: TCLK jitter,  $V_{\text{DD}}$  noise (noise bandwidth and out-of-band noise)

Media: ISI, Large  $V_{CM}$  shifts Deserializer:  $V_{DD}$  noise

Please see the section on "Using  $t_{\rm RNM}$  to Validate Signal Quality" for more information.

#### **RECOVERING FROM LOCK LOSS**

In the case where the Deserializer loses lock during data transmission, up to 1 cycle of data that was previously received can be invalid. This is due to the delay in the lock detection circuit. The lock detect circuit requires that invalid clock information be received two times in a row to indicate

loss of lock. Since clock information has been lost, it is possible that data was also lost during these cycles. Therefore, after the Deserializer relocks to the incoming data stream and the Deserializer LOCKn pin goes low, at least one previous data cycle should be suspect for bit errors.

The Deserializer can relock to the incoming data stream by making the Serializer resend SYNC patterns, as described above, or by locking to pseudo random data, which can take more time, depending on the data patterns being received.

#### **HOT INSERTION**

All Bus LVDS Deserializers are hot pluggable if you follow a few rules. When inserting, ensure the Ground pin(s) makes contact first, then the VCC pin(s), and then the I/O pins. When removing, the I/O pins should be unplugged first, then the VCC, then the Ground. Random lock hot insertion is illustrated in Figure 9.

FIGURE 9. Hot Insertion Lock to Pseudo-Random Data

#### TRANSMISSION MEDIA

The Serializer and Deserializer can also be used in point-to-point configurations, through PCB trace, through twisted pair cable, or twinax cables. In point-to-point configurations, the transmission media need only be terminated at the receiver end. Please note that in point-to-point configurations, the potential of offsetting the ground levels of the Serializer vs. the Deserializer must be considered. In some applications, multidrop configurations may be possible. Bus LVDS provides a  $\pm 1.0V$  common mode range at the receiver inputs.

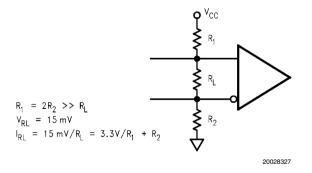

#### **FAILSAFE BIASING FOR THE SCAN926260**

The SCAN926260 has internal failsafe biasing and an improved input threshold sensitivity of  $\pm 50$ mV versus  $\pm 100$ mV for the DS92LV1210.. This allows for a greater differential noise margin. However, in cases where the receiver input is not being actively driven, the increased sensitivity of the SCAN926260 can pickup noise as a signal and cause unintentional locking. For example, this can occur when an input cable is disconnected.

External resistors can be added to the receiver circuit board to boost the level of failsafe biasing. Typically, the non-inverting receiver input is pulled up and the inverting receiver input is pulled down by high value resistors. The pull-up and pull-down resistors (R<sub>1</sub> and R<sub>2</sub>) provide a current path through the termination resistor (R<sub>L</sub>) which biases the receiver inputs when they are not connected to an active driver. The value of the pull-up and pull-down resistors should be chosen so that enough current is drawn to provide a +15mV minimum drop across the termination resistor in the presence of anticipated input noise. Also, in systems where use of the individual channel is well known or controlled, using the respective channel's  $\overline{\rm PWRDWNn}$  pin(s) may eliminate the need for ex-

ternal Failsafe Biasing. Please see Figure 11 for the Failsafe Biasing Setup.

# DIFFERENCES BETWEEN the DS92LV1260, the SCAN921260, and the SCAN926260

The DS92LV1260 is a six channel, ten bit, Bus LVDS Deserializer with random lock capability and a parallel clock rate up to 40MHz. Each channel contains a recovered clock (RCLKn) and lock (LOCKn) output. The DS92LV1260 also contains a seventh serial input channel that serves as a redundant input. Also, unlike previous deserializers, the LOCKn signal is synchronous to valid data appearing on the outputs. Please see the DS92LV1260 datasheet for more specific details about the seventh redundant channel and further details

The SCAN921260 contains the same basic functions as the DS92LV1260. However, the SCAN921260 has an increased parallel clock rate up to 66MHz, is IEEE 1149.1 (JTAG) compliant and also contains at-speed Built-In-Self-Test (BIST).

The SCAN926260 contains the same basic functions as the SCAN921260. However, in addition to a master powerdown, the SCAN926260 has individual powerdown pins per channel, has eliminated the seventh redundant channel, and now asserts all outputs ROUTn[0:9] and RCLKn high during powerdown and during loss of lock. Please also note that the LOCKn pin output is no longer affected by REN. Also, the SCAN926260 is footprint compatible and may be used interchangibly with the SCAN921260.

#### **USING NOISE MARGIN TO VALIDATE SIGNAL QUALITY**

The parameters t<sub>RNMI-LEFT</sub> and t<sub>RNMI-RIGHT</sub> are calculated by first measuring how much of the ideal bit the receiver needs to ensure correct sampling. After determining this amount, what remains of the ideal bit that is available for external sources of noise is called noise margin. Noise margin does not include transmitter jitter. Please see Figure 8 for a graphical explanation. Also, for a more detailed explanation of noise margin, please see Application Note 1217 titled "How to Validate BLVDS SER/DES Signal Integrity Using an Eye Mask." The vertical limits of the mask are determined by the SCAN926260 receiver input threshold of ±50mV.

#### **BYPASS**

Circuit board layout and stack-up for the BLVDS devices should be designed to provide noise-free power to the device. Good layout practice will also separate high-frequency or high-level inputs and outputs to minimize unwanted stray noise pickup, feedback and interference. Power system performance may be greatly improved by using thin dielectrics (4 to 10 mils) for power / ground sandwiches. This increases the intrinsic capacitance of the PCB power system which improves power supply filtering, especially at high frequencies, and makes the value and placement of external bypass capacitors less critical. External bypass capacitors should include both RF ceramic and tantalum electrolytic types. RF capacitors may use values in the range of 0.01 uF to 0.1 uF. Tantalum capacitors may be in the 2.2 uF to 10 uF range. Voltage rating of the tantalum capacitors should be at least 3X the power supply voltage being used.

It is a recommended practice to use two vias at each power pin as well as at all RF bypass capacitor terminals. Dual vias reduce the interconnect inductance by up to half, thereby reducing interconnect inductance and extending the effective frequency range of the bypass components. Locate RF capacitors as close as possible to the supply pins, and use wide low impedance traces (not 50 Ohm traces). Surface mount capacitors are recommended due to their smaller parasitics.

When using multiple capacitors per supply pin, locate the smaller value closer to the pin. A large bulk capacitor is recommend at the point of power entry. This is typically in the 50uF to 100uF range and will smooth low frequency switching noise

Some devices provide separate power and ground pins for different portions of the circuit. This is done to isolate switching noise effects between different sections of the circuit. Separate planes on the PCB are typically not required. Pin Description tables typically provide guidance on which circuit blocks are connected to which power pin pairs. In some cases, an external filter may be used to provide clean power to sensitive circuits such as PLL circuitry.

Use at least a four layer board with a power and ground plane. Locate CMOS (TTL) signals away from the LVDS lines to prevent coupling. Closely-coupled differential lines of 100 Ohms  $Z_{\rm DIFF}$  are typically recommended for LVDS interconnects. The closely-coupled lines help to ensure that coupled noise will appear as common-mode and is rejected by the receivers. Also, the tight coupled lines will radiate less.

Termination of the LVDS interconnect is required. For point-to-point applications, termination should be located at the load end. Nominal value is 100 Ohms to match the line's differential impedance. Place the resistor as close to the receiver inputs as possible to minimize the resulting stub between the termination resistor and receiver.

Additional general guidance can be found in the LVDS Owner's Manual - available in PDF format from the national web site at: www.national.com/lvds. For packaging information on BGA's, please see AN-1126.

Guidance for the SCAN926260 is provided next:

#### SCAN926260: SIX 1 TO 10 DESERIALIZERS

General guidance is provided below. Exact guidance can not be given as it is dictated by other board level /system level criteria. This includes the density of the board, power rails, power supply, and other integrated circuit power supply needs

#### **DVDD = DIGITAL SECTION POWER SUPPLY**

These pins supply the digital portion and receiver output buffers of the device. Receiver DVDD pins require more bypass to power outputs under synchronous switching conditions. An estimate of local capacitance requires a minimum of 20nF. This is calculated by taking 66 (60 LVTTL Outputs + 6 RCLK Outputs) times the maximum output short circuit current (IOS) of 85mA. Multiplying this number by the maximum rise time (t<sub>CLH</sub>) of 4ns and dividing by the maximum allowed droop in VDD (assume 50mV) yields 448.8nF. Dividing this number by the number of DVDD pins (25) yields 18nF. Rounding up to a standard value, 0.1uF is selected for each DVDD pin. The capacitative bandwidth for this capacitor may be extended by placing a 0.01uF capacitor in parallel. The 0.01uF capacitor should be placed closer to the DVDD pin than the 0.1uF capacitor.

#### **PVDD = PLL SECTION POWER SUPPLY**

The PVDD pin supplies the PLL circuit. PLL circuits require clean power for the minimization of jitter. A supply noise frequency in the 300kHZ to 1MHz range can cause increased output jitter. Certain power supplies may have switching frequencies or high harmonic content in this range. If this is the case, filtering of this noise spectrum may be required. A notch filter response is best to provide a stable VDD, suppression of the noise band, and good high-frequency response (clock fundamental). This may be accomplished with a pie filter

(CRC or CLC). If employed, a separate pie filter is recommended for each PLL to minimize drop in potential due to the series resistance. Separate power planes for the PVDD pins is typically not required.

#### AVDD = LVDS SECTION POWER SUPPLY

The AVDD pin supplies the LVDS portion of the circuit. The SCAN926260 has four AVDD pins. Due to the nature of the design, current draw is not excessive on these pins. A 0.1uF capacitor is sufficient for these pins. If space is available, the 0.01uF capacitor may be used in parallel with the 0.1uF capacitor for additional high frequency filtering.

#### **GROUNDs**

The AGND pin should be connected to the signal common in the cable for the return path of any common-mode current. Most of the LVDS current will be odd-mode and return within the interconnect pair. A small amount of current may be even-mode due to coupled noise and driver imbalances. This current should return via a low impedance known path.

For a typical application circuit, please see Figure 10.

FIGURE 10. Typical Application Circuit

(Only one power/ground for each supply type shown for clarity-bypass networks should be repeated for all power/ground pairs.)

FIGURE 11. Optional Additional External Failsafe Biasing

# Pin Diagram

#### Top View of SCAN926260TUF (196 pin LBGA)

|                       |                     |                     |                    | TOP VI              | ew or Su                                         | JAN926             | 260 I UF           | (196 bii            | n LBGA             | )                   |                     |                     |                                |

|-----------------------|---------------------|---------------------|--------------------|---------------------|--------------------------------------------------|--------------------|--------------------|---------------------|--------------------|---------------------|---------------------|---------------------|--------------------------------|

| (A1)                  | (A2)                | (A3)                | (A4)               | (A5)                | (A6)                                             | (A7)               | (A8)               | (A9)                | (A 1 0)            | (A 1 1)             | (A 1 2)             | (A 1 3)             | (A14)                          |

| DGND                  | REN                 | R <sub>INO</sub> -  | R <sub>INO</sub> + | AGND                | R <sub>IN2</sub> -                               | R <sub>IN2</sub> + | AGND               | R <sub>IN4</sub> -  | R <sub>IN4</sub> + | AVDD                | PWRDWN*1            | PWRDWN*             | 0 PGND                         |

| (B1)                  | (B2)                | (B3)                | (B4)               | (B5)                | (B6)                                             | (B7)               | (B8)               | (B9)                | (B10)              | (B11)               | (B12)               | (B13)               | (B14)                          |

| $DV_DD$               | GND                 | $DV_{DD}$           | REFCLK N           | IS_PWRDWI           | N* AVDD                                          | AGND               | AGND               | AV <sub>DD</sub> BI | STMODE_R           | EQ AGND             | PGND                | N/C                 | GND                            |

| (C1)                  | (C2)                | (C3)                | (C4)               | (C5)                | (C6)                                             | (C7)               | (C8)               | (C9)                | (C10)              | (C 1 1)             | (C12)               | (C13)               | (C14)                          |

| TMS                   | TRST*               | PWRDWN*2            | $DV_{DD}$          | R <sub>IN 1</sub> - | R <sub>IN 1</sub> +                              | $AV_{DD}$          | R <sub>IN3</sub> - | R <sub>IN3</sub> +  | R <sub>IN5</sub> - | R <sub>IN5</sub> +  | PWRDWN*5            | N/C                 | BIST_SEL2                      |

| (D1)                  | (D2)                | (D3)                | D4                 | (D5)                | D6                                               | (D7)               | (D8)               | (D9)                | (D10)              | (D11)               | (D12)               | (D13)               | (D14)                          |

| TDI                   | TCK                 | TDO                 | DGND               | DGND                | $DV_DD$                                          | DGND               | BIST_SEL0          | DGND                | PGND               | DGND                | $OV_{DD}$           | LOCK <sub>5</sub> * | BIST_SEL1                      |

| E1                    | E2                  | E3                  | E4                 | (E5)                | E6                                               | (E7)               | (E8)               | E9                  | E10                | (E11)               | E 12                | E13                 | (E 14)                         |

| $PV_{DD}$             | R <sub>OUTO9</sub>  | N/C                 | R <sub>OUTO8</sub> | DGND                | $DV_DD$                                          | $DV_DD$            | DGND               | $DV_DD$             | $DV_DD$            | PWRDWN*3            | R <sub>OUT57</sub>  | R <sub>OUT58</sub>  | R <sub>OUT59</sub>             |

| (F1)                  | (F2)                | F3                  | (F4)               | (F5)                | (F6)                                             | F7                 | (F8)               | F9                  | (F10)              | (F11)               | (F12)               | (F13)               | (F 1 4)                        |

| PVDD                  | RCLK <sub>0</sub>   | LOCK <sub>0</sub> * | R <sub>OUT07</sub> | DGND                | DGND                                             | DV <sub>DD</sub>   | DGND               | DGND                | DV <sub>DD</sub>   | PWRDWN*4            | $DV_{DD}$           | RCLK <sub>5</sub>   | PVDD                           |

| (G1)                  | (G2)                | (G3)                | (G4)               | (G5)                | (G6)                                             | (G7)               | (68)               | (G9)                | (G10)              | (G11)               | (G12)               | (G13)               | G 1 4                          |

| PGND                  | PGND                | R <sub>OUTO6</sub>  | R <sub>OUTO5</sub> | DGND                | $\overline{DV_{DD}}$                             | DGND               | DGND               | DGND                | DV <sub>DD</sub>   | R <sub>OUT55</sub>  | R <sub>OUT56</sub>  | PGND                | PV <sub>DD</sub>               |

| (H1)                  | (H2)                | (H3)                | (H4)               | (H5)                | (H6)                                             | (H7)               | (H8)               | (H9)                | (H10)              | (H11)               | (H 1 2)             | (H13)               | (H 1 4)                        |

| PGND                  | R <sub>OUTO4</sub>  | R <sub>OUTO2</sub>  | R <sub>OUTO3</sub> | DGND                | $DV_{DD}$                                        | DGND               | DGND               | DGND                | DV <sub>DD</sub>   | R <sub>OUT54</sub>  | R <sub>OUT53</sub>  | PGND                | PGND                           |

| $\left( J_{1}\right)$ | $\left( J2\right)$  | $\left( J3\right)$  | $\left( J4\right)$ | (J5)                | $\left( \begin{array}{c} 16 \end{array} \right)$ | (J7)               | (J8)               | (J9)                | (J10)              | $\left( J11\right)$ | (J12)               | (J13)               | (J 1 4)                        |

| PV <sub>DD</sub>      | R <sub>OUT12</sub>  | R <sub>OUT10</sub>  | PGND               | DV <sub>DD</sub>    | DGND                                             | DGND               | DV <sub>DD</sub>   | DV <sub>DD</sub>    | DV <sub>DD</sub>   | R <sub>OUT52</sub>  | R <sub>OUT51</sub>  | PGND                | PV <sub>DD</sub>               |

| (K1)                  | (K2)                | (K3)                | (K4)               | (K5)                | (K6)                                             | (K7)               | (K8)               | (K9)                | (K10)              | (K11)               | (K12)               | (K13)               | (K14)                          |

| $PV_{DD}$             | R <sub>OUT14</sub>  | R <sub>OUTOO</sub>  | R <sub>OUTO1</sub> | DV <sub>DD</sub>    | $DV_DD$                                          | DV <sub>DD</sub>   | DGND               | DGND                | DV <sub>DD</sub>   | BIST_ACT            | R <sub>OUT50</sub>  | R <sub>OUT40</sub>  | PV <sub>DD</sub>               |

| (L1)                  | (L2)                | (L3)                | (L4)               | (L5)                | (F8)                                             | (L7)               | (L8)               | (L9)                | (L10)              | (L11)               | (L12)               | (L13)               | (L14)                          |

| R <sub>OUT13</sub>    | RCLK <sub>1</sub>   | R <sub>OUT11</sub>  | GND                | GND                 | R <sub>OUT21</sub>                               | DGND               | R <sub>OUT31</sub> | R <sub>OUT34</sub>  | DV <sub>DD</sub>   | R <sub>OUT45</sub>  | R <sub>OUT41</sub>  | R <sub>OUT44</sub>  | R <sub>OUT42</sub>             |

| (M1)                  | (M2)                | (M3)                | (M4)               | (M5)                | (M6)                                             | (M7)               | (M8)               | (M9)                | (M10)              | (M11)               | (M 1 2)             | (M13)               | (M14)                          |

| R <sub>OUT15</sub>    | R <sub>OUT 18</sub> | R <sub>OUT19</sub>  | R <sub>OUT29</sub> | R <sub>OUT25</sub>  | R <sub>OUT23</sub>                               | R <sub>OUT20</sub> | R <sub>OUT30</sub> | R <sub>OUT33</sub>  | R <sub>OUT35</sub> | R <sub>OUT36</sub>  | R <sub>OUT46</sub>  | RCLK <sub>4</sub>   | R <sub>OUT43</sub>             |

| $\binom{N1}{}$        | $\binom{N2}{}$      | (N3)                | (N4)               | (N5)                | (N6)                                             | (N7)               | (N8)               | (N9)                | (N10)              | (N11)               | (N 1 2)             | (N13)               | (N 1 4)                        |

| R <sub>OUT16</sub>    | R <sub>OUT 17</sub> | LOCK <sub>2</sub> * | R <sub>OUT27</sub> | RCLK <sub>2</sub>   | R <sub>OUT22</sub>                               | PGND               | PGND               | R <sub>OUT32</sub>  | RCLK <sub>3</sub>  | R <sub>OUT37</sub>  | R <sub>OUT39</sub>  | R <sub>OUT47</sub>  | R <sub>OUT48</sub>             |

| (P1)                  | (P2)                | (P3)                | (P4)               | (P5)                | (P6)                                             | (P7)               | (P8)               | (P9)                | (P10)              | (P11)               | (P12)               | (P13)               | (P14)                          |

| LOCK <sub>1</sub> *   | R <sub>OUT28</sub>  | R <sub>OUT26</sub>  | R <sub>OUT24</sub> | $PV_{DD}$           | PVDD                                             | PGND               | PGND               | $PV_{DD}$           | $PV_{DD}$          | R <sub>OUT38</sub>  | LOCK <sub>3</sub> * | LOCK <sub>4</sub> * | R <sub>OUT49</sub><br>20028314 |

| * 0///                | <u> </u>            |                     |                    |                     |                                                  |                    |                    |                     |                    |                     |                     |                     | 20020014                       |

Note:  $* = \overline{OVERBAR}$

# **Pin Descriptions**

| Pin Name           | Туре                | Pins                                                                                                                                                                                                                                                                    | Description                                                                                                                                                                                                                                                                                                     |

|--------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GND                | GND                 | B2, B14, L4, L5                                                                                                                                                                                                                                                         | Ground pins for ESD structures.                                                                                                                                                                                                                                                                                 |

| R <sub>INn</sub> ± | Bus LVDS<br>Input   | A3-A4, A6-A7, A9-10, C5-<br>C6, C8-C9, C10-C11                                                                                                                                                                                                                          | Bus LVDS differential input pins. Failsafe described in Application Information section.                                                                                                                                                                                                                        |

| N/C                |                     | E3                                                                                                                                                                                                                                                                      | This pin is not bonded out. Therefore, you may tie this pin High, Low, or as a N/C. However, for board layout compatibility with the SCAN921260 or the DS92LV1260, tie this pin LOW.                                                                                                                            |

| DVdd               |                     | B1, B3, C4, D6, D12, E6,<br>E7, E9, E10, F7, F10, F12,<br>G6, G10, H6, H10, J5, J8,<br>J9, J10, K5, K6, K7, K10,<br>L10                                                                                                                                                 | Supply voltage for digital section.                                                                                                                                                                                                                                                                             |

| DGND               |                     | A1, D4, D5, D7, D9, D11,<br>E5, E8, F5, F6, F8, F9, G5,<br>G7, G8, G9, H5, H7, H8, H9,<br>J6, J7, K8, K9, L7                                                                                                                                                            | Ground pins for digital section.                                                                                                                                                                                                                                                                                |

| PVdd               |                     | E1, F1, F14, G14, J1, J14,<br>K1, K14,P5, P6, P9, P10                                                                                                                                                                                                                   | Supply voltage for PLL circuitry.                                                                                                                                                                                                                                                                               |

| PGND               |                     | A14, B12, D10, G1, G2,<br>G13, H1, H13, H14, J4, J13,<br>N7, N8, P7, P8                                                                                                                                                                                                 | Ground pins for PLL circuitry.                                                                                                                                                                                                                                                                                  |

| AVdd               |                     | A11, B6, B9, C7                                                                                                                                                                                                                                                         | Supply voltage for analog circuitry.                                                                                                                                                                                                                                                                            |

| AGND               |                     | A5, A8, B7, B8, B11                                                                                                                                                                                                                                                     | Ground pins for analog circuitry.                                                                                                                                                                                                                                                                               |

| PWRDWN [0:5]       | 3.3V CMOS<br>Input  | A12, A13, C3, C12, E11,<br>F11                                                                                                                                                                                                                                          | A low on one of these pins puts the corresponding channel into sleep mode and a high makes the corresponding channel active. There is an internal pull-down on each of these pins that defaults the PWRDWNn input to sleep mode. Active operation requires asserting a high on the PWRDWNn and MS_PWRDWN input. |

| MS_PWRDWN          | 3.3V CMOS<br>Input  | B5                                                                                                                                                                                                                                                                      | A low on this pin puts the device into sleep mode and a high makes the part active. There is an internal pull-down that defaults the MS_PWRDWNn input to sleep mode. Active operation requires asserting a high on the MS_PWRDWNn input.                                                                        |

| REN                | 3.3V CMOS<br>Input  | A2                                                                                                                                                                                                                                                                      | Enables the ROUTn[0:9], RCLKn, outputs. There is an internal pull-down that defaults REN to TRI-STATE the outputs. Active outputs require asserting a high on REN. Please note that LOCKn is not affected by REN.                                                                                               |

| REFCLK             | 3.3V CMOS<br>Input  | B4                                                                                                                                                                                                                                                                      | Frequency reference input. Used by the PLL while locking onto incoming LVDS streams. Has no phase relation to RCLK.                                                                                                                                                                                             |

| LOCK[0:5]          | 3.3V CMOS<br>Output | D13, F3, N3, P1, P12, P13                                                                                                                                                                                                                                               | Indicates the status of the PLLs for the individual deserializers:<br>\overline{LOCKn} = L indicates locked, \overline{LOCKn} = H indicates unlocked.                                                                                                                                                           |

| ROUTn[0:9]         | 3.3V CMOS<br>Output | E2, E4, E12, E13, E14, F4, G3, G4, G11, G12, H2, H3, H4, H11, H12, J2, J3, J11, J12, K2, K3, K4, K12, K13, L1, L3, L6, L8, L9, L11, L12, L13, L14, M1, M2, M3, M4, M5, M6, M7, M8, M9, M10, M11, M12, M14, N1, N2, N4, N6, N9, N11, N12, N13, N14, P2, P3, P4, P11, P14 | Outputs for the ten bit deserializers; n = deserializer number. When a channel is not locked, ROUT[0:9] are high for that channel.                                                                                                                                                                              |

| RCLK[0:5]          | 3.3V CMOS<br>Output | F2, F13, L2, M13,N5, N10                                                                                                                                                                                                                                                | Recovered clock for each deserializer's output data. When a channel is not locked, the RCLK for that channel is high.                                                                                                                                                                                           |

| Pin Name      | Type                | Pins         | Description                                                                                                                                                                                                                                                                                                          |

|---------------|---------------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pili Name     | Туре                | PIIIS        | -                                                                                                                                                                                                                                                                                                                    |

| TMS           | 3.3V CMOS<br>Input  | C1           | Test Mode Select input to support IEEE 1149.1. There is a weak internal pull-up on TMS that defaults TRST, TDI, TCK and TDO to be inactive. However, in noisy environments, pulling TMS high ensures the JTAG test access port (TAP) is never activated.                                                             |

| TRST          | 3.3V CMOS<br>Input  | C2           | Test Reset Input to support IEEE 1149.1. There is a weak internal pull-up on this pin.                                                                                                                                                                                                                               |

| TDI           | 3.3V CMOS<br>Input  | D1           | Test Data Input to support IEEE 1149.1. There is a weak internal pull-up on this pin.                                                                                                                                                                                                                                |

| тск           | 3.3V CMOS<br>Input  | D2           | Test Clock to support IEEE 1149.1                                                                                                                                                                                                                                                                                    |

| TDO           | 3.3V CMOS<br>Output | D3           | Test Data Output to support IEEE 1149.1.                                                                                                                                                                                                                                                                             |

| BISTMODE_REQ  | 3.3V CMOS<br>Input  | B10          | BIST Alone Error Reporting Mode Select Input.                                                                                                                                                                                                                                                                        |

| BIST_SEL[0:2] | 3.3V CMOS<br>Input  | C14, D8, D14 | These pins control which channels are active for the BIST Alone operating mode. The BIST Alone Mode Selection Table describes their function. There are internal pull-ups that default all BIST_SEL[0:2] to high, which is the idle state for all channels in the BIST Alone mode.                                   |

| BIST_ACT      | 3.3V CMOS<br>Input  | K11          | A high on this pin activates the BIST Alone operating mode. There is a weak internal pull-down that should default the BIST_ACT to de-activate the BIST Alone operating mode. In a noisy operating environment, it is recommended that an external pull down be used to ensure that BIST_ACT stays in the low state. |

| N/C           |                     | B13, C13     | Unused solder ball location. Do not connect.                                                                                                                                                                                                                                                                         |

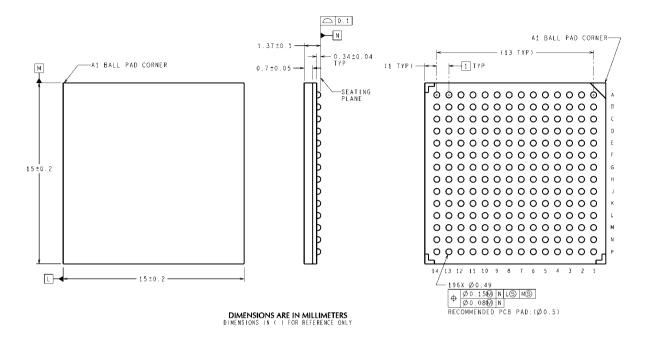

# Physical Dimensions inches (millimeters) unless otherwise noted

UJB196A (Rev C)

Order Number SCAN926260TUF (Tray) Order Number SCAN926260TUFX (Tape and Reel) NS Package Number UJB196A

## **Notes**

For more National Semiconductor product information and proven design tools, visit the following Web sites at:

| Pr                             | oducts                       | Design Support          |                                |  |  |

|--------------------------------|------------------------------|-------------------------|--------------------------------|--|--|

| Amplifiers                     | www.national.com/amplifiers  | WEBENCH                 | www.national.com/webench       |  |  |

| Audio                          | www.national.com/audio       | Analog University       | www.national.com/AU            |  |  |

| Clock Conditioners             | www.national.com/timing      | App Notes               | www.national.com/appnotes      |  |  |

| Data Converters                | www.national.com/adc         | Distributors            | www.national.com/contacts      |  |  |

| Displays                       | www.national.com/displays    | Green Compliance        | www.national.com/quality/green |  |  |

| Ethernet                       | www.national.com/ethernet    | Packaging               | www.national.com/packaging     |  |  |

| Interface                      | www.national.com/interface   | Quality and Reliability | www.national.com/quality       |  |  |

| LVDS                           | www.national.com/lvds        | Reference Designs       | www.national.com/refdesigns    |  |  |

| Power Management               | www.national.com/power       | Feedback                | www.national.com/feedback      |  |  |

| Switching Regulators           | www.national.com/switchers   |                         |                                |  |  |

| LDOs                           | www.national.com/ldo         |                         |                                |  |  |

| LED Lighting                   | www.national.com/led         |                         |                                |  |  |

| PowerWise                      | www.national.com/powerwise   |                         |                                |  |  |

| Serial Digital Interface (SDI) | www.national.com/sdi         |                         |                                |  |  |

| Temperature Sensors            | www.national.com/tempsensors |                         |                                |  |  |