Click here to ask an associate for production status of specific part numbers.

## **Ultra-Low Quiescent Current PMIC with** SIMO Buck-Boost for Wearable Applications

### MAX20310

#### **General Description**

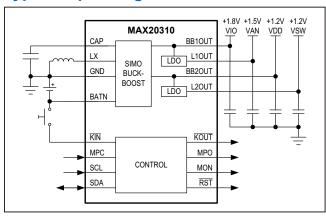

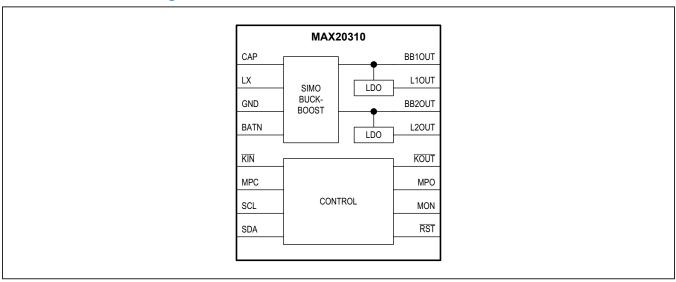

The MAX20310 is a compact power management integrated circuit (PMIC) for space-constrained, batterypowered applications where size and efficiency are critical. The device combines two single inductor, multiple output (SIMO) buck-boosted outputs with two LDOs and other system power management features like a push-button monitor and sequencing controller.

The device includes a SIMO buck-boost switching regulator that provides two programmable voltage rails using a single inductor, minimizing solution footprint. The MAX20310 operates with battery voltages down to 0.7V for use with Zinc Air, Silver Oxide, or Alkaline batteries. The architecture allows for output voltages above or below the battery voltage.

Additionally, the MAX20310 has two programmable lowdropout (LDO) linear regulators. The linear regulators can also operate as power switches that can disconnect the quiescent load of system peripherals.

The MAX20310 includes a programmable power controller that allows the device to be configured for use in applications that require a true off state or for always-on applications. This controller provides a delayed reset signal, voltage sequencing, and customized button timing for on/off control and recovery hard reset.

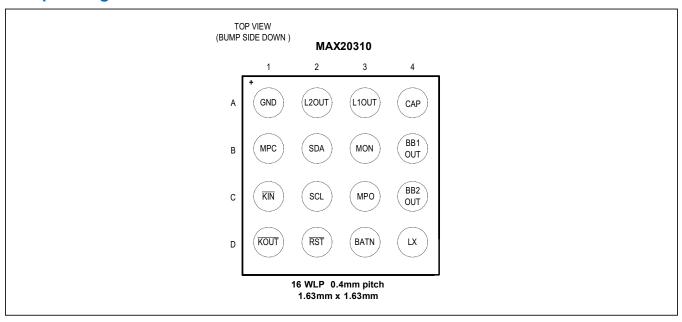

The device also features a multiplexer for monitoring the power inputs and outputs of each function. The MAX20310 is available in a 16-bump 0.4mm pitch 1.63mm x 1.63mm wafer-level package (WLP) and operates over the -40°C to +85°C extended temperature range.

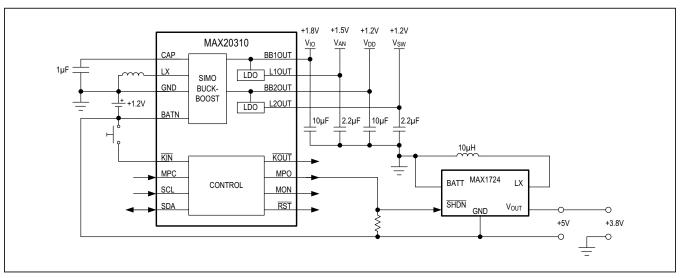

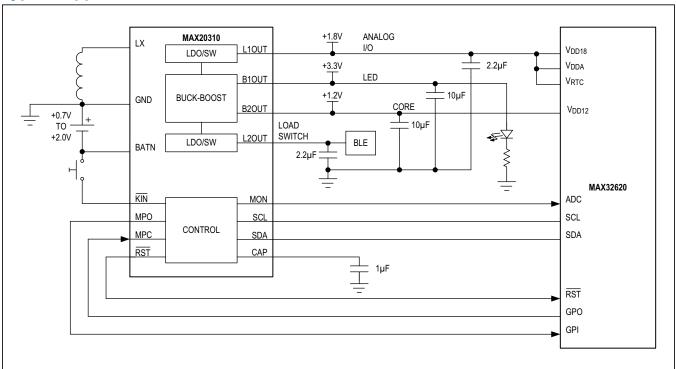

## **Typical Operating Circuit**

#### **Benefits and Features**

- Extend System Battery Use Time

- · Single Inductor, Multiple Output (SIMO) Ultra-Low IO Buck-Boost Regulator

- Battery Input Voltage from 0.7V to 2.0V

- Output Voltage Programmable From 0.9V to 4.05V

- 250mW Maximum Total Input Power

- Incremental CAP Quiescent Current 1µA per

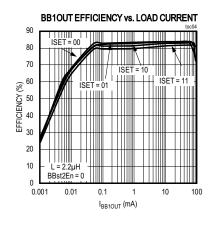

- 84% Efficiency for 1.8V, 10mA Output

- Input Current Limited

- Dual Ultra-Low I<sub>O</sub> 50mA LDO

- Inputs Supplied by Dual Buck-Boost Outputs

- Output Programmable from 0.5V to 3.65V

- Quiescent Current 1.1µA per LDO / 600nA per Load Switch

- Configurable as Load Switch

- Extend Product Shelf-Life

- · Battery Seal Mode

- 10nA Battery Current (typ)

- Minimize Board Area

- 1.63mm x 1.63mm WLP

- Easy-to-Implement System Control

- Voltage Monitor Multiplexer

- 1% Accurate Battery Inverter (±10mV at 1.0V)

- Power Button Monitor

- Buffered Output

- Power Sequencing

- Reset Output

- I<sup>2</sup>C Control Interface

#### **Applications**

- Wearable Medical Devices

- Wearable Fitness Devices

- Portable Medical Devices

Ordering Information appears at end of data sheet.

19-8611: Rev 3: 12/21

#### **MAX20310**

# Ultra-Low Quiescent Current PMIC with SIMO Buck-Boost for Wearable Applications

### **Absolute Maximum Ratings**

| (Voltages reference to GND unless otherwise noted) CAP, BB1OUT, BB2OUT, L1OUT, L2OUT |

|--------------------------------------------------------------------------------------|

| MPC, SDA, SCL, $\overline{RST}$ , $\overline{KOUT}$ to GND, BATN0.3V to +6V          |

|                                                                                      |

| KIN(BATN – 0.3V) to (GND + 0.3V)                                                     |

| LX to BATN0.3V to +6V                                                                |

| MPO, MON to BATIN0.3V to +6V                                                         |

| GND to BATN0.3V to +2.2V                                                             |

| Continuous Current into LX, BATN+0.5A                                                |

| Continuous Current into any other terminal             | ±100mA     |

|--------------------------------------------------------|------------|

| Continuous Power Dissipation (T <sub>A</sub> = +70°C): |            |

| 16-bump WLP 1.65mm x 1.65mm 0.4mm Pitch                |            |

| (derate 17.4mW/°C above +70°C)                         | 957mW      |

| Operating Temperature Range40°                         | C to +85°C |

| Junction Temperature                                   | +150°C     |

| Storage Temperature Range65°C                          | to +150°C  |

| Soldering Temperature (reflow)                         | +260°C     |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only; functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Package Information**

| PACKAGE TYPE: 16 WLP                               |          |  |  |  |  |

|----------------------------------------------------|----------|--|--|--|--|

| Package Code                                       | W161F1+1 |  |  |  |  |

| Outline Number                                     | 21-0491  |  |  |  |  |

| Land Pattern Number Refer to Application Note 1891 |          |  |  |  |  |

| THERMAL RESISTANCE, FOUR-LAYER BOARD               |          |  |  |  |  |

| Junction to Ambient (θ <sub>JA</sub> )             | 58°C/W   |  |  |  |  |

For the latest package outline information and land patterns (footprints), go to <a href="www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

#### **Electrical Characteristics**

$(V_{BAT} = +1.2V, V_{BB1OUT} = +1.8V, V_{BB2OUT} = +1.2V, V_{L1OUT} = +1.5V, V_{L2OUT} = +1.0V, I_{BB1OUT} = I_{BB2OUT} = I_{L1OUT} = I_{L2OUT} = 0A, T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ all registers in their default state, unless otherwise noted. Typical values are at } T_A = +25^{\circ}C) \text{ (Note 1) (Note 2)}$

| PARAMETER                              | SYMBOL                      | CONDITIONS                                                   | MIN  | TYP  | MAX  | UNITS |

|----------------------------------------|-----------------------------|--------------------------------------------------------------|------|------|------|-------|

| SUPPLY CURRENT                         | I                           |                                                              |      |      |      |       |

| Seal Input Current                     | I <sub>SEAL</sub>           | Seal mode, all functions disabled,<br>T <sub>A</sub> = +25°C |      | 0.01 | 0.2  | μА    |

| KIN Pullup Resistor to GND             | KIN <sub>PULLUP</sub>       |                                                              |      | 465  |      | kΩ    |

|                                        |                             | Buck-boost 1 enabled                                         |      | 4    |      | μA    |

| CAP Quiescent Current                  |                             | Buck-boost 1 and 2 enabled                                   |      | 5    |      | μA    |

| CAP Quiescent Current                  | I <sub>Q_CAP</sub>          | Buck-boost 1 and 2 and LDO 1 enabled                         |      | 5.25 |      | μA    |

|                                        |                             | Buck-boost 1 and 2 and LDO 1 and 2 enabled                   |      | 5.5  |      | μA    |

| POWER SEQUENCE                         |                             |                                                              |      |      |      |       |

| Reset Time Accuracy                    | t <sub>RST</sub>            |                                                              | -10  |      | +10  | %     |

| BUCK-BOOST REGULA                      | TOR                         |                                                              |      |      |      |       |

| Input Voltage                          | V <sub>BAT</sub>            | Operating                                                    | 0.7  |      | 2    | V     |

|                                        | · DAI                       | Startup                                                      | 0.8  |      | 2    |       |

| Output Voltage Range                   | V <sub>OUT</sub>            | 50mV steps, (Note 3)                                         | 0.9  |      | 4.05 | V     |

| Quiescent Supply<br>Current From CAP   | I <sub>Q_BB</sub>           | Burst mode, no switching, V <sub>BB_OUT</sub> = +1.8V        |      | 1    |      | μА    |

|                                        |                             | T <sub>A</sub> = +25°C                                       | -1   |      | 1    |       |

| Output Accuracy                        | V <sub>OUT_ACC_BB_OUT</sub> | T <sub>A</sub> = 0°C to +85°C                                | -1.8 |      | +1.8 | %     |

|                                        |                             | T <sub>A</sub> = -40°C to +85°C                              | -3   |      | +3   |       |

| Power Supply Rejection Ratio           | PSRR                        | C <sub>BB_OUT</sub> = 10µF                                   |      | 40   |      | dB    |

| Maximum Input Power                    | P <sub>IN</sub>             | (Note 5)                                                     | 250  |      |      | mW    |

| Maximum Input Current                  | 1                           | V <sub>BB_OUT</sub> = +1.8V                                  |      | 200  |      | m A   |

| Maximum Input Current                  | I <sub>IN</sub>             | V <sub>BB_OUT</sub> = +3.3V                                  |      | 244  |      | mA    |

| Short-Circuit Current<br>Limit         | I <sub>LIM</sub>            | Maximum programmable current setting                         |      | 0.6  |      | А     |

| Passive Discharge<br>Resistance        | R <sub>PAS_BB_OUT</sub>     |                                                              |      | 10   |      | kΩ    |

| LDO                                    |                             |                                                              |      |      |      |       |

| Quiescent Supply                       |                             | LDO UVLO enabled                                             |      | 1.1  | 2    |       |

| Current                                | IQ_LDO                      | Switch mode, V <sub>BB_OUT</sub> = +1.8V                     |      | 0.4  |      | μA    |

| Quiescent supply<br>Current in Dropout | IQ_LDO_D                    | V <sub>BB_OUT</sub> = V <sub>LDO_SET</sub> - 0.1V            |      | 1.7  | 3.5  | μА    |

| Maximum Output<br>Current              | I <sub>MAX_LDO</sub>        | (Note 4)                                                     | 50   |      |      | mA    |

| Output Voltage                         | V <sub>OUT_LDO</sub>        | 50mV steps                                                   | 0.5  |      | 3.65 | V     |

## **Electrical Characteristics (continued)**

$(V_{BAT} = +1.2V, V_{BB1OUT} = +1.8V, V_{BB2OUT} = +1.2V, V_{L1OUT} = +1.5V, V_{L2OUT} = +1.0V, I_{BB1OUT} = I_{BB2OUT} = I_{L1OUT} = I_{L2OUT} = 0A, T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ all registers in their default state, unless otherwise noted. Typical values are at } T_A = +25^{\circ}C) \text{ (Note 1) (Note 2)}$

| PARAMETER                                              | SYMBOL                 | COI                                                         | NDITIONS              | MIN  | TYP   | MAX  | UNITS            |

|--------------------------------------------------------|------------------------|-------------------------------------------------------------|-----------------------|------|-------|------|------------------|

| Output Accuracy                                        | Vout acc ldo           | V <sub>BB_OUT</sub> = (V <sub>LDO_SET</sub> +               | $T_A = 0$ °C to +85°C | -3   |       | 3    | %                |

| Curput/toourdoy                                        | *OOT_ACC_LDO           | 0.5V) or higher,<br>$I_{LOAD}$ = 1mA $T_A$ = -40°C to +85°C |                       | -3.5 |       | +3.5 | ,,               |

| Dropout Voltage                                        | V <sub>DROP_LDO</sub>  | $V_{BB\_OUT} = V_{LDC}$ $I_{LOAD} = 50$ mA                  | _SET = +1.8V,         |      |       | 100  | mV               |

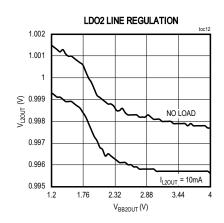

| Line Regulation                                        | LINEREG <sub>LDO</sub> | V <sub>BB_OUT</sub> = (V <sub>LD0</sub><br>+4.05V           | D_SET + 0.5V) to      | -1   |       | 1    | %/V              |

| Load Regulation                                        | LOADREG <sub>LDO</sub> | $I_{LOAD} = 50\mu A \text{ to } $                           | 50mA                  |      | 0.003 |      | %/mA             |

| Passive Discharge<br>Resistance                        | R <sub>PAS_LDO</sub>   |                                                             |                       |      | 10    |      | kΩ               |

| Power Switch Mode<br>Resistance                        | R <sub>ON_LS</sub>     | V <sub>BB_OUT</sub> = +1.2\                                 | /                     |      |       | 1    | Ω                |

| T. 0 T                                                 |                        | I <sub>LDO_OUT</sub> = 0mA                                  |                       |      | 0.7   |      | \// <sub>1</sub> |

| Turn-On Time                                           | <sup>t</sup> ON_SLOPE  | I <sub>LDO_OUT</sub> = 0mA                                  | . Switch mode.        |      | 2.8   |      | V/µs             |

| Thermal Shutdown Threshold                             | T <sub>SD</sub>        | T <sub>J</sub> rising                                       |                       |      | 150   |      | °C               |

| Thermal Shutdown<br>Hysteresis                         | T <sub>HYS</sub>       |                                                             |                       |      | 21    |      | °C               |

| MONITOR MULTIPLEXE                                     | R                      |                                                             |                       |      |       |      |                  |

| MON Impedance                                          | R <sub>MON</sub>       | Sense pin voltage                                           | e > +0.5V             |      |       | 500  | Ω                |

| Battery Voltage Buffer<br>Precision                    | V <sub>BAT_OFF</sub>   |                                                             |                       | -10  |       | 10   | mV               |

| DIGITAL SIGNALS                                        |                        |                                                             |                       |      |       |      |                  |

| SDA, SCL, MPC Input<br>Logic-High                      | $V_{IH}$               |                                                             |                       | 1.4  |       |      | V                |

| SDA, SCL, MPC Input<br>Logic-Low                       | $V_{IL}$               |                                                             |                       |      |       | 0.5  | V                |

| SDA, RST, KOUT<br>Output Logic-Low                     | V <sub>OL</sub>        | I <sub>OL</sub> = 4mA                                       |                       |      |       | 0.4  | V                |

| MDO Output Logic Low                                   | V                      | I <sub>OL</sub> = 4mA to GNI                                | )                     |      |       | 0.4  | V                |

| MPO Output Logic-Low                                   | V <sub>OL_MPO</sub>    | I <sub>OL</sub> = 4mA to BAT                                | N                     |      |       | 0.4  | v                |

| SCL Clock Frequency                                    | f <sub>SCL</sub>       | (Note 5)                                                    |                       | 0    |       | 400  | kHz              |

| Bus Free Time Between<br>a STOP and START<br>Condition | t <sub>BUF</sub>       |                                                             |                       | 1.3  |       |      | μs               |

#### **Electrical Characteristics (continued)**

$(V_{BAT} = +1.2V, V_{BB1OUT} = +1.8V, V_{BB2OUT} = +1.2V, V_{L1OUT} = +1.5V, V_{L2OUT} = +1.0V, I_{BB1OUT} = I_{BB2OUT} = I_{L1OUT} = I_{L2OUT} = 0A, T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ all registers in their default state, unless otherwise noted. Typical values are at } T_A = +25^{\circ}C) \text{ (Note 1) (Note 2)}$

| PARAMETER                               | SYMBOL              | CONDITIONS   | MIN | TYP | MAX | UNITS |

|-----------------------------------------|---------------------|--------------|-----|-----|-----|-------|

| START Condition<br>(Repeated) Hold Time | t <sub>HD:STA</sub> | (Note 6)     | 0.6 |     |     | μs    |

| Low Period of SCL<br>Clock              | t <sub>LOW</sub>    |              | 1.3 |     |     | μs    |

| High Period of SCL<br>Clock             | t <sub>HIGH</sub>   |              | 0.6 |     |     | μs    |

| Setup Time for a<br>Repeated START      | <sup>t</sup> su:sta |              | 0.6 |     |     | μs    |

| Condition                               | 30.01/1             |              |     |     |     | μs    |

| Data Hold Time                          | t <sub>HD:DAT</sub> | (Notes 7, 8) | 0   |     |     | μs    |

| Data Setup Time                         | t <sub>SU:DAT</sub> | (Note 7)     | 100 |     |     | ns    |

| Setup Time for STOP<br>Condition        | t <sub>SU:STO</sub> |              | 0.6 |     |     | μs    |

- Note 1: All devices are 100% production tested at  $T_A = +25$ °C. Limits over the operating temperature range are guaranteed by design.

- **Note 2:**  $V_{BAT}$  refers to the voltage across the battery terminals;  $V_{BAT} = V_{GND} V_{BATN}$ . **Note 3:** Output voltage must not exceed  $V_{BB\_OUT} V_{BATN} = 5.0V$ .

- Note 4: Actual value may be limited by the lower of the capability of the source (battery) or the maximum input power of the MAX20310.

- Note 5: Timing must be fast enough to prevent the device from entering sleep mode due to bus low for period > t<sub>SI FFP</sub>.

- Note 6: f<sub>SCL</sub> must meet the minimum clock low time plus the rise/fall times.

- Note 7: The maximum t<sub>HD:DAT</sub> has to be met only if the device does not stretch the low period (t<sub>LOW</sub>) of the SCL signal.

- Note 8: The device internally provides a hold time of at least 100ns for the SDA signal (referred to the V<sub>IH MIN</sub> of the SCL signal) to bridge the undefined region of the falling edge of SCL.

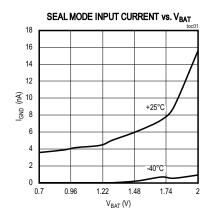

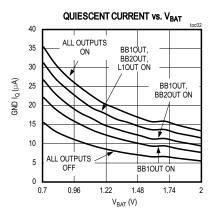

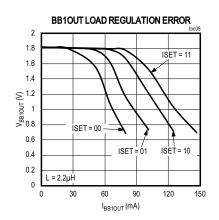

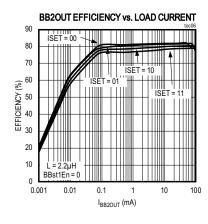

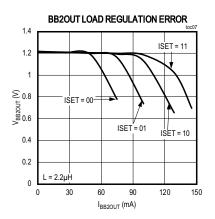

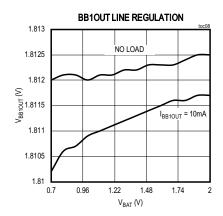

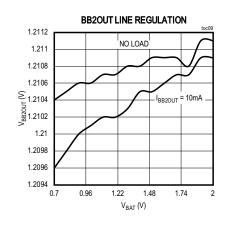

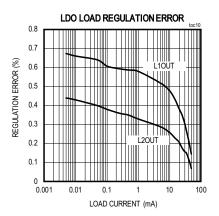

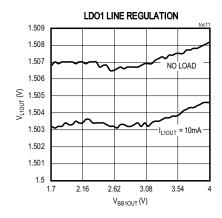

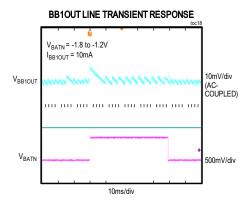

## **Typical Operating Characteristics**

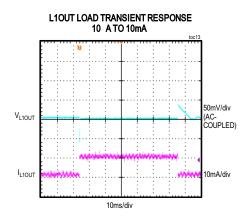

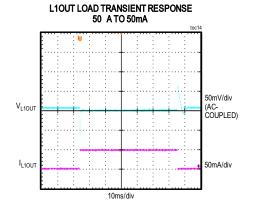

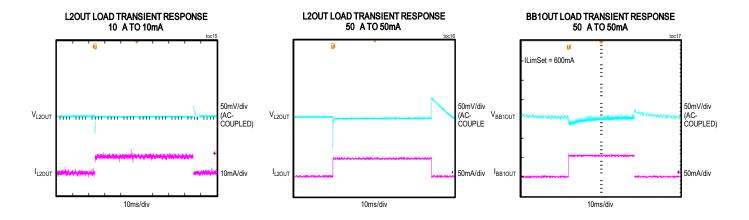

$(V_{BAT} = 1.2V, V_{BB1OUT} = 1.8V, V_{BB2OUT} = 1.2V, V_{L1OUT} = 1.5V, V_{L2OUT} = 1.0V, L = 1.5\mu\text{H}, C_{BB\_OUT} = 10\mu\text{F} \text{ (effective)}, C_{CAP} = 1\mu\text{F} \text{ (effective)}, C_{LDO} = 2.2\mu\text{F} \text{ (effective)} \text{ no load on any rail, } T_A = +25^{\circ}\text{C}, \text{ unless otherwise noted.)}$

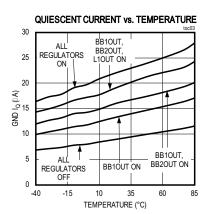

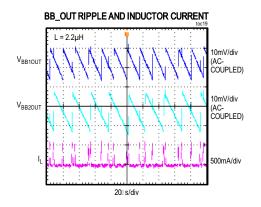

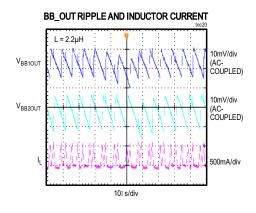

## **Typical Operating Characteristics (continued)**

$(V_{BAT} = 1.2V, V_{BB1OUT} = 1.8V, V_{BB2OUT} = 1.2V, V_{L1OUT} = 1.5V, V_{L2OUT} = 1.0V, L = 1.5\mu\text{H}, C_{BB\_OUT} = 10\mu\text{F} \text{ (effective)}, C_{CAP} = 1\mu\text{F} \text{ (effective)}, C_{LDO} = 2.2\mu\text{F} \text{ (effective)} \text{ no load on any rail, } T_A = +25^{\circ}\text{C}, \text{ unless otherwise noted.)}$

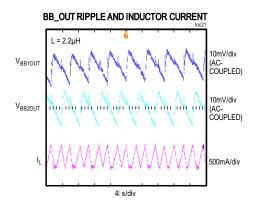

## **Typical Operating Characteristics (continued)**

$(V_{BAT} = 1.2V, V_{BB1OUT} = 1.8V, V_{BB2OUT} = 1.2V, V_{L1OUT} = 1.5V, V_{L2OUT} = 1.0V, L = 1.5\mu\text{H}, C_{BB\_OUT} = 10\mu\text{F} \text{ (effective)}, C_{CAP} = 1\mu\text{F} \text{ (effective)}, C_{LDO} = 2.2\mu\text{F} \text{ (effective)} \text{ no load on any rail, } T_A = +25^{\circ}\text{C}, \text{ unless otherwise noted.)}$

## **Bump Configuration**

## **Bump Description**

| BUMP | NAME   | FUNCTION                                                                                                               |

|------|--------|------------------------------------------------------------------------------------------------------------------------|

| A1   | GND    | Ground/Battery Positive Terminal                                                                                       |

| A2   | L2OUT  | LDO/Switch 2 Output                                                                                                    |

| A3   | L1OUT  | LDO/Switch 1 Output                                                                                                    |

| A4   | CAP    | Internal Supply Decoupling. Connect a minimum 1µF of capacitance to GND.                                               |

| B1   | MPC    | Multipurpose Control Input                                                                                             |

| B2   | SDA    | I <sup>2</sup> C Serial Data                                                                                           |

| В3   | MON    | Monitor Multiplexer Output                                                                                             |

| B4   | BB1OUT | Buck-Boost 1 Output                                                                                                    |

| C1   | KIN    | Key Input, Internally Pulled to GND. To signal active, short KIN to BATN.                                              |

| C2   | SCL    | I <sup>2</sup> C Serial Clock                                                                                          |

| C3   | MPO    | Multipurpose Output. Level shifted digital output for controlling devices referenced to the negative battery terminal. |

| C4   | BB2OUT | Buck-Boost 2 Output                                                                                                    |

| D1   | KOUT   | Key Output. Active-low, level-shifted button status output.                                                            |

| D2   | RST    | Reset Output. Active-low, open-drain output indicates completion of sequencer.                                         |

| D3   | BATN   | Battery Negative Terminal                                                                                              |

| D4   | LX     | Inductor Switch Connection                                                                                             |

### **Functional Block Diagram**

#### **Detailed Description**

#### **Power Regulation**

The MAX20310 features an ultra-low  $I_Q$  SIMO buck-boost switching regulator that provides two programmable voltagle rails and two low- $I_Q$  LDOs. The regulators minimize quiescent current and operate on low input voltages. This makes the MAX20310 ideal for applications powered by singe-cell Alkaline, Zinc Air, or Silver Oxide batteries. All regulator outputs are capable of being discharged through a resistive load (passive discharge) when turned off. The discharge mode is set by the PDsc bits in each regulator's configuration register.

#### **Switching Regulator**

In order to maximize efficiency, the switching regulator is implemented with an inverting buck-boost topology. Referencing the battery's positive terminal to ground configures the battery as a negative supply and the switching regulator output is positive. The switching regulator operates at supplies from -2.0V down to -0.7V, but requires -0.8V to start up. The outputs are independently configurable in 50mV increments.

#### **LDO**

For applications that require lower noise supplies, or simply need additional regulated voltages, the MAX20310 includes two LDO regulators. In normal operation, each LDO can source up to 50mA. The LDO inputs are

supplied by the buck-boost outputs. As such, an LDO cannot be enabled unless its corresponding switching regulator output is active. The LDOs can be used as switches to disconnect the quiescent loads of peripheral systems, increasing battery life. The LDO outputs are configurable from 0.5 to 3.65V in 50mV increments.

#### Voltage Monitor Multiplexer

In addition to the four regulator outputs, the MAX20310 includes a voltage monitor multiplexer. The I<sup>2</sup>C controlled multiplexer connects the MON pin to any one of the regulator outputs or to BATN. This provides access to the different voltage rails in the device for ADC measurements. An inverting amplifier buffers the BATN channel in order to allow a positive, single-ended ADC to measure the voltage.

#### **Multipurpose Control Input**

The MAX20310 includes a multipurpose control (MPC) pin that can control various functions inside the part based on the buck-boost and LDO configuration and sequence register settings. For devices with at least one BBst\_Seq[2:0] or LDO\_Seq[2:0] field set by the factory to 101 (enabled by MPC, active-low) or 110 (enabled by MPC, active-high) according to Table 19, the MPC pin can be configured to control the multipurpose output (MPO) pin for level-shifting to the battery voltage. See the Multipurpose Output section below for details. If the MPC pin is unused, it must be tied to GND.

#### **Multipurpose Output**

In addition to the MPC pin, the MAX20310 also features a multipurpose output (MPO). The MPO pin can be configured to pull down to BATN, to pull up to GND, to pullup/down (push/pull), or be disabled (no pull). On devices with at least one BBst\_Seq[2:0] or LDO\_Seq[2:0] field set by the factory to 101 (enabled by MPC, active-low) or 110 (enabled by MPC, active-high), as detailed in table 19, the MPOCfg register allows the state of the MPO pin to be controlled either by I<sup>2</sup>C command or by

the MPC pin, regardless of polarity. <u>Table 1</u> below shows the truth table associated with such devices. Devices with none of the one BBst\_Seq[2:0] or LDO\_Seq[2:0] fields set by the factory to 101 (enabled by MPC, active-low) or 110 (enabled by MPC, active-high) allow the MPO output to be controlled by I<sup>2</sup>C command only. <u>Table 2</u> below shows the truth table associated with such devices. An example implementation is included in <u>Figure 1</u> to show how to use this pin to control an external regulator powered directly from the battery.

Table 1. MPO Truth Table for Devices with One or More BBst\_Seq[2:0]/LDO\_Seq[2:0] Field Set to 101 or 110 by the Factory

| MPOP | Pull[1:0] | МРОЕ | in[1:0] | MPC | OUTPUT STATE   |

|------|-----------|------|---------|-----|----------------|

| 0    | 0         | Х    | Х       | X   | High-Impedance |

| 0    | 1         | 0    | 0       | X   | High-Impedance |

| 0    | 1         | 0    | 1       | X   | Pulled to BATN |

| 0    | 1         | 1    | 0       | 0   | Pulled to BATN |

| 0    | 1         | 1    | 0       | 1   | High-Impedance |

| 0    | 1         | 1    | 1       | 0   | High-Impedance |

| 0    | 1         | 1    | 1       | 1   | Pulled to BATN |

| 1    | 0         | 0    | 0       | X   | Pulled to GND  |

| 1    | 0         | 0    | 1       | X   | High-Impedance |

| 1    | 0         | 1    | 0       | 0   | High-Impedance |

| 1    | 0         | 1    | 0       | 1   | Pulled to GND  |

| 1    | 0         | 1    | 1       | 0   | Pulled to GND  |

| 1    | 0         | 1    | 1       | 1   | High-Impedance |

| 1    | 1         | 0    | 0       | X   | Pulled to GND  |

| 1    | 1         | 0    | 1       | X   | Pulled to BATN |

| 1    | 1         | 1    | 0       | 0   | Pulled to BATN |

| 1    | 1         | 1    | 0       | 1   | Pulled to GND  |

| 1    | 1         | 1    | 1       | 0   | Pulled to GND  |

| 1    | 1         | 1    | 1       | 1   | Pulled to BATN |

Table 2. MPO Truth Table for Devices with None of the BBst\_Seq[2:0]/LDO\_Seq[2:0] Fields Set to 101 or 110 by the Factory

| MPOP | ull[1:0] | МРОЕ | n[1:0] | MPC | OUTPUT STATE   |

|------|----------|------|--------|-----|----------------|

| 0    | 0        | X    | X      | X   | High-Impedance |

| 0    | 1        | 0    | 0      | X   | High-Impedance |

| 0    | 1        | 0    | 1      | X   | Pulled to BATN |

| 1    | 0        | 0    | 0      | X   | Pulled to GND  |

| 1    | 0        | 0    | 1      | X   | High-Impedance |

| 1    | 1        | 0    | 0      | X   | Pulled to GND  |

| 1    | 1        | 0    | 1      | X   | Pulled to BATN |

#### Power On/Off and Reset Control

The MAX20310 is intended for use in small battery-powered applications. It includes an off mode to minimize drain on the battery. In the off mode, all outputs are disabled and the part waits until the  $\overline{\text{KIN}}$  input goes active to wake the device. The  $\overline{\text{KIN}}$  input is internally pulled to GND and needs to be shorted to BATN to wake the device. An open-drain buffered copy of the state of  $\overline{\text{KIN}}$  is available at  $\overline{\text{KOUT}}$  allowing the system to monitor the status of the button. When the device is powered on, each function can be automatically enabled by a sequencing controller or remain off until an I<sup>2</sup>C command enables it. This behavior is determined by the factory settings. A button monitor is present on the MAX20310 and can produce different actions for long or short button presses.

The list of settings and corresponding actions is shown in <u>Table 18</u>. A button press always wakes up the device, and the factory configuration determines other behavior.

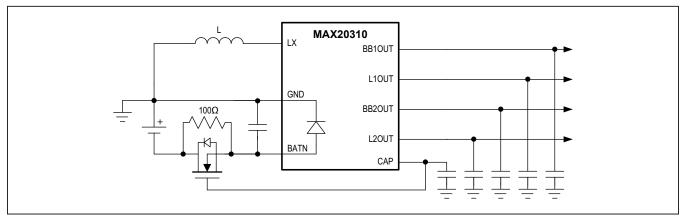

#### **Reverse Battery Protection**

Some applications use batteries like AAA's that do not have mechanical reverse installation protection. In such applications, an optional external nMOSFET and resistor connected as shown in Figure 2 provide reverse battery protection for the system. In normal operation, the  $100\Omega$  resistor slows the charging of  $C_{IN}$  at startup until  $V_{CAP}-V_{BATN}$  exceeds the threshold of the external MOSFET. Thereafter, the circuit functions nominally. In the case of battery reversal, the  $100\Omega$  resistor limits the current from the battery and protects the downstream system.

Figure 1. Controlling an External Regulator with MPO

Figure 2. Reverse Battery Protection Using an External MOSFET

#### **Power Sequencing**

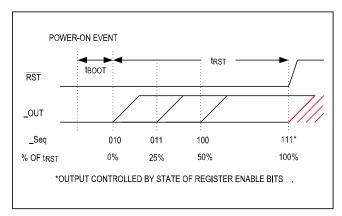

The sequencing of the voltage regulators during power-on is configurable. Regulators can be configured to turn on at one of four points during the power on process. The four points are: 100ms after the power-on event, after the RST signal is released, or at two points in between. The two points are fixed proportionally to the duration of the Power-On Reset (POR) process, but the overall time of the reset delay is configurable (refer to PwrCfg register). The timing relationship is presented graphically in Figure 3. Additionally, the regulators are controllable by the sequencer, an input pin, or I<sup>2</sup>C command after reset is released. Note that the LDOs will not turn on until the associated switching output is also enabled.

#### I<sup>2</sup>C Interface

The MAX20310 uses the two-wire I<sup>2</sup>C interface to communicate with a host microcontroller. The configuration settings and status information provided through this interface are detailed in the register descriptions. The slave address is 0x50 for writes and 0x51 for reads.

#### **Applications Information**

#### **Always-On Devices**

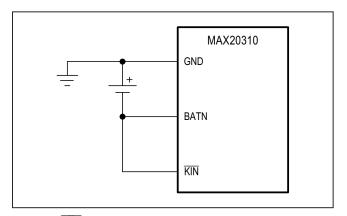

Due to its low power consumption, the MAX20310 is ideal for always-on applications. Products targeting these always-on, buttonless applications should select a version of the MAX20310 with PwrCfgMd[1:0] = 00 and connect the  $\overline{\text{KIN}}$  input to BATN as shown in Figure 4. This PwrCfgMd setting configures a  $\overline{\text{KIN}}$  press to only turn on the device. When a fresh battery is inserted, or when a battery tab used during product shelf life is removed,  $\overline{\text{KIN}}$  is pulled to BATN and the device turns on.

Figure 3. Reset Sequence Programming

#### **Additional Voltage Regulators**

In applications with additional voltage regulators operating directly from the battery, careful consideration must be given to battery and system power domains. Due to the negative battery implementation of the MAX20310, the common node for the system power domain (GND) is connected to the positive terminal of the battery.

Regulators using the battery as a positive supply should connect BATN as the local ground and GND as the input supply. However, the output must always be referenced to the positive terminal of the battery (GND). This causes the output voltage of the regulator, referenced to GND, to equal  $V_{\mbox{OUT}} - V_{\mbox{BAT}}$ . As the battery discharges, this voltage might change over time.

For example, in Figure 1, the external MAX1724 step-up converter produces 5V with respect to the regulator ground (BATN). Because the battery voltage is 1.2V, the output voltage in the system power domain is 3.8V. Due to the relative flatness of the discharge curves for Silver-Oxide, Zinc-Air, and other common coin cell batteries, the challenges associated with a changing reference node are reduced. However, designs should account for some variation of the BATN node.

#### I<sup>2</sup>C Interface

The MAX20310 contains an I<sup>2</sup>C-compatible interface for data communication with a host controller (SCL and SDA). The interface supports a clock frequency of up to 400kHz. SCL and SDA require pullup resistors that are connected to a positive supply.

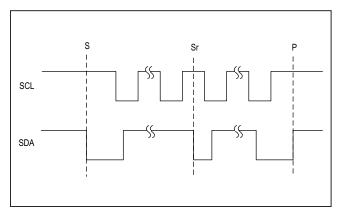

#### Start, Stop, and Repeated Start Conditions

When writing to the MAX20310 using I<sup>2</sup>C, the master sends a START condition (S) followed by the MAX20310

Figure 4. KIN Connected to BATN for Always-On Applications

#### **MAX20310**

## Ultra-Low Quiescent Current PMIC with SIMO Buck-Boost for Wearable Applications

I<sup>2</sup>C address. After the address, the master sends the register address of the register that is to be programmed. The master then ends communication by issuing a

Figure 5. I<sup>2</sup>C START, STOP and REPEATED START Conditions

STOP condition (P) to relinquish control of the bus, or a REPEATED START condition (Sr) to communicate to another I<sup>2</sup>C slave. See Figure 5.

#### **Slave Address**

Set the Read/Write bit high to configure the MAX20310 to read mode. Set the Read/Write bit low to configure the MAX20310 to write mode. The address is the first byte of information sent to the MAX20310 after the START condition.

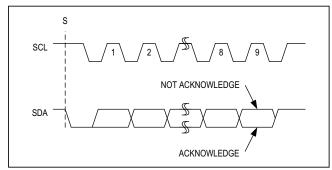

#### **Bit Transfer**

One data bit is transferred on the rising edge of each SCL clock cycle. The data on SDA must remain stable during the high period of the SCL clock pulse. Changes in SDA while SCL is high and stable are considered control signals (see the START, STOP and REPEATED START Conditions section). Both SDA and SCL remain high when the bus is not active.

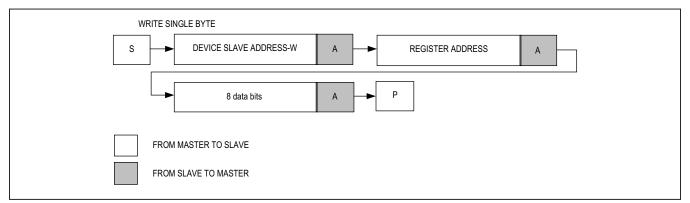

Figure 6. Write Byte Sequence

Figure 7. Burst Write Sequence

#### **MAX20310**

## Ultra-Low Quiescent Current PMIC with SIMO Buck-Boost for Wearable Applications

#### Single-Byte Write

In this operation, the master sends an address and two data bytes to the slave device (Figure 6). The following procedure describes the single byte write operation:

The master sends a START condition

The master sends the 7-bit slave address plus a write bit (low)

The addressed slave asserts an ACK on the data line

The master sends the 8-bit register address

The slave asserts an ACK on the data line only if the address is valid (NAK if not)

The master sends 8 data bits

The slave asserts an ACK on the data line

The master generates a STOP condition

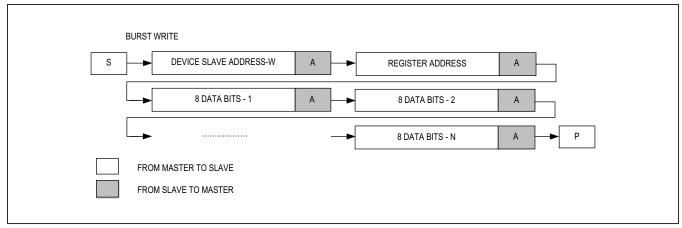

#### **Burst Write**

In this operation, the master sends an address and multiple data bytes to the slave device (Figure 7). The slave device automatically increments the register address after each data byte is sent, unless the register being accessed is 0x00, in which case the register address remains the same. The following procedure describes the burst write operation:

The master sends a START condition

The master sends the 7-bit slave address plus a write bit (low)

The addressed slave asserts an ACK on the data line

The master sends the 8-bit register address

The slave asserts an ACK on the data line only if the address is valid (NAK if not)

The master sends 8 data bits

The slave asserts an ACK on the data line

Repeat 6 and 7 N-1 times

The master generates a STOP condition

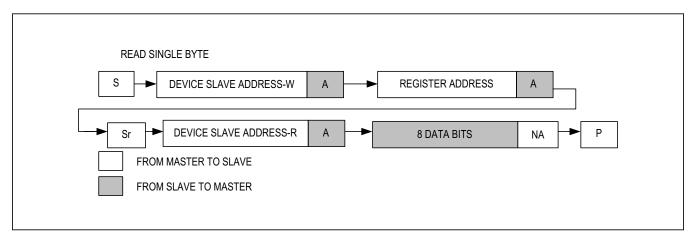

#### Single-Byte Read

In this operation, the master sends an address plus two data bytes and receives one data byte from the slave device (Figure 8). The following procedure describes the single byte read operation:

The master sends a START condition

The master sends the 7-bit slave address plus a write bit (low)

The addressed slave asserts an ACK on the data line

The master sends the 8-bit register address

The slave asserts an ACK on the data line only if the address is valid (NAK if not)

The master sends a REPEATED START condition

The master sends the 7-bit slave address plus a read bit (high)

The addressed slave asserts an ACK on the data line

The slave sends 8 data bits

The master asserts a NACK on the data line

The master generates a STOP condition

Figure 8. Read Byte Sequence

Figure 9. Burst Read Sequence

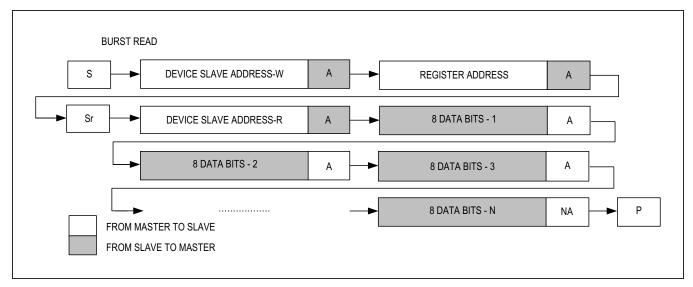

#### **Burst Read**

In this operation, the master sends an address plus two data bytes and receives multiple data bytes from the slave device (Figure 9). The following procedure describes the burst byte read operation:

The master sends a START condition

The master sends the 7-bit slave address plus a write bit (low)

The addressed slave asserts an ACK on the data line

The master sends the 8-bit register address

The slave asserts an ACK on the data line only if the address is valid (NAK if not)

The master sends a REPEATED START condition

The master sends the 7-bit slave address plus a read bit (high)

The slave asserts an ACK on the data line

The slave sends 8 data bits

The master asserts an ACK on the data line

Repeat 9 and 10 N-2 times

The slave sends the last 8 data bits

The master asserts a NACK on the data line

The master generates a STOP condition

Figure 10. Acknowledge

#### **Acknowledge Bits**

Data transfers are acknowledged with an acknowledge bit (ACK) or a not-acknowledge bit (NACK). Both the master and the MAX20310 generate ACK bits. To generate an ACK, pull SDA low before the rising edge of the ninth clock pulse and hold it low during the high period of the ninth clock pulse (see <a href="Figure 10">Figure 10</a>). To generate a NACK, leave SDA high before the rising edge of the ninth clock pulse and leave it high for the duration of the ninth clock pulse. Monitoring for NACK bits allows for detection of unsuccessful data transfers.

| REGISTER | REGISTER  | R/W | B7          | B6          | B5           | B4           | B3           | B2           | <b>B</b> 4   | B0           |

|----------|-----------|-----|-------------|-------------|--------------|--------------|--------------|--------------|--------------|--------------|

| 00X0     | Chipld    | 2   | Chipld[7]   | Chipld[6]   | ChipId[5]    | ChipId[4]    | Chipld[3]    | Chipld[2]    | ChipId[1]    | Chipld[0]    |

| 0x01     | ChipRev   | 22  | ChipRev[7]  | ChipRev[6]  | ChipRev[5]   | ChipRev[4]   | ChipRev[3]   | ChipRev[2]   | ChipRev[1]   | ChipRev[0]   |

| 0x02     | BBstCfg   | RW  | BBstDmpEn   | I           |              | 1            | [LimSet[1]   | [LimSet[0]   | FetScale[1]  | FetScale[0]  |

| 0x03     | Reserved  | I   | 1           | I           | 1            | 1            | 1            | 1            | I            | I            |

| 0x04     | BBst1VSet | RW  | 1           | I           | BBst1VSet[5] | BBst1VSet[4] | BBst1VSet[3] | BBst1VSet[2] | BBst1VSet[1] | BBst1VSet[0] |

| 0x05     | BBst1VCfg | RW  | BBst1En[1]  | BBst1En[0]  | BBst1PDsc    | BBst1ADsc    | BBst1RmpDis  | I            | I            | I            |

| 90x0     | BBst2VSet | RW  | I           | I           | BBst2VSet[5] | BBst2VSet[4] | BBst2VSet[3] | BBst2VSet[2] | BBst2VSet[1] | BBst2VSet[0] |

| 0x07     | BBst2VCfg | RW  | BBst2En[1]  | BBst2En[0]  | BBst2PDsc    | BBst2ADsc    | BBst2RmpDis  |              | I            | ı            |

| 80x0     | LDO1Vset  | RW  | I           | I           | LDO1VSet[5]  | LDO1VSet[4]  | LDO1VSet[3]  | LDO1VSet[2]  | LDO1VSet[1]  | LDO1VSet[0]  |

| 60x0     | LDO1Cfg   | RW  | LDO1En[1]   | LDO1En[0]   | LDO1PDsc     | LD01ADsc     | 1            | 1            | I            | LDO1Mode     |

| 0x0A     | LDO2Vset  | RW  | I           | 1           | LDO2VSet[5]  | LDO2VSet[4]  | LDO2VSet[3]  | LDO2VSet[2]  | LDO2VSet[1]  | LDO2VSet[0]  |

| 0x0B     | LD02Cfg   | RW  | LDO2En[1]   | LDO2En[0]   | LD02PDsc     | LDO2ADsc     | 1            | 1            | I            | LDO2Mode     |

| 0x0C     | MonCfg    | RW  | ı           | 1           | I            |              | MonHiZ       | MonSel[2]    | MonSel[1]    | MonSel[0]    |

| 0x0D     | MPOCfg    | RW  | MPOEn[1]    | MPOEn[0]    |              |              | 1            | _            | MPOPul[1]    | MPOPull[0]   |

| 0x0E     | PwrCmd    | RW  | PwrCmd[7]   | PwrCmd[6]   | PwrCmd[5]    | PwrCmd[4]    | PwrCmd[3]    | PwrCmd[2]    | PwrCmd[1]    | PwrCmd[0]    |

| 0x0F     | Status    | 2   | LDO2UVLO    | LDO1UVLO    | LDO2Thm      | LDO1Thm      | LDO2CrMd     | LDO1CrMd     | KINSts       | MPCSts       |

| 0x10     | PwrCfg    | R   | PwrCfgMd[1] | PwrCfgMd[0] | GPasDsc      |              | I            | _            | BootDly[1]   | BootDly[0]   |

| 0x11     | BBstSeq   | R   | I           | BBst2Seq[2] | BBst2Seq[1]  | BBst2Seq[0]  | I            | BBst1Seq[2]  | BBst1Seq[1]  | BBst1Seq[0]  |

| 0x12     | LDOSeq    | R   | I           | LDO2Seq[2]  | LDO2Seq[1]   | LDO2Seq[0]   | 1            | LDO1Seq[2]   | LDO1Seq[1]   | LDO1Seq[0]   |

Analog Devices | 17 www.analog.com

# I<sup>2</sup>C Register Descriptions Table 3. Chipld Register (0x00)

| ADDRESS     | 0x00 (Read-   | Only)           |                 |                 |             |   |   |   |

|-------------|---------------|-----------------|-----------------|-----------------|-------------|---|---|---|

| BIT         | 7             | 6               | 5               | 4               | 3           | 2 | 1 | 0 |

| NAME        |               |                 |                 | Chiple          | d[7:0]      |   |   |   |

| ChipId[7:0] | ChipId[7:0] b | its show inforr | mation about tl | ne version of t | he MAX20310 | ) |   |   |

## **Table 4. ChipRev Register (0x01)**

| ADDRESS      | 0x01 (Read- | Only)          |                 |                 |               |    |   |   |  |

|--------------|-------------|----------------|-----------------|-----------------|---------------|----|---|---|--|

| BIT          | 7           | 6              | 5               | 4               | 3             | 2  | 1 | 0 |  |

| NAME         |             | ChipRev[7:0]   |                 |                 |               |    |   |   |  |

| ChipRev[7:0] | ChipRev sho | ws information | n about the rev | vision of the M | AX20310 silic | on |   |   |  |

### Table 5. BBstCfg Register (0x02)

| ADDRESS       | 0x02 (Read, Write)                                                                                                                       |              |                |                 |          |                         |   |   |  |  |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------|--------------|----------------|-----------------|----------|-------------------------|---|---|--|--|

| BIT           | 7                                                                                                                                        | 6            | 5              | 4               | 3        | 2                       | 1 | 0 |  |  |

| NAME          | BBstDmpEn                                                                                                                                | -            | -              | -               | ILimS    | nSet[1:0] FetScale[1:0] |   |   |  |  |

| BBstDmpEn     | Buck-Boost Dur<br>This enables a of<br>0: Switch disable<br>1: Switch enable                                                             | dump switch  | n to reduce LX | oscillations    |          |                         |   |   |  |  |

| ILimSet[1:0]  | Buck-Boost Peak Current Limit Setting Sets the peak current supplied by the buck-boost regulator 00: 300mA 01: 400mA 10: 500mA 11: 600mA |              |                |                 |          |                         |   |   |  |  |

| FetScale[1:0] | FetScale<br>Scales the switc<br>00: 28%<br>01: 60%<br>10: 80%<br>11: 100%                                                                | ching FETs t | o optimize eff | iciency at a gi | ven load |                         |   |   |  |  |

## Table 6. BBst1VSet Register (0x04)

| ADDRESS        | 0x04 (Read, | 0x04 (Read, Write) |                |       |  |  |  |  |  |  |  |

|----------------|-------------|--------------------|----------------|-------|--|--|--|--|--|--|--|

| BIT            | 7           | 6                  | 5 4 3 2 1 0    |       |  |  |  |  |  |  |  |

| NAME           | -           | -                  | BBst1VSet[5:0] |       |  |  |  |  |  |  |  |

| BBst1VSet[5:0] |             | 95V<br>0V          |                | nents |  |  |  |  |  |  |  |

## Table 7. BBst1Cfg Register (0x05)

| ADDRESS      | 0x05 (Read,                                 | 0x05 (Read, Write)                                                                                                                                                                        |   |   |   |   |   |   |  |  |  |

|--------------|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|---|---|---|---|--|--|--|

| BIT          | 7                                           | 6                                                                                                                                                                                         | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

| NAME         | BBst1Ei                                     | BBst1En[1:0]         BBst1PDsc         —         BBst1RmpDis         —         —         —                                                                                                |   |   |   |   |   |   |  |  |  |

| BBst1En[1:0] | 00: Disabled<br>01: Enabled<br>10: Controll | Buck-Boost 1 Enable  00: Disabled  01: Enabled  10: Controlled by MPC (active low)  11: Controlled by MPC (active high)                                                                   |   |   |   |   |   |   |  |  |  |

| BBst1PDsc    | 0: Disabled                                 | Buck-Boost 1 Passive Discharge 0: Disabled 1: Enabled when output is off                                                                                                                  |   |   |   |   |   |   |  |  |  |

| BBst1RmpDis  | applied to the 1: Immedia                   | Disable the ramped output of Buck-Boost output 1. If disabled, the BBst1VSet value is immediately applied to the output.  1: Immediate transition to set value  0: Ramp to set value mode |   |   |   |   |   |   |  |  |  |

## Table 8. BBst2VSet Register (0x06)

| ADDRESS        | 0x06 (Read | 0x06 (Read, Write)     |                                |        |  |  |  |  |  |  |  |

|----------------|------------|------------------------|--------------------------------|--------|--|--|--|--|--|--|--|

| BIT            | 7          | 6                      | 5 4 3 2 1 0                    |        |  |  |  |  |  |  |  |

| NAME           | -          | -                      | BBst2VSet[5:0]                 |        |  |  |  |  |  |  |  |

| BBst2VSet[5:0] |            | 0.90V<br>0.95V<br>.00V | tage Setting<br>ale, 50mV incr | ements |  |  |  |  |  |  |  |

## Table 9. BBst2Cfg Register (0x07)

| ADDRESS      | 0x07 (Rea                                                                                                                                                                                 | 0x07 (Read, Write)                                                                                                         |           |   |             |   |   |   |  |  |  |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|-----------|---|-------------|---|---|---|--|--|--|

| BIT          | 7                                                                                                                                                                                         | 6                                                                                                                          | 5         | 4 | 3           | 2 | 1 | 0 |  |  |  |

| NAME         | BBst2                                                                                                                                                                                     | 2En[1:0]                                                                                                                   | BBst2PDsc | - | BBst2RmpDis | - | - | - |  |  |  |

| BBst2En[1:0] | 00: Disable<br>01: Enable<br>10: Contro                                                                                                                                                   | Buck-Boost 2 Output Enable 00: Disabled 01: Enabled 10: Controlled by MPC (active-low) 11: Controlled by MPC (active-high) |           |   |             |   |   |   |  |  |  |

| BBst2PDsc    | 0: Disable                                                                                                                                                                                | Buck-Boost 2 Passive Discharge 0: Disabled 1: Enabled when output is off                                                   |           |   |             |   |   |   |  |  |  |

| BBst2RmpDis  | Disable the ramped output of Buck-Boost output 2. If disabled, the BBst2VSet value is immediately applied to the output.  1: Immediate transition to set value  0: Ramp to set value mode |                                                                                                                            |           |   |             |   |   |   |  |  |  |

## Table 10. LDO1VSet Register (0x08)

| ADDRESS       | 0x08 (Read, Write) |                 |   |   |   |   |   |   |  |

|---------------|--------------------|-----------------|---|---|---|---|---|---|--|

| BIT           | 7                  | 6               | 5 | 4 | 3 | 2 | 1 | 0 |  |

| NAME          | _                  | — LDO1VSet[5:0] |   |   |   |   |   |   |  |

| LDO1VSet[5:0] |                    | 0.55V<br>.60V   | - |   |   |   |   |   |  |

## Table 11. LDO1Cfg Register (0x09)

| ADDRESS     | 0x09 (Read                                        | 0x09 (Read, Write)                                                                                                  |                   |    |  |  |  |  |  |  |  |

|-------------|---------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|-------------------|----|--|--|--|--|--|--|--|

| BIT         | 7                                                 | 7 6 5 4 3 2 1 0                                                                                                     |                   |    |  |  |  |  |  |  |  |

| NAME        | LDO1                                              | LDO1En[1:0] LDO1PDsc LDO1ADsc — — LDO1Mod                                                                           |                   |    |  |  |  |  |  |  |  |

| LDO1En[1:0] | 00: Disable<br>01: Enable<br>10: Controll         | LDO 1 Output Enable D0: Disabled D1: Enabled 10: Controlled by MPC (active-low) 11: Controlled by MPC (active-high) |                   |    |  |  |  |  |  |  |  |

| LDO1PDsc    | 0: Disabled                                       | LDO 1 Passive Discharge<br>0: Disabled<br>1: Enabled when output is off                                             |                   |    |  |  |  |  |  |  |  |

| LDO1Mode    | LDO 1 Mod<br>Configure L<br>0: LDO<br>1: Load Swi | DO1 as an Ll                                                                                                        | DO or a load swit | ch |  |  |  |  |  |  |  |

## Table 12. LDO2VSet Register (0x0A)

| ADDRESS       | 0x0A (Read, Write) |                |             |               |  |  |  |  |  |  |

|---------------|--------------------|----------------|-------------|---------------|--|--|--|--|--|--|

| BIT           | 7                  | 6              | 5 4 3 2 1 0 |               |  |  |  |  |  |  |

| NAME          | _                  | _              |             | LDO2VSet[5:0] |  |  |  |  |  |  |

| LDO2VSet[5:0] |                    | 0.55V<br>6.60V |             |               |  |  |  |  |  |  |

## Table 13. LDO2Cfg Register (0x0B)

| ADDRESS     | 0x0B (Rea                              | ad, Write)                                                                                                          |          |   |   |   |   |          |  |

|-------------|----------------------------------------|---------------------------------------------------------------------------------------------------------------------|----------|---|---|---|---|----------|--|

| BIT         | 7                                      | 6                                                                                                                   | 5        | 4 | 3 | 2 | 1 | 0        |  |

| NAME        | LDO2E                                  | En[1:0]                                                                                                             | LDO2PDsc | _ | _ | _ | _ | LDO2Mode |  |

| LDO2En[1:0] | 00: Disabl<br>01: Enable<br>10: Contro | LDO 2 Output Enable 00: Disabled 01: Enabled 10: Controlled by MPC (active-low) 11: Controlled by MPC (active-high) |          |   |   |   |   |          |  |

| LDO2PDsc    | 0: Disable                             | LDO 2 Passive Discharge<br>0: Disabled<br>1: Enabled when output is off                                             |          |   |   |   |   |          |  |

| LDO2Mode    | Configure<br>0: LDO                    | LDO 2 Mode Configure LDO2 as an LDO or a load switch 0: LDO 1: Load Switch                                          |          |   |   |   |   |          |  |

## Table 14. MonCfg Register (0x0C)

|             | 0 00 /5                                           |                                                                                            |       |   |        |   |             |   |  |  |

|-------------|---------------------------------------------------|--------------------------------------------------------------------------------------------|-------|---|--------|---|-------------|---|--|--|

| ADDRESS     | 0x0C (Rea                                         | id, Write)                                                                                 |       |   |        |   |             |   |  |  |

| BIT         | 7                                                 | 6                                                                                          | 5     | 4 | 3      | 2 | 1           | 0 |  |  |

| NAME        | _                                                 | _                                                                                          |       | _ | MonHiZ |   | MonSel[2:0] |   |  |  |

| MonHiZ      | 0: 100kΩ p                                        | Monitor Off Mode Condition 0: 100kΩ pulldown when disabled 1: High impedance when disabled |       |   |        |   |             |   |  |  |

| MonSel[2:0] | 000: Disab<br>001: BB1C<br>010: BB2C<br>011: L1OU | OUT selected<br>OUT selected<br>IT selected<br>IT selected<br>N selected<br>selected       | etion |   |        |   |             |   |  |  |

## **Table 15. MPOCfg Register (0x0D)**

| ADDRESS      | 0x0D (Read, Write)                                                                                                                                                          |                               |  |  |  |  |  |  |  |  |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|--|--|--|--|--|--|--|--|

| BIT          | 7                                                                                                                                                                           | 7 6 5 4 3 2 1 0               |  |  |  |  |  |  |  |  |

| NAME         | MPO                                                                                                                                                                         | MPOEn[1:0] — — — MPOPull[1:0] |  |  |  |  |  |  |  |  |

| MPOEn[1:0]   | Multipurpose Output Enable 00: Pull up (to GND) 01: Pull down (to BATN) 10: Pull up when MPC high, pull down when MPC low 11: Pull up when MPC low, pull down when MPC high |                               |  |  |  |  |  |  |  |  |

| MPOPull[1:0] | Multipurpose Output Pull Mode 00: Disabled 01: Pull down (to BATN) 10: Pull up (to GND) 11: Pull up/down (Push/Pull)                                                        |                               |  |  |  |  |  |  |  |  |

## Table 16. PwrCmd Register (0x0E)

| ADDRESS     | 0x0E (Read, Write)     |                                                                                |                                     |              |  |  |  |  |  |  |

|-------------|------------------------|--------------------------------------------------------------------------------|-------------------------------------|--------------|--|--|--|--|--|--|

| BIT         | 7                      | 7 6 5 4 3 2 1 0                                                                |                                     |              |  |  |  |  |  |  |

| NAME        |                        | PwrCmd[7:0]                                                                    |                                     |              |  |  |  |  |  |  |

| PwrCmd[7:0] | 10110010:<br>11000011: | nmand Registe<br>Power Off - To<br>Hard Reset - <sup>-</sup><br>Soft Reset - P | urn off and stag<br>Furn off and re | turn back on |  |  |  |  |  |  |

## Table 17. Status Register (0x0F)

| ADDRESS  | 0x0F (Read-Or                               | 0x0F (Read-Only)                                            |         |         |          |          |        |        |  |

|----------|---------------------------------------------|-------------------------------------------------------------|---------|---------|----------|----------|--------|--------|--|

| BIT      | 7                                           | 6                                                           | 5       | 4       | 3        | 2        | 1      | 0      |  |

| NAME     | LDO2UVLO                                    | LDO1UVLO                                                    | LDO2Thm | LDO1Thm | LDO2CrMd | LDO1CrMd | KINSts | MPCSts |  |

| LDO2UVLO | LDO 2 Undervoltage                          |                                                             | Status  |         |          |          |        |        |  |

| LDO1UVLO | 0: Normal                                   | LDO 1 Undervoltage Lockout Status 0: Normal 1: Undervoltage |         |         |          |          |        |        |  |

| LDO2Thm  | 0: Normal                                   | LDO 2 Thermal Limit Status 0: Normal 1: Thermal shutdown    |         |         |          |          |        |        |  |

| LDO1Thm  | 0: Normal                                   | LDO 1 Thermal Limit Status 0: Normal 1: Thermal shutdown    |         |         |          |          |        |        |  |

| LDO2CrMd | LDO 2 Current<br>0: LDO<br>1: Switch        |                                                             |         |         |          |          |        |        |  |

| LDO1CrMd | LDO 1 Current<br>0: LDO<br>1: Switch        |                                                             |         |         |          |          |        |        |  |

| KINSts   | KIN Status<br>0: Low<br>1: High             | 0: Low                                                      |         |         |          |          |        |        |  |

| MPCSts   | Multi-Purpose Control Status 0: Low 1: High |                                                             |         |         |          |          |        |        |  |

## Table 18. PwrCfg Register (0x10)

| ADDRESS       | 0x10 (Read-Only)                                                                                                                                                                                                                                                                                                        |          |         |   |   |   |       |         |  |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|---------|---|---|---|-------|---------|--|

| BIT           | 7                                                                                                                                                                                                                                                                                                                       | 6        | 5       | 4 | 3 | 2 | 1     | 0       |  |

| NAME          | PwrCf                                                                                                                                                                                                                                                                                                                   | gMd[1:0] | GPasDsc | _ | _ | _ | BootD | ly[1:0] |  |

| PwrCfgMd[1:0] | Power Configuration Mode A short button press will always wake the device from the off state.  00: Button only wakes device (can be turned off by I <sup>2</sup> C command)  01: Long button press generates reset pulse  10: Long button press power cycles and reboots device  11: Long button press turns device off |          |         |   |   |   |       |         |  |

| GPasDsc       | Global Passive Discharge 0: Passive discharge disabled in off state 1: Passive discharged enabled in off state                                                                                                                                                                                                          |          |         |   |   |   |       |         |  |

| BootDly[1:0]  | Boot Sequence Delay (t <sub>RST</sub> ) 00: 80ms 01: 120ms 10: 160ms 11: 200ms                                                                                                                                                                                                                                          |          |         |   |   |   |       |         |  |

## Table 19. BBstSeq Register (0x11)

| ADDRESS       | 0x11 (Read-Only)                                                                                                                                                                                                                                                                                                   |   |              |   |   |   |               |   |  |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|--------------|---|---|---|---------------|---|--|

| BIT           | 7                                                                                                                                                                                                                                                                                                                  | 6 | 5            | 4 | 3 | 2 | 1             | 0 |  |

| NAME          | _                                                                                                                                                                                                                                                                                                                  |   | BBst2Seq[2:0 | ] | _ |   | BBst1Seq[2:0] |   |  |

| BBst2Seq[2:0] | Buck-Boost 2 Sequencing Configuration 000: Disabled 001: Reserved 010: Enabled at 0% of power on delay 011: Enabled at 25% of power on delay 100: Enabled at 50% of power on delay 100: Enabled by MPC (active low) 110: Enabled by MPC (active high) 111: Controlled by BBst2En[1:0] after 100% of power on delay |   |              |   |   |   |               |   |  |

| BBst1Seq[2:0] | Buck-Boost 2 Sequencing Configuration 000: Disabled 001: Reserved 010: Enabled at 0% of power on delay 011: Enabled at 25% of power on delay 100: Enabled at 50% of power on delay 101: Enabled by MPC (active low) 110: Enabled by MPC (active high) 111: Controlled by BBst1En[1:0] after 100% of power on delay |   |              |   |   |   |               |   |  |

## Table 20. LDOSeq Register (0x12)

| ADDRESS      | 0x12 (Read-Only)                                                                                                                                                                                                                                                                                           |   |             |   |   |   |             |   |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-------------|---|---|---|-------------|---|

| BIT          | 7                                                                                                                                                                                                                                                                                                          | 6 | 5           | 4 | 3 | 2 | 1           | 0 |

| NAME         | _                                                                                                                                                                                                                                                                                                          |   | LDO2Seq[2:0 | ] | _ |   | LDO1Seq[2:0 |   |

| LDO2Seq[2:0] | LDO 2 Sequencing Configuration 000: Disabled 001: Reserved 010: Enabled at 0% of power on delay 011: Enabled at 25% of power on delay 100: Enabled at 50% of power on delay 100: Enabled by MPC (active low) 110: Enabled by MPC (active high) 111: Controlled by LDO2En[1:0] after 100% of power on delay |   |             |   |   |   |             |   |

| LDO1Seq[2:0] | LDO 1 Sequencing Configuration 000: Disabled 001: Reserved 010: Enabled at 0% of power on delay 011: Enabled at 25% of power on delay 100: Enabled at 50% of power on delay 101: Enabled by MPC (active low) 110: Enabled by MPC (active high) 111: Controlled by LDO1En[1:0] after 100% of power on delay |   |             |   |   |   |             |   |

**Table 21. Register Bit Default Values**

| REGISTER BITS  | MAX20310A                           | MAX20310B                           | MAX20310C                           | MAX20310D                           | MAX20310E                           |

|----------------|-------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|

| ILimSet[1:0]   | 400mA                               | 600mA                               | 300mA                               | 300mA                               | 300mA                               |

| FetScale[1:0]  | 100%                                | 100%                                | 80%                                 | 80%                                 | 80%                                 |

| LDO1En[1:0]    | Disabled                            | Disabled                            | Disabled                            | Disabled                            | Disabled                            |

| LDO1VSet[5:0]  | 1.5V                                | 0.5V                                | 1.5V                                | 3.0V                                | 1.2V                                |

| LDO2En[1:0]    | Disabled                            | Disabled                            | Disabled                            | Disabled                            | Disabled                            |

| LDO2VSet[5:0]  | 1.0V                                | 1.8V                                | 1.0V                                | 1.2V                                | 1.0V                                |

| BBst1En[1:0]   | Disabled                            | Disabled                            | Enabled                             | Enabled                             | Enabled                             |

| BBst1VSet[5:0] | 1.8V                                | 3.0V                                | 2.5V                                | 3.3V                                | 1.8V                                |

| BBst2En[1:0]   | Disabled                            | Disabled                            | Disabled                            | Disabled                            | Disabled                            |

| BBst2VSet[5:0] | 1.2V                                | 2.1V                                | 1.2V                                | 1.5V                                | 1.2V                                |

| BBstDmpEn      | Disabled                            | Disabled                            | Disabled                            | Disabled                            | Disabled                            |

| LDO2Mode       | Switch                              | LDO                                 | LDO                                 | LDO                                 | LDO                                 |

| LDO1Mode       | LDO                                 | Switch                              | LDO                                 | LDO                                 | LDO                                 |

| MPOEn[1:0]     | GND                                 | GND                                 | GND                                 | GND                                 | GND                                 |

| PullMode[1:0]  | Disabled                            | Disabled                            | Disabled                            | Disabled                            | Disabled                            |

| PwrCfgMd[1:0]  | ON/off                              | ON                                  | Hard Reset                          | Soft Reset                          | On/Off                              |

| GPasDsc        | Disabled                            | Disabled                            | Enabled                             | Enabled                             | Enabled                             |

| BootDly[1:0]   | 120ms                               | 80ms                                | 200ms                               | 160ms                               | 80ms                                |

| BBst2Seq[2:0]  | 0% boot                             | 25% boot                            | I <sup>2</sup> C after 100%<br>boot | I <sup>2</sup> C after 100%<br>boot | I <sup>2</sup> C after 100%<br>boot |

| BBst1Seq[2:0]  | 0% boot                             | 0% boot                             | I <sup>2</sup> C after 100%<br>boot | I <sup>2</sup> C after 100%<br>boot | I <sup>2</sup> C after 100%<br>boot |

| LDO2Seq[2:0]   | I <sup>2</sup> C after 100%<br>boot | 50% boot                            | I <sup>2</sup> C after 100%<br>boot | I <sup>2</sup> C after 100%<br>boot | I <sup>2</sup> C after 100%<br>boot |

| LDO1Seq[2:0]   | I <sup>2</sup> C after 100%<br>boot |

**Table 22. Register Default Values**

| REGISTER | REGISTER  |           | DEFAULT VALUES |           |           |           |  |  |

|----------|-----------|-----------|----------------|-----------|-----------|-----------|--|--|

| ADDRESS  | NAME      | MAX20310A | MAX20310B      | MAX20310C | MAX20310D | MAX20310E |  |  |

| 0x00     | Chipld    | 0x00      | 0x00           | 0x00      | 0x00      | 0x00      |  |  |

| 0x01     | ChipRev   | 0x00      | 0x00           | 0x00      | 0x00      | 0x00      |  |  |

| 0x02     | BBstCfg   | 0x07      | 0x0F           | 0x02      | 0x02      | 0x02      |  |  |

| 0x04     | BBst1VSet | 0x12      | 0x2A           | 0x20      | 0x30      | 0x12      |  |  |

| 0x05     | BBst1VCfg | 0x20      | 0x10           | 0x60      | 0x60      | 0x60      |  |  |

| 0x06     | BBst2VSet | 0x06      | 0x18           | 0x06      | 0x0C      | 0x06      |  |  |

| 0x07     | BBst2VCfg | 0x20      | 0x10           | 0x20      | 0x20      | 0x20      |  |  |

| 0x08     | LDO1Vset  | 0x14      | 0x00           | 0x14      | 0x32      | 0x0E      |  |  |

| 0x09     | LDO1Cfg   | 0x20      | 0x11           | 0x20      | 0x20      | 0x20      |  |  |

| 0x0A     | LDO2Vset  | 0x0A      | 0x1A           | 0x0A      | 0x0E      | 0x0A      |  |  |

| 0x0B     | LDO2Cfg   | 0x21      | 0x10           | 0x20      | 0x20      | 0x20      |  |  |

| 0x0D     | MPOCfg    | 0x00      | 0x00           | 0x00      | 0x00      | 0x00      |  |  |

| 0x10     | PwrCfg    | 0xE1      | 0x10           | 0xA3      | 0x62      | 0xE0      |  |  |

| 0x11     | BBstSeq   | 0x22      | 0x32           | 0x77      | 0x77      | 0x77      |  |  |

| 0x12     | LDOSeq    | 0x77      | 0x47           | 0x77      | 0x77      | 0x77      |  |  |

## **Typical Application Circuit**

**Note:** The capacitor values shown reflect an effective capacitance. Derate capacitors appropriately according to specific application requirements.

## **Ordering Information**

| PART           | TEMP RANGE     | PIN-<br>PACKAGE | TOP<br>MARK |

|----------------|----------------|-----------------|-------------|

| MAX20310AEWE+  | -40°C to +85°C | 16 WLP          | AAK         |

| MAX20310AEWE+T | -40°C to +85°C | 16 WLP          | AAK         |

| MAX20310BEWE+  | -40°C to +85°C | 16 WLP          | AAK         |

| MAX20310BEWE+T | -40°C to +85°C | 16 WLP          | AAK         |

| MAX20310CEWE+  | -40°C to +85°C | 16 WLP          | AAK         |

| MAX20310CEWE+T | -40°C to +85°C | 16 WLP          | AAK         |

| MAX20310DEWE+  | -40°C to +85°C | 16 WLP          | AAK         |

| MAX20310DEWE+T | -40°C to +85°C | 16 WLP          | AAK         |

| MAX20310EEWE+  | -40°C to +85°C | 16 WLP          | AAK         |