#### MAX44205

# 180MHz, Low-Noise, Low-Distortion, Fully Differential Op Amp/SAR ADC Driver

#### **General Description**

The MAX44205 is a low-noise, low-distortion fully differential operational amplifier suitable for driving high-speed, high-resolution, 20-/18-/16-bit SAR ADCs, including the MAX11905 ADC family. Featuring a combination of wide 2.7V to 13.2V supply voltage range and wide 400MHz bandwidth, the MAX44205 is suitable for low-power, high-performance data acquisition systems.

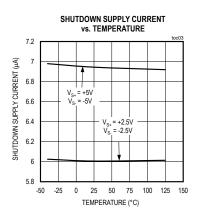

The MAX44205 offers a VOCM input to adjust the output common-mode voltage, eliminating the need for a coupling transformer or AC-coupling capacitors. This adjustable output common-mode voltage allows the MAX44205 to match the input common-mode voltage range of the ADC following it. A proprietary output voltage clamping solution ensures that the buffer output does not violate the ADC's maximum input voltage range, even if the MAX44205's supply rails are higher than the ADC's full-scale range. Shutdown mode consumes only 6.8µA and extends battery life in battery-powered applications or reduces average power in systems cycling between shutdown and periodic data readings.

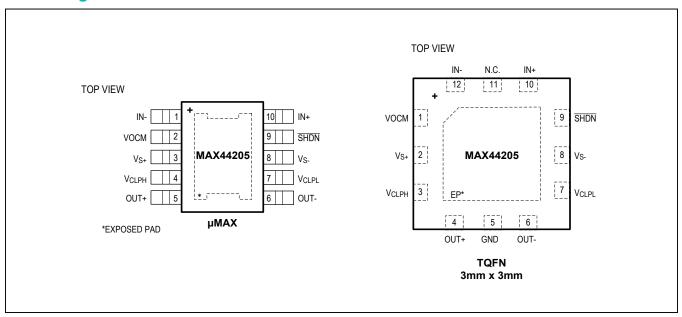

The MAX44205 is available in 12-pin, 3mm x 3mm, TQFN and 10-pin  $\mu$ MAX® packages and is specified for operation over the -40°C to +125°C temperature range.

For related parts and recommended products to use with this part, refer to <a href="https://www.maximintegrated.com/MAX44205.related">www.maximintegrated.com/MAX44205.related</a>.

µMAX is a registered trademark of Maxim Integrated Products. Inc.

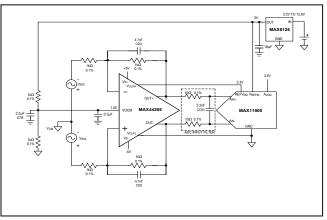

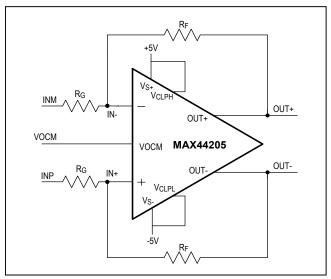

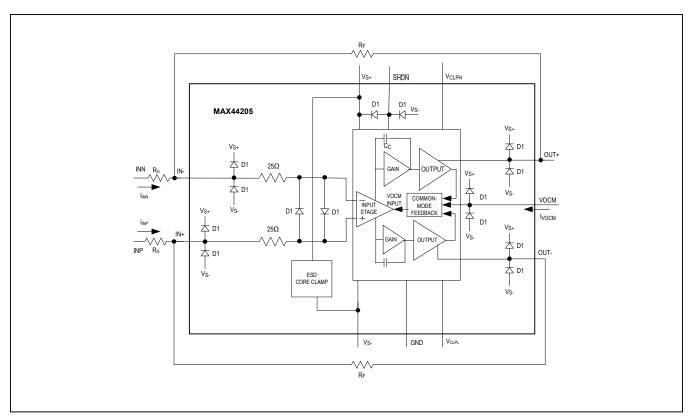

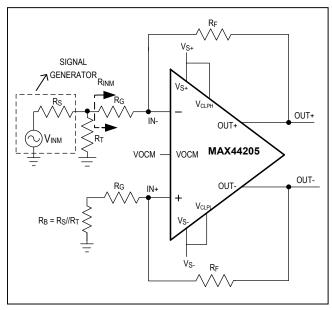

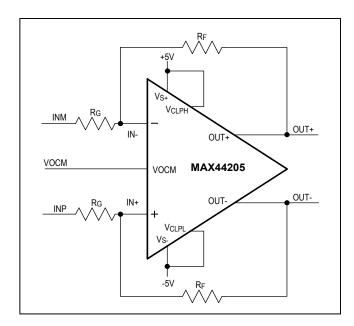

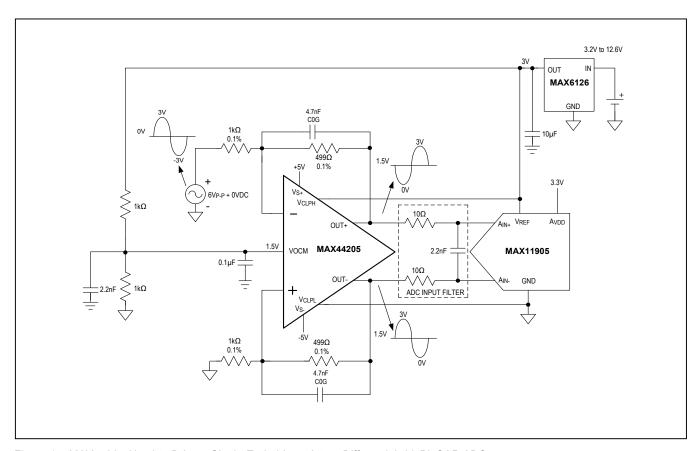

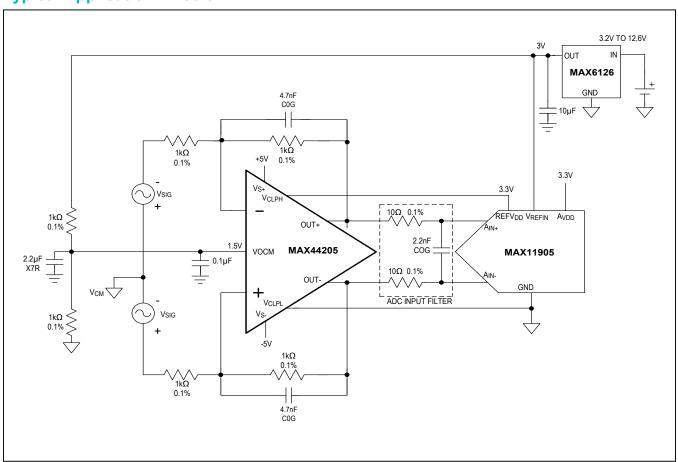

### **Typical Application Circuit**

#### **Benefits and Features**

- Low Input Noise to Drive Precision SAR ADCs

- 3.1nV/√Hz at 1kHz

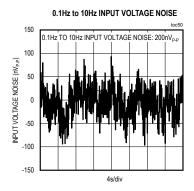

- 200nV<sub>P-P</sub> from 0.1Hz to 10Hz

- High Speed for DC and AC Applications

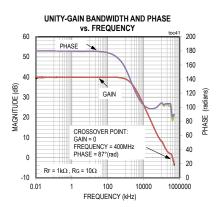

- · Gain-Bandwidth Product 400MHz

- -3dB Gain-Bandwidth Product 180MHz

- Slew Rate 180V/µs

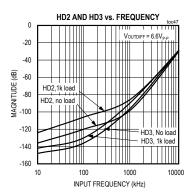

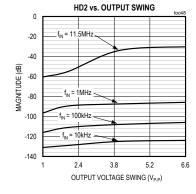

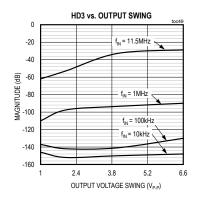

- Ultra-Low Distortion Drives AC Inputs to 20-Bit SAR ADCs

- HD2 = -141dB, HD3 = -146dB at f<sub>IN</sub> = 10kHz, V<sub>OUT.DIFF</sub> = 2V<sub>P-P</sub>

- HD2 = -106dB, HD3 = -115dB at f<sub>IN</sub> = 1MHz, VOUT.DIFF = 2VP-P

- Output Voltage Clamping Pins Enable Low Distortion True Rail-to-Rail ADC Input Operation

- Wide Supply Range (2.7V to 13.2V) Drives Unipolar or Bipolar (±6.6V) Signals

- 3.7mA Quiescent Supply Current with Only 6.8μA Shutdown Current

- 12-Pin, 3mm x 3mm TQFN and 10-Pin μMAX Packages Save Board Space

#### **Applications**

- Single-Ended to Differential Conversion

- High-Speed Process Control

- Medical Imaging

- Fully-Differential Signal Conditioning

- Active Filters

Ordering Information appears at end of data sheet.

### **Absolute Maximum Ratings**

| V <sub>S</sub> + to V <sub>S</sub> | 0.3V to +15V                                 |

|------------------------------------|----------------------------------------------|

| All Other Pins                     | $(V_{S}^{-})$ - 0.3V to $(V_{S}^{+})$ + 0.3V |

| IN+ to IN                          | 0.3V to +0.3V                                |

| Continuous Input Current into Ar   | ny Pin (Note 1)±20mA                         |

| Output Short-Circuit Duration (N   | ote 1) 10s                                   |

| Continuous Power Dissipation (7    | $\Gamma_A = +70^{\circ}C$                    |

| TQFN (derate 14.7mW/°C abo         | ove +70°C)1176.5mW                           |

| uMAX (derate 10.3mW/°C abo         | ove +70°C)824.7mW                            |

| 40°C to +125°C |

|----------------|

| +150°C         |

| 65°C to +150°C |

| +300°C         |

| +260°C         |

|                |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **Package Thermal Characteristics (Note 1)**

Junction-to-Ambient Thermal Resistance ( $\theta_{JA}$ )...........68°C/W Junction-to-Case Thermal Resistance ( $\theta_{JC}$ )...........11°C/W

$\mu$ MAX Junction-to-Ambient Thermal Resistance ( $\theta_{JA}$ ) ......97°C/W Junction-to-Case Thermal Resistance ( $\theta_{JC}$ ).......5°C/W

Note 1: Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

### **Electrical Characteristics (±5V Supply)**

$(V_{S+} = +5V, V_{S-} = -5V, V_{CLPH} = V_{S+}, V_{CLPL} = V_{S-}, V_{OCM} = 0V, \overline{SHDN} = V_{S+}, GND/EP = 0V \text{ (Note 2)}, R_F = R_G = 1k\Omega, R_L = 1k\Omega \text{ (between OUT+ and OUT-)}, T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}, \text{ unless otherwise noted. Typical values are at } T_A = +25^{\circ}\text{C}.) \text{ (Note 3)}$

| PARAMETE <i>R</i>                    | SYMBOL                              | CONDITIONS                                                                | MIN                     | TYP  | MAX                      | UNITS |  |

|--------------------------------------|-------------------------------------|---------------------------------------------------------------------------|-------------------------|------|--------------------------|-------|--|

| POWER SUPPLY                         |                                     |                                                                           |                         |      |                          |       |  |

| Supply Voltage Range                 | Vs                                  | $V_S$ + to $V_S$ -, guaranteed by PSRR (GND = $V_S$ -)                    | 2.7                     |      | 13.2                     | V     |  |

| Quiescent Current                    | 1-                                  | No load, R <sub>L</sub> = ∞                                               |                         | 3.7  | 6.8                      | mA    |  |

| Quiescent Current                    | I <sub>S</sub>                      | SHDN = GND                                                                |                         | 6.8  | 20                       | μA    |  |

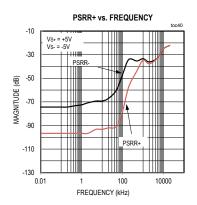

| Power-Supply Rejection Ratio         | PSRR                                | $V_S$ + to $V_S$ - = 2.7V to 13.2V (GND = $V_S$ .)                        | 90                      | 123  |                          | dB    |  |

| DIFFERENTIAL PERFORMANCE             | E—DC SPEC                           | IFICATIONS                                                                |                         |      |                          |       |  |

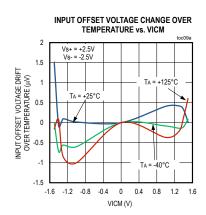

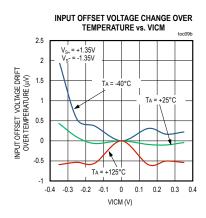

| Input Common-Mode Range              | V <sub>ICM</sub>                    | Guaranteed by CMRR                                                        | (V <sub>S</sub> -) + 1. | 1    | (V <sub>S</sub> +) - 1.1 | V     |  |

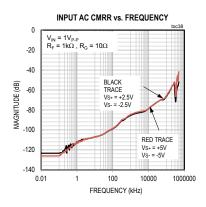

| Input Common-Mode<br>Rejection Ratio | CMRR                                | V <sub>ICM</sub> = (V <sub>S</sub> -) + 1.1V to (V <sub>S</sub> +) - 1.1V | 94                      | 130  |                          | dB    |  |

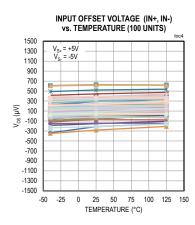

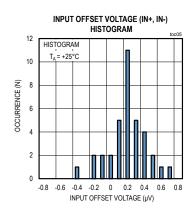

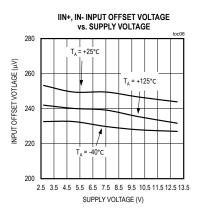

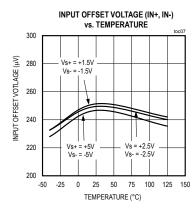

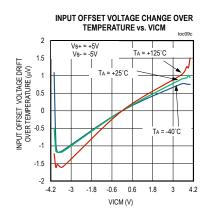

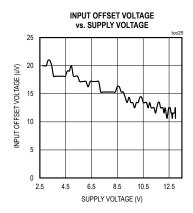

| Input Offset Voltage                 | Vos                                 |                                                                           |                         | ±0.2 | ±1.5                     | mV    |  |

| Input Offset Voltage Drift           | TCVOS                               |                                                                           |                         | 0.2  |                          | μV/°C |  |

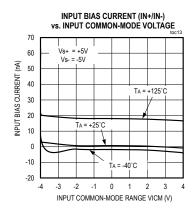

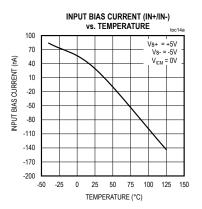

| Input Bias Current                   | I <sub>B</sub>                      |                                                                           |                         | 30   | 750                      | nA    |  |

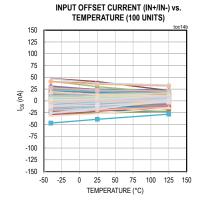

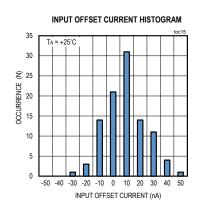

| Input Offset Current                 | los                                 |                                                                           |                         | ±15  | ±350                     | nA    |  |

| Open-Loop Gain                       | A <sub>VOL</sub>                    | V <sub>OUT,DIFF</sub> = 6.6V <sub>P-P</sub> , T <sub>A</sub> = +25°C      | 96                      | 130  |                          | dB    |  |

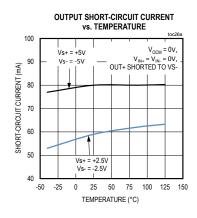

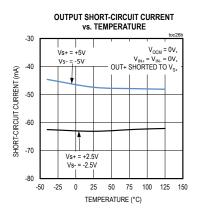

| Output Short-Circuit Current         | I <sub>SC</sub>                     |                                                                           |                         | 60   |                          | mA    |  |

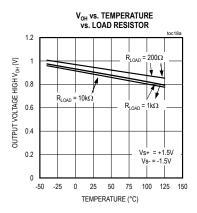

| Output Voltage Swing                 | V <sub>S</sub> + - V <sub>OUT</sub> | Applies to V <sub>OUT+</sub> , V <sub>OUT</sub>                           |                         | 0.98 | 1.15                     |       |  |

| Output Voltage Swing                 | V <sub>OUT</sub> -V <sub>S</sub> -  | Applies to V <sub>OUT+</sub> , V <sub>OUT-</sub>                          |                         | 0.92 | 1.10                     | V     |  |

### **Electrical Characteristics (±5V Supply) (continued)**

$(V_{S+}=+5V,\,V_{S-}=-5V,\,V_{CLPH}=V_{S+},\,V_{CLPL}=V_{S-},\,V_{OCM}=0V,\,\overline{SHDN}=V_{S+},\,GND/EP=0V\,\,(Note\,\,2),\,R_F=R_G=1k\Omega,\,R_L=1k\Omega\,\,(between\,\,OUT+\,\,and\,\,OUT-),\,T_A=-40\,^{\circ}C\,\,to\,\,+125\,^{\circ}C,\,unless\,\,otherwise\,\,noted.$

| PARAMETER                      | SYMBOL                | CONDITIONS                                                    | MIN  | TYP           | MAX      | UNITS             |  |

|--------------------------------|-----------------------|---------------------------------------------------------------|------|---------------|----------|-------------------|--|

| DIFFERENTIAL PERFORMANC        | E—AC SPEC             | FIFICATIONS                                                   |      |               |          |                   |  |

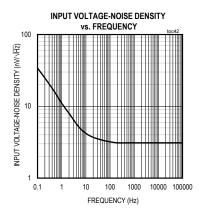

| Input Voltage-Noise Density    | e <sub>N</sub>        | f = 1kHz                                                      |      | 3.1           |          | nV/√Hz            |  |

| Input Voltage Noise            |                       | 0.1Hz < f < 10Hz                                              |      | 200           |          | nV <sub>P-P</sub> |  |

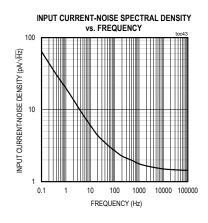

| Input Current-Noise Density    | i <sub>N</sub>        | f = 1kHz                                                      |      | 1.5           |          | pA/√Hz            |  |

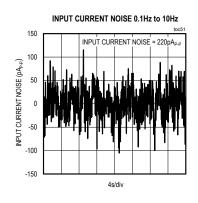

| 1/f Noise Due to Input Current |                       | 0.1Hz < f < 10Hz                                              |      | 220           |          | pA <sub>P-P</sub> |  |

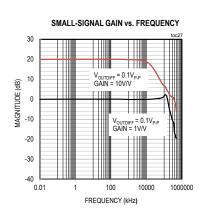

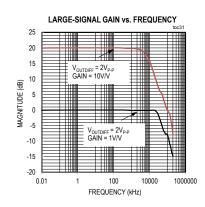

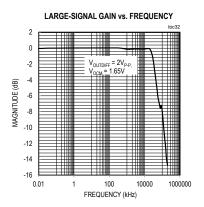

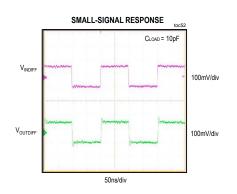

| -3dB Small-Signal Bandwidth    |                       | V <sub>OUT,DIFF</sub> = 0.1V <sub>P-P</sub>                   |      | 180           |          | MHz               |  |

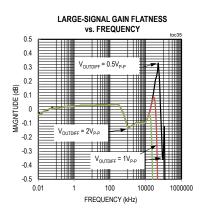

| 0.1dB Gain Flatness Bandwidth  |                       | V <sub>OUT,DIFF</sub> = 0.1V <sub>P-P</sub>                   |      | 25            |          | MHz               |  |

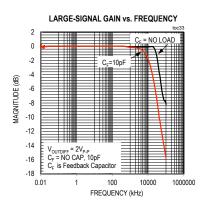

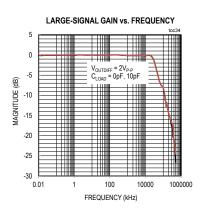

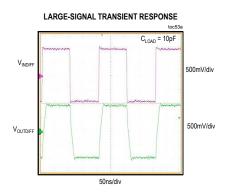

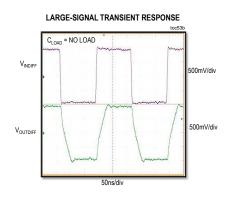

| -3dB Large-Signal Bandwidth    |                       | V <sub>OUT,DIFF</sub> = 2V <sub>P-P</sub>                     |      | 38            |          | MHz               |  |

| 0.1dB Gain Flatness Bandwidth  |                       | V <sub>OUT,DIFF</sub> = 2V <sub>P-P</sub>                     |      | 19            |          | MHz               |  |

| Slew Rate (Differential)       | SR                    | V <sub>OUT,DIFF</sub> = 2V <sub>P-P</sub>                     |      | 180           |          | V/µs              |  |

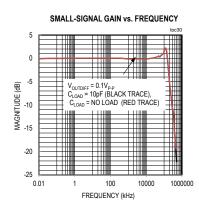

| Capacitive Loading             | CL                    | No sustained oscillations                                     |      | 10            |          | pF                |  |

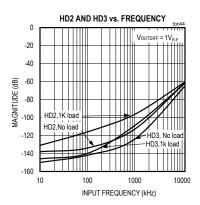

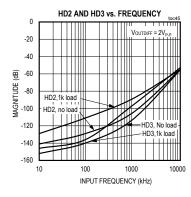

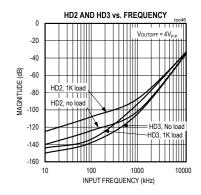

|                                |                       | V <sub>OUT,DIFF</sub> = 2V <sub>P-P</sub> , f = 10kHz         |      | -129/<br>-146 |          |                   |  |

|                                |                       | V <sub>OUT,DIFF</sub> = 2V <sub>P-P</sub> , f = 1MHz          |      | -90/<br>-98   |          |                   |  |

| HD2/HD3 Specifications         |                       | V <sub>OUT,DIFF</sub> = 6.6V <sub>P-P</sub> , f = 10kHz       |      | -124/<br>-142 |          | dBc               |  |

|                                |                       | V <sub>OUT,DIFF</sub> = 6.6V <sub>P-P</sub> , f = 1MHz        |      | -86/<br>-90   |          |                   |  |

| O (III) T                      |                       | Settling to 0.1%, V <sub>OUT,DIFF</sub> = 4V <sub>P-P</sub>   |      | 58            | ,        |                   |  |

| Settling Time                  | t <sub>S</sub>        | Settling to 0.1%, V <sub>OUT,DIFF</sub> = 6.6V <sub>P-P</sub> |      | 107           |          | ns                |  |

| Output Impedance               | R <sub>OUT,DIFF</sub> | f <sub>C</sub> = 1MHz                                         |      | 0.1           |          | Ω                 |  |

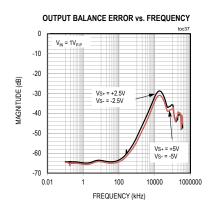

| Output Balance Error           |                       | V <sub>OUT,DIFF</sub> = 1V <sub>P-P</sub> , f = 1MHz          |      | -54           |          | dB                |  |

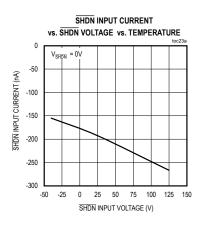

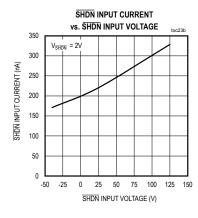

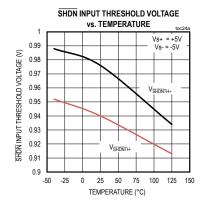

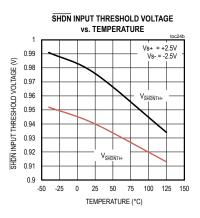

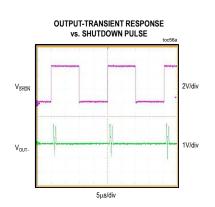

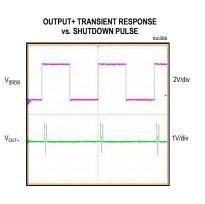

| SHDN INPUT                     |                       |                                                               |      |               |          |                   |  |

| Innut Valtage                  | V <sub>IH</sub>       |                                                               | 1.25 |               |          | V                 |  |

| Input Voltage                  | V <sub>IL</sub>       |                                                               |      |               | 0.65     |                   |  |

| Input Current                  | I <sub>IH</sub>       | V <sub>SHDN</sub> = 2V                                        |      | 0.2           | 1.5      |                   |  |

| Input Current                  | I <sub>IL</sub>       | V <sub>SHDN</sub> = 0V                                        | -1.5 | -0.2          |          | μA                |  |

| Turn-On Time                   | t <sub>ON</sub>       | Output condition                                              |      | 1.2           |          | μs                |  |

| Turn-Off Time                  | t <sub>OFF</sub>      | Output condition                                              |      | 0.8           | <u> </u> | μs                |  |

### **Electrical Characteristics (±5V Supply) (continued)**

$(V_{S+}=+5V,\,V_{S-}=-5V,\,V_{CLPH}=V_{S+},\,V_{CLPL}=V_{S-},\,V_{OCM}=0V,\,\overline{SHDN}=V_{S+},\,GND/EP=0V\,\,(Note\,\,2),\,R_F=R_G=1k\Omega,\,R_L=1k\Omega\,\,(between\,\,OUT+\,\,and\,\,OUT-),\,T_A=-40\,^{\circ}C\,\,to\,\,+125\,^{\circ}C,\,unless\,\,otherwise\,\,noted.$

| PARAMETER                                          | SYMBOL             | CONDITIONS                                                                                           | MIN                      | TYP        | MAX                     | UNITS |

|----------------------------------------------------|--------------------|------------------------------------------------------------------------------------------------------|--------------------------|------------|-------------------------|-------|

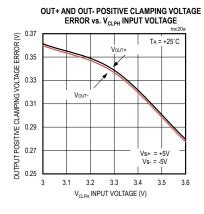

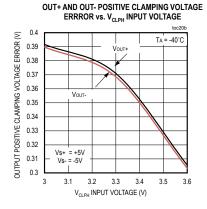

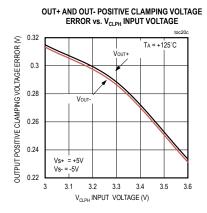

| V <sub>CLPH</sub> INPUT to OUT+, OUT- P            | ERFORMANO          | E                                                                                                    |                          |            |                         |       |

| High-Output Clamping Voltage                       | VOH <sub>CLP</sub> | High-side clamping: applies to OUT+ and OUT- with outputs driven "high", V <sub>CLPH</sub> = +3.3V   | V <sub>CLPH</sub> + 0.34 |            | V                       |       |

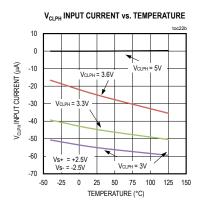

| Input Current                                      | ICLPH              | V <sub>CLPH</sub> = +3.3V                                                                            |                          | -38        |                         | μA    |

| V <sub>CLPL</sub> INPUT to OUT+, OUT- P            | ERFORMANC          | E                                                                                                    |                          |            |                         |       |

| Low-Output Clamping Voltage                        | VOL <sub>CLP</sub> | Low-side clamping: applies to OUT+ and OUT- with outputs driven "low", V <sub>CLPL</sub> = 1.7V      | Vo                       | CLPL - 0.4 | 12                      | V     |

| Input Current                                      | I <sub>CLPL</sub>  | V <sub>CLPL</sub> = 0V                                                                               |                          | 92         |                         | μA    |

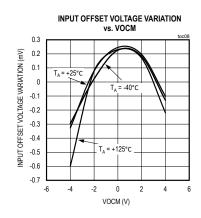

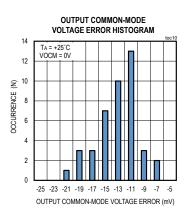

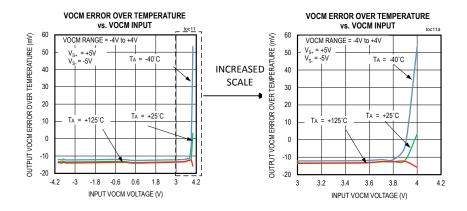

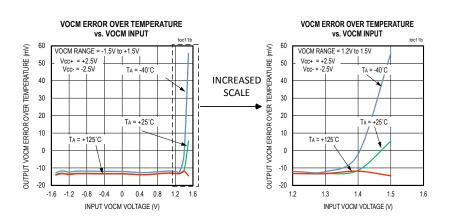

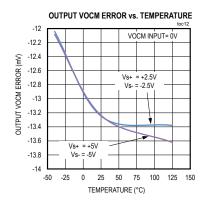

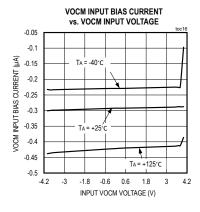

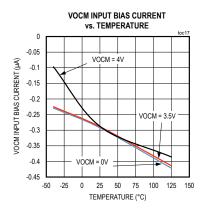

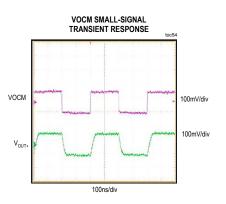

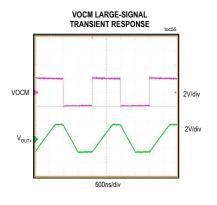

| V <sub>OCM</sub> INPUT to V <sub>OUT,CM</sub> PERF | ORMANCE            |                                                                                                      |                          |            |                         |       |

| Input Voltage Range                                |                    | Guaranteed by gain parameter                                                                         | (V <sub>S</sub> -) + 1.  | 2 (V       | ' <sub>S</sub> +) - 1.2 | V     |

| Output Common-Mode Gain                            | G <sub>OCM</sub>   | $\Delta(V_{OUT,CM})/\Delta(V_{OCM}), V_{OCM} = (V_{S^-}) + 1.2$ to $(V_S^+) - 1.2$                   | 0.99                     | 1          | 1.01                    | V/V   |

| Input Offset Voltage                               |                    |                                                                                                      |                          | ±13        | ±38                     | mV    |

| Input Bias Current                                 |                    |                                                                                                      | -2                       | -0.30      |                         | μΑ    |

| Output Common-Mode<br>Rejection Ratio (Note 4)     | OCMRR              | $2 \times \Delta(V_{OS_{-}})/\Delta(V_{OCM}), V_{OCM} = (V_{S^{-}}) + 1.2$<br>to $(V_{S}^{+}) - 1.2$ | 100                      | 130        |                         | dB    |

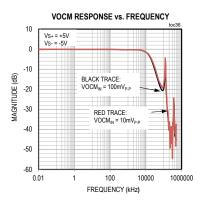

| -3dB Small-Signal Bandwidth                        |                    | V <sub>OUT,CM</sub> = 100mV <sub>P-P</sub>                                                           |                          | 16         |                         | MHz   |

| Slew Rate                                          |                    | V <sub>OUT,CM</sub> = 1V <sub>P-P</sub>                                                              |                          | 6          |                         | V/µs  |

### **Electrical Characteristics (+5V Supply)**

$(V_{S+} = +5V, \textbf{V}_{S-} \textbf{= 0V}, V_{CLPH} = V_{S+}, V_{CLPL} = V_{S-}, \textbf{V}_{OCM} \textbf{= 2.5V}, \overline{SHDN} = V_{S+}, GND/EP = 0V (Note 2), R_F = R_G = 1k\Omega, R_L = 1k\Omega (between OUT+ and OUT-), T_A = -40°C to +125°C, unless otherwise noted. Typical values are at T_A = +25°C.) (Note 3)$

| · / /                                |                    |                                                                           | / \                     | , ,  | ,                       |       |

|--------------------------------------|--------------------|---------------------------------------------------------------------------|-------------------------|------|-------------------------|-------|

| PARAMETER                            | SYMBOL             | CONDITIONS                                                                | MIN                     | TYP  | MAX                     | UNITS |

| POWER SUPPLY                         | •                  |                                                                           | •                       |      |                         |       |

| Supply Voltage Range                 | V <sub>S</sub>     | $V_S$ + to $V_S$ -, guaranteed by PSRR (GND = $V_S$ -)                    | 2.7                     |      | 13.2                    | V     |

| Quiescent Current                    |                    | No load, R <sub>L</sub> = ∞                                               |                         | 3.7  | 6.8                     | mA    |

|                                      | I <sub>S</sub>     | SHDN = GND                                                                |                         | 5.9  | 20                      | μΑ    |

| DIFFERENTIAL PERFORMANCE             | CE—DC SPEC         | IFICATIONS                                                                |                         |      |                         |       |

| Input Common-Mode Range              | V <sub>ICM</sub>   | Guaranteed by CMRR                                                        | (V <sub>S</sub> -) + 1. | 1 (\ | V <sub>S</sub> +) - 1.1 | V     |

| Input Common-Mode<br>Rejection Ratio | CMRR               | V <sub>ICM</sub> = (V <sub>S</sub> -) + 1.1V to (V <sub>S</sub> +) - 1.1V | 94                      | 130  |                         | dB    |

| Input Offset Voltage                 | Vos                |                                                                           |                         | ±0.2 | ±1.5                    | mV    |

| Input Offset Voltage Drift           | TC V <sub>OS</sub> |                                                                           |                         | 0.2  |                         | μV/°C |

### **Electrical Characteristics (+5V Supply) (continued)**

$(V_{S+} = +5V, \textbf{V}_{S-} = \textbf{0V}, V_{CLPH} = V_{S+}, V_{CLPL} = V_{S-}, \textbf{V}_{\textbf{OCM}} = \textbf{2.5V}, \overline{SHDN} = V_{S+}, GND/EP = 0V \text{ (Note 2)}, R_F = R_G = 1k\Omega, R_L = 1k\Omega \text{ (between OUT+ and OUT-)}, T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}, \text{ unless otherwise noted. Typical values are at } T_A = +25^{\circ}\text{C}.) \text{ (Note 3)}$

| PARAMETER                      | SYMBOL                              | CONDITIONS                                                           | MIN  | TYP             | MAX  | UNITS              |

|--------------------------------|-------------------------------------|----------------------------------------------------------------------|------|-----------------|------|--------------------|

| Input Bias Current             | I <sub>B</sub>                      |                                                                      |      | 30              | 750  | nA                 |

| Input Offset Current           | los                                 |                                                                      |      | ±15             | ±350 | nA                 |

| Open-Loop Gain                 | A <sub>VOL</sub>                    | V <sub>OUT,DIFF</sub> = 2.8V <sub>P-P</sub> , T <sub>A</sub> = +25°C | 95   | 120             |      | dB                 |

| Output Short-Circuit Current   | I <sub>SC</sub>                     |                                                                      |      | 60              |      | mA                 |

| Output Voltage Swing           | V <sub>S</sub> + - V <sub>OUT</sub> | Applies to V <sub>OUT+</sub> , V <sub>OUT</sub>                      |      | 0.95            | 1.1  | V                  |

| Output voltage Swing           | V <sub>OUT</sub> - V <sub>S</sub> - | Applies to V <sub>OUT+</sub> , V <sub>OUT</sub>                      |      | 0.85            | 1.1  | ]                  |

| DIFFERENTIAL PERFORMANC        | E—AC SPEC                           | IFICATIONS                                                           | ,    |                 |      |                    |

| Input Voltage-Noise Density    | e <sub>N</sub>                      | f = 1kHz                                                             |      | 3.1             |      | nV/√ <del>Hz</del> |

| Input Voltage Noise            |                                     | 0.1Hz < f < 10Hz                                                     |      | 200             |      | nV <sub>P-P</sub>  |

| Input Current-Noise Density    | i <sub>N</sub>                      | f = 1kHz                                                             |      | 1.5             |      | pA/√Hz             |

| 1/f Noise Due to Input Current |                                     | 0.1Hz < f < 10Hz                                                     |      | 220             |      | pA <sub>P-P</sub>  |

| -3dB Small-Signal Bandwidth    |                                     | V <sub>OUT,DIFF</sub> = 0.1V <sub>P-P</sub>                          |      | 180             |      | MHz                |

| 0.1dB Gain Flatness Bandwidth  |                                     | V <sub>OUT,DIFF</sub> = 0.1V <sub>P-P</sub>                          |      | 25              |      | MHz                |

| -3dB Large-Signal Bandwidth    |                                     | V <sub>OUT,DIFF</sub> = 2V <sub>P-P</sub>                            |      | 38              |      | MHz                |

| 0.1dB Gain Flatness Bandwidth  |                                     | V <sub>OUT,DIFF</sub> = 2V <sub>P-P</sub>                            |      | 19              |      | MHz                |

| Slew Rate (Differential)       | SR                                  | V <sub>OUT,DIFF</sub> = 2V <sub>P-P</sub>                            |      | 120             |      | V/µs               |

| Capacitive Loading             | CL                                  | No sustained oscillations                                            |      | 10              |      | pF                 |

| LIDO// IDO O continue          |                                     | V <sub>OUT</sub> = 4V <sub>P-P</sub> , f = 10kHz                     |      | -123/<br>-145   |      | ID.                |

| HD2/HD3 Specifications         |                                     | V <sub>OUT</sub> = 4V <sub>P-P</sub> , f = 1MHz                      |      | -88.5/<br>-95.5 |      | dBc                |

| Cottling Time                  | 4 _                                 | Settling to 0.1%, V <sub>OUT,DIFF</sub> = 4V <sub>P-P</sub>          |      | 58              |      | no                 |

| Settling Time                  | t <sub>S</sub>                      | Settling to 0.1%, V <sub>OUT,DIFF</sub> = 6.6V <sub>P-P</sub>        |      | 100             |      | ns                 |

| Output Impedance               | R <sub>OUT,DIFF</sub>               | f <sub>C</sub> = 1MHz (V <sub>OUT,DIFF</sub> )                       |      | 0.1             |      | Ω                  |

| Output Balance Error           |                                     | $V_{OUT,DIFF} = 1V_{P-P}$ , $f = 1MHz$                               |      | -52             |      | dB                 |

| SHDN INPUT                     |                                     |                                                                      |      |                 |      |                    |

| Innut Voltage                  | V <sub>IH</sub>                     |                                                                      | 1.25 |                 |      | V                  |

| Input Voltage                  | V <sub>IL</sub>                     |                                                                      |      |                 | 0.65 | \ \ \              |

| Input Current                  | I <sub>IH</sub>                     | V <sub>SHDN</sub> = 2V                                               |      | 0.2             | 1.5  |                    |

| Input Current                  | I <sub>IL</sub>                     | V <sub>SHDN</sub> = 0V                                               | -1.5 | -0.2            |      | μA                 |

| Turn-On Time                   | t <sub>ON</sub>                     | Output condition                                                     |      | 1.2             |      | μs                 |

| Turn-Off Time                  | t <sub>OFF</sub>                    | Output condition                                                     |      | 0.8             |      | μs                 |

### **Electrical Characteristics (+5V Supply) (continued)**

$(V_S+=+5V, \textbf{V}_S-\textbf{= 0V}, V_{CLPH}=V_S+, V_{CLPL}=V_S-, \textbf{V}_{\textbf{OCM}}\textbf{= 2.5V}, \overline{SHDN}=V_{S+}, GND/EP=0V \text{ (Note 2)}, R_F=R_G=1k\Omega, R_L=1k\Omega \text{ (between OUT+ and OUT-)}, T_A=-40^{\circ}\text{C to } +125^{\circ}\text{C}, \text{ unless otherwise noted. Typical values are at } T_A=+25^{\circ}\text{C}.) \text{ (Note 3)}$

| PARAMETER                                      | SYMBOL             | CONDITIONS                                                                                          | MIN                      | TYP     | MAX                    | UNITS |

|------------------------------------------------|--------------------|-----------------------------------------------------------------------------------------------------|--------------------------|---------|------------------------|-------|

| V <sub>CLPH</sub> INPUT to OUT+, OUT- P        | ERFORMANO          | ČE                                                                                                  |                          |         |                        |       |

| High-Output Clamping Voltage                   | VOH <sub>CLP</sub> | High-side clamping: applies to OUT+ and OUT- with outputs driven "high", V <sub>CLPH</sub> = 3.3V   | V <sub>CLPH</sub> + 0.39 |         | V                      |       |

| Input Current                                  | I <sub>CLPH</sub>  | V <sub>CLPH</sub> = 3.3V                                                                            |                          | -45     |                        | μA    |

| V <sub>CLPL</sub> INPUT to OUT+, OUT- P        | ERFORMANC          | E                                                                                                   |                          |         | ,                      |       |

| Low-Output Clamping Voltage                    | VOL <sub>CLP</sub> | Low-side clamping: applies to OUT+ and OUT- with outputs driven "low", V <sub>CLPL</sub> = 1.7V     | VC                       | LPL - C | .42                    | V     |

| Input Current                                  | ICLPL              | V <sub>CLPL</sub> = 0V                                                                              |                          | 85      |                        | μA    |

| VOCM INPUT to V <sub>OUT,CM</sub> PERF         | ORMANCE            |                                                                                                     |                          |         |                        |       |

| Input Voltage Range                            |                    | Guaranteed by gain parameter                                                                        | (V <sub>S</sub> -) +1.2  | 2       | (V <sub>S</sub> +)-1.2 | V     |

| Output Common-Mode Gain                        | G <sub>OCM</sub>   | $\Delta(V_{OUT,CM})/\Delta(V_{OCM}), V_{OCM} = (V_{S^-}) + 1.2$<br>to $(V_S^+) - 1.2$               | 0.99                     | 1       | 1.01                   | V/V   |

| Input Offset Voltage                           |                    |                                                                                                     |                          | ±13     | ±38                    | mV    |

| Input Bias Current                             |                    |                                                                                                     | -2                       | -0.3    |                        | μΑ    |

| Output Common-Mode<br>Rejection Ratio (Note 4) | OCMRR              | $2 \times \Delta(V_{OS})/\Delta(V_{OCM}),$<br>$V_{OCM} = (V_{S}-) + 1.2 \text{ to } (V_{S}+) - 1.2$ | 90                       | 130     |                        | dB    |

| -3dB Small-Signal Bandwidth                    |                    | V <sub>OUT,CM</sub> = 100mV <sub>P-P</sub>                                                          |                          | 16      |                        | MHz   |

| Slew Rate                                      |                    | V <sub>OUT,CM</sub> = 1V <sub>P-P</sub>                                                             |                          | 6       |                        | V/µs  |

Note 2: GND and EP are internally shorted. GND pin is only present on the 12-pin TQFN package and GND is the exposed pad on the 10-pin  $\mu$ MAX package.

**Note 3:** All devices are 100% production tested at  $T_A = +25$ °C. Temperature limits are guaranteed by design.

Note 4: OCMRR is mainly determined by external gain resistors matching. The formula used for OCMRR calculation assumes that gain resistors are perfectly matched. Therefore, OCMRR =  $(1 + RF/RG) \times \Delta V_{OS}/\Delta V(VOCM)$ .

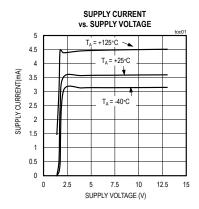

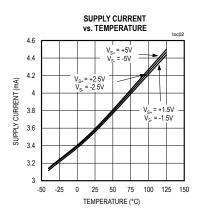

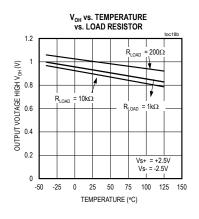

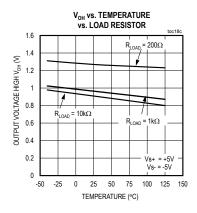

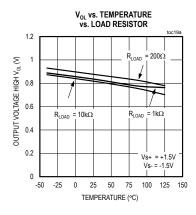

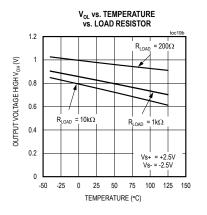

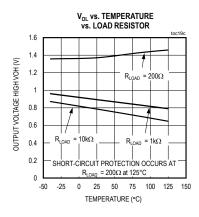

### **Typical Operating Characteristics**

### **Typical Operating Characteristics (continued)**

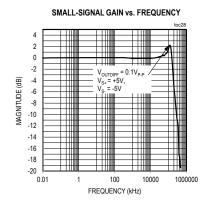

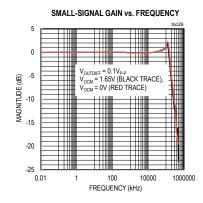

$(V_{S+} = +5V, V_{S-} = -5V, V_{CLPH} = V_{S+}, V_{CLPL} = V_{S-}, V_{OCM} = 0V, \overline{SHDN} = V_{S+}, GND/EP = 0V, R_F = R_G = 1k\Omega, R_L = 1k\Omega \ (between OUT+ and OUT-), T_A = -40^{\circ}C \ to +125^{\circ}C, unless otherwise noted.)$

### **Typical Operating Characteristics (continued)**

### **Typical Operating Characteristics (continued)**

### **Typical Operating Characteristics (continued)**

### **Typical Operating Characteristics (continued)**

### **Typical Operating Characteristics (continued)**

### **Typical Operating Characteristics (continued)**

$(V_{S+} = +5V, V_{S-} = -5V, V_{CLPH} = V_{S+}, V_{CLPL} = V_{S-}, V_{OCM} = 0V, \overline{SHDN} = V_{S+}, GND/EP = 0V, R_F = R_G = 1k\Omega, R_L = 1k\Omega \ (between OUT+ and OUT-), T_A = -40^{\circ}C \ to +125^{\circ}C, unless otherwise noted.)$

### **Typical Operating Characteristics (continued)**

### **Typical Operating Characteristics (continued)**

$(V_{S+}=+5V,V_{S-}=-5V,V_{CLPH}=V_{S+},V_{CLPL}=V_{S-},V_{OCM}=0V,\overline{SHDN}=V_{S+},GND/EP=0V,R_F=R_G=1k\Omega,R_L=1k\Omega \ (between OUT+ and OUT-),T_A=-40^{\circ}C \ to +125^{\circ}C, unless otherwise noted.)$

### **Typical Operating Characteristics (continued)**

$(V_{S+}=+5V,V_{S-}=-5V,V_{CLPH}=V_{S+},V_{CLPL}=V_{S-},V_{OCM}=0V,\overline{SHDN}=V_{S+},GND/EP=0V,R_F=R_G=1k\Omega,R_L=1k\Omega \ (between OUT+ and OUT-),T_A=-40^{\circ}C \ to +125^{\circ}C, unless otherwise noted.)$

## **Pin Configurations**

## **Pin Description**

| I    | PIN  |                   |                                                                             |  |  |  |

|------|------|-------------------|-----------------------------------------------------------------------------|--|--|--|

| TQFN | μМΑХ | NAME              | Output Common-Mode Voltage Input                                            |  |  |  |

| 1    | 2    | VOCM              | Output Common-Mode Voltage Input                                            |  |  |  |

| 2    | 3    | V <sub>S+</sub>   | Positive Supply Voltage Input                                               |  |  |  |

| 3    | 4    | V <sub>CLPH</sub> | High-Output Voltage Clamping Input                                          |  |  |  |

| 4    | 5    | OUT+              | Noninverting Differential Output                                            |  |  |  |

| 5    | *    | GND               | External Ground Input. *The µMAX exposed pad also functions as GND.         |  |  |  |

| 6    | 6    | OUT-              | Inverting Differential Output                                               |  |  |  |

| 7    | 7    | V <sub>CLPL</sub> | Low-Output Voltage Clamping Input                                           |  |  |  |

| 8    | 8    | V <sub>S-</sub>   | Negative Supply Voltage Input                                               |  |  |  |

| 9    | 9    | SHDN              | Shutdown Mode Input (active low)                                            |  |  |  |

| 10   | 10   | IN+               | Noninverting Input                                                          |  |  |  |

| 11   | _    | N.C.              | No Connection. Not connected internally                                     |  |  |  |

| 12   | 1    | IN-               | Inverting Input                                                             |  |  |  |

| _    | _    | EP                | Exposed Pad. Connected to GND internally. The μMAX exposed pad is also GND. |  |  |  |

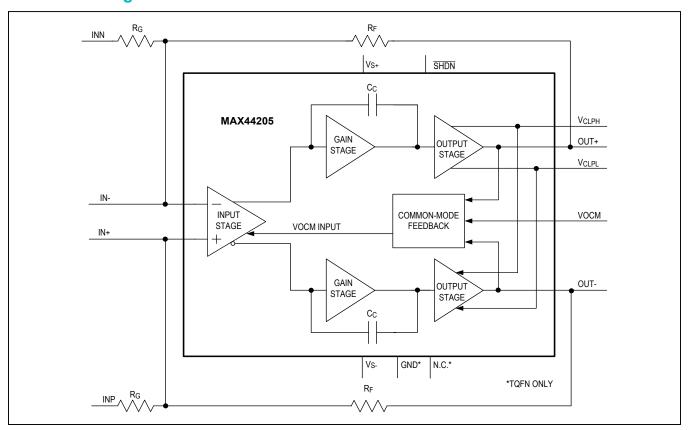

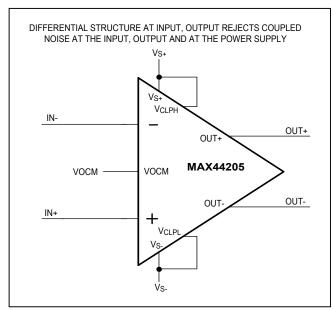

#### **Functional Diagram**

#### **Detailed Description**

The MAX44205 is a low-noise, low-power, very low-distortion fully differential (input and output) op amp capable of driving high-resolution 16-/18-/20-bit SAR ADCs with input signal frequencies from DC to 1MHz. These high-resolution signal chain ICs are used in test and measurement applications, as well as medical instrumentation and industrial control systems.

This fully differential op amp accepts either single-ended or fully differential input signals at its inputs and converts the input signal into fully differential outputs that are exactly equal in amplitude and 180° apart in phase. Ideally, the noise and distortion performance of the amplifier should match or exceed the linearity of the ADC to preserve the overall system accuracy.

Four precisely matched resistors (two for feedback and two for gain setting) set the differential closed-loop gain as shown in the *Functional Diagram*.

The MAX44205 has a unique output stage clamping feature. Pins ( $V_{Cl\ PH}$  and  $V_{Cl\ Pl}$ ) can be useful in protecting the ADC

from electrical overstress when the driver output exceeds the input range of ADC. If  $V_{CLPH}$  and  $V_{CLPL}$  are connected to  $V_{CC}$  and GND of the ADC respectively, then the output of the driver will not go out beyond the power supply of the ADC.

The MAX44205 has an output voltage common-mode (VOCM) input to set the DC common-mode voltage level of the differential outputs without affecting the balance of the AC differential output signal on each output. The MAX44205 also features a low-power shutdown mode that consumes only  $6.8\mu A$  of supply current from the  $V_{S+}$  pin. Note that while the outputs are floating during shutdown, the feedback networks may provide paths for current to flow from the input source(s).

#### **Terminology and Definitions**

Figure 1. Differential Input, Differential Output Configuration (Decoupling Capacitors Not Shown for Simplicity)

#### **Differential Voltage**

The differential voltage at the input is the voltage applied across INP to INM and the differential voltage at the output is the voltage across OUT+ to OUT-. Equations for input and output differential voltages are listed below:

$$V_{IN,dm} = (V_{INP} - V_{INM})$$

$V_{OUT,dm} = (V_{OUT+} - V_{OUT-})$

$V_{OUT+}$  and  $V_{OUT-}$  are voltages at the OUT+ and OUT-terminals with respect to output common-mode voltage set by the VOCM input voltage.

#### Common-Mode Voltage

The common-mode voltage at the input is the average of the input pins (IN+ and IN-) and at the output, it is the average of two outputs. Equations for input and output common-mode voltages are listed below:

$$V_{IN,cm} = (V_{IN+} + V_{IN-})/2$$

$V_{OUT,cm} = V_{OCM} = (V_{OUT+} + V_{OUT-})/2$

Though it was mentioned that the input common-mode voltage is the average of the voltage seen on both input pins, the range is slightly different depending on if the input signal is fully differential or single ended.

For fully differential input applications, where  $V_{INP}$  =  $-V_{INM}$ , the common-mode input voltage is:

$$\begin{split} V_{IN,cm} = (V_{IN+} + V_{IN-})/2 &\cong VOCM \ x \ R_G/(R_F + R_G) \\ &+ V_{CM} \ x \ R_F/(R_F + R_G). \end{split}$$

With single-ended input applications there will be an input signal component to the input common-mode voltage, as there is no out-of-phase signal not applied on the other input. Applying  $V_{\mbox{\footnotesize{INP}}}$  (connecting  $V_{\mbox{\footnotesize{INM}}}$  to zero), the common-mode input voltage is:

$$V_{IN,cm} = (V_{IN+} + V_{IN-})/2 \cong VOCM \times R_G/(R_F + R_G) + V_{CM} \times R_F/(R_F + R_G) + V_{INP}/2 \times R_F/(R_F + R_G)$$

#### **Common-Mode Offset Voltage**

The common-mode offset voltage is defined as the difference between the voltage applied to the VOCM terminal and the output common-mode voltage.

#### Input Offset Voltage, CMRR, and VOCM CMRR

Input offset voltage is the differential voltage error ( $V_{OS,dm}$ ) between the input pins (IN+ and IN-). CMRR performance is affected by both the input offset voltage error at the input due to change in input common-mode voltage ( $V_{IN\_,cm}$ ) and the change in input offset voltage ( $V_{OS,dm}$ ) due to VOCM change. So, there are two CMRR terms:

CMRR<sub>VIN,cm</sub> =

$$\Delta$$

(V<sub>IN\_,cm</sub>)/ $\Delta$ (V<sub>OS,dm</sub>)

CMRR<sub>VOCM</sub> =  $\Delta$ (VOCM)/ $\Delta$ (V<sub>OS,dm</sub>)

The output common-mode rejection ratio is strongly affected by the matching of gain-setting feedback network.

#### **Output Balance Error**

An ideal differential output implies the two outputs of the amplifier should be exactly equal in amplitude but 180° apart in phase. Output balance is the measure of how well the outputs are balanced and is defined as the ratio of the output common-mode voltage to the output differential signal. It is generally expressed as dB in log scale.

Output Balance Error =  $20 \times \log|(V_{OUT,cm})/(V_{OUT,dm})|$

#### **Operation and Equations**

The <u>Functional Diagram</u> details the internal architecture of the differential op amp. The negative feedback loop across the outputs to respective inputs force voltages on IN+ and IN- pins equal to each other. That implies:

$$\frac{V_{INP}}{R_F} = \frac{-V_{OUT-}}{R_G}$$

$$\frac{V_{INN}}{R_F} = \frac{-V_{OUT+}}{R_G}$$

From above equations see the relationship between differential output voltage and inputs.

$$(V_{OUT+} - V_{OUT-}) = (V_{INP} - V_{INN}) \times \frac{R_F}{R_G}$$

The VOCM input voltage with the help of the common-mode feedback circuit drives the output common-mode voltage level to VOCM. This results in the following output relations:

$$(V_{OUT+}) = (VOCM) + \frac{V_{OUT,DM}}{2}$$

$$(V_{OUT-}) = (VOCM) - \frac{V_{OUT,DM}}{2}$$

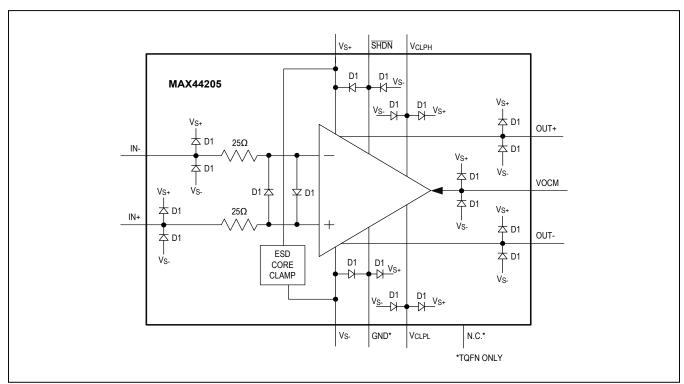

#### Input and ESD Protection

As shown in Figure 2, ESD diodes are present on all the pins with respect to the  $V_{S+}$  and  $V_{S-}$  pins so that these ESD diodes turn on and protect the part when voltages on these pins go out of range from either supplies by more than one diode drop. There are two series input resistors and back-to-back diode protection between the inputs for protection against excessive differential voltages across the amplifier's inputs.

#### **VCLPH** and **VCLPL** Output Clamp Supplies

The MAX44205 design incorporates patent-pending circuitry that limits the outputs voltage levels in order to avoid overstressing an ADC that accepts the MAX44205 outputs. The outputs are clipped if the voltage swing exceeds

the voltage levels set at  $V_{CLPH}$  and  $V_{CLPL}$  inputs. This is an advantageous feature when the front-end amplifier is operated with split supplies or a wider supply voltage range than that of an ADC. For example, the ADC detailed in the <u>Typical Application Circuit</u> (MAX11905) operates from a single 3V or 3.3V supply and ground. When operating the MAX44205 from  $\pm 5$ V supplies, it is desirable to limit the amplifier outputs between 0V and 3.3V. Connect VCLPH to 3.3V and VCLPL to 0V.

#### **Exposed Pad**

Both of the MAX44205 packages have their exposed pads internally connected to GND. The EP should be connected to the PCB's ground plane for optimum thermal dissipation.

#### **SHDN** Input

#### **SHDN** Operation

The MAX44205 offers a shutdown mode for low-power operation. Drive  $\overline{SHDN}$  below 0.65V (typ) with respect to GND/EP to shut down the part and only 6.8 $\mu$ A (typ) will be drawn from V<sub>S+</sub>.  $\overline{SHDN}$  and GND are referred to each other and allow for convenient interfacing to the logic-level input signals, which operate independent of the V<sub>S+</sub> and V<sub>S-</sub> supplies.

Figure 2. Showing ESD protection scheme in MAX44205

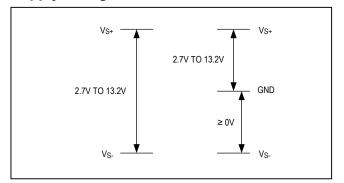

In single-supply operation, connect  $V_{S-}$  and GND to 0V. In single-supply mode,  $V_{S+}$  can range between 2.7V to 13.2V. In dual supply operation,  $V_{S+}$  and  $V_{S-}$  are connected to the positive and negative voltage rails, respectively (see <u>Figure 4</u>). In dual supply operation, <u>SHDN</u> is still referred to GND. To keep the part active, <u>SHDN</u> needs to be maintained between 1.25V and  $V_{S+}$  with respect to GND/EP.

For the shutdown function to work correctly in very low supply voltage applications, one has to maintain a minimum of 2.7V difference between the  $V_{S+}$  and GND pins. This is necessary when operation with  $\pm 1.35V$  supplies is required and in that case, the GND pin and EP need to be tied to  $V_{S-}$ .

# Shutdown Operation with External Components and Stimuli

In shutdown mode, quiescent supply current is low. However, there will be currents flowing into the IC pins

depending on the external components and applied signals. Figure 3 shows the block diagram with these current paths and shows internal protection devices. In active operation mode (shutdown disabled), input signals are applied to INP and INN. The voltage applied to the VOCM pin sets the output common-mode voltage.

In shutdown mode, the voltages applied to INP, INN, and VOCM will interact with the IC internal components resulting in current flowing into the IC pins. It must be noted that the op amp's outputs, OUT+ and OUT-, exhibit high-impedance state in shutdown mode.

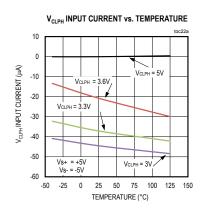

# Shutdown Quiescent Currents Dependency on $V_{CLPL}$ and $V_{CLPH}$

Supply currents exhibit dependency with respect to clamping voltages applied to the  $V_{CLPL}$  and  $V_{CLPH}$  pins. These currents will not be seen if the clamping feature is not used or the  $V_{CLPL}$  and  $V_{CLPH}$  pins are left open.

Figure 3. Currents Flowing when MAX44205 is in Shutdown

#### **Applications Information**

The fully differential op amp is shown in Figure 5 for reference. Fully differential op amps provide a lot of advantages, including rejecting common-mode noise coupled to the input, the output, and from the power supply. The effective output swing is increased by a factor of two as the outputs are equal in amplitude and 180° apart in phase.

For example, by applying a fully differential input signal of 1V<sub>P-P</sub> across INP and INN on Figure 1 there is a 2V<sub>P-P</sub> differential output voltage swing. Another advantage of having fully differential outputs is that even order harmonics will be suppressed at the output.

#### Potential Difference Between Supply Voltage Pins

Figure 4. Explaining Potential Difference Between Supply Voltage Pins

Figure 5. Showing Fully Differential Architecture

#### **Input Impedance Mismatch Due to Source Impedance**

The impedance looking into the IN+ and IN- nodes of Figure 5 depends on how the inputs are driven. For a fully differential input signal, i.e., V<sub>INP</sub> = -V<sub>INM</sub>, the input impedance looking into inputs is shown in Figure 6.

$$R_{INP} = R_{INM} = R_{G}$$

For a single-ended input signal, since the inputs are not balanced, the input impedance actually increases relative to the fully differential case. The input impedance looking into either input is:

$$R_{INP} = R_{INM} = \frac{R_G}{[1 - (\frac{1}{2}) \times \frac{R_F}{(R_G + R_F)}]}$$

Apart from the single-ended input and differential input signal cases, an input signal source from a nonzero source impedance may cause imbalance between feedback resistor networks for single-ended input driving case as shown in the Figure 7. A terminating resistor RT as shown in Figure 7 is used to impedance match to the source such that:

$$R_T = R_{INM} \times \frac{R_S}{R_{INM} - R_S}$$

Figure 6. Fully Differential Amplifier

A terminating resistor is inserted to correct for impedance mismatch between the source and input. The gain resistor mismatch across feedback networks is created due to the parallel combination of R<sub>T</sub> and R<sub>S</sub>. So, to balance out the gain resistor mismatch on the other input, insert RR such that:

$$R_B = R_T \times \frac{R_S}{R_T - R_S}$$

#### **Effects of Input Resistor Mismatch**

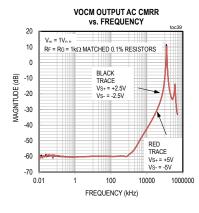

If there is a mismatch between the feedback resistor (R<sub>F</sub>) pair and gain resistor (R<sub>G</sub>) pair, there will be a small delta in the feedback factor across the input pins. This delta in the feedback factor is a source of common-mode error. To apply an AC CMRR test without a differential input signal, the common-mode rejection is proportional to the resistor mismatch. Using 0.1% or better resistors will mitigate most of the problems and will yield good CMRR performance.

#### **Noise Calculations**

The MAX44205 offers input voltage and current noise densities of  $3.1 \text{nV}/\sqrt{\text{Hz}}$  and  $1.5 \text{pA}/\sqrt{\text{Hz}}$ , respectively. From Figure 6, the total output noise is a combination of noise generated by the amplifier and the feedback and gain resistors. The total output noise generated by both the amplifier and the feedback components is given by the equation:

Figure 7. Compensation for Source Impedance

$$e_{nt} = \sqrt{\frac{[e_n \times (1 + \frac{R_F}{R_G})]^2 + 2 \times (i_n \times R_F)^2}{+2 \times (e_{nRG} \times \frac{R_F}{R_G})^2 + 2 \times (e_{nRF})^2}}$$

en is the input voltage-noise density

in is the input current-noise density

enRG is the noise voltage density contributed by the gain resistor R<sub>G</sub>

enRF is the noise voltage density contributed by the feedback resistor RF

Resistor Noise =  $\sqrt{4 \times k \times T \times R \times \Delta f}$  in  $nV/\sqrt{Hz}$

T is absolute temperature in Kelvin

k is Boltzmann constant: k = 1.38 x 10-23 in joules/Kelvin

R is resistance in ohms and  $\Delta f$  is frequency range in Hertz

The MAX44205 input-referred voltage noise contributes the equivalent noise of a  $600\Omega$  resistor. For low noise, keep the source and feedback resistance at or below this value, i.e.  $R_S + R_G//R_F \le 600\Omega$ . At combinations of below  $600\Omega$ , amplifier noise is dominant, but in the region  $600\Omega$ to  $10k\Omega$ , the noise is dominated by resistor thermal noise. Any larger resistances beyond that, the noise current multiplied by the total resistance dominated the noise.

Figure 8. Fully Differential Amplifier

Lower resistor values are ideal for low-noise performance at the cost of increased distortion due to increased loading of the feedback network on the output stage. Higher resistor values will yield better distortion performance due to less loading on the output stage but at the cost of increase in higher output noise.

# Improving Stability using Feedback Capacitors

When the MAX44205 is configured such that a combination of parasitic capacitances at the inverting input form a pole whose frequency lies within the closed-loop bandwidth of the amplifier, a feedback capacitor across the feedback resistor is needed to form a zero at a frequency close to the frequency of the parasitic pole to recover the lost phase margin.

Adding larger value feedback capacitors will reduce the peaking of the amplifier but decreases the closed-loop -3dB bandwidth.

#### **Layout and Bypass Capacitors**

For single-supply applications, it is recommended to place a  $0.1\mu F$  NPO or C0G ceramic capacitor within 1/8th of an inch from the  $V_{S+}$  pin to ground and to also connect a  $10\mu F$  ceramic capacitor within 1in of the  $V_{S+}$  pin to GND. One can short  $V_{S-}$ , GND, and EP in that case.

In dual-supply applications, it is recommended to place a 0.1  $\mu F$  NPO or C0G ceramic capacitor within 1/8th of an inch from the  $V_{S+}$  and  $V_{S-}$  pins to GND and place 10  $\mu F$  ceramic capacitors within 1in of the  $V_{S+}$  and  $V_{S-}$  pins to GND. Low ESR\ESL NPO capacitors are recommended for 0.1  $\mu F$  or smaller decoupling capacitors. A 0.1  $\mu F$  or 0.22  $\mu F$  capacitor should be placed as close as possible between the VOCM input pin to ground.

Signal routing into and out of the part should be direct and as short as possible into and out of the op amp inputs and outputs. The feedback path should be carefully routed with the shortest path possible without any parasitic capacitance forming between feedback trace and board power planes. Ground and power planes should be removed from directly under the amplifier input and output pins. Also, care should be taken such that there will be no parasitic capacitance formed around the summing nodes at the inputs that could affect the phase margin of the part.

Any load capacitance beyond a few picofarads needs to be isolated using series output resistors placed as close as possible to the output pins to avoid excessive peaking or instability.

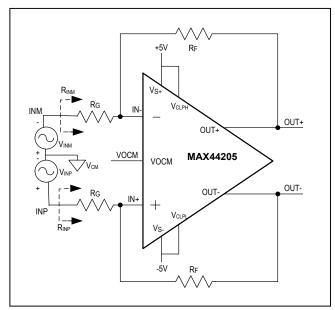

#### **Driving a Fully Differential ADC**

The MAX44205 was designed to drive fully differential SAR ADCs such as the MAX11905. The MAX11905 is part of a family of 20-/18-/16-bit, 1.6Msps/1Msps ADCs that offer excellent AC and DC performance. The *Typical Application Circuit* details a fully differential input to the MAX44205, which then drives the fully differential MAX11905 ADC inputs through the ADC input filter shown in the dashed box.

The MAX6126 provides a 3V reference output voltage, which is fed to the ADC's reference. The MAX44205's common mode (VOCM) is created by dividing down the reference voltage by a factor of two. A pair of  $1k\Omega$  0.1% resistors are used for this purpose. The VOCM input is bypassed to GND with a combination of  $2.2\mu F$  (X7R) and  $0.1\mu F$  (NPO) capacitors.

The MAX44205 is connected in a unity-gain configuration. The input resistors and feedback resistors are all  $1k\Omega$  0.1% resistors. The feedback resistors are bypassed by 4.7nF (C0G, 100V) capacitors.

The ADC input filter uses a pair of  $10\Omega$  0.1% resistors and a 2.2nF (COG) capacitor. This input filter assists the MAX44205's settling response with the MAX11905's fast acquisition window.

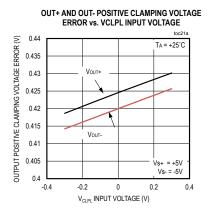

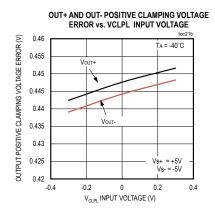

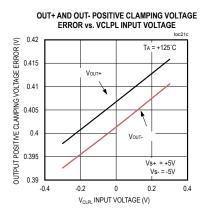

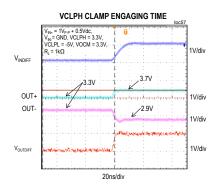

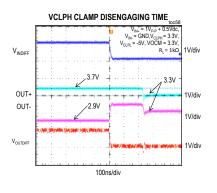

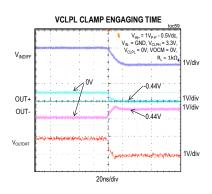

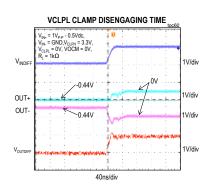

#### **Output Clamps Performance while Driving ADC**

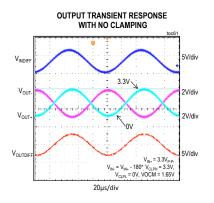

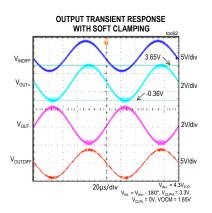

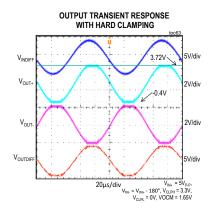

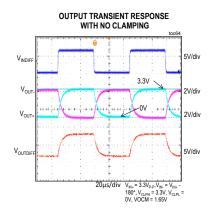

While driving ADC as shown in the Typical Operating Circuit, it is important that the driver output swing into ADC is contained within ADC supplies. The MAX44205 is operated over ±5V split supplies or +5V supply and ADC operating at slightly smaller voltage around 3.3V or 1.8V. The MAX44205 has built-in output voltage clamp feature that limits the output swing of the driver to within VCLPH + 0.34V to VCLPL - 0.42V when ADC rails are connected to Output clamp supply pins (VCLPH and VCLPL) of MAX44205. Typical Operating Characteristic graphs from TOC 61 thru TOC66 show the performance of this clamping feature when output swing of the MAX44205 is a) driven to clamp voltages, b) driven slightly above the clamps and c) driven well beyond the clamp voltages/ ADC supply voltage. Both sinusoidal and square transient response is shown.

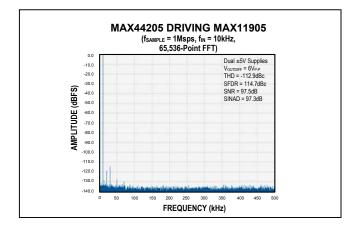

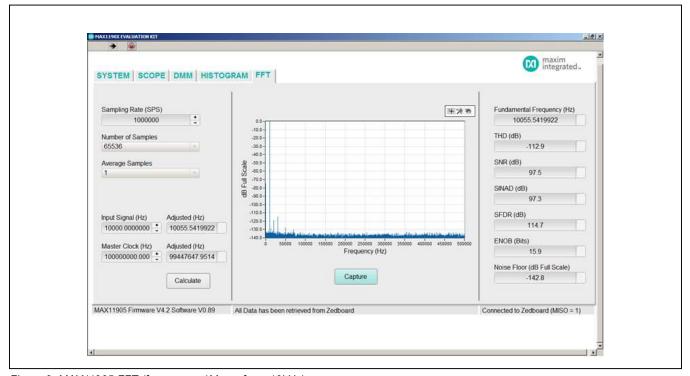

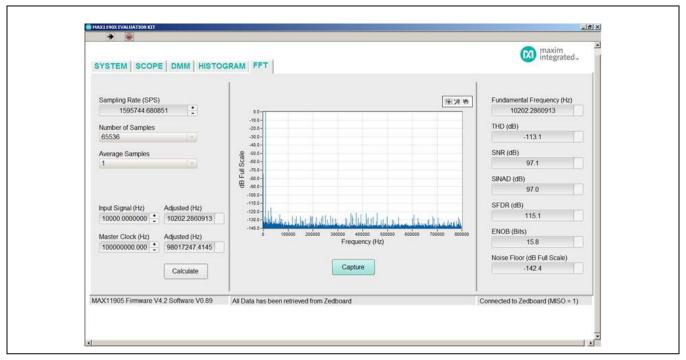

The <u>Typical Application Circuit</u> was used to test the AC performance in <u>Figures 9</u> and <u>10</u>. Data were taken with the input frequencies at 10kHz on the MAX11905 Evaluation Kit. Figures 9 to 13 detail the results of the MAX11905 Evaluation Kit (MAX11905DIFEVKIT#) GUI.

The sample rate for  $\underline{\text{Figure 9}}$  is 1Msps and the sample rate for  $\underline{\text{Figure 10}}$  is 1.6Msps, the MAX11905's maximum

sample rate. As measured at the MAX11905 output, the signal-to-noise ratio is > 97dB for both sample rates, with total harmonic distortion > 112.9dB.

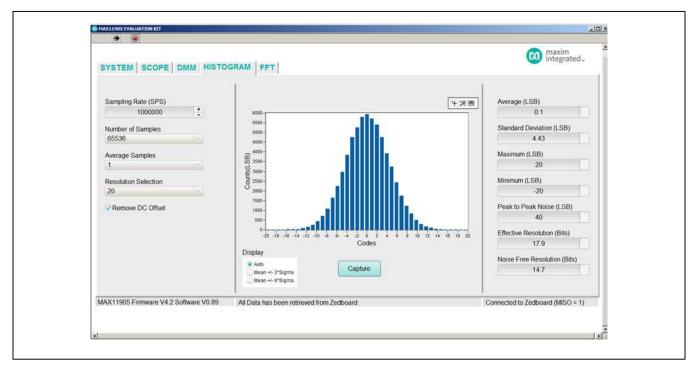

<u>Figures 11</u> to <u>13</u> detail the DC performance of the MAX44205 and MAX11905. These three figures detail the results of shorting the inputs together to GND at the  $V_{SIG}$  sources and measuring the noise histogram at the output of the ADC. All data was measured at 1Msps, with 65,536 samples taken. <u>Figure 11</u> shows the results at a 20-bit code level with no averaging. Effective number of bits (ENOB) is 17.9 bits.

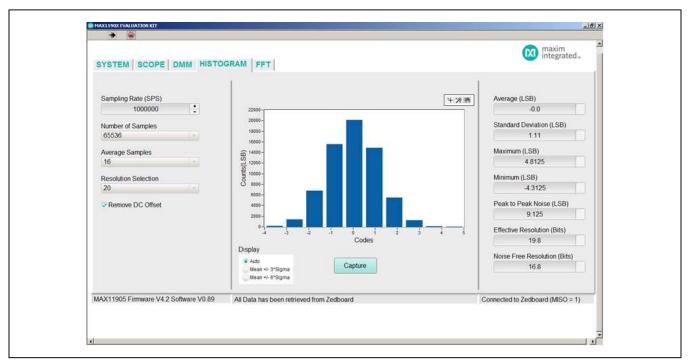

One technique to improve a system's ENOB is to average multiple samples. The tradeoff is a reduced effective sample rate. The theoretical expected results of averaging are a 0.5 improvement in ENOB for every average factor of 2. Therefore, averaging by 16x should improve ENOB by 2 bits. Figure 12 details this example, and the ENOB is improved nearly 2 bits, from 17.9 bits to 19.8 bits. This shows that the noise from the ADC and the op amp are not limiting the ENOB.

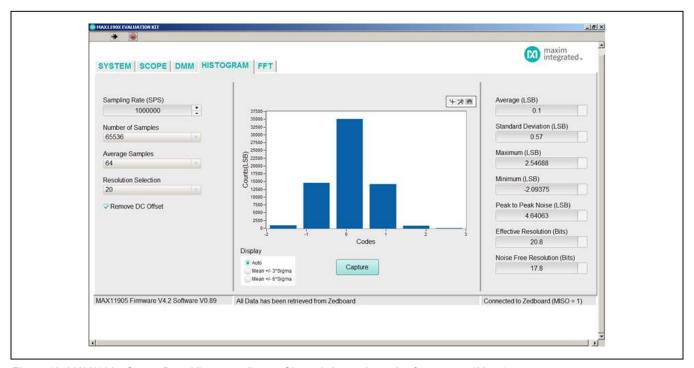

<u>Figure 13</u> shows the results of averaging by 64x, which will limit the effective sample rate to 15.6ksps (1Msps/64). ENOB is 20.8 bits in this mode, making the MAX11905 a lower power alternative to high-speed 24-bit delta sigma ADCs.

Figure 9. MAX11905 FFT ( $f_{SAMPLE} = 1Msps, f_{IN} = 10kHz$ )

Figure 10. MAX11905 FFT ( $f_{SAMPLE} = 1.6 Msps, f_{IN} = 10 kHz$ )

Figure 11. MAX11905 Output Data Histogram (Inputs Shorted, Averaging = 1, f<sub>SAMPLE</sub> = 1Msps)

Figure 12. MAX11905 Output Data Histogram (Inputs Shorted, Averaging = 16,  $f_{SAMPLE}$  = 1Msps)

Figure 13. MAX11905 Output Data Histogram (Inputs Shorted, Averaging = 64, f<sub>SAMPLE</sub> = 1Msps)

Figure 14. MAX44205 Used to Drive a Single-Ended Input into a Differential, 20-Bit SAR ADC

### **Typical Application Circuit**

### **Ordering Information**

| PART         | TEMP RANGE      | PIN-<br>PACKAGE | TOP<br>MARK |

|--------------|-----------------|-----------------|-------------|

| MAX44205ATC+ | -40°C to +125°C | 12 TQFN-EP*     | +ADA        |

| MAX44205AUB+ | -40°C to +125°C | 10 μMAX         | +AABW       |

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package.

### **Chip Information**

PROCESS: BICMOS

### **Package Information**

For the latest package outline information and land patterns (footprints), go to <a href="www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE<br>TYPE | PACKAGE<br>CODE | OUTLINE<br>NO. | LAND<br>PATTERN NO. |

|-----------------|-----------------|----------------|---------------------|

| 10 μMAX         | U10E-3          | 21-0109        | 90-0148             |

| 12 TQFN-EP      | T1233-4         | 21-0136        | 90-0017             |

<sup>\*</sup>EP = Exposed pad.

#### MAX44205

# 180MHz, Low-Noise, Low-Distortion, Fully Differential Op Amp/SAR ADC Driver

### **Revision History**

| REVISION<br>NUMBER | REVISION DATE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                | PAGES<br>CHANGED           |

|--------------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| 0                  | 6/14          | Initial release                                                                                                                                                                                                                                                                                                                                                            | _                          |

| 1                  | 12/14         | Updated the Benefits and Features, Typical Application Circuit, Electrical Characteristics, Typical Operating Characteristics, Pin Description, Functional Diagram, Detailed Description, SHDN Operation, Applications Information, and Ordering Information sections. Added the Output Clamps Performance While Driving ADCs section. Updated Figures 2, 5, 6, 7, and 14. | 1–17, 19, 21–26,<br>29, 30 |

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim Integrated's website at www.maximintegrated.com.

Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.