# CSI-2/DSI D-PHY Tx IP Core - Lattice Radiant Software

# **User Guide**

#### **Disclaimers**

Lattice makes no warranty, representation, or guarantee regarding the accuracy of information contained in this document or the suitability of its products for any particular purpose. All information herein is provided AS IS and with all faults, and all risk associated with such information is entirely with Buyer. Buyer shall not rely on any data and performance specifications or parameters provided herein. Products sold by Lattice have been subject to limited testing and it is the Buyer's responsibility to independently determine the suitability of any products and to test and verify the same. No Lattice products should be used in conjunction with mission- or safety-critical or any other application in which the failure of Lattice's product could create a situation where personal injury, death, severe property or environmental damage may occur. The information provided in this document is proprietary to Lattice Semiconductor, and Lattice reserves the right to make any changes to the information in this document or to any products at any time without notice.

# **Contents**

| Acronyms in This Document                                                           | 5  |

|-------------------------------------------------------------------------------------|----|

| 1. Introduction                                                                     | 6  |

| 1.1. Quick Facts                                                                    | 6  |

| 1.2. Features                                                                       | 6  |

| 1.2.1. Hard MIPI D-PHY Tx IP Core Features                                          | 7  |

| 1.2.2. Soft MIPI D-PHY Tx IP Core Features                                          | 7  |

| 1.3. Conventions                                                                    | 7  |

| 1.3.1. Nomenclature                                                                 | 7  |

| 1.3.2. Signal Names                                                                 | 7  |

| 2. Functional Description                                                           | 8  |

| 2.1. Module Descriptions                                                            | 11 |

| 2.1.1. Wrapper Module                                                               | 11 |

| 2.1.2. Packet Formatter Module                                                      | 13 |

| 2.1.3. Global Operation Module                                                      | 13 |

| 2.1.4. LMMI Device Slave                                                            | 15 |

| 2.2. Signal Description                                                             | 16 |

| 2.3. Attribute Summary                                                              | 19 |

| 2.4. Internal Registers                                                             |    |

| 2.4.1. Hard Configured D-PHY Tx IP Configuration Registers (MIPI Programmable Bits) | 22 |

| 2.4.2. D-PHY Tx IP Configuration Registers for Timing Parameters                    | 26 |

| 2.4.3. D-PHY Tx IP Packet Formatter Registers                                       |    |

| 3. Timing Diagrams                                                                  |    |

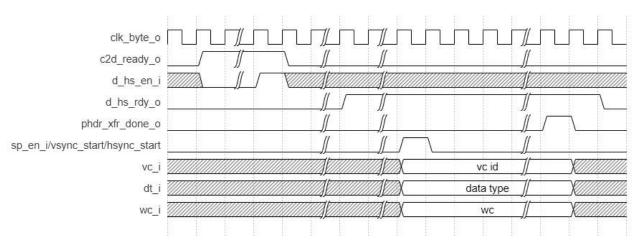

| 3.1. Short Packet Transmission in CSI-2/DSI Interfaces                              |    |

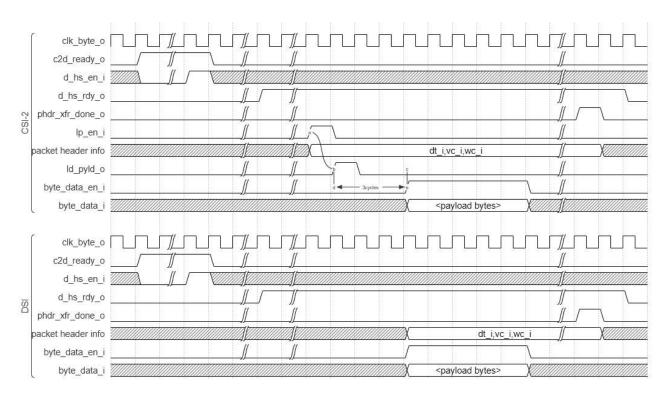

| 3.2. Long Packet Transmission in CSI-2/DSI Interface                                |    |

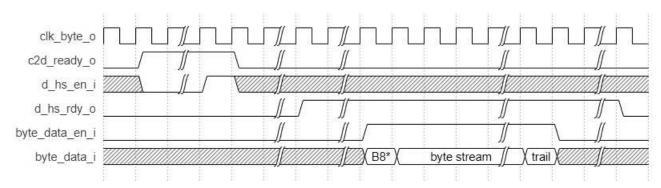

| 3.3. Long Packet Transmission in CSI-2/DSI Interface without Packet Formatter       |    |

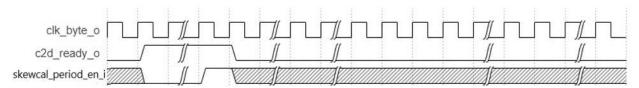

| 3.4. Enable Periodic Skew Calibration                                               | 30 |

| 3.5. AXI4-Stream Device Slave                                                       | 30 |

| 3.6. Byte Data Arrangement                                                          | 31 |

| 4. Core Generation, Simulation, and Validation                                      | 32 |

| 4.1. Generation and Synthesis                                                       | 32 |

| 4.2. Functional Simulation                                                          | 34 |

| 4.3. Core Validation                                                                | 35 |

| 5. Licensing and Evaluation                                                         |    |

| 5.1. Licensing the IP                                                               | 36 |

| 5.2. Hardware Evaluation                                                            | 36 |

| 6. Ordering Part Number                                                             | 37 |

| Appendix A. Resource Utilization                                                    |    |

| Appendix B. Limitations                                                             |    |

| References                                                                          | 40 |

| Technical Support Assistance                                                        | 41 |

| Revision History                                                                    | 42 |

# **Figures**

| Figure 1.1 D-PHY Tx IP                                                                             | 6  |

|----------------------------------------------------------------------------------------------------|----|

| Figure 2.1. D-PHY Tx IP Block Diagram with Both AXI4-Stream and LMMI Enabled                       | 8  |

| Figure 2.2. D-PHY Tx IP Block Diagram with AXI4-Stream Enabled and LMMI Disabled                   | 9  |

| Figure 2.3. D-PHY Tx IP Block Diagram with AXI4-Stream Disabled and LMMI Enabled                   |    |

| Figure 2.4. D-PHY Tx IP Block Diagram with Both AXI4-Stream and LMMI Disabled                      | 11 |

| Figure 2.5. Internal PLL Block Diagram                                                             |    |

| Figure 2.6. MIPI D-PHY Tx LP to HS Transition Flow Diagram on Data Lanes                           | 13 |

| Figure 2.7. High-Speed Entry Sequence and Payload Data Transmission Cycle on Data Lanes            | 14 |

| Figure 2.8. High-Speed Data Transmission in Skew Calibration                                       |    |

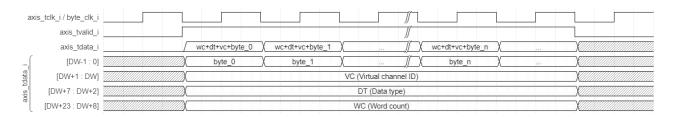

| Figure 3.1. D-PHY Tx Input Bus for Short Packet Transmission in CSI-2/DSI Interfaces               | 28 |

| Figure 3.2. D-PHY Tx Input Bus for Long Packet Transmission in CSI-2/DSI Interface                 |    |

| Figure 3.3. D-PHY Tx Input Bus for LP Transmission in CSI-2/DSI Interface without Packet Formatter |    |

| Figure 3.4. D-PHY Tx Input Bus to Enable Periodic Skew Calibration                                 | 30 |

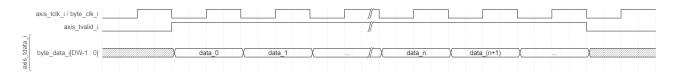

| Figure 3.5. AXI4-Stream Enabled and LMMI Disabled Data Format and Packet Formatter Enabled         |    |

| Figure 3.6. AXI4-Stream Enabled and Packet Formatter Disabled Data Format                          |    |

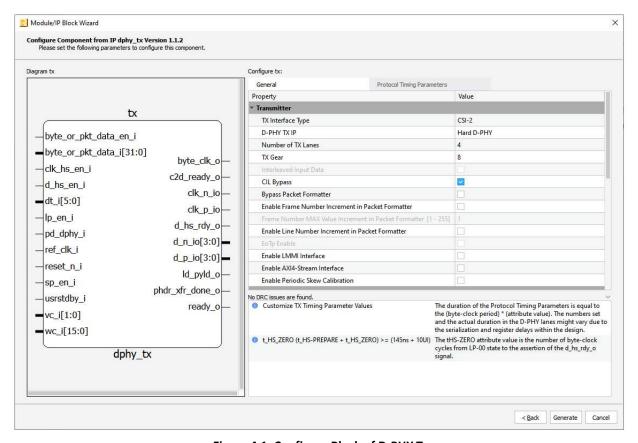

| Figure 4.1. Configure Block of D-PHY Tx                                                            | 32 |

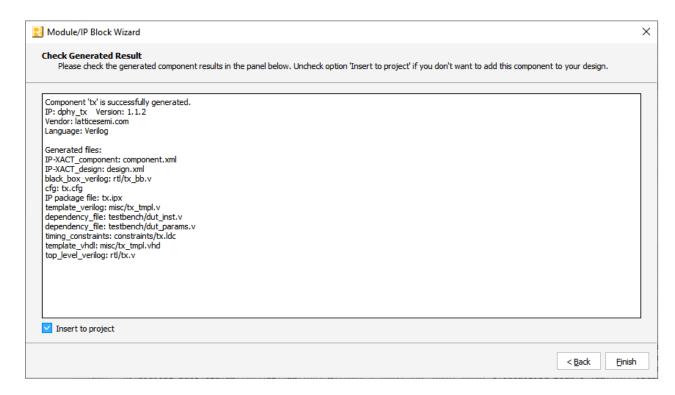

| Figure 4.2. Check Generating Result                                                                | 33 |

| Figure 4.3. Synthesizing Design                                                                    | 33 |

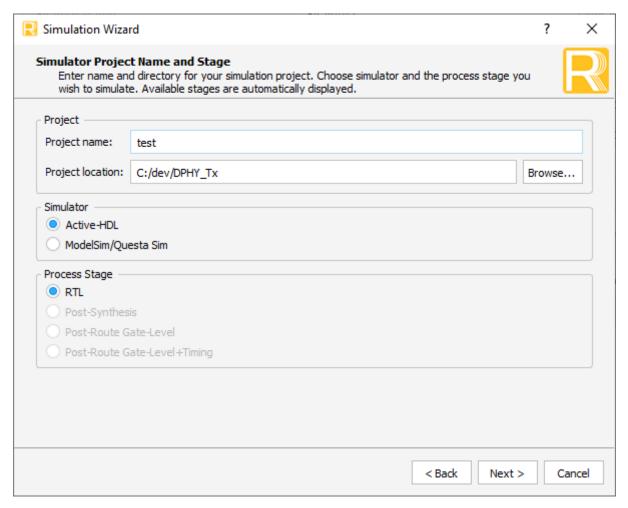

| Figure 4.4. Simulation Wizard                                                                      | 34 |

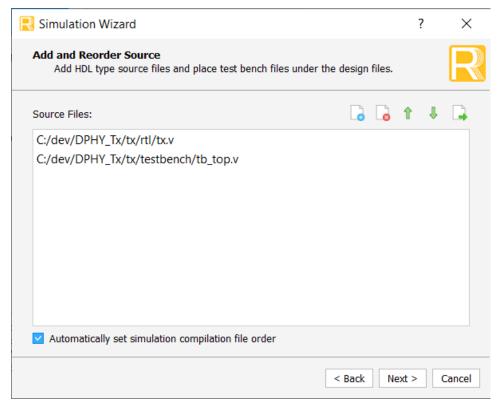

| Figure 4.5. Adding and Reordering Source.                                                          | 35 |

| Tables                                                                                             |    |

| Table 1.1. CSI-2/DSI DPHY Tx IP Core Quick Facts                                                   | 6  |

| Table 2.1. High-Speed Trail Timer for Different Data Rates                                         | 15 |

| Table 2.2. D-PHY Tx IP Core Signal Description                                                     | 16 |

| Table 2.3. Attributes Table                                                                        | 19 |

| Table 2.4. Hard Configured D-PHY Tx Configuration Registers (MIPI Programmable Bits)               | 22 |

| Table 2.5. CN and CO Table of Values                                                               | 24 |

| Table 2.6. CM Table of Values                                                                      | 24 |

| Table 2.7. D-PHY Tx Configuration Registers for Timing Parameters                                  | 26 |

| Table 2.8. D-PHY Tx Status Registers for Timing Parameters                                         | 27 |

| Table 3.1. Interleaved vs. Sequential Byte Data Input                                              | 31 |

| Table A.1. Device and Tool Tested                                                                  | 38 |

# **Acronyms in This Document**

A list of acronyms used in this document.

| Acronym | Definition                      |

|---------|---------------------------------|

| AXI     | Advance eXtensible Interface    |

| CSI-2   | Camera Serial Interface-2       |

| DSI     | Digital Serial Interface        |

| ЕоТР    | End of Transmission Packet      |

| FPGA    | Field-Programmable Gate Array   |

| LMMI    | Lattice Memory Mapped Interface |

| LP      | Low Power                       |

FPGA-IPUG-02080-1.3

# 1. Introduction

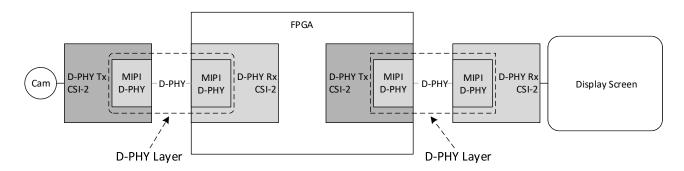

The Lattice Semiconductor CSI-2/DSI D-PHY Transmitter IP Core converts data bytes from a requestor to either DSI or CSI-2 data format for Lattice Semiconductor CrossLink™-NX and Certus™-NX family devices as indicated in the dark gray boxes in Figure 1.1.

The CSI-2/DSI D-PHY Transmitter Submodule IP is intended for use in applications that require a D-PHY transmitter in the FPGA logic.

This IP supports both high-speed and low power modes. The payload data uses the high-speed mode whereas the control and status information are sent in low power mode.

The number of D-PHY data lanes to be used for the transmission of data is configurable and supports 1, 2, 3, or 4 data lanes.

Figure 1.1 D-PHY Tx IP

# 1.1. Quick Facts

Table 1.1 presents a summary of the CSI-2/DSI DPHY Tx IP Core.

Table 1.1. CSI-2/DSI DPHY Tx IP Core Quick Facts

| IP Requirements      | Supported FPGA Families   | CrossLink-NX, Certus-NX                                                          |  |  |

|----------------------|---------------------------|----------------------------------------------------------------------------------|--|--|

|                      | Targeted Devices          | LIFCL-40, LIFCL-17, LFD2NX-40                                                    |  |  |

| Resource Utilization | Supported User Interfaces | LMMI/LINTR/AXI4-Stream Interface/ADC IP Core Native Interface                    |  |  |

|                      | Resource                  | See Table A.2. Resource Utilization1                                             |  |  |

|                      | Lattice Implementation    | IP Core v1.0.x – Lattice Radiant® Software 2.0                                   |  |  |

|                      |                           | IP Core v1.1.x – Lattice Radiant Software 2.1 or later                           |  |  |

| Design Tool Support  | Cunthosis                 | Lattice Synthesis Engine (LSE)                                                   |  |  |

| Design 1001 support  | Synthesis                 | Synopsys® Synplify Pro® for Lattice                                              |  |  |

|                      | Simulation                | For a list of supported simulators, see the Lattice Radiant Software User Guide. |  |  |

#### 1.2. Features

- Compliant with MIPI D-PHY v2.1, MIPI DSI v1.3 and MIPI CSI-2 v1.2 Specifications.

- Supports MIPI DSI and MIPI CSI-2 interfacing up to 6 Gb/s for Soft D-PHY and up to 10 Gb/s for Hard D-PHY

- Supports 1, 2, 3, or 4 MIPI D-PHY data lanes

- Supports DSI burst mode and non-burst mode with sync events only

- Supports low-power (LP) mode during vertical and horizontal blanking

- Supports periodic deskew calibration

- Option for AXI4-Stream Interface

- Hard D-PHY is supported on Crosslink-NX devices only

- Soft D-PHY is supported on Crosslink-NX and Certus-NX devices.

6

#### 1.2.1. Hard MIPI D-PHY Tx IP Core Features

- Maximum rate up to 2500 Mbps per lane

- Supported gearing: 8x, 16x

- Option to use the dedicated D-PHY TX PLL or an external clock source

- Internal PLL configurable through LMMI bus

- Option to bypass the Control and Interface Logic (CIL)

- Reference Frequency for the internal PLL from 24 MHz to 200 MHz

- Internal PLL output Frequency from 80 MHz to 1250 MHz

#### 1.2.2. Soft MIPI D-PHY Tx IP Core Features

- Maximum rate up to 1500Mbps per lane

- Supported gearing: 8x

- External clock source

## 1.3. Conventions

#### 1.3.1. Nomenclature

The nomenclature used in this document is based on Verilog HDL.

## 1.3.2. Signal Names

Signal names that end with:

- \_n are active low (asserted when value is logic 0)

- \_*i* are input signals

- \_o are output signals

# 2. Functional Description

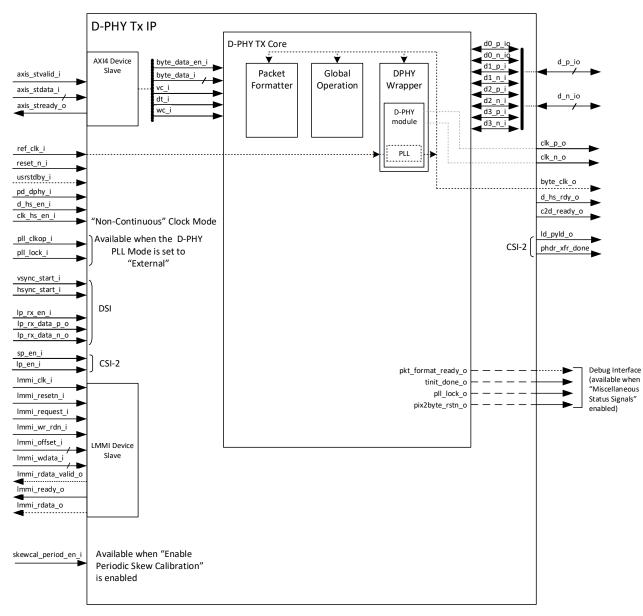

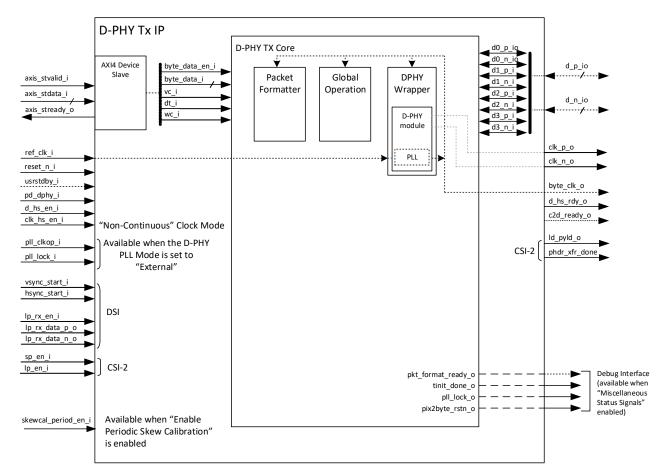

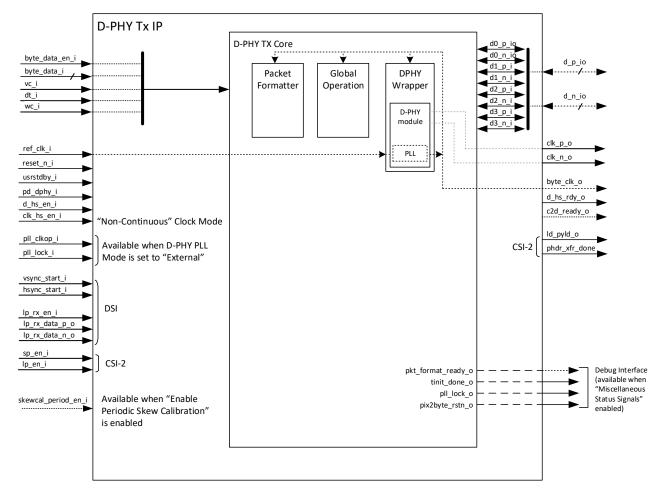

The CSI-2/DSI D-PHY Transmitter IP Core consists of the Global Operation Module, the D-PHY Tx Wrapper Module, an optional Packet Formatter Module, an optional AXI4 Stream Device Slave, and an optional LMMI Slave Module. Figure 2.1 shows the D-PHY Tx IP block with both LMMI Device and AXI4 Stream Device enabled. Figure 2.2 shows the D-PHY Tx IP block with AXI4 Stream Device enabled and LMMI Device disabled. Figure 2.3 shows the D-PHY Tx IP block with AXI4 Stream Device disabled and LMMI Device enabled. Figure 2.4 shows the D-PHY Tx IP block with both AXI4 Stream Device and LMMI Device disabled.

Figure 2.1. D-PHY Tx IP Block Diagram with Both AXI4-Stream and LMMI Enabled

Figure 2.2. D-PHY Tx IP Block Diagram with AXI4-Stream Enabled and LMMI Disabled

Figure 2.3. D-PHY Tx IP Block Diagram with AXI4-Stream Disabled and LMMI Enabled

Figure 2.4. D-PHY Tx IP Block Diagram with Both AXI4-Stream and LMMI Disabled

# 2.1. Module Descriptions

## 2.1.1. Wrapper Module

The D-PHY Tx Wrapper Module instantiates the PHY block. It may be configured to instantiate either a hardened D-PHY block or a soft logic implementation of the MIPI D-PHY.

Additional logic in the Wrapper Module is used to configure the connection between the PHY and the higher protocol layers.

## 2.1.1.1. **D-PHY Module**

The D-PHY Module provides the MIPI D-PHY physical serial data communication layer on which the protocols CSI-2 or DSI runs. This may be a hardened block or a soft logic implementation of the D-PHY using special IOs.

When the hardened block is used, a dedicated D-PHY PLL may be used to generate the byte clock and the high-speed clock for the D-PHY clock lanes. This PLL may be reconfigured by accessing the hard D-PHY registers through the LMMI bus. If the LMMI is disabled, the PLL registers take on the value corresponding to the Reference Clock Frequency and the TX Line Rate per Lane attributes set in the user interface.

#### **External PLL**

When PLL Mode is External, two signals become available for users: pll\_clkop\_i and pll\_lock\_i. The pll\_lock\_i is a D-PHY PLL lock signal that is in effect a reset signal for D-PHY. The pll\_clkop\_i is an external clock source, which is generated by the user and must meet a few requirements, depending on whether the D-PHY is Soft or Hard. In case of Soft D-PHY, this clock must have the same frequency as DPHY Clock Frequency in the user interface. In case of Hard D-PHY, this clock must be exactly twice the DPHY Clock Frequency in the user interface. When the PLL Mode is External, the frequency can be changed by changing pll\_clkop\_i frequency while resetting pll\_lock\_i.

#### **Internal PLL**

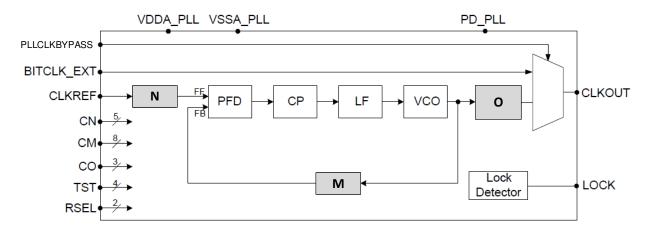

The CSI-2/DSI D-PHY Transmitter IP contains its own PLL to generate the D-PHY clock lanes and the byteclock. The block diagram of the PLL is shown in Figure 2.5.

Figure 2.5. Internal PLL Block Diagram

The internal PLL multiplies the input frequency by (M/(N\*O)), where N is the input divider, M is the feedback divider, and O is the output divider. The CLKOUT frequency is twice the D-PHY clock lane frequency.

The valid CLKREF of the D-PHY PLL, connected to the signal refclk\_i, ranges from 24 MHz up to 200 MHz. The input divider, N, has to be programmed such that the frequency FF after the input divider is within 24 MHz and 50 MHz. The VCO output, which is also the input to the O divider, must be between 1250 MHz and 2500 MHz.

When PLL Mode is Internal, the frequency can be changed by reconfiguring the LMMI control registers CM, CN, CO, and the protocol timing parameters. See Table 2.4. for details on register offsets and corresponding values.

The data rate can be computed using this equation:

$$TX \ data \ rate = \left(\frac{CLKREF}{N}\right) * \left(\frac{M}{O}\right)$$

You can update the data rate without reprogramming the FPGA by following the steps below:

- Set user standby input High. Keep it High at all time while registers CM, CN, and CO are written through LMMI write command.

- 2. Perform LMMI write command to the CM, CN, and CO register addresses with the values for the desired PLL frequency. See Table 2.5 and Table 2.6 for the conversion of the Control registers CM, CN, and CO to their respective M, N, and O values.

- 3. Adjust the protocol timing registers for the new data rate.

- 4. Set user standby input to Low.

- 5. Wait for the pll\_lock\_o to assert.

#### 2.1.2. Packet Formatter Module

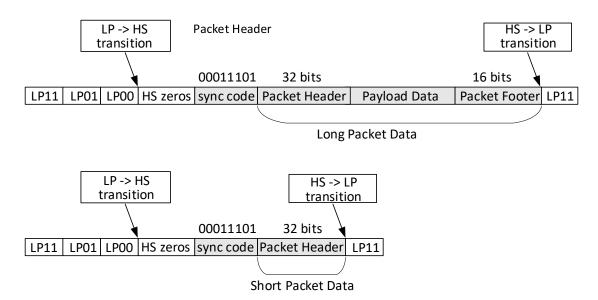

The Packet Formatter Module includes the Packet Header and Packet Footer modules.

The Packet Header module generates the 32-bit header, including the ECC, for the DSI or the CSI-2 packet based on the input information. For CSI-2 configured IP whose frame and line number information are not available, there is an internal line and frame counter logic than can be enabled through the IP user interface.

The Packet Footer module appends the CRC checksum at the end of the payload. It also generates the End-of-Transmit packet (EoTP) for DSI when it is enabled.

## 2.1.3. Global Operation Module

The Global Operation Module contains the FSM for controlling the HS and LP transitions for high-speed transmission. This also contains counters for the D-PHY protocol timing requirements. These timing parameters are also listed in Table 2.3.

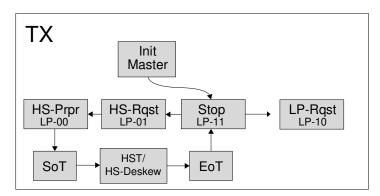

Figure 2.6 shows the LP-to-HS transition flow diagram for data lanes.

Only the sequences from the Stop State to the high-speed state and vice versa are supported; the LP-request, escape mode and turnaround path are not supported.

Figure 2.6. MIPI D-PHY Tx LP to HS Transition Flow Diagram on Data Lanes

During normal operation a Data Lane is either in Control or in High-Speed mode.

For sending payload data (the image data), the transmitter drives a particular sequence on data lanes to enter the receiver from the low power mode to high-speed mode.

As part of the initialization of D-PHY, initially all the lanes are held at LP11 state for a specified time. This LP11 state is also known as the Stop State. For sending the image data in high-speed, the transmitter drives the D-PHY lanes a particular LP sequence before it enters high-speed mode. The high-speed entry sequence (see Figure 2.7) consists of driving LP11->LP01->LP00 (LP->HS transition) on the lanes. On successful reception of this sequence, the high-speed receiver module enables its termination to receive the high-speed differential data.

After LP-to-HS transition, the transmitter sends HS Zeros (V(Dn)>V(Dp)) for a specified amount of time to make sure that the receiver is enabled properly before any payload data is transmitted.

Before the payload data of every HS burst on each lane, the transmitting D-PHY inserts a sync sequence (00011101). This sync sequence is used by the data lanes of the receiving D-PHY to establish synchronization with the high-speed payload data.

The LP11 state brings back the data lane from high-speed mode to low power mode.

After every HS burst, the data lanes go to LP11 state. A single HS burst represents the image data corresponding to one of the horizontal lines of an image and the LP11 state in-between the HS bursts represents the blanking periods.

Figure 2.7. High-Speed Entry Sequence and Payload Data Transmission Cycle on Data Lanes

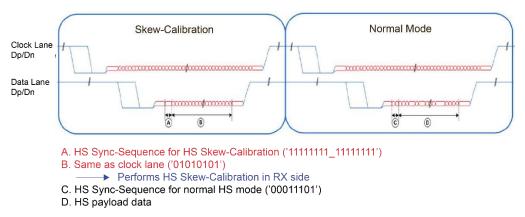

Receiver deskew is initiated by the transmitter for the DUTs supporting > 1.5 Gbps. The transmitter sends a special deskew burst, as shown in Figure 2.8. When operating above 1.5 Gbps or changing to any rate above 1.5 Gbps, an initial deskew sequence is transmitted before High-Speed Data Transmission in normal operation. When operating at or below 1.5 Gbps, the transmission of the initial deskew sequence is optional. Periodic deskew is optional irrespective of data rate.

Figure 2.8. High-Speed Data Transmission in Skew Calibration

#### 2.1.4. LMMI Device Slave

The LMMI (Lattice Memory Mapped Interface) Device Slave Module is used for configuring the control registers of the D-PHY Tx IP.

For more information on LMMI, see Lattice Memory Mapped Interface and Lattice Interrupt Interface User Guide (FPGA-UG-02039).

If the LMMI bus is not enabled, the Hard D-PHY configuration registers take on the corresponding values based on the IP configuration set in the user interface. See the Internal Registers section for the list of the configuration registers.

An example of how the T<sub>HS-TRAIL</sub> Timing Parameter changes depending on u\_PRG\_HS\_TRAIL[5:0] register is given in Table 2.1.

Table 2.1. High-Speed Trail Timer for Different Data Rates

| Data Rate | Min (ns) | Max (ns) | u_PRG_HS_TRAIL [5:0] | THS-TRAIL (ns) |

|-----------|----------|----------|----------------------|----------------|

| 2.5 Gbps  | 61.6     | 109.8    | 011000               | 76.8           |

| 1.5 Gbps  | 62.67    | 113      | 001111               | 80             |

| 1.0 Gbps  | 64       | 117      | 001100               | 96             |

| 500 Mbps  | 68       | 129      | 000110               | 96             |

| 250 Mbps  | 79       | 153      | 000100               | 128            |

| 80 Mbps   | 110      | 255      | 000010               | 200            |

The other Timing Parameters can be changed by changing corresponding registers following the same logic.

# 2.2. Signal Description

Table 2.2 shows the D-PHY Tx IP Core top-level Input and Output signals.

Table 2.2. D-PHY Tx IP Core Signal Description

| Port Name                                 | Direction | Mode/Configuration                     | Description                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------------------------------------|-----------|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LMMI                                      |           |                                        |                                                                                                                                                                                                                                                                                                                                                                                               |

| lmmi_clk_i                                | In        | _                                      | LMMI Interface clock                                                                                                                                                                                                                                                                                                                                                                          |

| lmmi_resetn_i                             | In        | _                                      | Active low signal to reset the configuration registers                                                                                                                                                                                                                                                                                                                                        |

| lmmi_wdata_i[LDW¹ – 1:0]                  | In        | _                                      | Write data                                                                                                                                                                                                                                                                                                                                                                                    |

| lmmi_wr_rdn_i                             | In        | _                                      | Write = HIGH, Read = LOW                                                                                                                                                                                                                                                                                                                                                                      |

| Immi_offset_i[LOW <sup>2</sup> – 1:0]     | In        | _                                      | Register offset, starting at offset 0                                                                                                                                                                                                                                                                                                                                                         |

| lmmi_request_i                            | In        | _                                      | Start transaction                                                                                                                                                                                                                                                                                                                                                                             |

| lmmi_ready_o                              | Out       | _                                      | Ready to start a new transaction                                                                                                                                                                                                                                                                                                                                                              |

| lmmi_rdata_o[LDW¹ – 1:0]                  | Out       | _                                      | Read data                                                                                                                                                                                                                                                                                                                                                                                     |

| lmmi_rdata_valid_o                        | Out       | _                                      | Immi_rdata[3:0] contains valid data                                                                                                                                                                                                                                                                                                                                                           |

| AXI4-Stream Slave                         | II.       |                                        |                                                                                                                                                                                                                                                                                                                                                                                               |

| axis_stvalid_i                            | In        | _                                      | Source indicates that data to be transmitted is valid                                                                                                                                                                                                                                                                                                                                         |

| axis_stdata_i[ADW³ – 1:0]                 | In        | _                                      | Payload data receiving channel (Byte Data or Packet Data with Virtual Channel and Data Type and Word Count)                                                                                                                                                                                                                                                                                   |

| axis_stready_o                            | Out       | _                                      | Indicates that AXI4-Stream is ready to accept the data                                                                                                                                                                                                                                                                                                                                        |

| D-PHY Tx                                  |           |                                        |                                                                                                                                                                                                                                                                                                                                                                                               |

| clk_p_io, clk_n_io                        | Out       | _                                      | MIPI D-PHY clock lane                                                                                                                                                                                                                                                                                                                                                                         |

| $d_p_io[BUS_WIDTH^4-1:0],$                | In/Out    | _                                      | MIPI D-PHY data lanes                                                                                                                                                                                                                                                                                                                                                                         |

| d_n_io[BUS_WIDTH <sup>4</sup> – 1:0]      |           |                                        |                                                                                                                                                                                                                                                                                                                                                                                               |

| ref_clk_i                                 | In        |                                        | If the PLL mode is internal, this is used as the reference clock for the internal PLL. The frequency must be between 24-200 MHz.  If the PLL mode is external and the hardened CIL is enabled, this clock is used as the escape mode clock. In this case, the minimum frequency should be 60 MHz.  If using the Soft PHY implementation, this clock is used to clock the gddr_sync primitive. |

| reset_n_i                                 | In        | _                                      | Synchronous active low system reset                                                                                                                                                                                                                                                                                                                                                           |

| usrstdby_i                                | In        | _                                      | Active high puts the hard D-PHY block to standby mode                                                                                                                                                                                                                                                                                                                                         |

| pd_dphy_i                                 | In        | D-PHY TX IP = "Hard D-<br>PHY"         | Active high powers down the hard D-PHY block, including the internal PLL                                                                                                                                                                                                                                                                                                                      |

| byte_or_pkt_data_i[DW <sup>5</sup> – 1:0] | In        | AXI4 Stream - disabled                 | Byte data or Packet data                                                                                                                                                                                                                                                                                                                                                                      |

| byte_or_pkt_data_en_i                     | In        | AXI4 Stream - disabled                 | indicates valid data on the byte_or_pkt_data_i bus                                                                                                                                                                                                                                                                                                                                            |

| vc_i [1:0]                                | In        | AXI4 Stream - disabled                 | 2-bit virtual channel ID of the packet                                                                                                                                                                                                                                                                                                                                                        |

|                                           |           | Bypass Packet Formatter - unchecked    | This is used only when the Packet Formatter is enabled.                                                                                                                                                                                                                                                                                                                                       |

| dt_i [5:0]                                | In        | AXI4 Stream - disabled                 | CSI-2 or DSI 6-bit data type field                                                                                                                                                                                                                                                                                                                                                            |

|                                           |           | Bypass Packet Formatter - unchecked    | This is used only when the Packet Formatter is enabled.                                                                                                                                                                                                                                                                                                                                       |

| wc_i [15:0]                               | In        | AXI4 Stream – disabled                 | 16-bit Word Count field                                                                                                                                                                                                                                                                                                                                                                       |

|                                           |           | Bypass Packet Formatter -<br>unchecked | This denotes the number of bytes in the payload of a long packet. In a short packet, this contains a 2-byte data.                                                                                                                                                                                                                                                                             |

|                                           |           |                                        | This is used only when the Packet Formatter is enabled.                                                                                                                                                                                                                                                                                                                                       |

| Port Name           | Direction | Mode/Configuration                                                                             | Description                                                                                                                                                                                                                               |

|---------------------|-----------|------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| clk_hs_en_i         | In        | DPHY Clock Mode – Non<br>continuous                                                            | Active high pulse going to the Tx Global Operation This triggers the IP to start HS entry sequence on the clock lane. Enabled for non-continuous clock mode.                                                                              |

| d_hs_en_i           | In        | _                                                                                              | Active high pulse going to the Tx Global Operation This triggers the IP to start HS entry sequence on the data lanes.                                                                                                                     |

| pll_clkop_i In      |           | DPHY PLL Mode - External                                                                       | External PLL clock source For Hard PHY implementation, the frequency of this clock should be twice that of the D-PHY clock lanes. For Soft PHY, the frequency of this clock should be the same as the frequency of the D-PHY clock lanes. |

| pll_lock_i          | In        | DPHY PLL Mode - External                                                                       | D-PHY PLL lock signal                                                                                                                                                                                                                     |

| sp_en_i             | In        | Tx Interface Type - CSI-2<br>Bypass Packet Formatter -<br>unchecked                            | Short packet enable (frame or line packet) This high active pulse triggers the IP to transmit a CSI-2 short packet.                                                                                                                       |

| lp_en_i             | In        | Tx Interface Type - CSI-2<br>Bypass Packet Formatter -<br>unchecked                            | This high active pulse is used to trigger the packet formatter to prepare the 32-bit packet header for the CSI-2 long packet. The IP expects the payload to arrive 4 cycles after the assertion of the lp_en_i.                           |

| vsync_start_i       | In        | Tx Interface Type - DSI<br>Bypass Packet Formatter -<br>unchecked                              | This high active pulse triggers the IP to transmit a vsync_start packet.                                                                                                                                                                  |

| hsync_start_i       | In        | Tx Interface Type - DSI<br>Bypass Packet Formatter -<br>unchecked                              | This high active pulse triggers the IP to transmit an hsync_start packet.                                                                                                                                                                 |

| lp_rx_en_i          | In        | Tx Interface Type - DSI                                                                        | Low Power Rx Enable signal                                                                                                                                                                                                                |

| lp_rx_data_p_o      | Out       | Tx Interface Type - DSI                                                                        | Low Power Rx Positive data                                                                                                                                                                                                                |

| lp_rx_data_n_o      | Out       | Tx Interface Type - DSI                                                                        | Low Power Rx Negative data                                                                                                                                                                                                                |

| d_hs_rdy_o          | Out       | _                                                                                              | Active high signal to indicate data lane is ready for transmission.                                                                                                                                                                       |

| byte_clk_o          | Out       | _                                                                                              | Byte clock generated by D-PHY PLL.                                                                                                                                                                                                        |

| c2d_ready_o         | Out       | _                                                                                              | Indicates that CMOS2DPHY is ready to receive data                                                                                                                                                                                         |

| phdr_xfr_done_o     | Out       | Tx Interface Type – CSI-2<br>Bypass Packet Formatter -<br>unchecked                            | Single cycle pulse to indicate that the packet information, along with the payload and CRC, are sent out to the Tx Global Operation (available when PKT_FORMAT = ON).                                                                     |

| ld_pyld_o           | Out       | Tx Interface Type – CSI-2<br>Bypass Packet Formatter -<br>unchecked                            | When high, the packet formatter is ready to receive data for packing (available when PKT_FORMAT = ON).                                                                                                                                    |

| skewcal_period_en_i | In        | Enable Periodic Skew<br>Calibration = 'checked'                                                | Initiates periodic deskew calibration when set from low to high.                                                                                                                                                                          |

| Debug Interface     |           |                                                                                                |                                                                                                                                                                                                                                           |

| tinit_done_o        | Out       | Miscellaneous – enabled                                                                        | tINIT done signal generated from IP                                                                                                                                                                                                       |

| pll_lock_o          | Out       | Miscellaneous – enabled                                                                        | D-PHY PLL lock signal                                                                                                                                                                                                                     |

| pix2byte_rstn_o     | Out       | Miscellaneous – enabled<br>Bypass Packet Formatter<br>– unchecked<br>Tx Interface Type – CSI-2 | Resets signal for pixel2byte FIFOs                                                                                                                                                                                                        |

| Port Name          | Direction | Mode/Configuration                   | Description                                                                                 |

|--------------------|-----------|--------------------------------------|---------------------------------------------------------------------------------------------|

| pkt_format_ready_o | Out       | Miscellaneous – enabled              | Indicates the state of Packet Formatter                                                     |

|                    |           | Bypass Packet Formatter  – unchecked | This is available when PKT_FORMAT = ON and AXI4 Stream = OFF and Tx Interface Type = CSI-2. |

|                    |           | Tx Interface Type – CSI-2            |                                                                                             |

|                    |           | AXI4 Stream – disabled               |                                                                                             |

#### Notes:

- 1. LDW LMMI Data Width

- if CIL\_BYPASS is unchecked, then LDW = 4

- otherwise LDW = 8

- 2. LOW LMMI Offset Width

- if CIL\_BYPASS is unchecked, then LOPW = 5

- otherwise LOW = 7

- 3. ADW AXI4 Stream Data Width

- if (Bypass Packet Formatter is unchecked) AND (LMMI is unchecked) then ADW = GEAR \* NUM\_TX\_LANE + 24

- otherwise ADW = GEAR \* NUM\_TX\_LANE

- 4. BUS\_WIDTH Number of D-PHY Lanes, 1 to 4 (available on the user interface)

- 5. DW Byte or Packet Data Width

- DW = GEAR \* NUM\_TX\_LANE

# 2.3. Attribute Summary

The D-PHY Tx IP attributes summary is shown in Table 2.3. All attributes can be configured from the General tab of the Lattice Radiant Software user interface.

**Table 2.3. Attributes Table**

| Attribute Name                                             | Values                         | Default      | Description                                                                                                                                                                                                 |

|------------------------------------------------------------|--------------------------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| General Settings                                           |                                |              |                                                                                                                                                                                                             |

| Transmitter                                                |                                |              |                                                                                                                                                                                                             |

| TX Interface Type                                          | "DSI", "CSI-2"                 | "CSI-2"      | DPHY-Tx Interface Type                                                                                                                                                                                      |

| D-PHY TX IP                                                | "Hard D-PHY", "Soft D-<br>PHY" | "Hard D-PHY" | Implementation of the PHY layer of the D-PHY Tx For Certus-NX devices, only <i>Soft D-PHY</i> is available.                                                                                                 |

| Number of TX Lanes                                         | 1, 2, 3, 4                     | 4            | Number of active D-PHY Tx data lanes The 3-lane configuration is only available when Bypass Packet Formatter is unchecked.                                                                                  |

| TX Gear                                                    | 8, 16                          | 8            | Gearing ratio between the ports in fabric and the high-speed I/O  TX Gear = 16 is available only on D-PHY TX IP = 'Hard D-PHY'.                                                                             |

| Interleaved Input<br>Data                                  | 'checked','unchecked'          | 'unchecked'  | When this option is checked, the input parallel data is already interleaved across the lanes. See Table 3.1. Available only when TX Gear = 16.                                                              |

| CIL Bypass                                                 | 'checked','unchecked'          | 'checked'    | When using <i>D-PHY TX IP = Hard D-PHY</i> , this option bypasses the built in Control Interface Logic of the Hard D-PHY.                                                                                   |

| Bypass Packet<br>Formatter                                 | 'checked','unchecked'          | 'unchecked'  | Bypasses the Packet Formatter module. The data input to the IP should already be in packet format and the bytes are interleaved across the active data lanes. Editable only if TX Interface Type = 'CSI-2'. |

| Enable Frame<br>Number Increment<br>in Packet Formatter    | 'checked','unchecked'          | 'unchecked'  | Enables the Frame Number Increment in the Packet Formatter Editable only if <i>Bypass Packet Formatter</i> is unchecked.                                                                                    |

| Frame Number MAX<br>Value Increment in<br>Packet Formatter | 1–255                          | 1            | Maximum frame number used in packet formatter This option is editable only if Enable Frame Number Increment in Packet Formatter is checked.                                                                 |

| Enable Line Number<br>Increment in Packet<br>Formatter     | 'checked','unchecked'          | 'unchecked'  | Enables the line number increment feature for the Packet Formatter This option is editable only if <i>Bypass Packet Formatter</i> is unchecked.                                                             |

| EoTp Enable                                                | 'checked','unchecked'          | 'unchecked'  | When checked, the IP appends an end-of-transmit packet at the end of a high-speed transmission.  This option is enabled only if TX Interface Type = 'DSI'.                                                  |

| Enable LMMI<br>Interface                                   | 'checked','unchecked'          | 'unchecked'  | Enables the LMMI bus                                                                                                                                                                                        |

| Enable AXI4-Stream<br>Interface                            | 'checked','unchecked'          | 'unchecked'  | Enables the AXI4-Stream bus                                                                                                                                                                                 |

| Enable Periodic Skew<br>Calibration                        | 'checked', 'unchecked'         | 'unchecked'  | When this option is checked, there is an option to perform periodic skew calibration through the port 'skewcal_period_en_i'.                                                                                |

| Attribute Name                       | Values                 | Default     | Description                                                                        |

|--------------------------------------|------------------------|-------------|------------------------------------------------------------------------------------|

| Clock                                |                        |             |                                                                                    |

| Target TX Line Rate                  | 160-2500               | 1000        | Maximum bandwidth per lane for TX Gear = 16                                        |

| (Mbps per Lane)                      | 160-1500               | 1000        | Maximum bandwidth per lane for TX Gear = 8                                         |

| Target TX Data Rate                  | 160-10000              | 4000        | Target total bandwidth of the D-PHY TX channel.                                    |

| (Mbps)                               |                        |             | Not editable. For information only.                                                |

| Target TX D-PHY                      | 80–1250                | 1250        | Target frequency of the D-PHY clock lane.                                          |

| Clock Frequency<br>(MHz)             |                        |             | Not editable. For information only.                                                |

| Target TX Byte Clock                 | 10-187.5               | 125         | Target operating frequency of the internal clock                                   |

| Frequency (MHz)                      |                        |             | byte_clock_o. The value is (line_rate_per_lane /                                   |

|                                      |                        |             | gearing)  Not editable. For information only.                                      |

| D-PHY Clock Mode                     | Continuous,            | Non-        | Determines the clock mode of the PHY layer                                         |

| D TTT Clock Wood                     | Non-continuous         | Continuous  | Continuous – if the clock lane is always in high                                   |

|                                      |                        |             | speed mode                                                                         |

|                                      |                        |             | Non-continuous – the clock lane goes to low-                                       |

|                                      |                        |             | power mode in between high speed transactions                                      |

| D-PHY PLL Mode                       | "Internal", "External" | "Internal"  | Enables or disables the internal PLL when TX Interface = Hard D-PHY                |

|                                      |                        |             | For Soft D-PHY, only external PLL sources are                                      |

|                                      |                        |             | supported.                                                                         |

| Reference Clock                      | 24–200                 | 24          | Operating frequency of the components                                              |

| Frequency (MHz)                      |                        |             | interfaced with the fabric                                                         |

| Actual TX Data Rate                  | 160-10000              | 4000        | Actual D-PHY TX data rate based on the PLL                                         |

| (Mbps)                               |                        |             | settings and Reference Clock Frequency.                                            |

| Astro-LTV Line Date                  | 460, 3500              | 1000        | Not editable. For information only.                                                |

| Actual TX Line Rate (Mbps per Lane)  | 160–2500               | 1000        | Actual data rate per lane based on the PLL settings and Reference Clock Frequency. |

| (Wibps per Lune)                     |                        |             | Not editable. For information only.                                                |

| Actual TX D-PHY                      | 80–1250                | 1250        | Actual D-PHY TX clock frequency based on the                                       |

| Clock Frequency                      |                        |             | PLL settings and Reference Clock Frequency.                                        |

| (MHz)                                |                        |             | Not editable. For information only.                                                |

| Actual TX Byte Clock                 | 10-187.5               | 125         | Actual operating frequency of the internal clock                                   |

| Frequency (MHz)                      |                        |             | byte_clock_o. The inputs to the IP should be synchronized to this clock.           |

|                                      |                        |             | Not editable. For information only.                                                |

| Deviation from                       | _                      | 0           | ((target data rate - actual data rate)/ target data                                |

| Target Data Rate                     |                        |             | rate), in percent                                                                  |

| Initialization                       |                        |             |                                                                                    |

| tINIT Counter                        | 'checked','unchecked'  | 'unchecked' | Enables the initialization counter                                                 |

| tINIT_SLAVE Value<br>(Number of Byte | 1–32768                | 1000        | Maximum counter value; editable only if <i>tINIT</i> Counter is checked            |

| Clock Cycles)                        |                        |             |                                                                                    |

| tinit Value in ns                    | int                    | 0           | Equivalent value of tINIT_SLAVE Value in ns                                        |

|                                      |                        |             | Not editable. For information only.                                                |

20

| Attribute Name                                                    | Values                     | Default     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------------------------------------------------------------|----------------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Miscellaneous Signals                                             |                            |             | '                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Enable<br>Miscellaneous Status<br>Signals                         | 'checked','unchecked'      | 'unchecked' | Enables the other miscellaneous signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Protocol Timing Param                                             | neters                     |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| TX Global Operation T                                             | iming Parameters           |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Customize TX Timing Parameter Values                              | 'checked','unchecked'      | 'unchecked' | Enables customization of the timing parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| t_LPX 50ns minimum                                                | 1–63                       | 4           | Duration of any Low-Power state                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| t_HS-PREPARE (40 ns<br>+ 4 UI) to (85 ns + 6<br>UI)               | 1–63                       | 3           | Duration of the LP-00 Line state before the HS-0 Line state                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| t_HS_ZERO<br>(t_HS_PREPARE +<br>t_HS_ZERO) >= (145<br>ns + 10 UI) | 1–63                       | 7           | Delay from the LP-00 State to the assertion of the d_hs_rdy_o signal  The actual HS-ZERO on the D-PHY data lanes still depend on these three factors:  • The delay between the d_hs_rdy_o assertion and the time the requestor sends the payload of a long packet  • The number of cycles the packet header (if enabled) can create the sync pattern and the 32-bit header. This varies with the number of lanes and gearing.  • The serializer delay. The timing from parallel data input to the serialized output data differs between soft and hard D-PHY implementation. |

| t_HS_TRAIL                                                        | 1–63                       | 8           | Duration of the flipped bit after the last payload data bit of an HS transmission burst                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| t_HS_EXIT 100 ns<br>minimum                                       | 1–63                       | 7           | Duration of the data LP-11 state following an HS transmission burst                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| t_CLK-PREPARE 38 ns<br>to 95 ns                                   | 1–63                       | 3           | Duration of the LP-00 clock state immediately before the HS-0 clock state in the LP-to-HS sequence                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| t_CLK-ZERO (t_CLK-<br>PREPARE +<br>t_CLK_ZERO) >= 300<br>ns       | 1–63                       | 17          | Duration of the clock HS-0 state prior to starting the actual toggling of the high-speed clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| t_CLK-PRE 8UI<br>minimum                                          | 1–63                       | 2           | Duration of the HS clock prior to the start of the LP-to-HS sequence of the data lanes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| T_CLK_POST (60ns + 52UI) minimum                                  | 1–63                       | 8           | Duration of the HS clock after the last associated Data Lane has transitioned to LP Mode.  The interval is defined as the period from the end of tHS-TRAIL to the beginning of tCLK-TRAIL.                                                                                                                                                                                                                                                                                                                                                                                   |

| t_CLK-TRAIL 60 ns<br>minimum                                      | 1–63                       | 19          | Duration of the HS-0 state after the last clock bit of an HS transmission burst.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| t_CLK-EXIT 100 ns<br>minimum                                      | 1–63                       | 32          | Duration of the clock LP-11 state following an HS transmission burst                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| t_SKEWCAL-INIT                                                    | 21 <sup>5</sup> UI –100 us | 1874        | Duration of initial Skew Calibration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| t_SKEWCAL-PERIOD                                                  | 21 <sup>5</sup> UI –100 us | 1874        | Duration of periodic Skew Calibration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                   |                            | •           | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

Note: The duration of the timing parameter is equal to the (byteclock period) \* (attribute value).

The timing parameters are in number of byteclock cycles. This is computed automatically to ensure the design meets the required minimum and maximum timing ranges. The numbers set in the user interface and the actual duration in the D-PHY lanes might vary due to the serialization and register delays within the design.

# 2.4. Internal Registers

For both hard and soft configurations of D-PHY Tx IP, the Configuration Registers are available when LMMI is enabled. All D-PHY Tx IP Configuration Registers are controlled through the LMMI bus. If the LMMI feature is not enabled, then the Hard D-PHY configuration registers (MIPI programmable bits) are set to their default values and the general registers become not actual and, instead, turn to top level input signals.

## 2.4.1. Hard Configured D-PHY Tx IP Configuration Registers (MIPI Programmable Bits)

(Available when DPHY TX IP = Hard D-PHY)

Table 2.4. Hard Configured D-PHY Tx Configuration Registers (MIPI Programmable Bits)

| ADDR [5:0] | Bit[3]                      | Bit[2]                                  | Bit[1]                         | Bit[0]                  |

|------------|-----------------------------|-----------------------------------------|--------------------------------|-------------------------|

| 0x00       | HSEL                        | AUTO_PD_EN                              | MASTER_SLAVE                   | DSI_CSI                 |

|            | RX High Speed Select.       | Powers down inactive lanes.             | Selects the PHY IP             | Selects the PHY IP      |

|            | [0] – Less than <=1.5 Gbps  | [0] – lanes are kept powered            | Configuration.                 | Application.            |

|            | [1] – Higher than 1.5 Gbps  | up and at LP11.                         | [0] – Slave                    | [0] – CSI2              |

|            |                             | [1] – lanes powered down.               | [1] – Master                   | [1] – DSI               |

| 0x01       | RXCDRP[1:0]                 |                                         | 2'b00*                         |                         |

|            | LP-CD threshold voltage. De | fault is 2'b01.                         |                                |                         |

|            | Min – 200 mV, Max – 450 m   | V                                       |                                |                         |

| 0x02       | EN_CIL                      | RXLPRP[2:0]                             |                                |                         |

|            | Enables or disables CIL.    | Adjust the threshold voltage a          | nd hysteresis of LP-RX, defaul | t setting 2'b001        |