# DESCRIPTION

The MP5981 is a monolithic, integrated controller and switch that contains a high-side MOSFET and other circuitries that enable it to work in standalone operation or to be controlled by a hot-swap controller. The MP5981 drives up to 50A of continuous current per device at room temperature. With air flow, the continuous current can reach 60A.

The MP5981 limits the inrush current to the load when a circuit card is inserted into a live backplane power source, thereby limiting the backplane's voltage drop. The MP5981 limits the internal MOSFET current by controlling the gate voltage through the current limit reference input and soft-start ramp.

The MP5981 offers many features to simplify system design. It provides an integrated current mirror to monitor the output current and on-die temperature sensing, eliminating the need for an external current-sense power resistor, power MOSFET, and thermal sense device.

The MP5981 detects the power FET gate, source, and drain short conditions. It can also provide feedback to the hot-swap controller via the fault reporting output (GOK). The MP5981 can be paralleled for higher current applications. All devices in parallel actively share current during soft start.

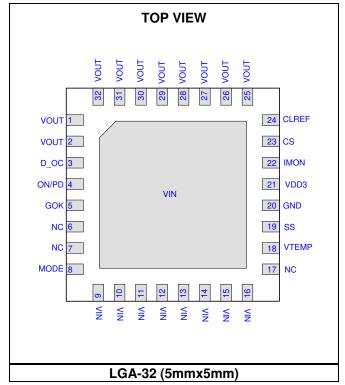

The MP5981 is available in an LGA-32 (5mmx5mm) package.

## FEATURES

- 4V to 16V Operating Input Range

- Maximum 50A Output Current

- Supports 60A of Output Current with Air Flow

- Integrated Switch with 1.1mΩ R<sub>DS(ON)</sub>

- Built-In MOSFET Driver

- 3.0V LDO Output

- Integrated Current Sensing with Sense

Output

- Separate Current-Sensing Output Used to

Program Over-Current Value

- Built-In Insertion Delay

- Adjustable Soft Start (SS)

- Output Short-Circuit Protection (SCP)

- Over-Temperature Protection (OTP)

- Built-In Fuse Health Reporting

- Fault Signal Output

- Parallel Operation for High-Current

Applications

- Integrated Intelli-Fuse Temperature Sense

- Output Voltage Power-Down Control

- Available in an LGA-32 (5mmx5mm) Package

## **APPLICATIONS**

- Hot Swap

- PC Cards

- Disk Drives

- Servers

- Networking

All MPS parts are lead-free, halogen-free, and adhere to the RoHS directive. For MPS green status, please visit the MPS website under Quality Assurance. "MPS", the MPS logo, and "Simple, Easy Solutions" are registered trademarks of Monolithic Power Systems, Inc. or its subsidiaries.

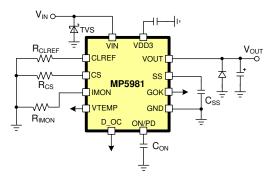

# **TYPICAL APPLICATION**

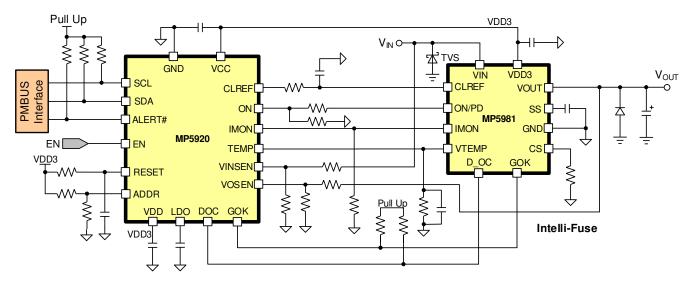

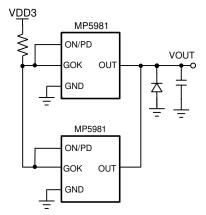

MP5981 Controlled by Hot-Swap Controller

### MP5981 Controlled by Hot-Swap Controller in Parallel Application

## **TYPICAL APPLICATION** (continued)

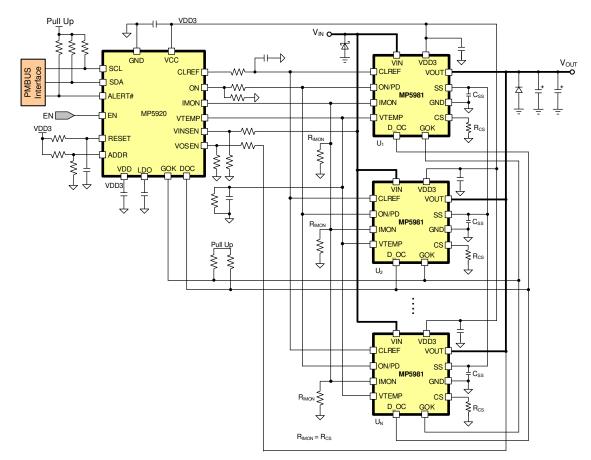

MP5981 Standalone Operation (Set RIMON ≥ Rcs)

**MP5981 Standalone Parallel Operation**

## **ORDERING INFORMATION**

| Part Number      | Package          | Top Marking |

|------------------|------------------|-------------|

| MP5981GLU*       | LGA-32 (5mmx5mm) | See Below   |

| MP5981GLU-C00E** | LGA-32 (5mmx5mm) | See Below   |

\* For Tape & Reel, add suffix -Z (e.g. MP5981GLU-Z)

\*\* For Tape & Reel, add suffix -Z (e.g. MP5981GLU-C00E-Z)

\*\*Refer to PCB layout guideline section for the recommendation of MP5981GLU and MP5981GLU-C00E

## **TOP MARKING**

## MPSYYWW

MP5981

LLLLLL

MPS: MPS prefix YY: Year code WW: Week code MP5981: Part number LLLLLLL: Lot number

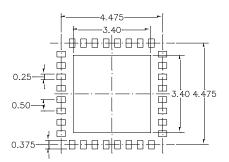

## **PACKAGE REFERENCE**

## **PIN FUNCTIONS**

| Pin #          | Name  | Description                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9-16           | VIN   | System input power supply. The MP5981 operates from a 4V to 16V input rail.                                                                                                                                                                                                                                                                                                                                                         |

| 1, 2,<br>25-32 | VOUT  | Output voltage controlled by the IC. VOUT is connected to the source of the integrated MOSFET.                                                                                                                                                                                                                                                                                                                                      |

| 3              | D_OC  | <b>Digital output of the over-current indication.</b> D_OC is an open-drain output. When the CS voltage ( $V_{CS}$ ) is higher than 85% of CLREF, the D_OC logic is pulled low.                                                                                                                                                                                                                                                     |

| 4              | ON/PD | <b>Power FET on/off control and V</b> out <b>pull-down mode control.</b> Drive ON/PD between 1.4V and 3V to turn the power FET on; drive ON/PD low to turn the power FET off. Do not float ON/PD. To pull down V <sub>OUT</sub> after a 2.1ms delay, use an integrated 500 $\Omega$ resistor to force ON/PD to about 1V. If the MP5981 is controlled by the hot-swap controller, connect a 10k $\Omega$ resistor from ON/PD to GND. |

| 5              | GOK   | <b>Intelli-Fuse fault reporting output.</b> GOK asserts low and latches after a fault occurs. The faults that can trigger GOK include over-current fault (during normal operation), short-circuit fault, over-temperature fault, and FET health fault. GOK is an open-drain output pin.                                                                                                                                             |

| 6, 7           | NC    | No connection.                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 8              | MODE  | <b>Latch or hiccup operation.</b> If the mode pin is pulled to GND, the MP5981 operates in hiccup mode and automatically retries after ~560ms. The MODE pin has an internal pull up, and if not pulled low externally will default to latch mode operation.                                                                                                                                                                         |

| 17             | NC    | No connection. Connect this pin to GND.                                                                                                                                                                                                                                                                                                                                                                                             |

| 18             | VTEMP | Junction temperature sense output.                                                                                                                                                                                                                                                                                                                                                                                                  |

| 19             | SS    | <b>Soft-start set.</b> An external capacitor connected to SS sets the soft-start time of the output voltage. The internal circuit controls the slew rate of the output voltage during turn-on.                                                                                                                                                                                                                                      |

| 20             | GND   | Signal ground.                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 21             | VDD3  | <b>Internal 3.0V LDO output.</b> VDD3 can be driven with an external 3.3V to reduce loss from VIN. Place a $1\mu$ F decoupling capacitor close to VDD3 and GND.                                                                                                                                                                                                                                                                     |

| 22             | IMON  | <b>Current monitor output.</b> The output current is proportional to the current flowing through the power device.                                                                                                                                                                                                                                                                                                                  |

| 23             | CS    | <b>Current-sense output.</b> CS requires an external resistor. The CS voltage ( $V_{CS}$ ) is compared with CLREF to determine the current limit.                                                                                                                                                                                                                                                                                   |

| 24             | CLREF | Current-limit reference voltage input.                                                                                                                                                                                                                                                                                                                                                                                              |

## **ABSOLUTE MAXIMUM RATINGS** (1)

| VIN (DC)                     | 0.3V to +20V                |

|------------------------------|-----------------------------|

| VIN (1µs)                    | +24V                        |

| VIN (25ns)                   | +29V                        |

| VOUT                         | 0.3V to +20V                |

| All other pins               | 0.3V to +4.2V               |

| Continuous power dissipation | $(T_A = 25^{\circ}C)^{(2)}$ |

|                              | 5.34W                       |

| Junction temperature         | 150°C                       |

| Lead temperature             | 260°C                       |

| Storage temperature          | 65°C to +155°C              |

|                              |                             |

## **Recommended Operating Conditions** <sup>(3)</sup>

## Thermal Resistance (4) $\theta_{JA}$ $\theta_{JC}$

LGA-32 (5mmx5mm) ......23.4 .... 12.5 . °C/W

#### Notes:

- 1) Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature  $T_{\rm J}$  (MAX), the junction-to-ambient thermal resistance  $\theta_{\rm JA}$ , and the ambient temperature  $T_{\rm A}$ . The maximum allowable continuous power dissipation at any ambient temperature is calculated by  ${\sf P}_{\rm D}$  (MAX) =  $(T_{\rm J}$  (MAX)  $T_{\rm A}$ ) /  $\theta_{\rm JA}$ . Exceeding the maximum allowable power dissipation produces an excessive die temperature, causing the regulator to go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- The device is not guaranteed to function outside of its operating conditions.

- 4) Measured on JESD51-7, 4-layer PCB.

# **ELECTRICAL CHARACTERISTICS**

VIN = 12V,  $R_{CS} = 2k\Omega$ ,  $R_{IMON} = 2k\Omega$ ,  $T_A = 25^{\circ}C$ , unless otherwise noted.

| Parameters                                      | Symbol                   | Condition                                                                                                                      | Min   | Тур   | Max   | Units  |

|-------------------------------------------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|--------|

| Supply Current                                  |                          |                                                                                                                                |       |       |       |        |

|                                                 |                          | Intelli-Fuse on, no load                                                                                                       |       | 1.8   | 2.7   | mA     |

| Quiescent current                               | lq                       | Fault latch off                                                                                                                |       | 1.5   | 2.4   | mA     |

|                                                 |                          | Intelli-Fuse off, VIN = 16V                                                                                                    |       | 1.6   | 2.5   | mA     |

| VDD3 Regulator and Under-Voltage                | Lockout (UVL             | .0)                                                                                                                            |       |       |       |        |

| VDD3 regulator output voltage                   | VDD3                     | Ivdds = 0mA                                                                                                                    | 2.855 | 3.05  | 3.245 | V      |

| VDD3 regulator load capability                  | Ivdd3                    | VOL = VDD3 - 40mV                                                                                                              | 14    |       |       | mA     |

| VDD3 under-voltage lockout threshold rising     | VDD <sub>VTH</sub>       |                                                                                                                                | 2.28  | 2.41  | 2.54  | V      |

| VDD33 under-voltage lockout threshold falling   | VDD <sub>VTL</sub>       |                                                                                                                                | 1.9   | 2.04  | 2.18  | V      |

| VDD3 under-voltage lockout threshold hysteresis | VDD <sub>HYS</sub>       |                                                                                                                                |       | 370   |       | mV     |

| VIN Under-/Over-Voltage Protection              | (UVP, OVP)               |                                                                                                                                |       |       |       |        |

| VIN under-voltage lockout threshold rising      | VINVTHR                  |                                                                                                                                | 2.74  | 2.91  | 3.08  | V      |

| VIN under-voltage lockout threshold falling     | VINVTHF                  |                                                                                                                                | 2.38  | 2.58  | 2.78  | V      |

| VIN over-voltage protection                     | VINOVP                   |                                                                                                                                | 17    | 18.5  | 20    | V      |

| Power MOSFET                                    |                          |                                                                                                                                |       |       |       |        |

|                                                 | _                        | T <sub>J</sub> = 25°C                                                                                                          |       | 1.1   | 1.375 |        |

| On resistance                                   | Rds(ON)                  | $T_{\rm J} = 125^{\circ}C^{(5)}$                                                                                               |       | 1.485 | 1.8   | mΩ     |

| Off-state leakage current                       | IOFF                     | $V_{IN} = 16V$ , power FET off                                                                                                 |       |       | 1     | μA     |

| Short-Circuit Current Limit                     |                          |                                                                                                                                |       |       |       |        |

| Short-circuit current limit <sup>(5)</sup>      | LimitSC                  |                                                                                                                                |       | 100   |       | Α      |

| Short-circuit protection response time          | tsc                      |                                                                                                                                |       | 200   |       | ns     |

| Current Limit Reference (CLREF)                 |                          |                                                                                                                                |       |       |       |        |

| Internal CLREF current                          | ICLREF                   |                                                                                                                                | 9.2   | 10    | 10.8  | μA     |

|                                                 |                          | $V_{\text{BE}}$ at $V_{\text{OUT}} < 80\%$ of $V_{\text{IN}},$ $T_{\text{J}} = 25^{\circ}\text{C}$                             | 570   | 635   | 699   | mV     |

| CLREF internal max current limit<br>clamp       | V <sub>CLREE_CLAMP</sub> | $V_{BE}atV_{OUT}<80\%$ of $V_{IN},$ $T_J$ = 125°C $^{(5)}$                                                                     | 370   | 440   | 510   | mV     |

|                                                 |                          | V <sub>OUT</sub> ≥ 80% of V <sub>IN</sub>                                                                                      | 1.44  | 1.6   | 1.76  | V      |

| CLREF over-current regulation time              | tcl_reg                  | $V_{OUT} \ge 90\%$ of $V_{IN}$ ,<br>CLREF $\ge 0.3V$                                                                           | 120   | 180   | 265   | μs     |

| Short-circuit start-up protection timer         | tsc_timer                | $V_{OUT} < 1/8 * V_{IN}$ , power<br>FET current is regulated<br>by V <sub>BE</sub> . Not valid when<br>ramping V <sub>IN</sub> |       | 2.1   | 3.2   | ms     |

| Current-Sense Output (CS)                       |                          |                                                                                                                                |       |       |       |        |

| Current-sense gain                              |                          | louт > 5A                                                                                                                      | 9.7   | 10    | 10.3  | µA/A   |

| Current-sense gain offset                       |                          | louт > 5А                                                                                                                      | -3    |       | 3     | μA     |

| Over-current D_OC high to low threshold         | Vdoc_th                  | $V_{OUT} \ge 90\%$ of $V_{IN}$ ,<br>0.3V $\le$ CLREF $\le 1.6V$                                                                | 0.8   | 0.85  | 0.9   | VCLREF |

MP5981 Rev. 1.3 5/16/2022

# ELECTRICAL CHARACTERISTICS (continued)

VIN = 12V,  $R_{CS} = 2k\Omega$ ,  $R_{IMON} = 2k\Omega$ ,  $T_A = 25^{\circ}C$ , unless otherwise noted.

| Parameters                                                      | Symbol                | Condition                                                                                                                                                                               | Min  | Тур  | Max  | Units |

|-----------------------------------------------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| VTEMP                                                           |                       |                                                                                                                                                                                         |      |      |      |       |

| VTEMP sense gain <sup>(5)</sup>                                 |                       | Sense range 0°C to 140°C                                                                                                                                                                | 8    | 8.7  | 9.4  | mV/°C |

| VTEMP sense output <sup>(5)</sup>                               |                       | $T_J = 25^{\circ}C$                                                                                                                                                                     |      | 370  |      | mV    |

| Soft Start (SS)                                                 |                       |                                                                                                                                                                                         |      |      |      |       |

| SS pull-up current                                              | lss                   | $V_{IN}$ = 12V, Iss dependent $V_{IN}$                                                                                                                                                  | 13   | 15   | 17   | μA    |

| Current Monitor Output (IMON)                                   |                       |                                                                                                                                                                                         |      |      |      |       |

| IMON sense gain                                                 |                       | louт > 5А                                                                                                                                                                               | 9.7  | 10   | 10.3 | µA/A  |

| IMON sense gain offset                                          |                       | louт > 5А                                                                                                                                                                               | -2   |      | 2    | μA    |

| ON/PD                                                           |                       |                                                                                                                                                                                         |      | •    | •    |       |

| Internal ON/PD current                                          | ON_PD                 |                                                                                                                                                                                         | 3.2  | 4.2  | 5.2  | μA    |

| FET on insertion delay time                                     | tdly_on               | VIN and VDD3 > UVLO                                                                                                                                                                     |      | 1.3  | 1.8  | ms    |

| FET on input rising threshold                                   | $V_{ON\_vth}$         | ON/PD rising                                                                                                                                                                            | 1.26 | 1.4  | 1.54 | V     |

| FT on hysteresis                                                | $V_{\text{ON\_hys}}$  |                                                                                                                                                                                         |      | 200  |      | mV    |

| FET on to PD mode threshold                                     | VPD_vth_fall          | ON/PD falling                                                                                                                                                                           | 1.08 | 1.2  | 1.32 | V     |

| PD mode to off mode threshold                                   | VOFF_vth_fall         | ON/PD falling                                                                                                                                                                           | 0.68 | 0.76 | 0.84 | V     |

| PD mode pull-down resistor                                      | Rpd                   |                                                                                                                                                                                         | 250  | 500  | 750  | Ω     |

| PD mode pull-down delay time                                    | tpd_dly               |                                                                                                                                                                                         |      | 2.1  | 3.2  | ms    |

| MODE Input                                                      |                       |                                                                                                                                                                                         |      |      |      |       |

| Hiccup Mode Voltage (5)                                         | VMODE IL              |                                                                                                                                                                                         |      | 0.7  |      | V     |

| Latch Mode Voltage (5)                                          | V <sub>MODE</sub> IH  |                                                                                                                                                                                         |      | 2.7  |      | V     |

| Thermal Shutdown                                                |                       |                                                                                                                                                                                         |      |      | 1    |       |

| Over-temperature shutdown and GOK fault flag                    | t <sub>STD</sub>      |                                                                                                                                                                                         |      | 143  |      | °C    |

| GOK Output                                                      |                       |                                                                                                                                                                                         |      |      |      |       |

| Output low voltage                                              | Vol_gok               | Sink current 1mA                                                                                                                                                                        |      |      | 0.2  | V     |

| GOK bar off-state leakage current                               | IGOK_LKG              | $V_{\text{GOK}} = 3.3 \text{V}$                                                                                                                                                         |      |      | 1    | μA    |

| D OC Output                                                     |                       |                                                                                                                                                                                         |      |      |      |       |

| Output low voltage                                              | V <sub>OL_DOC</sub>   | Sink current 1mA                                                                                                                                                                        |      |      | 0.3  | V     |

| D_OC bar off-state leakage current                              |                       | $V_{D OC} = 3.3V$                                                                                                                                                                       |      |      | 1    | μA    |

| FET Short Detection                                             |                       | 0_00                                                                                                                                                                                    |      |      |      |       |

| GOK fault flag for FET drain-to-source short                    | V <sub>OUT_DSTH</sub> | Measured at VOUT during                                                                                                                                                                 | 85%  | 90%  | 95%  | VIN   |

| GOK release high flag when drain-to-<br>source short is removed | V <sub>OUT_GOKH</sub> | start-up                                                                                                                                                                                |      | 70%  | 74%  | VIN   |

| Maximum soft-start time                                         | tss_max               | After ON_PD goes high, if $V_{OUT} < 90\%$ of $V_{IN}$ within 270ms, or if VGS remains less than 1.5V below internal charge pump voltage with 270ms, indication of fuse is not fully on | 200  | 270  | 340  | ms    |

Note:

5) Guaranteed by design.

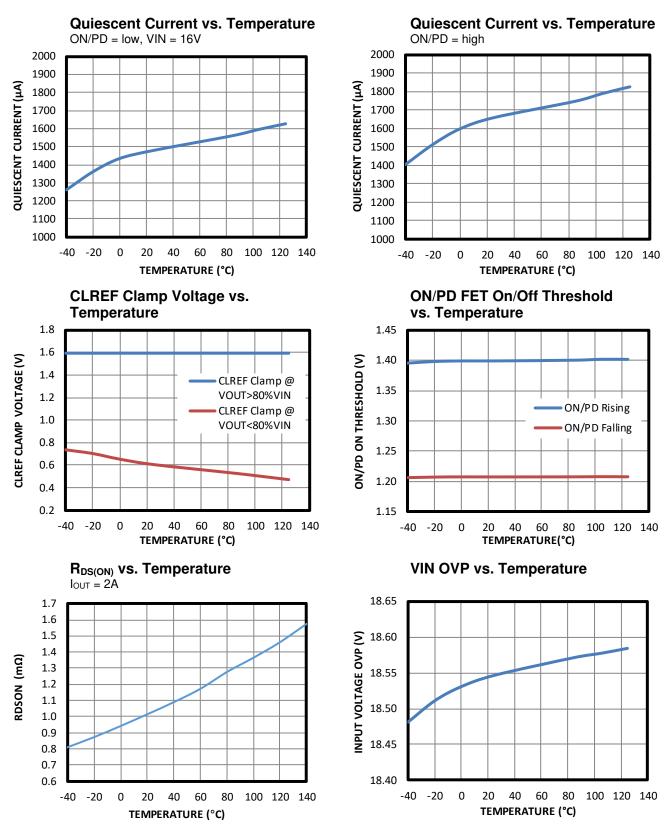

# **TYPICAL CHARACTERISTICS**

VIN = 12V,  $R_{CS} = R_{IMON} = 2k\Omega$ ,  $T_A = 25^{\circ}C$ , unless otherwise noted.

MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2022 MPS. All Rights Reserved.

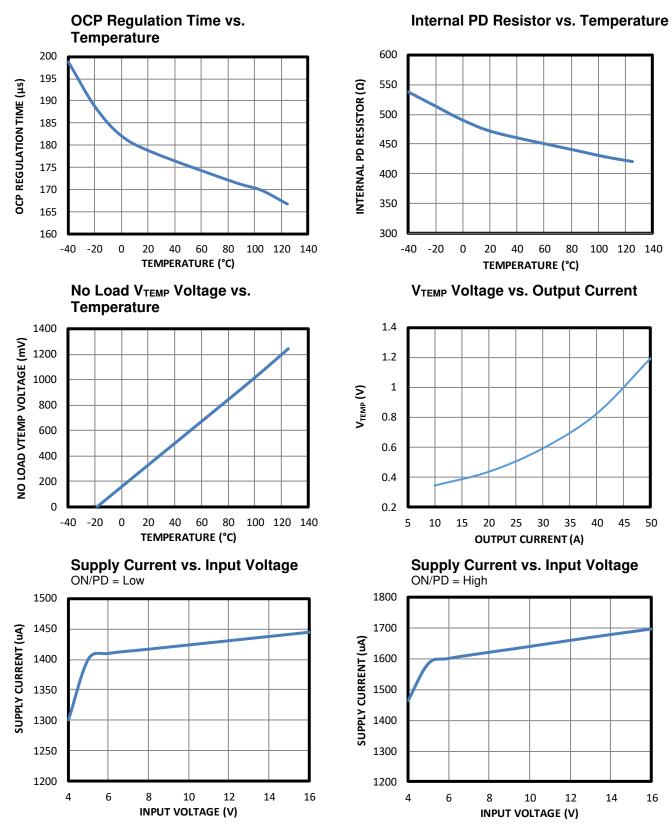

# TYPICAL CHARACTERISTICS (continued)

VIN = 12V,  $R_{CS} = R_{IMON} = 2k\Omega$ ,  $T_A = 25^{\circ}C$ , unless otherwise noted.

MP5981 Rev. 1.3 5/16/2022

MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2022 MPS. All Rights Reserved.

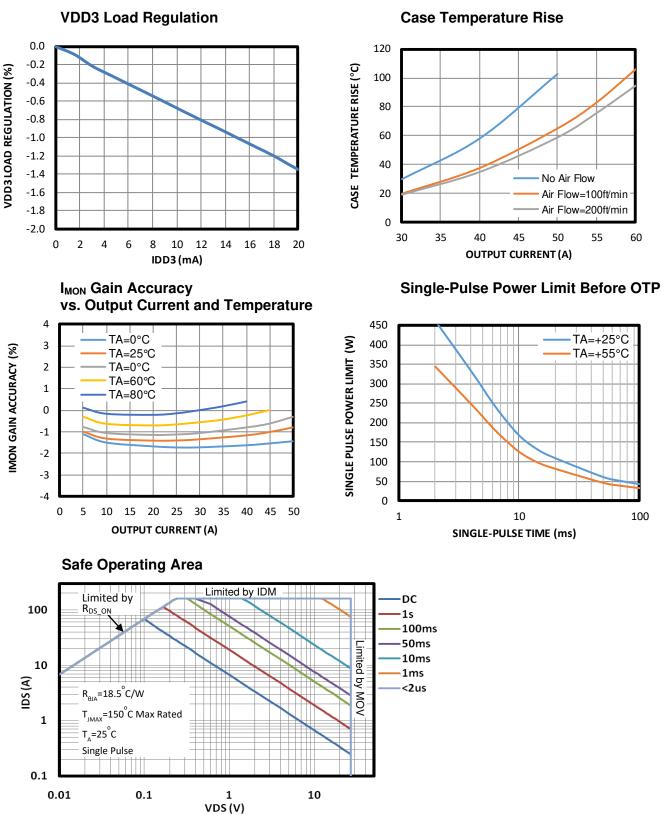

# TYPICAL CHARACTERISTICS (continued)

VIN = 12V,  $R_{CS} = R_{IMON} = 2k\Omega$ ,  $T_A = 25^{\circ}C$ , unless otherwise noted.

# **TYPICAL PERFORMANCE CHARACTERISTICS** (continued)

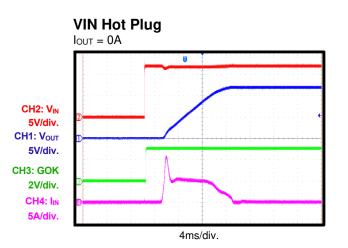

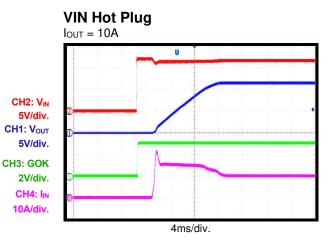

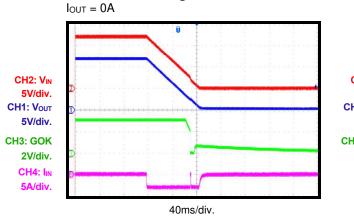

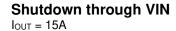

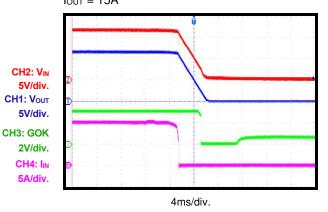

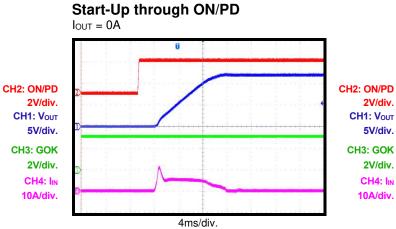

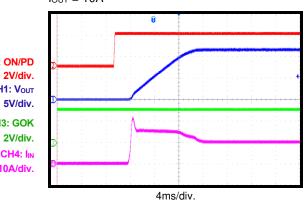

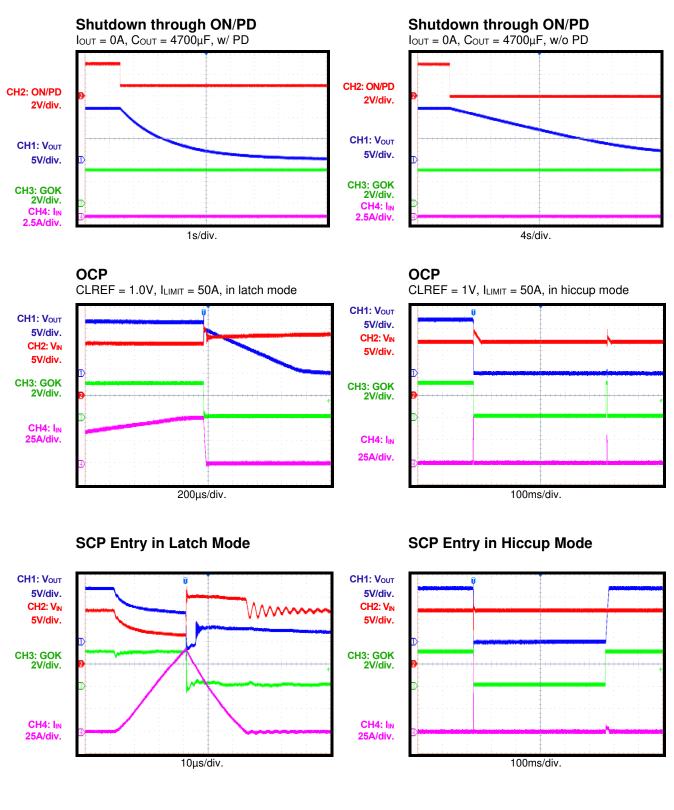

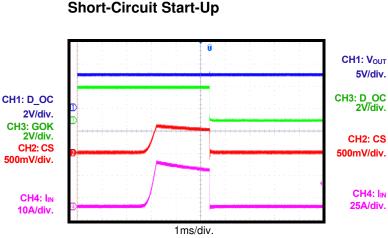

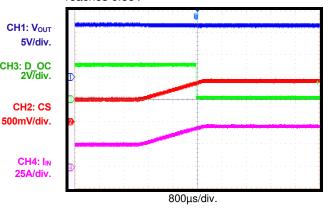

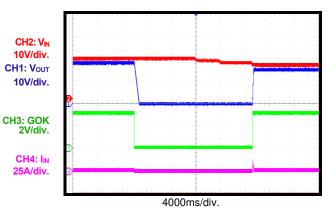

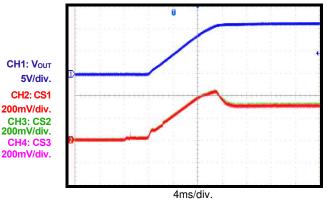

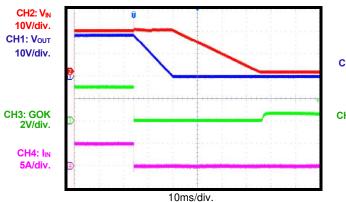

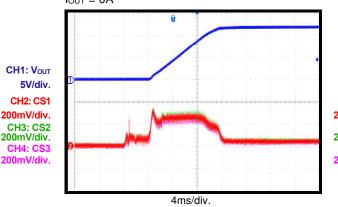

VIN = 12V,  $C_{OUT}$  = 4700µF,  $C_{SS}$  = 100nF,  $R_{CS}$  =  $R_{IMON}$  = 2k $\Omega$ ,  $R_{CLREF}$  = 100k $\Omega$ , GOK is pulled up to VDD3,  $T_A$  = 25°C, unless otherwise noted.

Shutdown through VIN

#### Start-Up through ON/PD Iout = 10A

# **TYPICAL PERFORMANCE CHARACTERISTICS** (continued)

VIN = 12V,  $C_{OUT}$  = 4700µF,  $C_{SS}$  = 100nF,  $R_{CS}$  =  $R_{IMON}$  = 2k $\Omega$ ,  $R_{CLREF}$  = 100k $\Omega$ , GOK is pulled up to VDD3,  $T_A$  = 25°C, unless otherwise noted.

# **TYPICAL PERFORMANCE CHARACTERISTICS** (continued)

VIN = 12V,  $C_{OUT}$  = 4700µF,  $C_{SS}$  = 100nF,  $R_{CS}$  =  $R_{IMON}$  = 2k $\Omega$ ,  $R_{CLREF}$  = 100k $\Omega$ , GOK is pulled up to VDD3,  $T_A$  = 25°C, unless otherwise noted.

### D\_OC Status at Normal Operation

Increase load, D\_OC is pulled down when CS reaches 0.85V

### VIN OVP in Hiccup Mode

IOUT = 1A, apply 18.5V on VIN, then reduce VIN

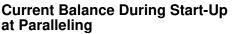

3-MP5981 parallel, RIMON = RCS per MP5981, IOUT = 37.5A

VIN OVP in Latch Mode

$I_{\text{OUT}}$  = 5A, apply 18.5V on VIN, then turn off VIN

# Current Balance During Start-Up at Paralleling

3-MP5981 parallel, RIMON = RCS per MP5981, IOUT = 0A

MP5981 Rev. 1.3 5/16/2022

MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2022 MPS. All Rights Reserved.

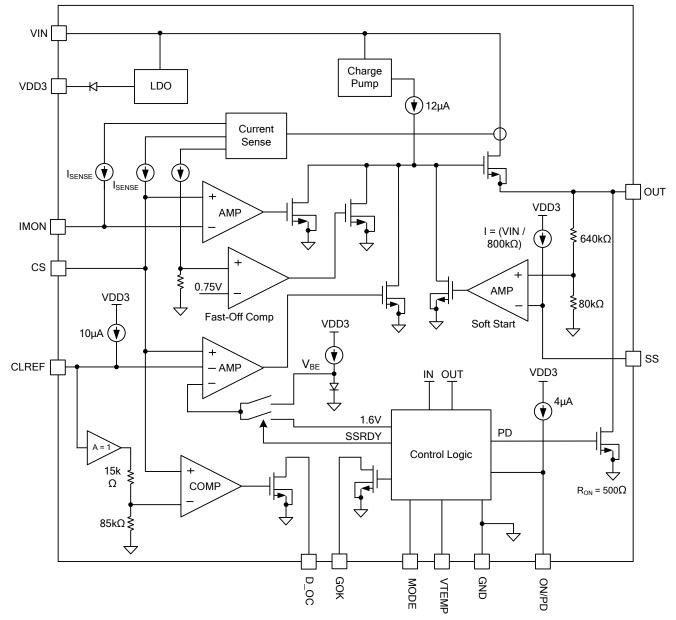

# FUNCTIONAL BLOCK DIAGRAM

Figure 1: Functional Block Diagram

# OPERATION

The MP5981 is a monolithic, high-side MOSFET with  $1m\Omega$  R<sub>DS(ON)</sub>, ideally suited for multi-fuse hot-swap applications. The MP5981 can work in standalone operation or can be controlled by a hot-swap controller for multi-fuse operation. The MP5981 drives up to 50A of continuous current per device at room temperature, and can reach 60A with air flow.

The MP5981 limits inrush current to the load when a circuit card is inserted into a live backplane power source. limitina the The backplane's voltage drop. MP5981 provides an integrated solution to monitor the output current and die temperature, eliminating the need for an external current-sense power resistor, power MOSFET, and thermal sense device. It also provides monitored current and temperature information feedback to the processor or controller. The MP5981 limits the internal MOSFET current by controlling the gate voltage through the current-limit reference input and soft-start ramp.

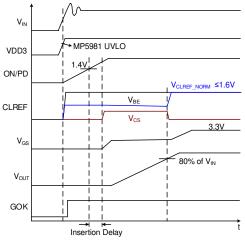

### **Current Limit at Start-Up**

The MP5981 load current is limited by the current limit reference input and the CS external resistor. The CS voltage ( $V_{SC}$ ) is compared with the current limit reference through an amplifier to regulate the power FET gate voltage. This prevents the Intelli-Fuse current from exceeding the reference-defined current limit. The current-limit reference voltage is set through CLREF and clamped low internally during soft start to allow a controlled and gradual ramp up of V<sub>OUT</sub>. Once V<sub>OUT</sub> is ramped close to V<sub>IN</sub>, the current-limit reference can be raised to the full current limit level set by the CLREF voltage. The power FET gate is fully enhanced, and the e-fuse is ready to deliver full power from the input.

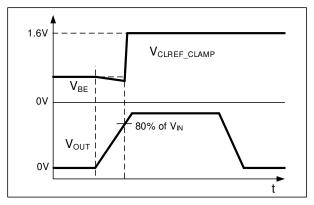

To protect the MP5981 from overheating during start-up, the current-limit reference signal has an internal maximum clamp that depends on V<sub>IN</sub> and V<sub>OUT</sub> (see Figure 2). When V<sub>OUT</sub> < 80% of V<sub>IN</sub>, the current-limit reference is clamped to V<sub>BE</sub> (about 635mV with a negative temperature coefficient). When V<sub>OUT</sub>  $\geq$  80% of V<sub>IN</sub>, the maximum current-limit reference voltage is clamped to 1.6V.

If the external CLREF voltage is lower than the

clamp voltage ( $V_{CLREF\_CLAMP}$ ), the actual currentlimit reference voltage is determined by the CLREF voltage.

Figure 2: CLREF Clamp According to VOUT

The desired start-up current limit ( $I_{LIMIT\_SS}$ ) is a function of the CS resistor ( $R_{CS}$ ), start-up current-sense gain, and CLREF voltage ( $V_{CLREF\_SS}$ ). The value of the current-sense gain at start-up is slightly higher than when the power FET is fully on.

The  $V_{OUT}$  power-up ramp time can be estimated with Equation (1):

$$t_{\text{RAMP}} = \frac{V_{\text{IN}}}{(I_{\text{LIMT}\_\text{SS}} - I_{\text{LOAD}})} \cdot C_{\text{OUT}}$$

(1)

The  $V_{OUT}$  ramp time varies with the load condition and the output capacitor ( $C_{OUT}$ ) while adopting the CLREF current limit during start-up.

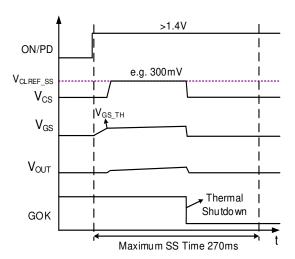

During start-up, once  $V_{CS}$  exceeds  $V_{CLREF_SS}$ , the power FET gate voltage is regulated to hold the FET current constant. If the power FET remains on while  $V_{OUT}$  remains below 90% of  $V_{IN}$  within the 270ms maximum soft-start time, the power FET shuts down when the 270ms time ends. If the value of  $V_{CLREF_SS}$  is higher, the power FET start-up instantaneous loss is huge, and triggers the thermal shutdown threshold (143°C) before the 270ms time ends, driving GOK low (see Figure 3).

During start-up, if  $V_{OUT}$  is below 1/8 \*  $V_{IN}$  and the power FET current is regulated by  $V_{BE}$  for 2.1ms, the power FET is turned off as a faulty latched condition, and GOK is pulled low.

Figure 3: Failed Start-Up within 270ms

## **Current Limit at Normal Operation**

When the output voltage has ramped up close to  $V_{IN}$ , and  $V_{OUT}$  exceeds 80% of  $V_{IN}$ , the internal current limit reference clamp voltage is released to 1.6V, and the power FET gate voltage is close to the internal charge pump voltage. Once the MP5981 detects that start-up has finished, the part operates normally.

During normal operation, once  $V_{CS}$  (which is programmed by an external resistor) exceeds the normal CLREF threshold, the internal circuit regulates the gate voltage to hold the power FET constant. To limit the current, the gate-tosource voltage needs to be regulated from 3.3V to about 1V. The typical response time is about 14µs. The output current may have a small overshoot during this time period.

When the current limit is triggered, the internal fault timer starts. If the output current falls below the current limit threshold before the end of the 180µs fault timeout period, the MP5981 resumes normal operation. Otherwise, if the current limit duration exceeds the fault timeout period, the power FET is latched off and GOK is pulled low.

The desired current limit at normal operation is a function of the CS external resistor ( $R_{CS}$ ).

The MP5981 current limit value can be higher than the normal maximum load current, allowing tolerances in the current-sense value. The current limit can be set using Equation (2):

$$I_{\text{LIMIT}} = \frac{V_{\text{CLREF}_N\text{ORM}}}{g_{\text{CS}} \cdot R_{\text{CS}}}$$

(2)

Where  $V_{CLREF_NORM}$  is the CLREF voltage in normal operation, and  $g_{CS}$  is  $10\mu A/A$ , which is the current-sense gain when the power FET is fully on. The FET works in the linear region.

## **Short-Circuit Protection (SCP)**

If the load current increases rapidly due to a short circuit, the current may exceed the current limit threshold significantly before the hot-swap control loop can respond. If the Intelli-Fuse current reaches 100A, a fast turn-off circuit in the Intelli-Fuse is activated to turn off the power FET. The total short-circuit response time is about 200ns. The GOK signal is pulled low when the power FET current reaches the 100A current limit and asserts low.

### Power-Up Sequence

For hot-swap applications, while the input voltage rises immediately, the power FET gate voltage should always be pulled low during the VIN plug-in with high dV/dt.

There are two operation modes for the MP5981: controlled by a hot-swap controller or in standalone mode.

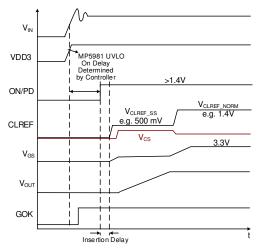

If MP5981 is controlled by a hot-swap controller, the power FET remains off until the ON/PD signal is pulled high. When the ON/PD signal goes high and the insertion delay time ends, the power FET is charged up by the internal 12µA charge pump. Once the MP5981 power FET voltage ( $V_{GS}$ ) reaches its threshold ( $V_{GSTH}$ ), the output voltage rises (see Figure 4). The maximum  $V_{CS}$  is clamped to  $V_{CLREF_SS}$  if the load current is high.

If the ON/PD signal stays high from the hotswap controller, the MP5981 can also be turned on or off through the input voltage.

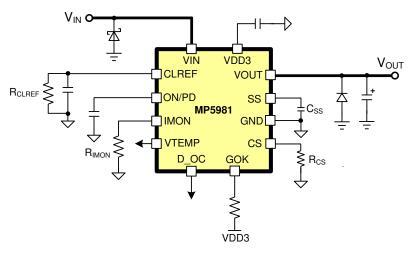

If the MP5981 works in standalone mode, an external capacitor ( $C_{ON}$ ) can be connected from ON/PD to ground for an automatic start-up (see Figure 5). The internal 4.2µA current source charges the capacitor when VDD3 exceeds the UVLO. ON/PD can also be pulled up externally to the VDD3 voltage. A 10µA CLREF current source determines the current limit level through a resistor to ground.

# Figure 5: MP5981 Schematic when Operating in Standalone Mode

Once the ON/PD voltage exceeds 1.4V and the insertion delay time ends, the power FET is charged up by the internal 12µA charge pump. The power FET turns on when  $V_{GS}$  reaches  $V_{GSTH}$ , and then the output voltage rises. The current-limit reference voltage is clamped internally to different voltage levels according to  $V_{OUT}$ . The external CLREF voltage is higher than the internal  $V_{BE}$  clamp (see Figure 6).

If the external CLREF voltage is below the clamp voltage, the actual current limit reference is determined by the CLREF voltage.

Figure 6: Start-Up when the MP5981 Operates in Standalone Mode

## Soft Start (SS)

A capacitor connected to SS determines the soft-start time. When ON/PD is pulled high and the insertion delay time ends, a constant current source proportional to the input voltage charges up the SS voltage. The output voltage rises at a similar slew rate to the SS voltage.

The SS capacitor value can be calculated with Equation (3):

$$C_{SS} = \frac{9 \cdot t_{SS}}{R_{SS}}$$

(3)

Where  $t_{SS}$  is the soft-start time (ms),  $C_{SS}$  is the soft-start capacitor (nF), and  $R_{SS}$  is 0.8M $\Omega$ .

For example, a 100nF capacitor provides a softstart time of 8.89ms. If the load capacitance is extremely large, the current required to maintain the preset soft-start time exceeds the start-up current limit. In this case, the rise time is controlled by the load capacitor and the startup current limit. Float SS to generate a fast ramp-up voltage. A 12 $\mu$ A current source pulls up the gate of the power FET. The gate charge current controls the output voltage rise time. The approximate soft-start time is then 1.5ms, which is the minimum output voltage soft-start time.

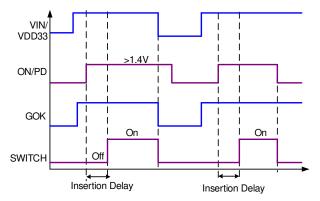

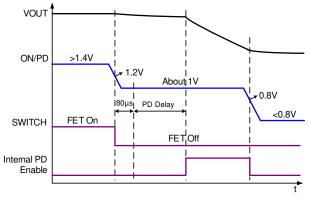

## **ON/PD Control**

ON/PD can be used for on/off control of the power FET and the pull-down mode of the output voltage. There are three types of connection on ON/PD:

- ON/PD is connect with a capacitor from ON/PD to GND;

- ON/PD is controlled by EFuse controller;

- ON/PD is controlled by external control signal. The control input may be from a pull up resistor to a non-VDD3 supply voltage, or a divider from VIN to GND. To guarantee the proper operation, make sure the ON voltage is always lower than 2.7V.

When ON/PD is used for on/off control, the power FET turns on if the ON/PD voltage exceeds 1.4V. Once the ON/PD voltage falls below 1.2V, the power FET turns off. If ON/PD is used for  $V_{OUT}$  pull-down mode, the ON/PD voltage must be clamped at about 1V for more than 80µs. The MP5981 recognizes 0.8V < ON/PD < 1.2V as a special state that requires  $V_{OUT}$  to be pulled down.

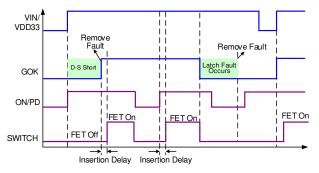

If ON/PD is used to turn on the power FET, there is a fixed 1.3ms insertion delay after VDD3 and VIN pass the UVLO threshold. All fault functionality is operative during the insertion delay, so the GOK signal is pulled high if no fault is detected and remains low if a fault is detected. The power FET remains off until the insertion delay time ends. At the end of the insertion delay, ON/PD behaves normally to turn on the power FET if no fault occurs. Figure 7 shows the detail logic when GOK is pulled up to the VDD3 voltage.

### Figure 7: Power FET On/Off Control when No Fault Occurs

Once the ON/PD voltage is pulled above 1.4V and the insertion delay ends, the internal  $12\mu$ A current source charges the power FET's gate. Once the gate voltage reaches its threshold (V<sub>GSTH</sub>), the output voltage rises. The output voltage rises following the CLREF-controlled current limit, or the SS slew rate and output capacitor.

If the MP5981 works in standalone mode, a capacitor on ON/PD can be used for automatic start-up by the internal  $4.2\mu$ A pull-up current source. Once the ON/PD voltage reaches its turn-on threshold, the power FET gate is charged by the internal  $12\mu$ A charge pump.

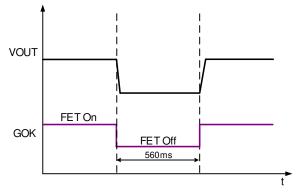

When the ON/PD voltage is set to about 1V, the MP5981 works in pull-down mode (see Figure 8). In pull-down mode, when the power FET is turned off, an integrated  $500\Omega$  pull-down resistor attached to the output discharges the output voltage after a fixed delay time (2.1ms). If the ON/PD signal is pulled low directly, pull-down mode is disabled, and the Intelli-Fuse output voltage is discharged through the external load.

Figure 8: VOUT PD Mode

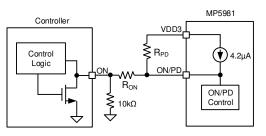

If the MP5981 is controlled by the hot-swap controller, to achieve power FET on/off control and  $V_{OUT}$  PD mode control, ON/PD can be connected (see Figure 9). Pull ON/PD up to VDD3 through a resistor divider (R<sub>PD</sub> and R<sub>ON</sub>) from the controller. If ON/PD is set to about 1V, when the hot-swap controller outputs low, the power FET turns off. R<sub>PD</sub> can be calculated with Equation (4):

$$\mathsf{R}_{\mathsf{PD}} = \frac{2 \cdot \mathsf{R}_{\mathsf{ON}}(\Omega)}{1 - 4.2 \mu \cdot \mathsf{N} \cdot \mathsf{R}_{\mathsf{ON}}(\Omega)} \tag{4}$$

Where N is the active parallel number. Choose

$R_{ON}$  to be 10k $\Omega$ . For example, if N is 2, then  $R_{PD}$  can be set to about 22k $\Omega$ .

Figure 9: ON/PD Connection for PD Mode

If ON/PD is controlled by the hot-swap controller and PD mode is not required, remove  $R_{PD}$  and set  $R_{ON}$  to  $0\Omega$ .

## **GOK Report**

GOK is an open-drain, active-low signal that reports the fault of the Intelli-Fuse. When a fault occurs, GOK is pulled low. Pull GOK up to the VDD3 voltage through a 100k $\Omega$  resistor. During VDD3 power-up, the GOK output is driven low. Before the power FET is turned on, the GOK fault condition is detected when VDD3 and VIN have passed the UVLO threshold. ON/PD is greater than 1.4V, so the GOK signal is pulled high if no fault is detected, and is pulled low if a fault is detected.

There are four fault latch protections for the MP5981:

- 1. <u>Over-current protection</u>: When  $V_{CS}$  exceeds the CLREF threshold during normal operation, the GOK signal is pulled low after a 180µs gate regulation time.

- 2. <u>Short-circuit protection</u>: When the Intelli-Fuse load current reaches 100A rapidly, GOK is pulled low immediately.

- <u>Over-temperature protection</u>: Once the junction temperature (T<sub>J</sub>) exceeds 143°C, GOK is pulled down.

- 4. <u>Power FET not fully on indication</u>: After the FET is enabled and  $V_{OUT}$  begins ramping, if  $V_{OUT} < 90\%$  of  $V_{IN}$  for the maximum soft-start time (270ms), GOK is driven low. If  $V_{OUT} < 1/8 V_{IN}$  and the FET current is regulated by  $V_{BE}$  for 2.1ms, GOK is driven low.

When a latch fault occurs, GOK is pulled low. The GOK fault latch can be released by recycling VIN. The MP5981 can detect a power FET drain-tosource short before the FET is turned on. If a short is detected, GOK is driven low. Once the short is removed, GOK is released high again.

Figure 10 shows the power FET on/off control with the GOK timing diagram when the MP5981 is controlled by the hot-swap controller.

Figure 10: Power FET On/Off Control when a Fault Occurs

## Damaged Intelli-Fuse MOSFET Detection

The MP5981 can detect a shorted pass FET during power-up. Once VDD3 exceeds the UVLO rising threshold and ON/PD exceeds the 1.4V FET on threshold, the MP5981 detects a shorted pass FET by treating an output voltage that exceeds 90% of V<sub>IN</sub> before the FET turns on as a short on the MOSFET. The GOK signal remains low when the MP5981 detects V<sub>OUT</sub> > 90% of V<sub>IN</sub> during start-up. Once the short is removed, and the MP5981 detects that V<sub>OUT</sub> < 70% of V<sub>IN</sub>, the GOK signal is released high again, and the MP5981 prepares for normal start-up.

## D\_OC Report

D\_OC is an open-drain, active-low output that reports the over-current warning when  $V_{OUT} ≥$ 90% of V<sub>IN</sub>. Once V<sub>CS</sub> exceeds 85% of the CLREF voltage, D\_OC is driven low. When V<sub>CS</sub> drops below the threshold, D\_OC is released high again. Pull D\_OC up to the VDD3 voltage through a 100kΩ resistor.

## Input and Output Transient Protection

The hot-swap system experiences positive transients on the input during a hot plug or rapid turn-off with high current due to parasitic

inductance in the input circuit. For input transient protection, a transient voltage suppressor (TVS) diode may be required on the input to limit transient voltages below the absolute maximum ratings.

The output may experience negative transients during rapid turn-off with high current due to inductance in the output circuit. If a transient makes OUT more negative, the power FET may not turn off properly.

An output voltage clamp diode is required on the output to limit negative transients. Select a Schottky diode with a low forward voltage.

## Current-Sense Output (CS)

CS provides a current proportional to the output current (the current through the power device). The current-sense gain is  $10\mu$ A/A when the power FET is fully on. There is a resistor (Rcs) connected on CS to form an external voltage. Determine a proper reference voltage with Equation (5) and Equation (6):

$$I_{CS} = I_{OUT} * 10 \mu A/A$$

(5)

$$V_{CS} = I_{CS} * R_{CS}$$

(6)

Once  $V_{CS}$  reaches the CLREF current limit threshold, the internal circuit regulates the gate voltage to hold the current in the power FET constant.

## Current Monitor Output (IMON)

The gain of the current monitor is  $10\mu$ A/A. There is a resistor (R<sub>IMON</sub>) connected from IMON to ground. The IMON voltage range of 0V to 1.6V is required to keep IMON's output current linearly proportional to the output current. Determine a proper reference voltage with Equation (7) and Equation (8):

$I_{MON} = I_{OUT} * 10 \mu A/A \tag{7}$

$$V_{\rm IMON} = I_{\rm MON} * R_{\rm IMON}$$

(8)

The MP5981 current monitor output can be used by the controller to accurately monitor the output current. Place a 100nF capacitor from IMON to GND to smooth the indicator voltage.

Connect a  $2k\Omega$  resistor (RIMON) to ground to set the gain of the output, which is about 20mV/A. For the best accuracy, use resistors within 1%.

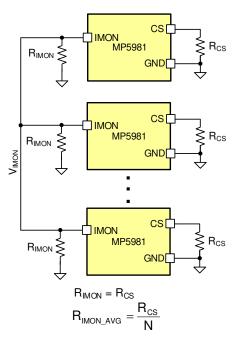

### **Current Balance for Parallel Operation**

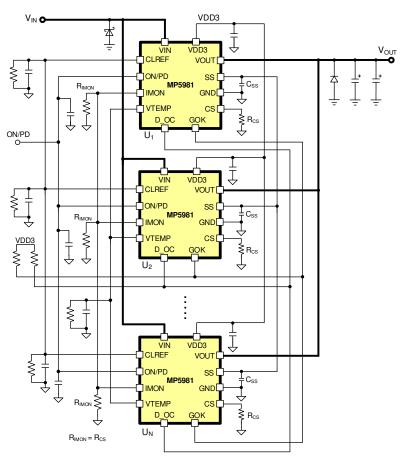

Multiple MP5981 devices can be used in parallel for higher current applications. The current balance loop in the MP5981 balances the start-up current per active channel. All IMON pins must be connected together.

The sensed current from each active MP5981 IMON is summed together and divided by the number of active channels. The resulting average load current provides a measure of the total load current. The MP5981 current balance is achieved by comparing the sensed current of CS in each MP5981 to the average current to make an appropriate adjustment to the power FET gate voltage of each Intelli-Fuse during start-up. The equivalent average IMON resistor can be calculated with  $R_{CS}$  / N, where N is the number of active MP5981 devices.

Start-up current balance is essential in achieving the thermal advantage of paralleling operation. With good current balance, the power loss is dissipated equally over multiple devices and a greater area.

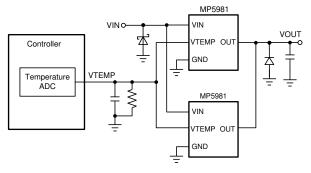

## Temperature-Sense Output (VTEMP)

VTEMP reports the junction temperature when there is no thermal gradient on the IC. VTEMP is a voltage output proportional to the junction temperature whenever VDD3 exceeds its UVLO threshold and the MP5981 is in active mode. The VTEMP output voltage ( $V_{TEMP}$ ) is 8.7mV/°C with a 152.5mV offset. N is the number of MP5981 in parallel design, 0.035 is a ratio of internal sink-source capability. Junction temperature (T<sub>J</sub>) can be calculated with Equation (9):

$$T_{J} = \frac{(V_{TEMP} - 152.5mV) \times \{1 + (0.035 \times (N-1))\}}{8.7 \text{ mV/}^{\circ}\text{C}}$$

(9)

For example, if  $V_{\text{TEMP}}$  is about 1.0225V, the junction temperature is 100°C. If  $V_{\text{TEMP}}$  is 0V, the junction temperature is about -18°C. The total temperature sense range is -18°C to +140°C. When the junction temperature is below -18°C, VTEMP remains at 0V.

In multi-fuse operation, the VTEMP pins of each Intelli-Fuse can be connected to the temperature monitor pin of the controller (see Figure 11).

Figure 11: Multi-Fuse Temperature Sense Utilization in Paralleling

### **Thermal Protection**

The Intelli-Fuse temperature is sensed by internally monitoring the junction temperature of the IC. The temperature information can be read from VTEMP.

The Intelli-Fuse has thermal protection. When the junction temperature exceeds the threshold (143°C), the power FET is turned off, and GOK is pulled low.

### **VDD3 Sub-Regulator**

The MP5981 has an internal 3.0V linear subregulator that steps down the input voltage to generate a 3.0V power supply. VDD3 can be driven with an external 3.3V to reduce subregulator loss from VIN.

### **Under-Voltage Lockout (UVLO) Protection**

The MP5981 has two under-voltage lockout (UVLO) protections: a 2.41V VDD3 UVLO and a 2.91V VIN UVLO. The MP5981 can start up only when both VDD3 and VIN exceed their respective UVLO thresholds. The MP5981 shuts down when either the VDD3 voltage is below the UVLO falling threshold (typically 2.04V) or VIN is below the VIN falling threshold (2.58V). These UVLO protections are not latch-off protections.

### Mode Pin (8)

The MP5981 has the ability to operate in latch or hiccup mode. Connecting pin 8 to ground

puts the MP5981 into hiccup mode operation. By default, the MODE pin is pulled high by internal weak pull up and operates in latch mode. When operating in hiccup mode, the MP5981 auto-restarts after any fault condition occurs with a fixed 560ms retry time (see Figure 12).

Figure 12: Auto-Retry Operation

To ensure all the devices are in parallel, enable the devices at the same time. ON/PD and GOK must be connected (see Figure 13).

### Figure 13: GOK and ON/PD Connection Parallel Devices

During retry, the GOK pin is kept low until the 560ms retry time has expired, at which time GOK is released and the connected ON/PD pin rises again, which enables all devices in parallel at the same time.

# **APPLICATION INFORMATION**

## Current Limit Resistor (R<sub>cs</sub>)

The MP5981's normal current limit value should be greater than the normal maximum load current, allowing the tolerances in the current sense value. The current limit can be calculated with Equation (10):

$$I_{\text{LIMIT}} = \frac{V_{\text{CLREF}_N\text{ORM}}}{R_{\text{CS}}} \times 10^5 (\text{A})$$

(10)

Where  $V_{CLREF_NORM}$  is the CLREF voltage when the power FET works in linear mode, and  $R_{CS}$  is the resistor from CS to ground ( $\Omega$ ).

If  $R_{CS}$  is set to  $3k\Omega$ , and  $V_{CLREF_NORM}$  is 1.2V, the desired current limit is about 40A. When  $V_{CLREF_NORM}$  is 0.3V, the desired current limit is about 10A.

Note that the maximum CS resistor ( $R_{CS}$ ) should be set no higher than 3.6k $\Omega$ .

### CLREF

CLREF sets the current-limit reference voltage, which can be determined by the hot-swap controller or a resistor to ground in standalone operation. A CLREF  $10\mu$ A current source sets the pin voltage. Place a 1nF capacitor from CLREF to ground to smooth the indicator voltage if the MP5981 is in standalone mode.

For the current limit at normal operation, the CLREF voltage can be set from 0.3V to 1.6V to program the current limit low or high while a fixed Rcs resistor is used.

## **Current Monitor Set (IMON)**

The MP5981 provides a power MOSFET current-monitoring function. Place a resistor to ground to set the gain of the output current.

In a single-MP5981 application, the IMON resistor should be set no lower than the CS resistor. When the MP5981 is used in a multifuse parallel application, achieve start-up current balance per device by connecting IMON and CS (see Figure 14).

The equivalent average IMON resistor  $(R_{IMON\_AVG})$  can be calculated with  $R_{CS}$  / N, where N is the active parallel number.

Figure 14: Multi-MP5981 IMON and CS Connection in Parallel Application

### Maximum Output Current

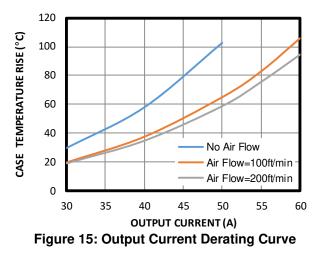

The MP5981 drives up to 50A of continuous current per device at room temperature, and can reach 60A with air flow. Figure 15 shows the case temperature rise vs. the output current at different air conditions.

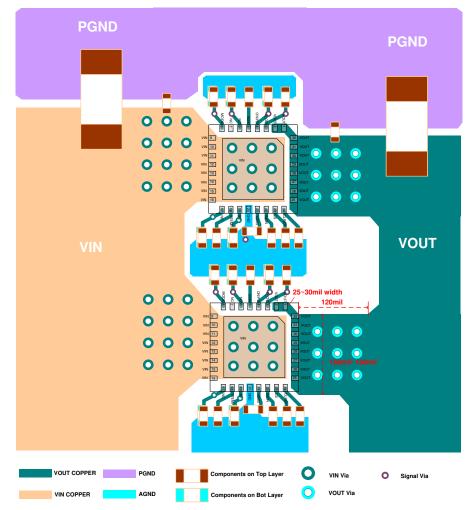

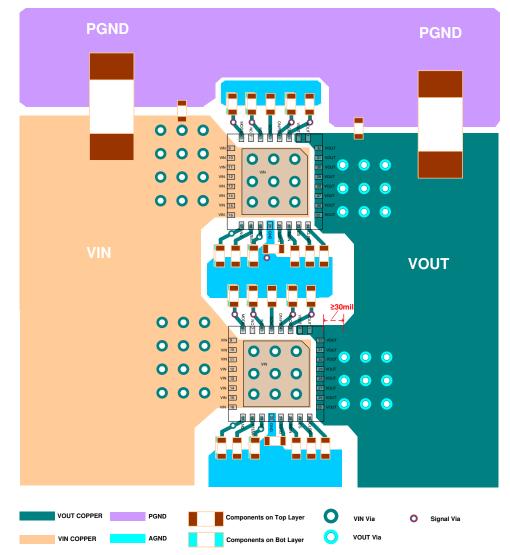

### **PCB Layout Guidelines**

Efficient PCB layout is critical for optimal IC performance. A 4-layer or more layout is strongly recommended to achieve better thermal performance. For best results, Figure 16 shows the PCB layout guideline of MP5981GLU. Figure 17 shows the PCB layout guideline of MP5981GLU-C00E.

- 1. Place the MP5981 close to the board's input connector to minimize trace inductance.

- 2. The output copper shape recommendation is different between MP5981GLU and MP5981GLU-C00E. This is to attain best IMON reporting accuracy.

### For MP5981GLU:

- Connect the VOUT pin25~32 with a wide and united copper shape, the width of the shape is 160~180mil. Do not cover the copper shape to pin1~2 directly.

- Connect VOUT pin1 and pin2 to the pin 32 with a 25~30mil trace;

- At multi-phase application, the pin25~32 VOUT shape should be keep the same width for at least 120mil before connecting to the entire system VOUT shape.

### For MP5981GLU-C00E:

Connect the Pin25~32 VOUT shape to pin1~2 directly. The VOUT shape is aligned with pin1~2 top and keep ≥30mil length from the IC edge before connecting to the system VOUT shape.

- At multi-phase application, the VOUT shape is aligned with pin1~2 top with ≥30mil length before connecting to the multi-phase system VOUT shape.

- 3. Place some vias to get better thermal performance.

- Place 9 vias or more on the bottom VIN pad;

- Place 12 vias or more close to MP5981 VIN pads at the IC edge

- Place at least 9 vias close to MP5981 VOUT pads.

- 4. Place a small capacitor ( $C_{IN}$ , 100nF) close to VIN and GND to minimize transients, which may occur on the input supply line.

Transients of several volts can occur easily when the load current is shut off.

- 5. Place a 1µF capacitor as close to VDD3 as possible.

- 6. Keep the high-current path from the board's input to load and the return path close to each other and in parallel to minimize loop inductance.

- Place an analog signal ground (AGND) plane locally in the MP5981 and connect it to the PCB power ground planes at a single point.

- 8. Connect the reference ground of all signal pins to the reference ground of the controller if the MP5981 cooperates with the hot-swap controller.

Figure 16: Example of PCB Layout for MP5981GLU (Placement & Top Layer PCB)

Figure 17: Example of PCB Layout for MP5981GLU-C00E (Placement & Top Layer PCB)

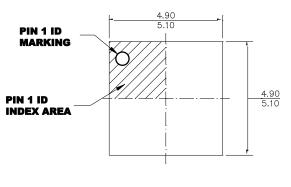

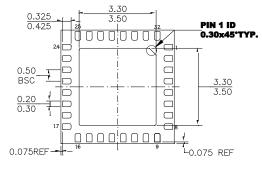

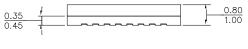

# **PACKAGE INFORMATION**

LGA-32 (5mmx5mm)

TOP VIEW

**BOTTOM VIEW**

**RECOMMENDED LAND PATTERN**

### NOTE:

1) ALL DIMENSIONS ARE IN MILLIMETERS.

2) LEAD COPLANARITY SHALL BE 0.10 MILLIMETERS MAX.

MILLIMETERS MAX.

3) JEDEC REFERENCE IS MO-303.4) DRAWING IS NOT TO SCALE.

I) DRAWING IS NOT TO SCALE

# **REVISION HISTORY**

| Revision # | <b>Revision Date</b> | Description                                                                  | Pages Updated |

|------------|----------------------|------------------------------------------------------------------------------|---------------|

| 1.0        | 7/5/2019             | Initial Release                                                              | -             |

| 1.1        | 3/19/2020            | Added the "MP5981GLU-C00E" information                                       | 4             |

|            |                      | Updated Rss to "0.8MΩ" in Figure 1                                           | 14            |

|            |                      | Updated the ON/PD Control section                                            | 17            |

|            |                      | Updated PCB Layout Guidelines section                                        | 23            |

|            | 1.2 3/23/2021        | Updated the description for the ON/PD pin in the Pin Functions section       | 5             |

| 1.2        |                      | Updated the description and circuit connection of ON/PD                      | 19            |

|            |                      | Updated Equation 9                                                           | 20            |

|            |                      | Change tape & reel suffix from "-Z" to "-Z"                                  | 4             |

| 1.3        | 5/16/2022            | Updated CLREF over-current regulation time max value from "240µs" to "265µs" | 6             |

|            |                      | Updated the calculation time of the 100nF soft-start capacitor to "8.89ms"   | 17            |

|            |                      | Minor grammar and formatting updates                                         | All           |

**Notice:** The information in this document is subject to change without notice. Please contact MPS for current specifications. Users should warrant and guarantee that third-party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.