# DESCRIPTION

The MP023 is an offline, primary-side controller that provides accurate, constant voltage and constant current regulation without the need of an optocoupler or secondary feedback circuit. It uses an integrated 700V current source to achieve quick start-up.

The MP023's variable off-time control allows its flyback converter to operate in discontinuous conduction mode (DCM). The MP023's current limit and maximum secondary duty cycle are programmable, making the output current easily set. The FB voltage sensing point is also programmable and is able to set different switching frequencies.

The internal high-voltage start-up current source and power-saving technologies limit the no-load power consumption to less than 30mW. Full protection features include VCC undervoltage lockout (UVLO), overload protection (OLP), over-temperature protection (OTP), open loop protection (OCkP), and over-voltage protection (OVP).

The MP023's variable switching frequency method provides a natural spectrum for shaping a smooth EMI signature, which is suitable for offline, low-power battery chargers and adapters.

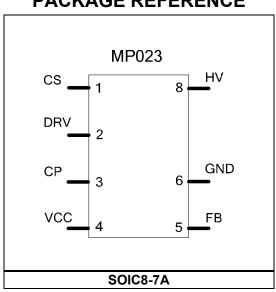

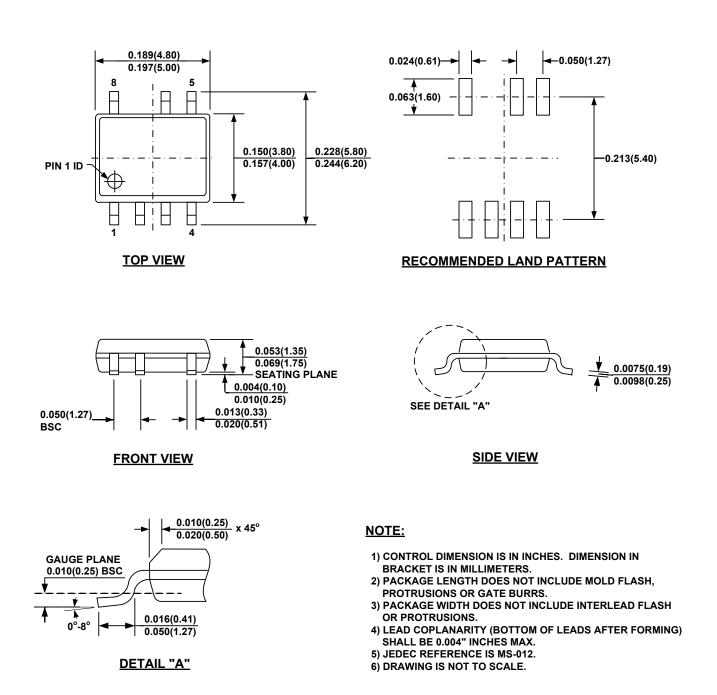

The MP023 requires a minimal number of readily available, standard, external components and is available in a SOIC8-7A package.

## **FEATURES**

- Primary-Side Control without Optocoupler or Secondary Feedback Circuit

- Precise Constant Current and Constant Voltage Control (CC/CV)

- Variable Off-Time Peak Current Control

- 700V High-Voltage Current Source

- 20mW No-Load Power Consumption

- Programmable Cable Compensation

- Programmable Current Limit and Maximum Secondary Duty Cycle

- Programmable FB Voltage Sensing Point

- Multiple Protection Features: OVP, OCkP, OLP, OTP, VCC UVLO

- Low Cost and Simple External Circuit

- Available in a SOIC8-7A Package

## **APPLICATIONS**

- Appliance Power Supplies

- Adapters for Handheld Electronics

- Standby and Auxiliary Power Supplies

All MPS parts are lead-free, halogen-free, and adhere to the RoHS directive. For MPS green status, please visit the MPS website under Quality Assurance. "MPS" and "The Future of Analog IC Technology" are registered trademarks of Monolithic Power Systems, Inc.

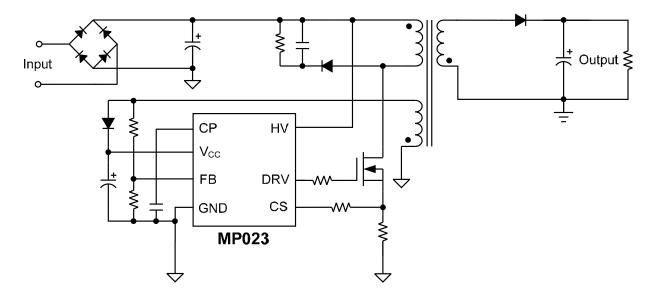

# **TYPICAL APPLICATION**

### **ORDERING INFORMATION**

| Part Number* | Package  | Top Marking |

|--------------|----------|-------------|

| MP023GS      | SOIC8-7A | See Below   |

\* For Tape & Reel, add suffix –Z (e.g. MP023GS–Z)

## **TOP MARKING**

### MP023

#### LLLLLLL

#### MPSYWW

MP023: first five digits of the part number; LLLLLLL: lot number; MPS: MPS prefix: Y: year code; WW: week code:

## PACKAGE REFERENCE

# ABSOLUTE MAXIMUM RATINGS <sup>(1)</sup>

| HV to GND                                  | 0.3V to 700V    |

|--------------------------------------------|-----------------|

| VCC to GND                                 | 0.3V to 28V     |

| DRV to GND                                 | 0.3V to 15V     |

| CP, CS to GND                              | 0.3V to 7V      |

| FB                                         |                 |

| Maximum power dissipation <sup>(2)</sup> . | 1.3W            |

| Junction temperature                       | 150°C           |

| Lead temperature                           | 260°C           |

| Storage temperature                        | -60°C to +150°C |

| ESD capability human body mo               | de2.0kV         |

| ESD capability machine mode.               | 200V            |

|                                            |                 |

## Recommended Operating Conditions <sup>(3)</sup>

| Junction temp. (T <sub>J</sub> ) |            |

|----------------------------------|------------|

| Operating VCC range              | 10V to 25V |

# Thermal Resistance $^{(4)}$ $\theta_{JA}$ $\theta_{JC}$

SOIC8-7A......96 ...... 45... °C/W

#### NOTES:

- 1) Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature T<sub>J</sub> (MAX), the junction-toambient thermal resistance  $\theta_{JA}$ , and the ambient temperature T<sub>A</sub>. The maximum allowable continuous power dissipation at any ambient temperature is calculated by P<sub>D</sub> (MAX) = (T<sub>J</sub> (MAX)-T<sub>A</sub>)/ $\theta_{JA}$ . Exceeding the maximum allowable power dissipation produces an excessive die temperature, causing the regulator to go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- The device is not guaranteed to function outside of its operating conditions.

- 4) Measured on JESD51-7, 4-layer PCB.

# **ELECTRICAL CHARACTERISTICS**

### $V_{cc}$ = 15V, $T_J$ = -40 °C~125 °C, unless otherwise noted.

| Parameter                                  | Symbol                 | Condition                                                | Min  | Тур  | Мах  | Units |

|--------------------------------------------|------------------------|----------------------------------------------------------|------|------|------|-------|

| Supply Voltage Management (                | /CC Pin)               | ·                                                        | •    |      |      |       |

| VCC ON threshold                           | V <sub>CCH</sub>       |                                                          | 18.8 | 19.4 | 20.0 | V     |

| VCC OFF threshold                          | V <sub>CCL</sub>       |                                                          | 8.2  | 8.7  | 9.2  | V     |

| Operating current                          | 1                      | f <sub>S-min</sub> , C <sub>L</sub> =1nF                 |      | 245  | 300  | μA    |

|                                            | I <sub>OP</sub>        | $fs = 40kHz, C_L=1nF$                                    |      | 1    | 1.3  | mA    |

| High Voltage Current Source (I             | HV Pin)                |                                                          |      |      |      |       |

| Break-down voltage                         | V <sub>BRDSS</sub>     |                                                          | 700  |      |      | V     |

| Supply current from HV pin                 |                        | $V_{CC}$ =18V, $V_{HV}$ =80V, $T_{J}$ =25°C              | 1.8  | 2.2  | 2.6  | mA    |

| Leakage current from HV pin                | I <sub>leak</sub>      | $V_{DS}$ =400 $V_{dc}$ , T <sub>J</sub> =25 $^{\circ}$ C |      |      | 10   | μA    |

| Driving (Drv Pin)                          |                        |                                                          |      |      |      |       |

| Driver voltage high level                  | $V_{High}$             | $C_L$ =1nF $V_{CC}$ =9.5V                                | 7.2  | 7.8  |      | V     |

| Driver voltage clamp level                 | $V_{Clamp}$            | C <sub>L</sub> =1nF, V <sub>CC</sub> =24V                | 12   | 13.4 | 15   | V     |

| Driver voltage low level                   | $V_{\text{Low}}$       | $C_L=1nF$ , $V_{CC}=24V$                                 |      |      | 50   | mV    |

| Driver voltage rise time                   | t <sub>R</sub>         | C <sub>L</sub> =1nF                                      |      | 30   |      | ns    |

| Driver voltage fall time                   | t <sub>F</sub>         | C <sub>L</sub> =1nF                                      |      | 40   |      | ns    |

| Maximum ON time                            | t <sub>ONmax</sub>     | V <sub>CS</sub> =0V                                      | 22   | 36   | 50   | us    |

| Minimum switching frequency                | f <sub>S-min</sub>     |                                                          |      | 72   | 105  | Hz    |

| Current Sense (CS Pin)                     |                        |                                                          |      |      |      |       |

| Current limit                              | V <sub>Limit-Max</sub> | f <sub>S</sub> >= f <sub>S-H</sub>                       | 464  | 480  | 496  | mV    |

|                                            | V <sub>Limit-Min</sub> | f <sub>S</sub> <= f <sub>S-L</sub>                       | 220  | 250  | 280  | mV    |

| fs to start the current fold back          | f <sub>S-Н</sub>       |                                                          | 30   | 40   | 50   | kHz   |

| fs to end the current fold back            | f <sub>S-L</sub>       |                                                          |      | 20   |      | kHz   |

| Propagation delay to Drv                   | t <sub>PD</sub>        |                                                          |      | 60   | 95   | ns    |

| Leading edge blanking                      | t <sub>LEB</sub>       |                                                          | 180  | 280  | 380  | ns    |

| Feedback input (FB Pin)                    |                        |                                                          |      |      |      |       |

|                                            |                        | $V_{FB} = 4V, V_{CP} = 2V$                               |      | 12   |      | μA    |

| FB pin input current                       | 1                      | V <sub>FB</sub> = 4V, V <sub>CP</sub> =1.5V              |      | 9    |      | μA    |

|                                            | I <sub>FB</sub>        | $V_{FB} = 4V, V_{CP} = 0.8V$                             |      | 4.6  |      | μA    |

|                                            |                        | $V_{FB} = 4V, V_{CP} = 0.2V$                             |      | 1.2  |      | μA    |

| FB reference voltage                       | $V_{FB}$               |                                                          | 3.90 | 3.96 | 4.02 | V     |

| OLP threshold at sampled FB <sup>(5)</sup> | $V_{FBolp}$            |                                                          |      | 1.38 |      | V     |

| OLP counter <sup>(1)</sup>                 |                        |                                                          |      | 768  |      |       |

| FB sampling duration                       | t <sub>FB_SD</sub>     |                                                          | 180  | 250  | 330  | ns    |

|                                            |                        | $R_{CS}$ =0 $\Omega$ , $V_{Limit}$ =0.5V                 | 2.50 | 3.45 | 4.70 |       |

| FB maximum sampling time                   |                        | $R_{CS}$ =1k $\Omega$ , $V_{Limit}$ =0.5V                | 1.70 | 2.58 | 3.50 |       |

|                                            | t <sub>FBS-Max</sub>   | $R_{CS}$ =2k $\Omega$ , $V_{Limit}$ =0.5V                | 3.60 | 5.20 | 7.00 | μs    |

|                                            |                        | $R_{CS}$ =4k $\Omega$ , $V_{Limit}$ =0.5V                | 5.00 | 7.00 | 9.20 | 1     |

# **ELECTRICAL CHARACTERISTICS**

$V_{cc}$  = 15V,  $T_J$  = -40  $^{\circ}C$ ~125  $^{\circ}C$ , unless otherwise noted.

| Parameter                                  | Symbol               | Condition                                       | Min   | Тур   | Мах    | Units |

|--------------------------------------------|----------------------|-------------------------------------------------|-------|-------|--------|-------|

|                                            | t <sub>FBS-Min</sub> | $R_{CS}$ =0 $\Omega$ , $V_{Limit}$ =0.25V       | 1.00  | 1.70  | 2.50   |       |

| FB minimum sampling time                   |                      | $R_{CS}$ =1k $\Omega$ , $V_{Limit}$ =0.25V      | 0.68  | 1.28  | 1.88   |       |

|                                            |                      | $R_{CS}$ =2k $\Omega$ , $V_{Limit}$ =0.25V      | 1.70  | 2.57  | 3.50   | μs    |

|                                            |                      | R <sub>CS</sub> =4kΩ, V <sub>Limit</sub> =0.25V | 2.50  | 3.42  | 4.70   |       |

| ZCD threshold                              | V <sub>DCM</sub>     |                                                 | 55    | 100   | 145    | mV    |

| FB open-circuit threshold                  | $V_{FBopen}$         |                                                 | -0.19 | -0.11 | -0.045 | V     |

| OVP threshold at FB                        | V <sub>FBovp</sub>   |                                                 | 5.7   | 5.96  | 6.3    | V     |

| FB OVP blanking time                       | t <sub>ovp-b</sub>   |                                                 | 0.9   | 1.2   | 1.53   | μs    |

| Output Cable Compensation (                | CP Pin)              |                                                 |       |       |        |       |

| Supply voltage on CP                       | $V_{\text{CP-Max}}$  |                                                 |       | 4     |        | V     |

| Thermal Shutdown                           |                      |                                                 |       |       |        |       |

| Thermal shutdown threshold <sup>(5)</sup>  |                      |                                                 |       | 140   |        | °C    |

| Thermal shutdown hysteresis <sup>(5)</sup> |                      |                                                 |       | 40    |        | °C    |

Notes:

(5) The parameters are guaranteed by characterization.

## **PIN FUNCTIONS**

| SOIC8-7A<br>Pin # | Name | Description                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                 | CS   | <b>Current sense.</b> CS connects to the current sense resistor to detect the MOSFET current for peak current mode control in CV and CC modes. CS can also be used to select a sampling time by different external resistor configurations. Connect CS to current sensing resistor directly, if default sampling time is selected. Please refer to EC table for additional details of sampling time selection.                                     |

| 2                 | DRV  | Driver. DRV drives the external power MOSFET.                                                                                                                                                                                                                                                                                                                                                                                                      |

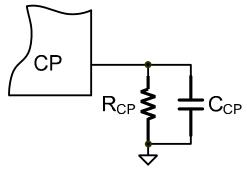

| 3                 | СР   | <b>Output cable compensation.</b> Usually, a $1\mu$ F ceramic capacitor can be connected to CP as a low pass-filter. The compensation voltage can be adjusted by the divided resistor. CP can also be used to select the secondary duty limitation by different external resistor configurations. Short CP to GND, if default secondary duty is selected and cable compensation isn't required.<br>Please refer to Table 1 for additional details. |

| 4                 | VCC  | <b>Supply voltage of the IC.</b> When VCC is lower than a certain level ( $V_{CCL}$ ), the internal high-voltage current source is turned on to charge VCC. When VCC is charged to a certain level ( $V_{CCH}$ ) by the internal high-voltage current source, the IC begins working. Connect a 0.1µF ceramic capacitor as close to VCC as possible to decouple the noise and the bulk capacitor.                                                   |

| 5                 | FB   | Feedback. Voltage on FB determines the operation mode (CV or CC mode).                                                                                                                                                                                                                                                                                                                                                                             |

| 6                 | GND  | Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 8                 | HV   | Internal high-voltage current source. HV draws current from the bus to charge up VCC for start-up.                                                                                                                                                                                                                                                                                                                                                 |

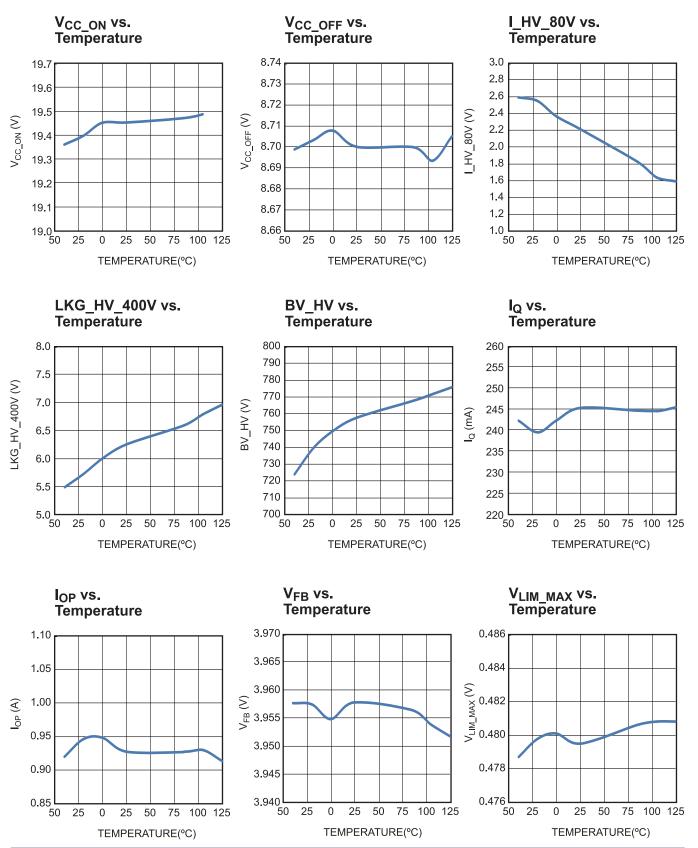

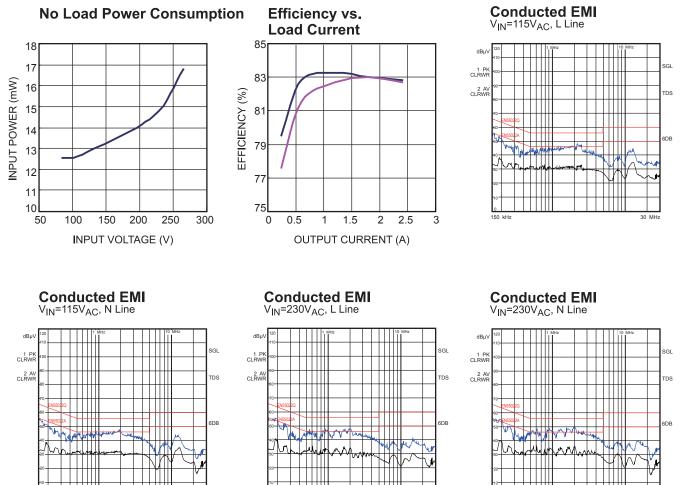

# **TYPICAL CHARACTERISTICS**

www.MonolithicPower.com

MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2016 MPS. All Rights Reserved.

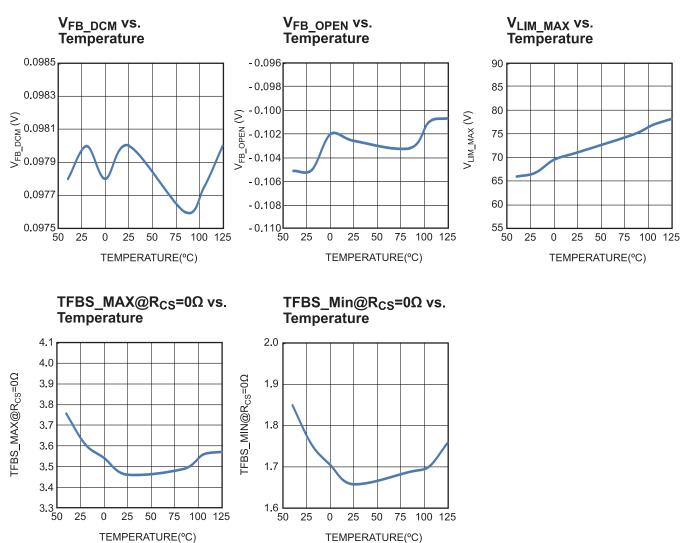

## **TYPICAL CHARACTERISTICS** (continued)

# **TYPICAL PERFORMANCE CHARACTERISTICS**

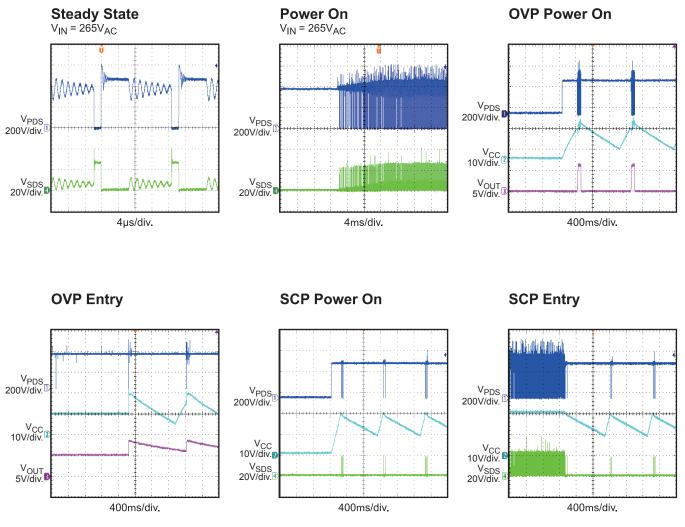

Performance waveforms are tested on the evaluation board of the Design Example section.  $V_{IN} = 230V_{AC}$ , unless otherwise noted.

30 MHz

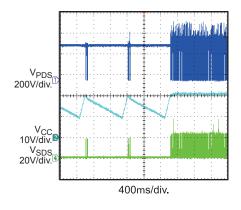

## **TYPICAL PERFORMANCE CHARACTERISTICS** (continued)

Performance waveforms are tested on the evaluation board of the Design Example section.  $V_{IN}$  = 230 $V_{AC}$ , unless otherwise noted.

### **SCP Recovery**

MP023 Rev. 1.1 7/18/2016

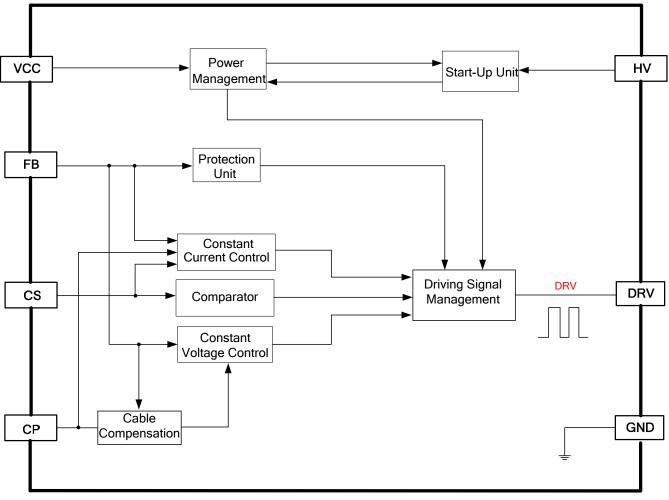

Figure 1: Functional Block Diagram

# **OPERATION**

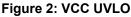

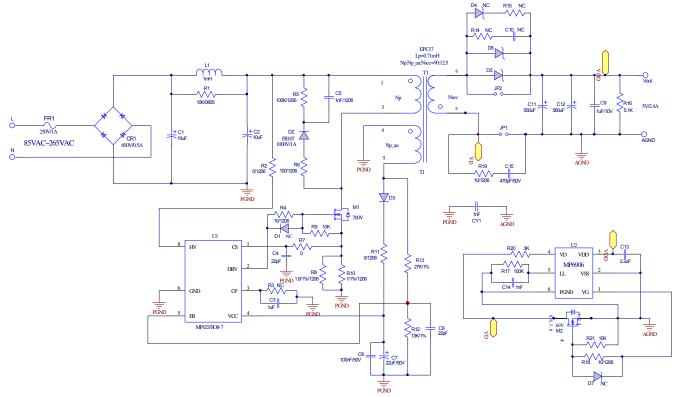

The MP023 is a primary-side controller that provides accurate, constant voltage and constant current regulation without the need of an optocoupler or secondary feedback circuit. As shown in the Typical Application diagram, the circuit is designed to operate with a minimal number of external components.

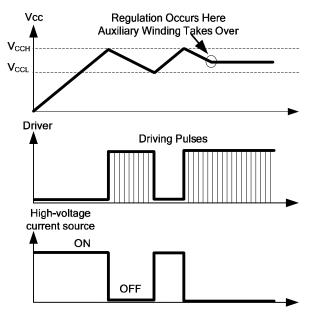

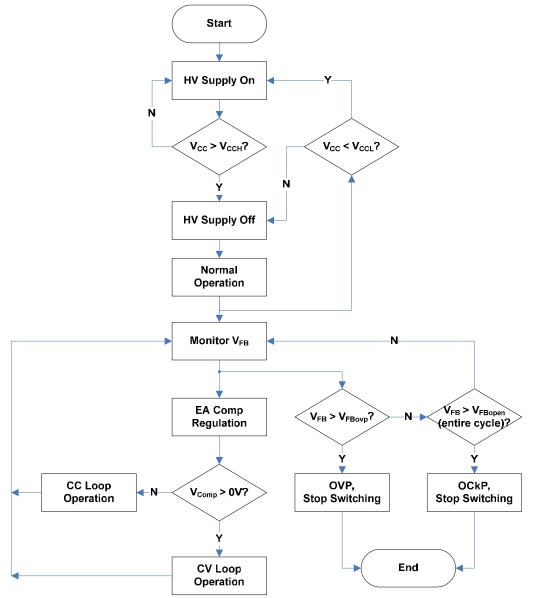

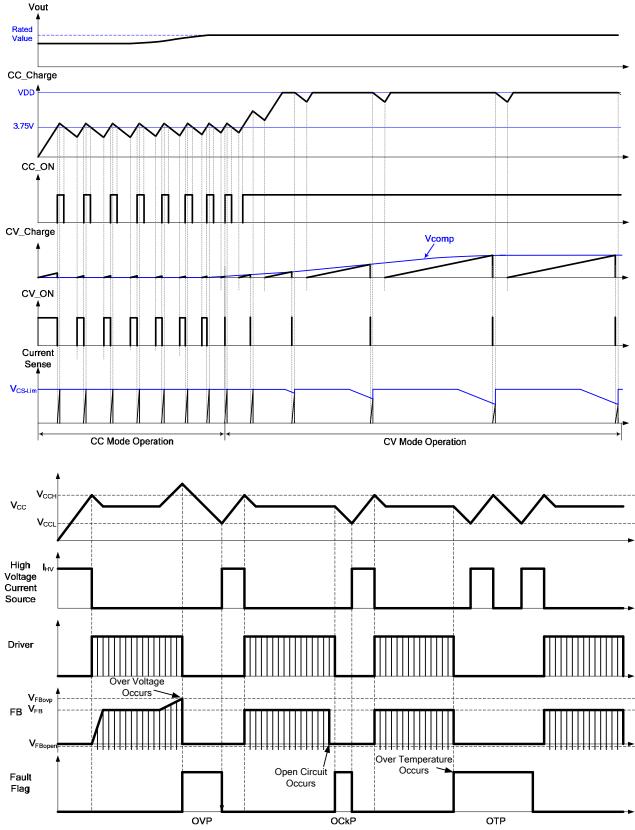

### Start-Up

The IC is self-supplied by the internal highvoltage current source, which is drawn from HV. Once the voltage on VCC reaches the VCC on threshold ( $V_{CCH}$ ), the internal high-voltage current source turns off for better efficiency. Afterward, the auxiliary winding of the transformer takes over the power supply. When VCC falls below the VCC off threshold ( $V_{CCL}$ ), the IC stops switching, and the internal highvoltage current source turns on again (see Figure 2).

### Peak Current Control on the Primary Side

The MP023 senses the primary current  $I_P(t)$  through the current sense resistor ( $R_S$ ), shown in Figure 3.

#### Figure 3: Simplified Flyback Converter

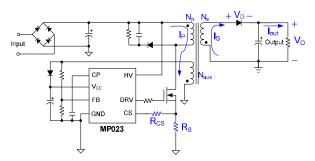

The current rises linearly at a rate shown in Equation (1):

#### Figure 4: Primary Current Waveform

When the current  $I_p(t)$  rises up to  $I_{pk}$  (see Figure 4), the primary switch turns off. The value of  $I_{pk}$  can be calculated with Equation (2):

$$I_{pk} = \frac{V_{CS}}{R_{S}}$$

(2)

The inductor  $(L_m)$  stores energy with each cycle. See Equation (3):

$$\mathsf{E} = \frac{1}{2} \mathsf{L}_{\mathsf{m}} \mathsf{I}_{\mathsf{pk}}^2 \tag{3}$$

The power transferred from the input to the output can be calculated with Equation (4):

$$P = \frac{1}{2} L_m l_{pk}^2 f_s \tag{4}$$

Where  $f_S$  is the switching frequency.

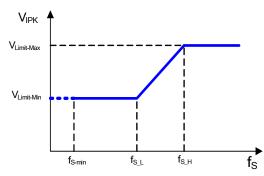

In constant current (CC) operation, the reference for  $I_{pk}$  is fixed at  $V_{\text{Limit-Max}}$ . In constant voltage (CV) operation,  $I_{pk}$  is modulated by the switching frequency (see Figure 5).

Figure 5: Peak Current Modulation

In the event that the external current sensing resistor is shorted, the maximum turn-on time is limited internally at  $t_{ONmax}$ . If this maximum limitation is reached, the IC enters protection mode.

#### **Constant Voltage (CV) Operation**

The MP023 detects the auxiliary winding voltage from FB and operates in constant voltage (CV) mode to regulate the output voltage.

The auxiliary voltage can be calculated with Equation (5):

$$V_{aux} = \frac{N_{aux}}{N_s} (V_O + V_D)$$

(5)

Where  $V_D$  is the forward drop voltage of the secondary diode.

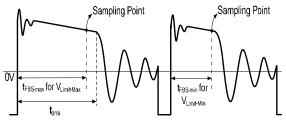

During the conduction time of the secondary diode, the difference between the output voltage and the voltage on the secondary winding is not constant since  $V_D$  varies with the current flowing through the diode. To compensate for the voltage drop difference, the sampling time decreases gradually from  $t_{FBS-Max}$  to  $t_{FBS-Min}$  as the current limitation folds back from  $V_{Limit-Max}$  to  $V_{Limit-Max}$  to  $V_{Limit-Min}$  (see Figure 6).

Figure 6: FB Voltage Sampling Point

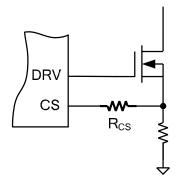

The FB sampling time is also customizable with different resistor values connected to CS (see Figure 7). Please refer to EC table for details.

Figure 7: External Resistor for Sampling Time Customization

Choose a sampling time toward the end of the secondary diode conduction period to improve the accuracy of the CV regulation. The CV regulation loop then generates the switching frequency to regulate the output voltage based on the sampled voltage.

#### Constant Current (CC) Operation

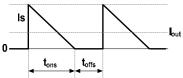

Figure 8 shows the secondary current waveforms.

Figure 8: Secondary Current Waveform

In constant current (CC) operation, the CC loop control function remains at a fixed ratio between the secondary diode on time ( $t_{ons}$ ) and the secondary diode off time ( $t_{offs}$ ) by charging or discharging the internal capacitance. The fixed ratio limits the maximum duty of the secondary side diode on time, as shown in Equation (6):

$$\frac{t_{ons}}{t_{ons} + t_{offs}} = D_{S-Max}$$

(6)

For applications with varying output voltages, the  $D_{S-Max}$  can be customized with CP. If CP is connected with a capacitor directly or shorted to GND, the  $D_{S-Max}$  remains at a default value of 0.4. However, if CP is connected with a resistor (Figure 9), several choices are available based on the different resistances.

Figure 9: The External Configuration of CP

Table 1 shows all available values for  $D_{S-Max}$ . The entire customization process is completed before start-up and latched in a register, so it does not have any influence on normal operation.

| $R_{CP}/C_{CP}$     | D <sub>S-Max</sub> |

|---------------------|--------------------|

| 0 Ω/NC <sup>*</sup> | 0.4                |

| 10 kΩ/NC            | 0.3                |

| 20 kΩ/NC            | 0.35               |

| 40 kΩ/NC            | 0.5                |

| NC/1µF              | 0.4                |

Table 1: D<sub>S-Max</sub> vs. CP Configuration

Notes:

\* NC means no connection.

$I_{pk}$  is also fixed in CC operation. The relationship between the output constant current and secondary peak current ( $I_{pks}$ ) can be calculated with Equation (7):

$$I_{out} = \frac{1}{2} I_{pks} \frac{t_{ons}}{t_{ons} + t_{offs}} = \frac{1}{2} I_{pks} D_{S-Max}$$

(7)

When the secondary diode is turned on, the peak current on the secondary side is calculated with Equation (8):

$$I_{pks} = \frac{N_p}{N_s} I_{PK}$$

(8)

The output current is then calculated with Equation (9):

$$I_{out} = \frac{1}{2} \frac{N_p}{N_s} I_{PK} D_{S-Max}$$

(9)

To implement the OLP function in CC mode, the sampling on the FB voltage continues running with the sampling time fixed at  $t_{\text{FBS-Max}}$ .

### Leading Edge Blanking

Turning the power switch on induces a spike on the sense resistor. The MP023 employs a leading edge blanking period ( $t_{LEB}$ ) to avoid falsely terminating the switching pulse. During this blanking period, the current sense comparator is disabled, and the part cannot be turned off.

#### **DCM Detection**

The MP023 is designed to operate in discontinuous conduction mode (DCM) in both CV and CC modes. To avoid operating in continuous conduction mode (CCM), the MP023 implements a zero current detection (ZCD) function internally with a threshold of  $V_{DCM}$ . The IC does not start the next cycle until ZCD is detected.

During normal operation, the blanking time for ZCD is synchronized with the FB sampling time (i.e., ZCD always starts after the sampling phase is done). There is also a soft-start function on the ZCD blanking time to prevent ZCD from being triggered falsely when the output capacitor is not charged up. During the start-up period, the blanking time for ZCD shrinks gradually from  $t_{B_{STP}}$  (10µs) to the FB sampling time in 3 cycles.

### OVP, OCkP, and OLP

The MP023 includes over-voltage protection (OVP), open-circuit protection (OCkP), and overload protection (OLP). If the voltage on FB exceeds  $V_{FBovp}$ , OVP is triggered. If  $V_{FBopen}$  cannot be monitored for each cycle, OCkP is triggered. If the sampled FB voltage is lower than  $V_{FBolp}$  for 128 consecutive cycles, OLP is triggered. When any of these protections are triggered, the MP023 shuts off immediately, enters hiccup mode, and resumes normal operation ( $t_{ons}$ ) when the fault has been removed.

OLP is not enabled until the soft-start period of the ZCD blanking time is finished.

### **Over-Temperature Protection (OTP)**

When the temperature of the IC exceeds 150°C, the over-temperature protection (OTP) is activated, and the IC enters auto-recovery mode. When the temperature falls below 120°C, the IC resumes operation.

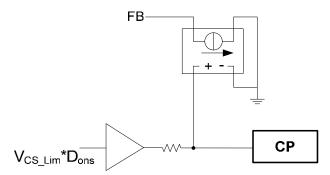

#### **Output Cable Compensation**

The MP023 has an internal output cable compensation (CP) circuit (see Figure 10). A switching signal ( $V_{CS\_Lim}*D_{ons}$ ) is generated internally and is synchronized with the switching frequency. The duty on-time of this signal is  $D_{ons}$ , and the amplitude of this signal is proportional to the current-limit threshold. This signal is output to CP through a 1M $\Omega$  resistor. A low pass filter can be implemented by placing an external capacitor on CP, and then a DC voltage ( $V_{CP}$ ) proportional to the output current can be deducted on CP. Note that if cable compensation function is needed,  $D_{S-Max}$  is default as 0.4 and can't be programmable by connecting external CP resistor.

Figure 10: Output Cable Compensation

Table 2 shows some typical voltage levels on CP when a low pass filter is applied as described above.

| Table 2: Typical CF | Voltage Levels | (C <sub>CP</sub> = 1µF) |

|---------------------|----------------|-------------------------|

|---------------------|----------------|-------------------------|

| V <sub>Limit</sub> | D <sub>ons</sub> | V <sub>CP</sub> |

|--------------------|------------------|-----------------|

| 500mV              | 0.4              | 1.6V            |

| 500mV              | 0.35             | 1.4V            |

| 400mV              | 0.3              | 0.96V           |

| 250mV              | 0.1              | 0.2V            |

An internal current sink in FB is proportional to  $V_{CP}$ . The voltage drop on the upper resistor of the divider implements the output cable compensation function.

The equation below determines the compensation voltage:

$$V_{FCP} = \frac{8 \times V_{\text{Limit}} \times D_{\text{S}}}{300 \times 10^{3}} \times 2 \times R_{\text{UP}} \times \frac{N_{\text{S}}}{N_{\text{P} \text{AU}}}$$

(10)

Where:

- D<sub>S</sub> is the secondary-diode duty cycle,

- R<sub>UP</sub> is the upper resistor of resistor divider,

- N<sub>s</sub> is the number of turns for the secondaryside transformer windings,

- N<sub>P\_AU</sub> is the number of transformer auxiliary winding turns,

- V<sub>Limit</sub> is the current limit,

Since CP is also used for  $D_{S-Max}$  customization, the cable compensation function is only available when CP is connected to the capacitors directly. If there is a non-zero resistor connected to CP, all of the internal blocks related to the cable compensation function are disabled. During normal operation under this condition, CP is clamped to GND internally and there is no current flowing through FB.

## **APPLICATION INFORMATION**

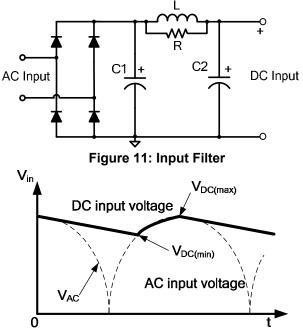

#### **Input Filter**

The input filter helps to convert the AC input voltage to DC voltage. Figure 11 shows the input filter, and Figure 12 shows the typical DC bus voltage waveform after the rectifier.

Figure 12: DC Input Voltage Waveform

The bulk capacitors (C1 and C2) filter the rectified AC input. The inductor (L) forms a pi ( $\pi$ ) filter with C1 and C2 to restrain the differential mode EMI noise. The resistor (R) in parallel with L restrains the mid-frequency band EMI noise. Normally, R is 1k $\Omega$  to 10k $\Omega$ .

Usually C1 and C2 are set at  $2\mu$ F/W to  $3\mu$ F/W for a universal input condition. For  $230V_{AC}$  single-range applications, cut the capacitor values in half.

A low DC input voltage causes insufficient output current due to the maximum on-duty limitation of the secondary side. To avoid this situation, calculate the minimum input DC voltage with Equation (11):

$$V_{DC(min)} \ge \frac{N_{p}}{N_{s}}(V_{O} + V_{D})\frac{D_{S-Max}}{1 - D_{S-Max}}$$

(11)

If  $V_{DC(min)}$  cannot satisfy this expression, use larger input capacitors to increase  $V_{DC(min)}$ .

#### **Output Capacitor**

Low or very low ESR output capacitors are recommended to meet the output voltage ripple requirements. Low ESR capacitors improve the output voltage regulation accuracy at high or low temperatures. Output capacitors with an ESR of tens of m $\Omega$  provide better efficiency than high ESR output capacitors.

#### **Output Diode or Synchronous Rectifier**

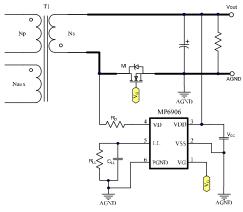

Schottky diodes are recommended for their fast switching speeds and low forward-voltage drops for better high or low temperature CV regulation and efficiency.

If lower average efficiency (3% to 4%) is acceptable, replace the output diode with a fast or ultra-fast diode to reduce cost. Re-adjust the resistor divider values for an accurate output voltage since the forward voltage drop is higher than the Schottky diode.

If the circuit has a high efficiency requirement, it is recommended to use a synchronous rectifier (SR) instead. The MP6906 is a suitable SR controller where the output voltage is low and there is no need for a secondary auxiliary winding. Figure 13 shows a typical SR circuit. The MP6906 is available in a SOT23-6 package, which does not require extra PCB dimensions or external components.

Figure 13: Synchronous Rectifier

#### Leakage Inductance

The transformer's leakage inductance decreases system efficiency and affects either the output current or voltage constant precision. The transformer structure can be optimized to minimize the leakage inductance. The leakage inductance should be less than 5% of the primary inductance.

www.MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2016 MPS. All Rights Reserved.

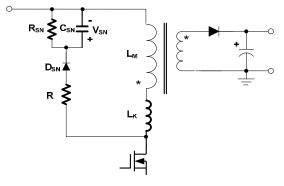

#### **RCD Snubber**

The transfomer's leakage inductance causes MOSFET drain voltage spikes and excessive ringing on the drain voltage waveform, which affects the output voltage sampling after the primary MOSFET turns off.

The RCD snubber circuit limits the drain voltage spike. Figure 14 shows the RCD snubber circuit.

Figure 14: RCD Snubber

Select  $R_{SN}$  and  $C_{SN}$  to meet the voltage spike requirements and improve system operation.

The power dissipated in the snubber circuit can be approximated with Equation (12):

$$P_{SN} = \frac{1}{2} L_{K} I_{PK}^{2} \frac{V_{SN}}{V_{SN} - N_{PS} V_{O}} f_{S}$$

(12)

Where  $L_K$  is the leakage inductance,  $V_{SN}$  is the clamp voltage, and  $N_{PS}$  is the turn ratio of the primary-to-secondary side.

Since  $R_{SN}$  consumes the majority of the power, calculate  $R_{SN}$  with Equation (13):

$$R_{SN} = \frac{V_{SN}^2}{P_{SN}}$$

(13)

The maximum ripple of the snubber capacitor voltage is then calculated with Equation (14):

$$\Delta V_{\rm SN} = \frac{V_{\rm SN}}{C_{\rm SN}R_{\rm SN}f_{\rm S}}$$

(14)

Generally, a 15% ripple is reasonable. The previous equation can also be used to estimate  $C_{\text{SN}}$ .

Select a time constant (t =  $R_{SN}xC_{SN}$ ) less than 0.1ms for better CV sampling.

The RCD resistor is a trade-off based on the power loss and the acceptable clamp voltage in practical applications.

The damping resistor in series with the RCD has a relatively large value to prevent any excessive voltage ringing that can affect the CV sampling and increase the output ripple. Use a damping resistor value in the range of  $100\Omega$  to  $500\Omega$  to restrain the drain voltage ringing.

#### **Divided Resistor**

For better application performance, select the resistor divider values from  $10k\Omega$  to  $100k\Omega$  to limit noise from adjacent components on FB. An RC filter can be inserted between the resistor divider and FB to sense purified voltage. The C<sub>FB</sub> value is recommended to be several pF, and R<sub>FB</sub> is recommended to be between  $1k\Omega$  and  $2k\Omega$ . R<sub>FB</sub> can also limit substrate injection current effects (see Figure 15).

Figure 15: Feedback Resistor Divider Circuit

For accurate CV regulation, the accuracy of these feedback resistors should be at least 1%.

#### Dummy Load

When the system operates without any load, the output voltage rises above normal operation because of the minimum switching frequency limitation. Use a dummy load for good load regulation. The dummy load is a trade-off between efficiency and load regulation. For example, a large dummy load can deteriorate efficiency and the no-load consumption. For most applications, several mWs for a dummy load is reasonable.

#### Maximum Switching Frequency

The maximum switching frequency should be limited by the sampling point. Figure 7 and EC table show the relationship of  $R_{CS}$  and the sampling point. The secondary on time must be longer than the maximum  $T_{FBS-Max}$ . Calculate  $T_{S ON}$  with Equation (15):

$$T_{\text{S}_{ON}} = I_{\text{PK}} \frac{N_{\text{S}} \cdot L_{\text{M}}}{N_{\text{P}} \cdot (V_{\text{O}} + V_{\text{D}})} > t_{\text{FBS}_{\text{Max}}} + t_{\text{FB}_{\text{SD}}} \quad (15)$$

Where  $T_{FBS-Max}$  is the FB maximum sampling time, and  $t_{FB_SD}$  is the FB sampling duration.

Combine Equation (15) and the relationship of  $R_{CP}$  and  $D_{S-Max}$  shown in Table 1 to fix the maximum switching frequency.

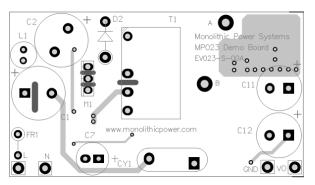

#### **PCB Layout Guidelines**

Efficient PCB layout is critical for stable operation, good EMI, and good thermal performance. For best results, refer to Figure 16 and follow the guidelines below.

- 1. Minimize the loop area formed by the input capacitor, the primary transformer winding, the MOSFET drain source, and the sensing resistor to reduce EMI noise.

- 2. Minimize the voltage jumping area, such as the MOSFET drain, the anode of the secondary diode, etc. for better EMI.

- 3. Minimize the clamp circuit loop to reduce EMI.

- 4. Minimize the secondary loop area of the output diode and output filter to reduce EMI noise. Sufficient copper areas should be provided at the cathode terminal of the output diode to act as a heat sink.

- 5. Place the AC input away from the switching nodes to minimize any noise coupling that may bypass the input filter.

- 6. Place the bypass capacitor as close to the IC as possible.

- 7. Place the feedback resistors next to FB and minimize the feedback sampling loop to minimize noise coupling.

- 8. Use a single-point connection at the negative terminal of the input filter capacitor for the IC GND and bias winding return.

**Top Layer**

Bottom Layer

Figure 16: Recommended Layout

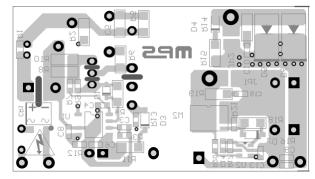

### Design Example

Table 3 is a design example following the application guidelines.

| Table | 3: | Design | Example |

|-------|----|--------|---------|

|-------|----|--------|---------|

| V <sub>IN</sub>  | 85Vac~265Vac<br>47Hz/63Hz |  |

|------------------|---------------------------|--|

| V <sub>OUT</sub> | 5V                        |  |

| I <sub>OUT</sub> | 2.4A                      |  |

| f <sub>S</sub>   | 70kHz                     |  |

Figure 17 shows the detailed application schematic. For more device applications, please refer to the related evaluation board datasheets.

# **TYPICAL APPLICATION CIRCUIT**

Figure 17: Typical Application—Universal Input, 5V/2.4A Output

# **FLOW CHART**

# SIGNAL TIMING SEQUENCE WAVEFORMS

# **PACKAGE INFORMATION**

SOIC8-7A

**NOTICE:** The information in this document is subject to change without notice. Users should warrant and guarantee that third party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.