# **ON Semiconductor**

# Is Now

To learn more about onsemi™, please visit our website at www.onsemi.com

onsemi and ONSEMI. and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. onsemi reserves the right to make changes at any time to any products or information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/ or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use onsemi products for any such unintended or unauthorized application,

# **Bus-Controlled Video Matrix Switch**

## Description

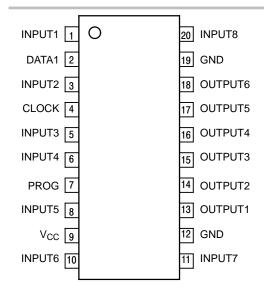

The main function of the NCS6415 is to switch 8 video input sources to the 6 outputs.

Each output can be switched to only one of the inputs, whereas any single input may be connected to several outputs.

All switching possibilities are controlled through the I<sup>2</sup>C bus.

#### **Features**

- Cascadable with another NCS6415 (Internal Address can be changed by Pin 7 Voltage)

- 8 Inputs (CVBS, RGB, Chroma, ...)

- 6 Outputs with Low Impedance Driver

- Possibility of Chroma Signal for each Input by Switching off the Clamp with an External Resistor Bridge

- Bus Controlled

- 6.5 dB Gain between any Input and Output

- -45 dB Crosstalk at 5 MHz

- Compatible with TEA6415C

- Full ESD Protection

- These are Pb-Free Devices

## ON Semiconductor®

http://onsemi.com

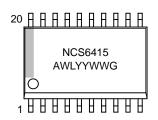

## **MARKING DIAGRAMS\***

SO-20 WB DW SUFFIX CASE 751D

A = Assembly Location

WL = Wafer Lot

YY = Year

WW = Work Week

G = Pb-Free Package

\*For additional marking information, refer to Application Note AND8002/D.

#### **ORDERING INFORMATION**

| Device       | Package            | Shipping <sup>†</sup> |

|--------------|--------------------|-----------------------|

| NCS6415DWG   | SO-20<br>(Pb-Free) | 38 Units / Rail       |

| NCS6415DWR2G | SO-20<br>(Pb-Free) | 1000 / Tape & Reel    |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

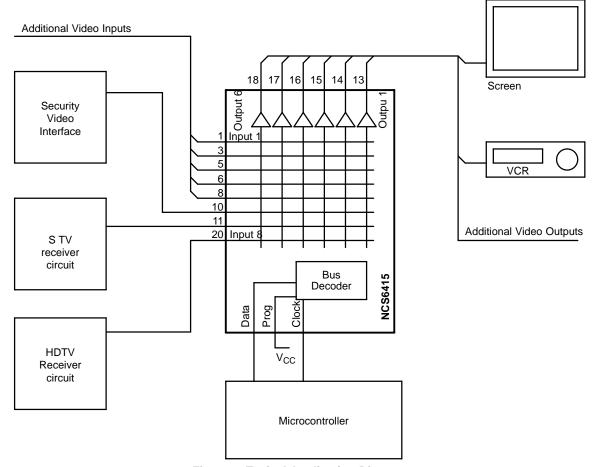

Figure 1. Block Diagram

The main function of the NCS6415 is to switch 8 video input sources to the 6 outputs.

Each output can be switched to only one of the inputs, whereas any single input may be connected to several outputs. The lowest level of each signal is aligned on each input (bottom of sync pulse for CVBS or Black Level for RGB signals).

The nominal gain between any input and output is 6 dB. For Chroma signals, the alignment is switched off by forcing, with an external 5' VDC resistor bridge on the input.

Each input can be used as a normal input or as a Chroma input (with external resistor bridge). All the switching possibilities are changed through the I<sup>2</sup>C bus.

The switches configuration is defined by words of 16 bits: one word of 16 bits for each output channel.

So, 6 words of 16 bits are necessary to determine the starting configuration upon power—on (power supply: 0 to 10 V). But a new configuration needs only the words of the changed output channels. Driving a 75  $\Omega$  load requires an external transistor.

**Table 1. ATTRIBUTES**

| Characteristics               |                                   | Value                 |

|-------------------------------|-----------------------------------|-----------------------|

| ESD                           | Human Body Model<br>Machine Model | 4 kV<br>400 V         |

| Moisture Sensitivity (Note 1) |                                   | Level 3               |

| Flammability Rating           | Oxygen Index: 28 to 34            | UL 94 V-0 @ 0.125 in. |

<sup>1.</sup> For additional information, see Application Note AND8003/D

**Table 2. MAXIMUM RATINGS**

| Parameter                           |       | Symbol           | Rating      | Unit |

|-------------------------------------|-------|------------------|-------------|------|

| Power Supply Voltage                |       | V <sub>CC</sub>  | 12          | V    |

| Operating Temperature Range         |       | T <sub>A</sub>   | 0 to +70    | °C   |

| Storage Temperature Range           |       | T <sub>stg</sub> | -60 to +150 | °C   |

| Thermal Resistance, Junction-to-Air | SO-20 | $\theta_{JA}$    | 30 to 35    | °C/W |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

Table 3. DC & AC Characteristics (T<sub>A</sub> = 25°C, V<sub>CC</sub> = 10 V, R<sub>L</sub> = 10 k $\Omega$ , C<sub>L</sub> = 3 pF)

| Symbol                 | Parameter                                                                  | Min                     | Тур        | Max | Unit     |

|------------------------|----------------------------------------------------------------------------|-------------------------|------------|-----|----------|

| V <sub>CC</sub>        | Supply Voltage                                                             | 8                       | 10         | 11  | V        |

| Icc                    | Power Supply Current (No Load)                                             | 20                      | 30         | 40  | mA       |

| INPUTS                 |                                                                            |                         |            |     | •        |

|                        | Signal Amplitude (CVBS signal) (Note 2)                                    |                         | 1.5        | 2   | $V_{PP}$ |

|                        | Input Current (per output connected, V <sub>IN</sub> = 5 V <sub>DC</sub> ) |                         | 1          | 3   | μΑ       |

|                        | DC Level                                                                   | 3.3                     | 3.6        | 3.9 | V        |

|                        | DC Level Shift (0°C to 70°C)                                               |                         | 5          | 100 | mV       |

| R <sub>IN</sub>        | Input Resistance                                                           |                         | 1          |     | МΩ       |

| C <sub>IN</sub>        | Input Capacitance                                                          |                         | 2          |     | pF       |

| OUTPUTS                | 3                                                                          |                         |            |     |          |

|                        | Dynamic (V <sub>IN</sub> = 2.5 V <sub>PP</sub> )                           |                         | 5          |     | $V_{PP}$ |

|                        | Output Impedance (Note 2)                                                  |                         | 25         | 50  | Ω        |

| A <sub>V</sub>         | Gain (Note 2)                                                              | 6                       | 6.5        | 7   | dB       |

| BW                     | Bandwidth (Note 2) -1 dB Attenuation -3 dB Attenuation                     | 7                       | 15<br>20   |     | MHz      |

|                        | 0.1 dB Gain Flatness (Note 2)                                              | 6                       |            |     | MHz      |

|                        | Crosstalk f =                                                              | = 3.58 MHz<br>f = 5 MHz | -48<br>-45 |     | dB       |

|                        | DC Level                                                                   | 2.4                     | 2.75       | 3.1 | V        |

| I <sup>2</sup> C BUS I | NPUT: DATA, CLOCK AND PROG                                                 |                         |            |     | •        |

|                        | Threshold Voltage                                                          | 1.5                     | 2          | 3   | V        |

<sup>2.</sup> Guaranteed by design and/or characterization.

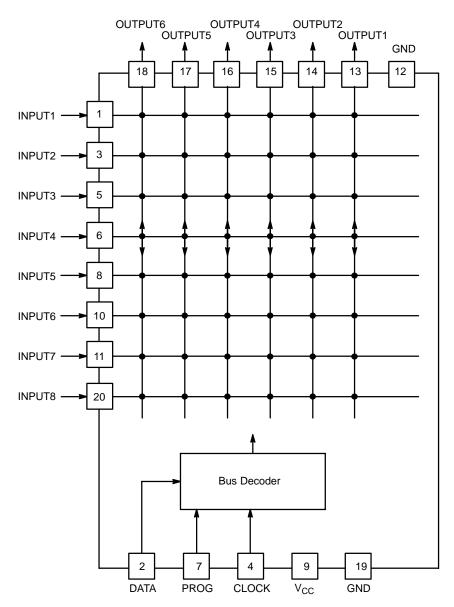

Table 4. I<sup>2</sup>C Bus Characteristics

| Symbol              | Parameter                                                        | Test Conditions        | Min  | Max                  | Unit |

|---------------------|------------------------------------------------------------------|------------------------|------|----------------------|------|

| SCL                 |                                                                  |                        |      |                      |      |

| V <sub>IL</sub>     | Low Level Input Voltage                                          |                        | -0.3 | +1.5                 | V    |

| V <sub>IH</sub>     | High Level Input Voltage                                         |                        | 3.0  | V <sub>CC</sub> +0.5 | V    |

| ILI                 | Input Leakage Current                                            | $V_I = 0$ to $V_{CC}$  | -10  | +10                  | μΑ   |

| f <sub>SCL</sub>    | Clock Frequency (Note 3)                                         |                        | 0    | 100                  | kHz  |

| t <sub>R</sub>      | Input Rise Time (Note 3)                                         | 1.5 V to 3 V           |      | 1000                 | ns   |

| t <sub>F</sub>      | Input Fall Time (Note 3)                                         | 3 V to 1.5 V           |      | 300                  | ns   |

| C <sub>I</sub>      | Input Capacitance (Note 3)                                       |                        |      | 10                   | pF   |

| SDA                 |                                                                  |                        |      |                      |      |

| V <sub>IL</sub>     | Low Level Input Voltage                                          |                        | -0.3 | +1.5                 | V    |

| V <sub>IH</sub>     | High Level Input Voltage                                         |                        | 3.0  | V <sub>CC</sub> +0.5 | V    |

| ILI                 | Input Leakage Current                                            | $V_I = 0$ to $V_{CC}$  | -10  | +10                  | μΑ   |

| C <sub>I</sub>      | Input Capacitance (Note 3)                                       |                        |      | 10                   | pF   |

| t <sub>R</sub>      | Input Rise Time (Note 3)                                         | 1.5 V to 3 V           |      | 1000                 | ns   |

| t <sub>F</sub>      | Input Fall Time (Note 3)                                         | 3 V to 1.5 V           |      | 300                  | ns   |

| V <sub>OL</sub>     | Low Level Output Voltage                                         | I <sub>OL</sub> = 3 mA |      | 0.4                  | V    |

| t <sub>F</sub>      | Output Fall Time (Note 3)                                        | 3V to 1.5 V            |      | 250                  | ns   |

| CL                  | Load Capacitance                                                 |                        |      | 400                  | pF   |

| TIMING              |                                                                  | -                      |      |                      |      |

| t <sub>LOW</sub>    | Clock Low Period (Note 4)                                        |                        | 4.7  |                      | μs   |

| t <sub>HIGH</sub>   | Clock High Period (Note 4)                                       |                        | 4.0  |                      | μs   |

| t <sub>SU,DAT</sub> | Data Setup Time (Note 4)                                         |                        | 250  |                      | ns   |

| t <sub>HD,DAT</sub> | Data Hold Time (Note 4)                                          |                        | 0    | 340                  | ns   |

| t <sub>SU,STO</sub> | Setup Time from Clock High to Stop (Note 4)                      |                        | 4.0  |                      | μs   |

| t <sub>BUF</sub>    | Start Setup Time following a Stop (Note 4)                       |                        | 4.7  |                      | μS   |

| t <sub>HD,STA</sub> | Start Hold Time (Note 4)                                         |                        | 4.0  |                      | μS   |

| t <sub>SU,STA</sub> | Start Setup Time following Clock Low to High Transition (Note 4) |                        | 4.7  |                      | μs   |

Guaranteed by design and/or characterization.

Functionality guaranteed by design and/or characterization.

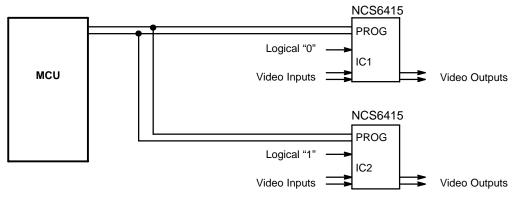

## I<sup>2</sup>C Bus Selections

The I<sup>2</sup>C chip address is defined by the first byte. The second byte defines the input/output configuration.

Table 5. CHIP ADDRESS BYTE (1ST BYTE OF TRANSMISSION)

| HEX | BINARY    | Comment                                       |  |

|-----|-----------|-----------------------------------------------|--|

| 86  | 1000 0110 | When PROG pin is connected to Ground          |  |

| 06  | 0000 0110 | When PROG pin is connected to V <sub>CC</sub> |  |

Input/Output Selection Byte (2<sup>nd</sup> byte of transmission)

Table 6. I<sup>2</sup>C BUS OUTPUT SELECTIONS

| Output Address (MSB) | Input Address (LSB) | Selected Output |                                   |

|----------------------|---------------------|-----------------|-----------------------------------|

| 00000                | XXX                 | Pin 18          | Output is selected by the 5 MSBs. |

| 00100                | XXX                 | Pin 14          |                                   |

| 00010                | XXX                 | Pin 16          |                                   |

| 00110                | -                   | Not Used        |                                   |

| 00001                | XXX                 | Pin 17          |                                   |

| 00101                | XXX                 | Pin 13          |                                   |

| 00011                | XXX                 | Pin 15          |                                   |

| 00111                | -                   | Not Used        |                                   |

Table 7. I<sup>2</sup>C BUS INPUT SELECTIONS

| Output Address (MSB) | Input Address (LSB) | Selected Input |                                  |

|----------------------|---------------------|----------------|----------------------------------|

| 00XXX                | 000                 | Pin 5          | Input is selected by the 3 LSBs. |

| 00XXX                | 100                 | Pin 8          |                                  |

| 00XXX                | 010                 | Pin 3          |                                  |

| 00XXX                | 110                 | Pin 20         |                                  |

| 00XXX                | 001                 | Pin 6          |                                  |

| 00XXX                | 101                 | Pin 10         |                                  |

| 00XXX                | 011                 | Pin 1          |                                  |

| 00XXX                | 111                 | Pin 11         |                                  |

Example: 0010 0101 (Binary) or 25 (Hex) connects Pin 10 (input) to Pin 14 (output)

Figure 2. I<sup>2</sup>C Timing Diagram

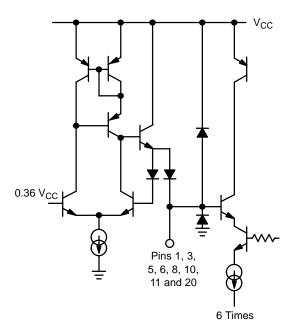

Figure 3. Input Configuration

Figure 4. Output Configuration

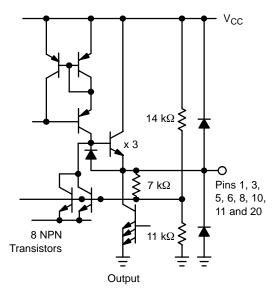

Figure 5. Bus I/O Configuration

Figure 6.  $V_{CC}$  Pin Configuration

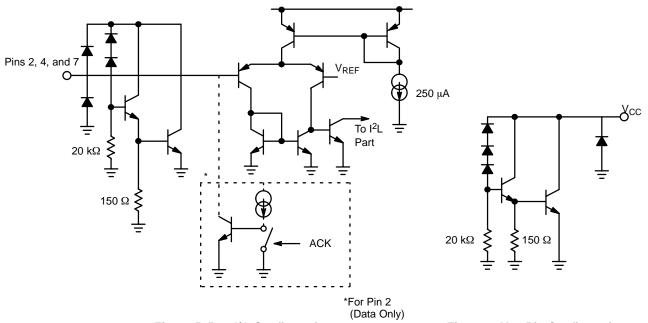

## **USING A SECOND NCS6415**

The programming input pin (PROG) allows two NCS6415 circuits to operate in parallel and to select them independently through the I<sup>2</sup>C bus by modifying the address

byte. Consequently, the switching capabilities are doubled, or IC1 and IC2 can be cascaded (see Figure 7).

Figure 7. Cascaded NCS6415

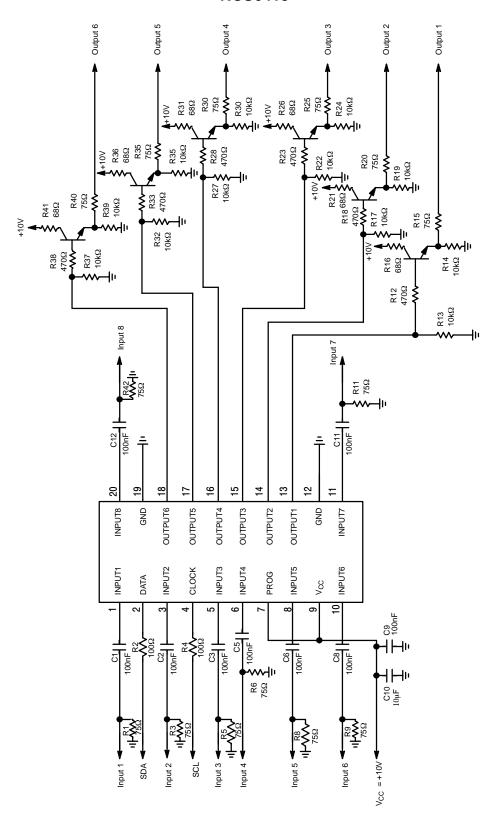

#### TYPICAL APPLICATION DIAGRAM

NCS6415 is suited for single supply system, running on a single  $\pm 10~V$  supply. The high quality of the output stage and excellent linearity provides video signal comparable to

broadcast studio quality signals. The layout is not as critical to the design and it can be easily realized on a single sided board.

Figure 8. Typical Application Diagram

**Figure 9. Typical Application Circuit**

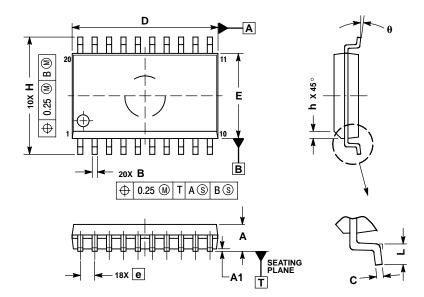

#### PACKAGE DIMENSIONS

**SO-20 WB** CASE 751D-05 **ISSUE G**

#### NOTES:

- DIMENSIONS ARE IN MILLIMETERS.

- INTERPRET DIMENSIONS AND TOLERANCES PER ASME Y14.5M, 1994.

- DIMENSIONS D AND E DO NOT INCLUDE MOLD PROTRUSION.

- PROTRUSION.

MAXIMUM MOLD PROTRUSION 0.15 PER SIDE.

DIMENSION B DOES NOT INCLUDE DAMBAR

PROTRUSION. ALLOWABLE PROTRUSION

SHALL BE 0.13 TOTAL IN EXCESS OF B

DIMENSION AT MAXIMUM MATERIAL CONDITION.

|     | MILLIMETERS |       |  |

|-----|-------------|-------|--|

| DIM | MIN         | MAX   |  |

| Α   | 2.35        | 2.65  |  |

| A1  | 0.10        | 0.25  |  |

| В   | 0.35        | 0.49  |  |

| С   | 0.23        | 0.32  |  |

| D   | 12.65       | 12.95 |  |

| Е   | 7.40        | 7.60  |  |

| е   | 1.27        | BSC   |  |

| Н   | 10.05       | 10.55 |  |

| h   | 0.25        | 0.75  |  |

| L   | 0.50        | 0.90  |  |

| A   | 0 0         | 7 °   |  |

ON Semiconductor and un are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice on semiconductor and are registred traderlands of semiconduction Components industries, LCC (SCIELC) science in SCIELC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCIELC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCIELC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts, SCIELC does not convey any license under its patent rights nor the rights of others. SCIELC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

## **PUBLICATION ORDERING INFORMATION**

## LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA **Phone**: 303–675–2175 or 800–344–3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com

N. American Technical Support: 800-282-9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81-3-5773-3850

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative