# Using the TPS650061EVM 2.25 MHz Step-Down Converter with Dual LDO

The TPS650061 is a single chip Power Management ICs for portable applications. The device combines a single step-down converter with two low dropout regulators and a Supply Voltage Supervisor (SVS). The step-down converter enters a low power mode at light load for maximum efficiency across the widest possible range of load currents. For low noise applications the device can be forced into fixed frequency PWM mode. The step-down converter allows the use of a small inductor and capacitors to achieve a small solution size. The step-down converter has Power Good status output that can be used for sequencing. The LDOs are capable of supplying 300mA and can operate with an input voltage range between 1.6V and 6.0V, allowing them to be supplied from the step-down converter or directly from the main battery.

The step-down converter and the LDOs have separate voltage inputs and enables, allowing for design and sequencing flexibility.

#### **Contents**

| 1 | Introd                               | uction                                                       |  |  |  |  |  |

|---|--------------------------------------|--------------------------------------------------------------|--|--|--|--|--|

|   | 1.1                                  | Applications                                                 |  |  |  |  |  |

|   | 1.2                                  | Features                                                     |  |  |  |  |  |

| 2 | TPS6                                 | 50061 EVM Electrical Performance Specifications              |  |  |  |  |  |

| 3 | Schematic                            |                                                              |  |  |  |  |  |

| 4 | Connector and Test Point Description |                                                              |  |  |  |  |  |

|   | 4.1                                  | J1 – VIN/GND                                                 |  |  |  |  |  |

|   | 4.2                                  | J2 – RST/GND                                                 |  |  |  |  |  |

|   | 4.3                                  | J3 – VODC / GND                                              |  |  |  |  |  |

|   | 4.4                                  | J4– VLDO1/GND                                                |  |  |  |  |  |

|   | 4.5                                  | J5 – VLDO2                                                   |  |  |  |  |  |

|   | 4.6                                  | J6 – PG/GND                                                  |  |  |  |  |  |

|   | 4.7                                  | JP1 – VINLDO1                                                |  |  |  |  |  |

|   | 4.8                                  | JP2 – VINLDO2                                                |  |  |  |  |  |

|   | 4.9                                  | JP3 -ENDCDC                                                  |  |  |  |  |  |

|   | 4.10                                 | JP4 –ENLDO1                                                  |  |  |  |  |  |

|   | 4.11                                 | JP5 – ENLDO2                                                 |  |  |  |  |  |

|   | 4.12                                 | JP6 –MODE                                                    |  |  |  |  |  |

|   | 4.13                                 | JP7 – MRPU                                                   |  |  |  |  |  |

|   | 4.14                                 | JP8 – VPU                                                    |  |  |  |  |  |

|   | 4.15                                 | JP9 – RSTSNS_IN                                              |  |  |  |  |  |

| 5 | TPS6                                 | TPS650061 Typical Performance Data and Characteristic Curves |  |  |  |  |  |

|   | 5.1                                  | Efficiency                                                   |  |  |  |  |  |

|   | 5.2                                  | Line and Load Regulation                                     |  |  |  |  |  |

|   | 5.3                                  | Output Voltage Ripple                                        |  |  |  |  |  |

|   | 5.4                                  | Startup Timing                                               |  |  |  |  |  |

| 6 | EVM /                                | Assembly Drawings and Layout1                                |  |  |  |  |  |

| 7 | List of                              | Materials                                                    |  |  |  |  |  |

|   |                                      | List of Figures                                              |  |  |  |  |  |

| 1 | TPS6                                 | 50061EVM Schematic                                           |  |  |  |  |  |

| 2 | TPS6                                 | TPS650061 Efficiency vs Load Current                         |  |  |  |  |  |

Introduction www.ti.com 3 4 TPS650061 LDOx Load Transient Response 8 5 6 TPS650061 Output Voltage Ripple (MODE = low) 9 7 8 9 10 11 12 TPS650061EVM Bottom Copper (View from Bottom) 13 **List of Tables** 1 2

## 1 Introduction

# 1.1 Applications

- Point of Load

- Embedded Processor Power

- Cell Phones, Smart-phones

- PDAs, Pocket PCs

- Portable Media Players

## 1.2 Features

- Input Voltage Rating: 2.3-V up to 6.0-V

- Output voltages of DCDC converter externally adjustable, output voltages of LDOs internally fixed

- Output Current Rating 1.0 A (DCDC converter) / 300-mA (LDOs)

- Spread Spectrum Clock (SSC) for best EMI performance

- Supply Voltage Supervisor : Adjustable Reset Voltage / Time , Manual Reset

- 2.25-MHz Switching Frequency

- 20 pin 3mm x 3mm QFN package

# 2 TPS650061 EVM Electrical Performance Specifications

Table 1. TPS650061EVM Electrical and Performance Specifications

|                       | PARAMETER                    | NOTES AND CONDITIONS                                                                     |                           | MIN   | NOM  | MAX  | UNITS |

|-----------------------|------------------------------|------------------------------------------------------------------------------------------|---------------------------|-------|------|------|-------|

| INPUT CHAP            | RACTERISTICS                 |                                                                                          |                           | 1     |      |      |       |

| V <sub>IN</sub>       | Input Voltage                |                                                                                          |                           | 2.3   |      | 6.0  | V     |

| $V_{\text{IN\_UVLO}}$ | Immed IIV/I O                | VIN falling                                                                              |                           | 1.72  | 1.77 | 1.82 | V     |

| Hysteresis            | Input UVLO                   |                                                                                          |                           |       | 160  |      | mV    |

| OUTPUT CH             | IARACTERISTICS               |                                                                                          |                           | 1     |      |      |       |

| V <sub>ODC</sub>      | Output Voltage DCDC          | V <sub>IN</sub> = Nom, I <sub>OUT</sub> = Nom                                            |                           |       | 1.2  |      | V     |

|                       | Accuracy DCDC1               | VINDCDC 2.3V to 6V,<br>With 1% tolerance resistors                                       | PFM/PWM                   | -3.5% |      | 3.5% |       |

|                       |                              |                                                                                          | PWM                       |       | 3%   |      |       |

|                       | 0.41.01.0000                 | V <sub>IN</sub> DCDC = 2.3 V to 2.5 V                                                    |                           |       |      | 300  | mA    |

| OUTDC                 | Output Current DCDC          | $V_{IN}DCDC = 2.7 \text{ V to 6 V}$                                                      |                           |       | 1000 | 600  |       |

| VLDO1                 | Output Voltage LDO1          | V <sub>IN</sub> = Nom, I <sub>OUT</sub> = Nom                                            |                           |       | 3.3  |      | V     |

| I <sub>OUTLDO1</sub>  | Output Current LDO1          | Continuous output current                                                                |                           |       |      | 300  | mA    |

| VLDO2                 | Output Voltage LDO2          |                                                                                          |                           |       | 1.8  |      | V     |

| I <sub>OUTLDO2</sub>  | Output Current LDO2          | Continuous output current                                                                | Continuous output current |       |      | 300  | mA    |

|                       | Accuracy LDOs                | VINLDO = 1.6 V to 6 V, lout = VLDOx = 1.2 V, With 1% tolers                              |                           | -5.5% |      | 5.5% |       |

|                       |                              | VINLDO = 1.5 V to 6 V, lout = 1 mA to 300 mA, VLDOx = 1.2 V, With 1% tolerance resistors |                           | -5.5% |      | 5.5% |       |

|                       | Supply Voltage<br>Supervisor |                                                                                          |                           |       |      |      |       |

|                       | RST Trip Voltage             | R7 = 475k, R8 = 232k, JP9 connected between VIN and RSTSN_IN                             |                           |       | 1.8  |      | V     |

| t <sub>RST</sub>      | RST Recovery Time            | C5 = 0.1 µF                                                                              |                           |       | 30   |      | ms    |

|                       | HARACTERISTICS               | 1                                                                                        |                           | I .   |      |      |       |

| F <sub>sw</sub>       | Switching Frequency          |                                                                                          |                           | 1722  | 2250 | 2847 | kHz   |

Schematic www.ti.com

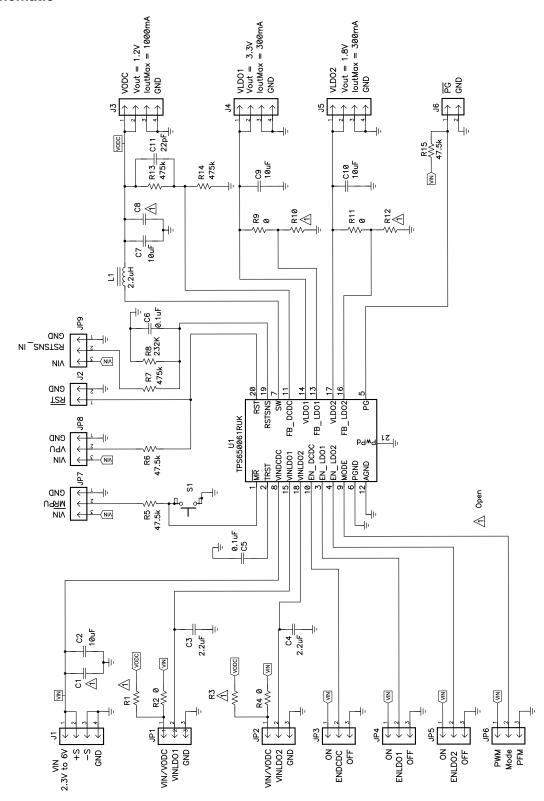

# 3 Schematic

For Reference Only, See Table 4: Bill of Materials for Specific Values

Figure 1. TPS650061EVM Schematic

# 4 Connector and Test Point Description

## 4.1 J1 – VIN/GND

The input power supply has to be connected to this header. The power supply must be connected between J1 pins 1 and 2 (positive connection) and J1 pins 3 and 4 (GND). The leads to the input supply should be twisted and kept as short as possible. The input voltage has to be between 2.3-V and 6-V.

#### 4.2 $J2 - \overline{RST}/GND$

J2 pin 1 is connected to the open drain output RST of the Supply Voltage Supervisor.

RST is pulled low if either manual reset input MR is low or the voltage on RSTSNS is below the threshold.

If manual reset  $\overline{MR}$  is released or the voltage on RSTSNS rises above the threshold voltage  $\overline{RST}$  goes high again after the reset recovery time  $t_{RST}$  exceeded.

## 4.3 J3 - VODC / GND

This header is the output of the step-down converter. This output voltage is externally adjustable for the TPS650061. The default setting on the EVM is 1.2V. VODC is capable of sourcing up to 1.0-A. A load can be connected between J3 pins 1 and 2 (positive connection) and J3 pins 3 and 4 (GND).

## 4.4 J4- VLDO1/GND

This header is the output of LDO1. This output voltage is internally fixed for the TPS650061 at 3.3-V. VLDO2 is capable of sourcing up to 300-mA. A load can be connected between J4 pins 1 and 2 (positive connection) and J4 pins 3 and 4 (GND).

# 4.5 J5 - VLDO2

This header is the output of LDO2. This output voltage is internally fixed for the TPS650061 at 1.8-V. VLDO2 is capable of sourcing up to 300-mA. A load can be connected between J5 pins 1 and 2 (positive connection) and J5 pins 3 and 4 (GND).

#### 4.6 J6 – PG/GND

J6 pin 1 is pulled to GND if the output voltages of the DCDC converter and both LDOs are > 90% of their set point and all enable pins are pulled high.

J6 pin 1 is pulled up to the selected pull-up voltage level if any of the output voltages VODC, VLDO1 or VLDO2 is < 90% of its set point or all enable pins are pulled low.

# 4.7 JP1 – VINLDO1

This header is the input supply for LDO1. Placing a shorting bar between VINLDO1 and VINDC/VODC supplies LDO1 from VIN with R2. It can be also supplied from the output of the converter VODC with R1 (not assembled). An external power supply can be connected between JP1 pin 2 (VINLDO1) and pin 3 (GND). Note that the resistors R1 and R2 should be removed when supplying the LDO from an external power supply.

# 4.8 JP2 – VINLDO2

This header is the input supply for LDO2. Placing a shorting bar between VINLDO2 and VINDC/VODC supplies LDO2 from VIN with R4. It can be also supplied from the output of the converter VODC with R3 (not assembled). An external power supply can be connected between JP2 pin 2 (VINLDO2) and pin 3 (GND). Note that the resistors R3 and R4 should be removed when supplying the LDO from an external power supply.

## 4.9 JP3 -ENDCDC

Placing a shorting bar between ENDCDC and ON ties the EN pin of the DCDC converter to VIN, thereby enabling the DCDC converter. Placing a shorting bar between ENDCDC and OFF ties the EN pin of the DCDC converter to GND, thereby disabling the DCDC converter.

#### 4.10 JP4 -ENLDO1

Placing a shorting bar between ENLDO1 and ON ties the EN pin of LDO1 to VIN, thereby enabling LDO1. Placing a shorting bar between ENLDO1 and OFF ties the EN pin of LDO1 to GND, thereby disabling LDO1.

## 4.11 JP5 – ENLDO2

Placing a shorting bar between ENLDO2 and ON ties the EN pin of LDO2 to VIN, thereby enabling LDO2. Placing a shorting bar between ENLDO2 and OFF ties the EN pin of LDO2 to GND, thereby disabling LDO2.

# 4.12 JP6 -MODE

JP6 selects the forced PWM or Power Save Mode (PSM) operation for the DCDC converter. Placing a shorting bar between MODE and PWM ties the MODE pin of TPS650061 to VIN, thereby selecting forced PWM operating mode for the DCDC converter. Placing a shorting bar between MODE and PFM ties the MODE pin of TPS650061 to GND, thereby selecting Power Save Mode operating mode for the DCDC converter at light-load conditions. If Power Save Mode is selected the DCDC converter will automatically switch to PWM mode at heavier load conditions.

## 4.13 JP7 – MRPU

JP7 selects the pull-up voltage for the Manual Reset input MRPU of the TPS650061. Placing a shorting bar between VIN and MRPU selects VIN as pull-up voltage. Any other voltage source can be used, by removing the shorting bar and connecting a power supply between MRPU (positive connection) and GND (negative connection). In the default setup VIN is used as pull-up voltage.

## 4.14 JP8 - VPU

JP8 selects the pull-up voltage used for the PG output.

Placing a shorting bar between VPU and VIN select VIN as pull-up voltage. Any other pull-up voltage can be used by removing the shorting bar and connecting a power supply between VPU and GND.

## 4.15 JP9 - RSTSNS IN

JP9 selects the voltage rail that is monitored by the Supply Voltage Supervisor (SVS). Placing a shorting bar between VIN and RSTSNS\_IN selects VIN as monitored rail. Any other voltage rail can be connected to the SVS input by removing the shorting bar and connecting the rail between RSTSNS IN and GND.

In default setup VIN is monitored by the SVS.

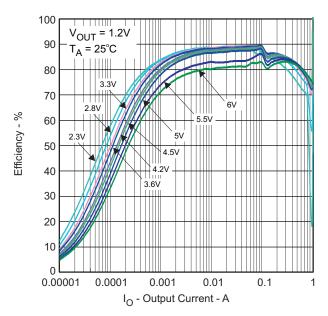

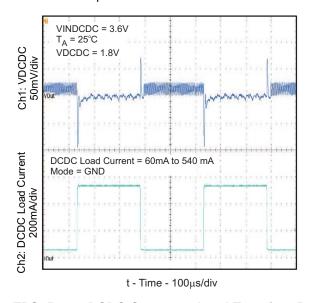

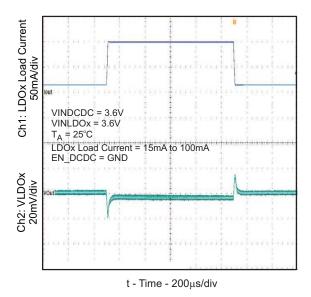

## 5 TPS650061 Typical Performance Data and Characteristic Curves

Figure 2 through Figure 9 present typical performance curves for the TPS650061. Since actual performance data can be affected by measurement techniques and environmental variables, these curves are presented for reference and may differ from actual field measurements.

# 5.1 Efficiency

Figure 2. TPS650061 Efficiency vs Load Current

# 5.2 Line and Load Regulation

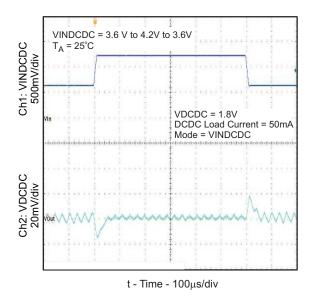

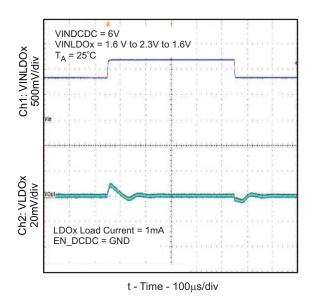

Figure 3 and Figure 4 show the load transient response of the DCDC converter and LDO, while Figure 5 and Figure 6 show the line transient response.

Figure 3. TPS650061 DCDC Converter Load Transient Response

Figure 4. TPS650061 LDOx Load Transient Response

Figure 5. TPS650061 DCDC Converter Line Transient Response

Figure 6. TPS650061 LDOx Line Transient Response

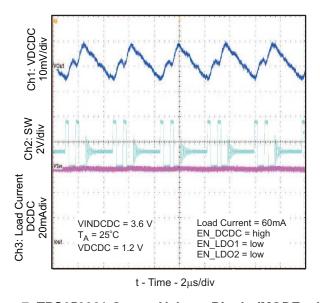

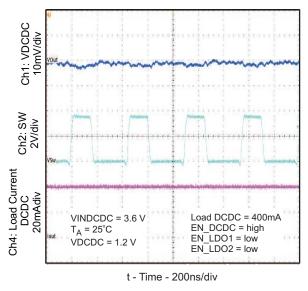

# 5.3 Output Voltage Ripple

Figure 7. TPS650061 Output Voltage Ripple (MODE = low)

Figure 8. TPS650061 Output Voltage Ripple (MODE = high)

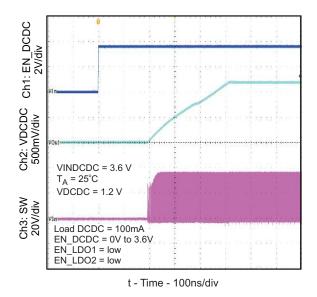

# 5.4 Startup Timing

Figure 9. TPS650061 DCDC Converter Startup Timing

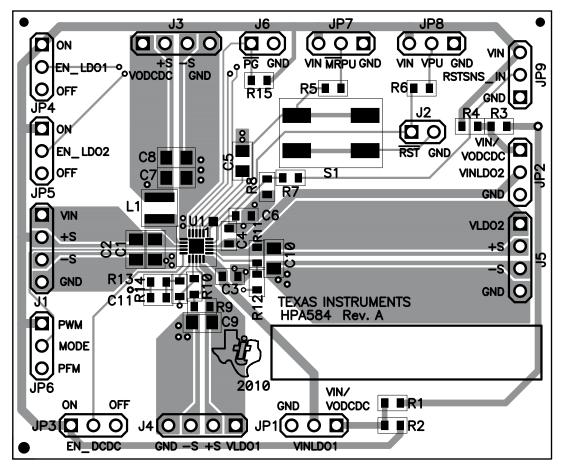

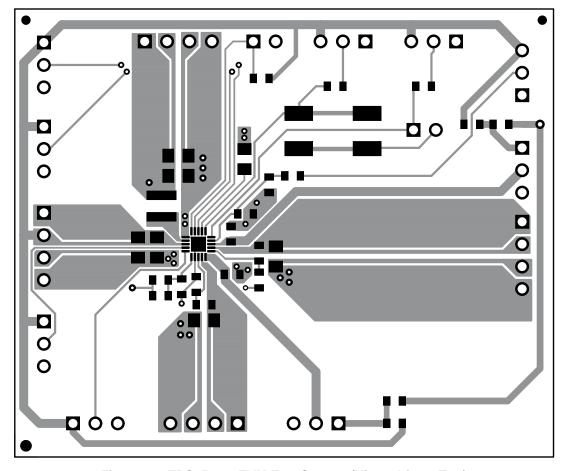

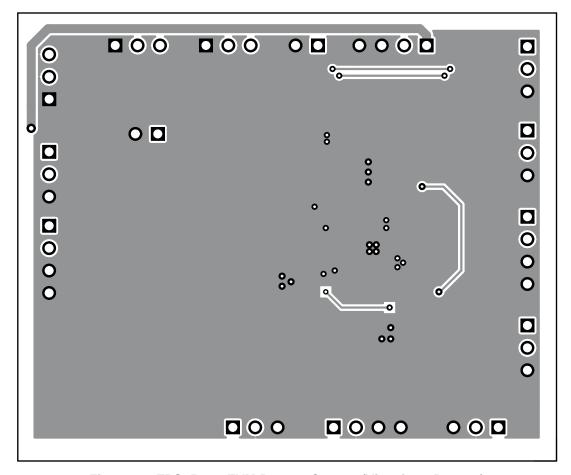

# 6 EVM Assembly Drawings and Layout

The following figures (Figure 10 through Figure 12) show the design of the TPS650061EVM printed circuit board. The EVM has been designed using a 2-Layer, 1oz copper-clad circuit board 2.4" x 2.0" (61.09mm x 50.80mm).

Figure 10. TPS650061EVM Component Placement (Viewed from Top)

Figure 11. TPS650061EVM Top Copper (Viewed from Top)

Figure 12. TPS650061EVM Bottom Copper (View from Bottom)

List of Materials www.ti.com

# 7 List of Materials

Table 2 lists the EVM components as configured according to the schematic shown in Figure 1.

# Table 2. TPS650061EVM Bill of Materials

| Count | RefDes              | Value            | Description                                             | Size               | Part Number        | MFR       |

|-------|---------------------|------------------|---------------------------------------------------------|--------------------|--------------------|-----------|

| 0     | C1, C8              | open             | Capacitor, Ceramic, 10V, X5R, 10%,                      | 0805               | Std                | Std       |

| 1     | C11                 | 22pF             | Capacitor, Ceramic, 50V, C0G, 5%                        | 0603               | Std                | Std       |

| 3     | C2, C7, C10         | 10μF             | Capacitor, Ceramic, 10V, X5R, 10%,                      | 0805               | GRM21BR61A106KE19L | muRata    |

| 2     | C3, C4              | 2.2µF            | Capacitor, Ceramic, 16V, X5R, 10%,                      | 0603               | GRM188R61C225KE15D | muRata    |

| 1     | C5                  | 0.1µF            | Capacitor, Ceramic, 50V, X7R, 10%,                      | 0805               | GRM21BR71H104KA01L | muRata    |

| 1     | C6                  | 0.1µF            | Capacitor, Ceramic, 25V, X7R, 10%,                      | 0603               | GRM188R71E104KA01D | muRata    |

| 1     | C9                  | 10μF             | Capacitor, Ceramic, 10V, X5R, 10%,                      | 0805               | GRM21BR61A106KE19L | muRata    |

| 4     | J1, J3, J4, J5      | PEC04SAAN        | Header, Male 4-pin, 100mil spacing                      | 0.100 inch x 4     | PEC04SAAN          | Sullins   |

| 2     | J2, J6              | PEC02SAAN        | Header, Male 2-pin, 100mil spacing                      | 0.100 inch x 2     | PEC02SAAN          | Sullins   |

| 9     | JP1 - JP9           | PEC03SAAN        | Header, Male 3-pin, 100mil spacing                      | 0.100 inch x 3     | PEC03SAAN          | Sullins   |

| 1     | L1                  | 2.2µH            | Inductor, SMT, 2.0A, 110milliohm                        | 0.118 x 0.118 inch | LPS3015-222ML      | Coilcraft |

| 0     | R1, R3, R10,<br>R12 | open             | Resistor, Chip, 1/16W, 1%                               | 0603               | Std                | Std       |

| 4     | R2, R4, R9,<br>R11  | 0                | Resistor, Chip, 1/16W, 1%                               | 0603               | Std                | Std       |

| 3     | R5, R6, R15         | 47.5k            | Resistor, Chip, 1/16W, 1%                               | 0603               | Std                | Std       |

| 1     | R7, R13, R14        | 475k             | Resistor, Chip, 1/16W, 1%                               | 0603               | Std                | Std       |

| 1     | R8                  | 232K             | Resistor, Chip, 1/16W, 1%                               | 0603               | Std                | Std       |

| 1     | S1                  | KT11P2JM         | Switch, SPST, PB Momentary, Sealed Tactile              | 0.245 X 0.251 inch | KT11P2JM           | C & K     |

| 1     | U1                  | TPS650061RU<br>K | IC, 2.25 MHz Step Down Converter with Dual LDOs and SVS | QFN                | TPS650061RUK       | TI        |

| 9     |                     |                  | Shunt, 100-mil, Black                                   | 0.100              | 929950-00          | 3M        |

| 1     |                     |                  | PCB, 2.0" x 2.4" x 0.062"                               |                    | HPA584             | Any       |

| 1     |                     |                  | Label                                                   | 1.25 x 0.25 inch   | THT-13-457-10      | Brady     |

Notes: 1. These assemblies are ESD sensitive, ESD precautions shall be observed.

<sup>2.</sup> These assemblies must be clean and free from flux and all contaminants. Use of no clean flux is not acceptable.

<sup>3.</sup> These assemblies must comply with workmanship standards IPC-A-610 Class 2.

Ref designators marked with an asterisk (\*\*\*) cannot be substituted.

All other components can be substituted with equivalent MFG's components.

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products                    |                        | Applications                 |                                   |

|-----------------------------|------------------------|------------------------------|-----------------------------------|

| Amplifiers                  | amplifier.ti.com       | Audio                        | www.ti.com/audio                  |

| Data Converters             | dataconverter.ti.com   | Automotive                   | www.ti.com/automotive             |

| DLP® Products               | www.dlp.com            | Communications and Telecom   | www.ti.com/communications         |

| DSP                         | <u>dsp.ti.com</u>      | Computers and<br>Peripherals | www.ti.com/computers              |

| Clocks and Timers           | www.ti.com/clocks      | Consumer Electronics         | www.ti.com/consumer-apps          |

| Interface                   | interface.ti.com       | Energy                       | www.ti.com/energy                 |

| Logic                       | logic.ti.com           | Industrial                   | www.ti.com/industrial             |

| Power Mgmt                  | power.ti.com           | Medical                      | www.ti.com/medical                |

| Microcontrollers            | microcontroller.ti.com | Security                     | www.ti.com/security               |

| RFID                        | www.ti-rfid.com        | Space, Avionics & Defense    | www.ti.com/space-avionics-defense |

| RF/IF and ZigBee® Solutions | www.ti.com/lprf        | Video and Imaging            | www.ti.com/video                  |

|                             |                        | Wireless                     | www.ti.com/wireless-apps          |