## ZL30264-ZL30267

# 2-APLL, 6- or 10-Output Any-to-Any Clock Multiplier and Frequency Synthesizer

Data Sheet

#### September 2020

#### **Features**

#### Four Flexible Input Clocks

- One crystal/CMOS input

- Two differential/CMOS inputs

- One single-ended/CMOS input

- Any input frequency from 9.72MHz to 1.25GHz (300MHz max for CMOS)

- Activity monitors, automatic or manual switching

- · Glitchless clock switching by pin or register

#### • 6 or 10 Any-Frequency, Any-Format Outputs

- Any output frequency from 1Hz to 1045MHz

- · 2 fractional-N APLLs with 0ppm error

- Each APLL has a fractional divider and an integer divider to make a total of four independent frequency families

- Output jitter from integer multiply and dividers as low as 0.17ps RMS (12kHz-20MHz)

- Output jitter from fractional dividers is typically

1ps RMS, many frequencies <0.5ps RMS</li>

- · Each output has an independent divider

- Each output configurable as LVDS, LVPECL, HCSL, 2xCMOS or HSTL

- In 2xCMOS mode, the P and N pins can be different frequencies (e.g. 125MHz and 25MHz)

- Multiple output supply voltage banks with CMOS output voltages from 1.5V to 3.3V

- Precise output alignment circuitry and peroutput phase adjustment

| Ordering Information                                                                                                                |                                                                                                       |                                                                                     |                                                                                       |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|--|--|--|

| ZL30264LDG1<br>ZL30264LDF1<br>ZL30265LDG1<br>ZL30265LDF1<br>ZL30266LDG1<br>ZL30266LDG1<br>ZL30267LDG1<br>ZL30267LDG1<br>ZL30267LDG1 | ext. EEPROM<br>ext. EEPROM<br>int. EEPROM<br>ext. EEPROM<br>ext. EEPROM<br>int. EEPROM<br>int. EEPROM | 6 Outputs 6 Outputs 6 Outputs 6 Outputs 10 Outputs 10 Outputs 10 Outputs 10 Outputs | Trays Tape and Reel Trays Tape and Reel Trays Tape and Reel Trays Tape and Reel Trays |  |  |  |

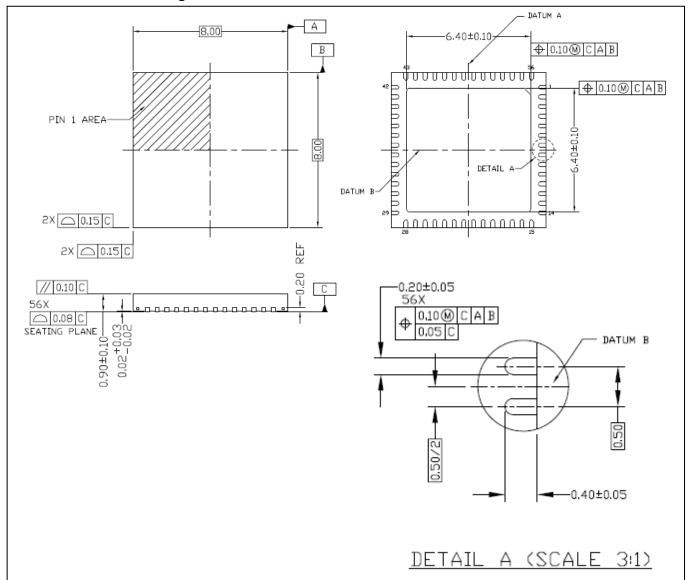

| Matte Tin Package size: 8 x 8 mm, 56 Pin QFN  -40°C to +85°C                                                                        |                                                                                                       |                                                                                     |                                                                                       |  |  |  |

Per-output enable/disable and glitchless start/stop (stop high or low)

#### General Features

- Automatic self-configuration at power-up from external (ZL30264 or 6) or internal (ZL30265 or 7) EEPROM; up to 8 configurations pin-selectable

- · External feedback for zero-delay applications

- Numerically controlled oscillator mode

- Spread-spectrum modulation mode

- Generates PCIe 1, 2, 3, 4 compliant clocks

- Easy-to-configure design requires no external VCXO or loop filter components

- SPI or I<sup>2</sup>C processor Interface

- Core supply voltage options: 2.5V only, 3.3V only, 1.8V+2.5V or 1.8V+3.3V

- Space-saving 8x8mm QFN56 (0.5mm pitch)

## **Applications**

Frequency conversion and frequency synthesis in a wide variety of equipment types

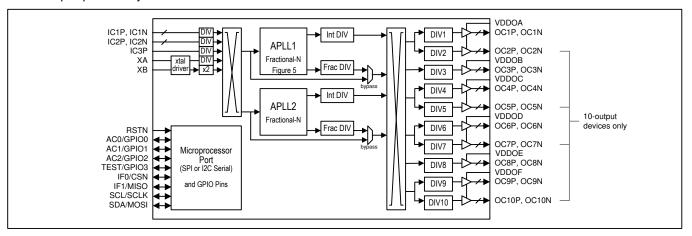

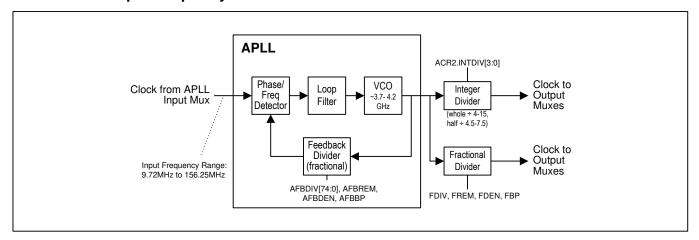

Figure 1 - Functional Block Diagram

## Table of Contents

| 1.         | APPLICATION EXAMPLE                                              | 5  |

|------------|------------------------------------------------------------------|----|

| 2.         | DETAILED FEATURES                                                | 5  |

| 2.1        | INPUT CLOCK FEATURES                                             | 5  |

| 2.2        | APLL FEATURES                                                    | _  |

| 2.3        | OUTPUT CLOCK FEATURES                                            |    |

| 2.4        | GENERAL FEATURES                                                 |    |

| 2.5        | EVALUATION SOFTWARE                                              |    |

|            |                                                                  |    |

| 3.         | PIN DIAGRAM                                                      |    |

| 4.         | PIN DESCRIPTIONS                                                 |    |

| 5.         | FUNCTIONAL DESCRIPTION                                           | 0  |

| 5.1        | DEVICE IDENTIFICATION                                            |    |

| 5.2        | PIN-CONTROLLED AUTOMATIC CONFIGURATION AT RESET                  | 0  |

|            | 2.1 ZL30264 and ZL30266—Internal ROM, External or No EEPROM      | 11 |

|            | .2.2 ZL30265 and ZL30267—Internal EEPROM                         | 11 |

| 5.3        |                                                                  |    |

|            | 3.1 External Oscillator                                          |    |

|            | 3.2 External Crystal and On-Chip Driver Circuit                  |    |

|            | 3.3 Clock Doublers                                               |    |

|            | 3.4 Ring Oscillator (for Auto-Configuration)                     | 14 |

| 5.4        |                                                                  |    |

| 5.5        | APLL CONFIGURATION                                               |    |

|            | 5.1 APLL Input Frequency                                         |    |

|            | 5.2 APLL Input Monitors                                          |    |

|            | 5.3 APLL Input Selection                                         |    |

|            | .5.4 APLL Output Frequency                                       |    |

|            | .5.5 Fractional Output Divider                                   |    |

| 5.         | 5.6 Numerically Controlled Oscillator (NCO) Mode                 |    |

|            | 5.5.6.1 Using the APLL's Feedback Divider                        |    |

| 5          | 5.7 Frequency Increment and Decrement                            |    |

|            | 5.8 Spread-Spectrum Modulation Mode                              |    |

| J.         | 5.5.8.1 Using the APLL's Feedback Divider                        |    |

|            | 5.5.8.2 Using the Fractional Output Divider                      |    |

| 5          | 5.9 APLL Phase Adjustment                                        |    |

| 5.6        |                                                                  |    |

| _          | .6.1 Output Enable, Signal Format, Voltage and Interfacing       |    |

|            | 6.2 Output Frequency Configuration                               |    |

|            | .6.3 Output Duty Cycle Adjustment                                |    |

|            | .6.4 Output Phase Adjustment                                     |    |

| <i>5</i> . | .6.5 Output-to-Output Phase Alignment                            |    |

|            | .6.6 Output-to-Input Phase Alignment                             | 23 |

|            | .6.7 Output Clock Start and Stop                                 |    |

| 5.7        |                                                                  |    |

|            | 7.1 SPI Slave                                                    |    |

|            | 7.2 SPI Master (ZL30264 and ZL30266 Only)                        |    |

|            | 7.3 PC Slave                                                     |    |

| 5.8        | INTERRUPT LOGIC                                                  |    |

| 5.9        | RESET LOGIC                                                      |    |

| <i>5</i> . | 9.1 Design Considerations for Using an External RC Reset Circuit | 30 |

| 5.  | 10     | POWER-SUPPLY CONSIDERATIONS                           | 30        |

|-----|--------|-------------------------------------------------------|-----------|

| 5.  | 11     | AUTO-CONFIGURATION FROM EEPROM OR ROM                 | 30        |

|     | 5.11.1 | Generating Device Configurations                      | 31        |

|     | 5.11.2 | P Direct EEPROM Write Mode (ZL30265 and ZL30267 Only) | 31        |

|     | 5.11.3 |                                                       |           |

| 5.  | 12     | CONFIGURATION SEQUENCE                                | 31        |

| 5.  | 13     | POWER SUPPLY DECOUPLING AND LAYOUT RECOMMENDATIONS    | 31        |

| 5.  | 14     | CHOOSING AMONG CORE POWER SUPPLY OPTIONS              | 31        |

| 6.  | RE     | GISTER DESCRIPTIONS                                   | 32        |

| 6.  | 1 R    | EGISTER TYPES                                         | 32        |

|     | 6.1.1  | Status Bits                                           |           |

|     | 6.1.2  | Configuration Fields                                  | 32        |

|     | 6.1.3  | Multiregister Fields                                  |           |

|     | 6.1.4  | Bank-Switched Registers (ZL30265 and ZL30267 Only)    |           |

| 6.  | 2 R    | EGISTER MAP                                           | 33        |

| 6.  | 3 R    | EGISTER DEFINITIONS                                   | 37        |

|     | 6.3.1  | Global Configuration Registers                        | 37        |

|     | 6.3.2  | Status Registers                                      |           |

|     | 6.3.3  | APLL Configuration Registers                          |           |

|     | 6.3.4  | Output Clock Configuration Registers                  |           |

|     | 6.3.5  | Input Clock Configuration Registers                   | <i>75</i> |

| 7.  | ELE    | ECTRICAL CHARACTERISTICS                              | 77        |

| 8.  | PA     | CKAGE AND THERMAL INFORMATION                         | 89        |

| 9.  | ME     | CHANICAL DRAWING                                      | 90        |

| 10. | AC     | RONYMS AND ABBREVIATIONS                              | 91        |

| 11  | DA.    | TA SHEET REVISION HISTORY                             | 91        |

|     |        |                                                       |           |

|                                                                                                                                         | List of Figures |

|-----------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| Figure 1 - Functional Block Diagram                                                                                                     | 1               |

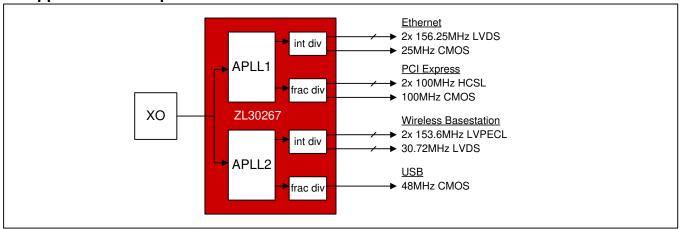

| Figure 2 - Application Example: ZL30267 Ethernet, PCIe, Wireless and USB Clocks Simultane                                               | ously5          |

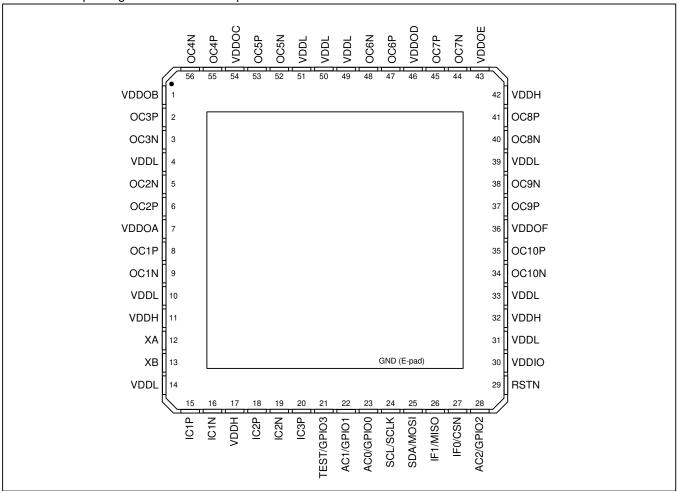

| Figure 3 - Pin Diagram                                                                                                                  |                 |

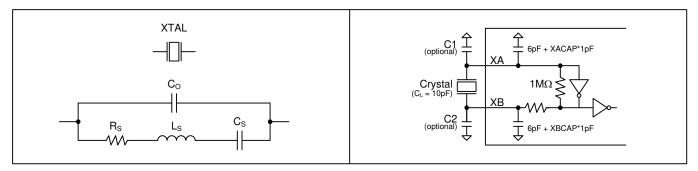

| Figure 4 - Crystal Equivalent Circuit / Recommended Crystal Circuit                                                                     |                 |

| Figure 5 - APLL Block Diagram                                                                                                           |                 |

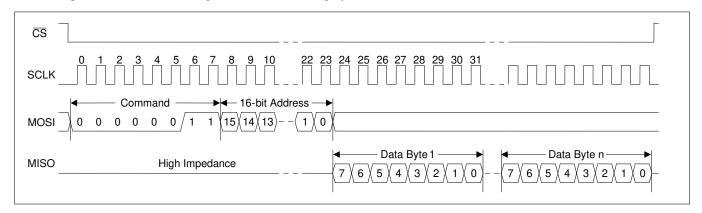

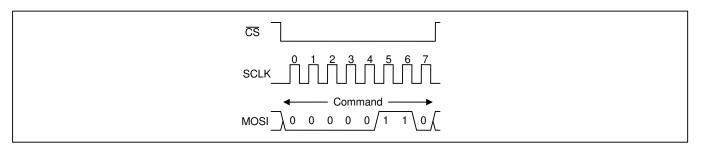

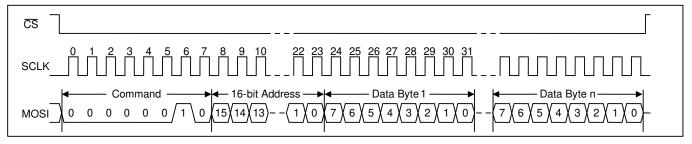

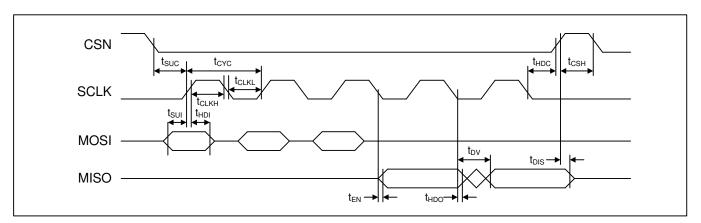

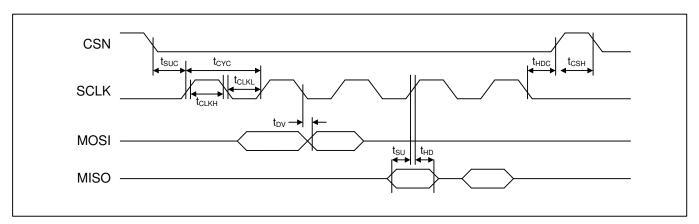

| Figure 6 - SPI Read Transaction Functional Timing                                                                                       |                 |

| Figure 7 - SPI Write Enable Transaction Functional Timing (ZL30265 and ZL30267 Only) Figure 8 - SPI Write Transaction Functional Timing |                 |

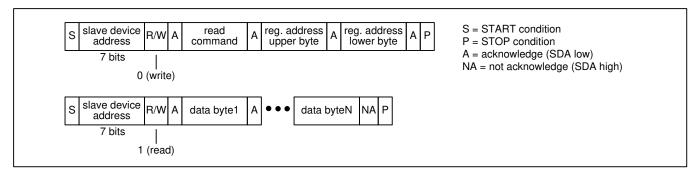

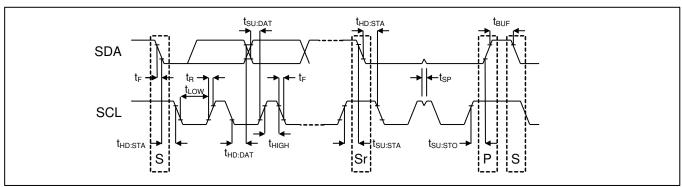

| Figure 9 - I <sup>2</sup> C Read Transaction Functional Timing                                                                          |                 |

| Figure 10 - I <sup>2</sup> C Register Write Transaction Functional Timing                                                               |                 |

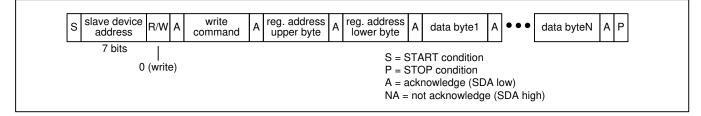

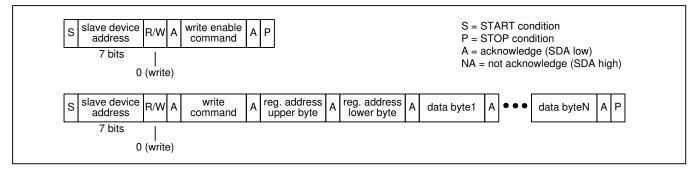

| Figure 11 - I <sup>2</sup> C EEPROM Write Transaction Functional Timing (ZL30265 and ZL30267 Only)                                      |                 |

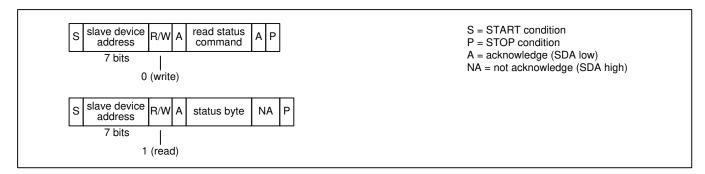

| Figure 12 - I <sup>2</sup> C EEPROM Read Status Transaction Functional Timing (ZL30265 and ZL30267                                      | Only)28         |

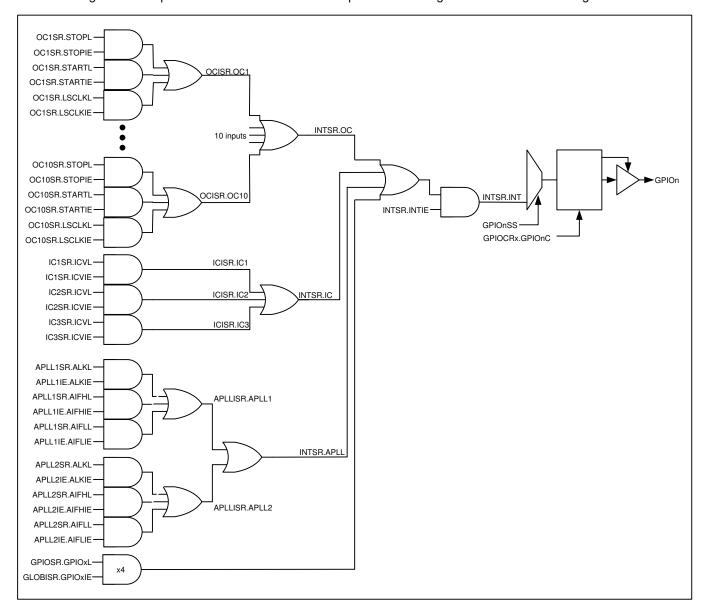

| Figure 13 - Interrupt Structure                                                                                                         |                 |

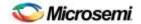

| Figure 14 - Electrical Characteristics: Clock Inputs                                                                                    | 79              |

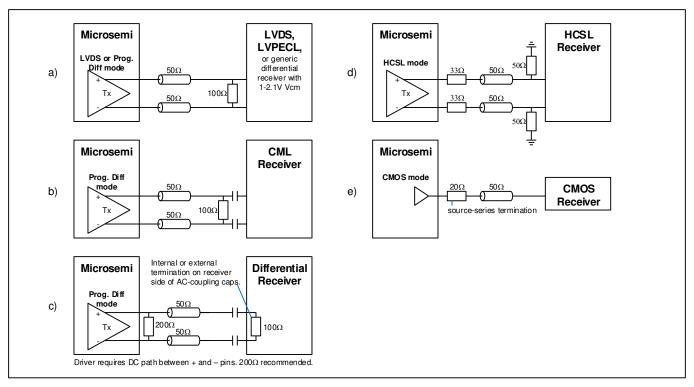

| Figure 15 - Example External Components for Differential Input Signals                                                                  |                 |

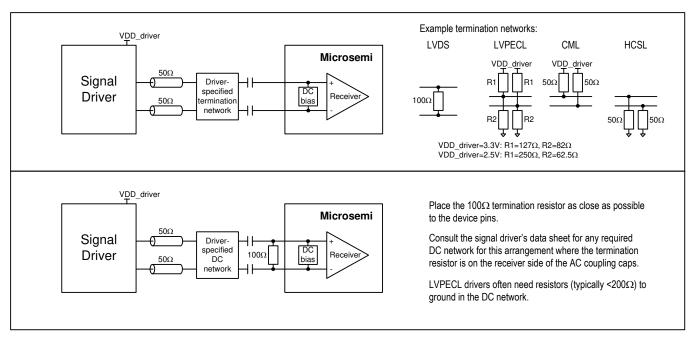

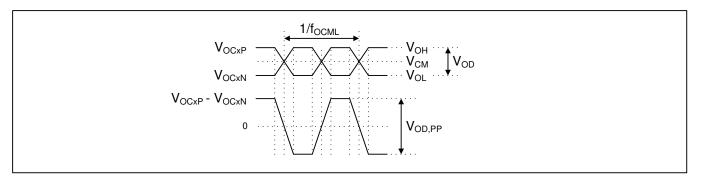

| Figure 16 - Electrical Characteristics: Differential Clock Outputs                                                                      |                 |

| Figure 17 - Example External Components for Differential Output Signals                                                                 |                 |

| Figure 18 - SPI Slave Interface Timing                                                                                                  |                 |

| Figure 19 - SPI Master Interface Timing                                                                                                 |                 |

| Figure 20 - I <sup>2</sup> C Slave Interface Timing                                                                                     | 88              |

| Table 1 - Pin Descriptions                                                                                                              | List of Tables  |

| Table 2 - Crystal Selection Parameters                                                                                                  |                 |

| Table 3 - SPI Commands                                                                                                                  |                 |

| Table 4 - Register Map                                                                                                                  | 33              |

| Table 5 - Recommended DC Operating Conditions                                                                                           |                 |

| Table 6 - Electrical Characteristics: Supply Currents                                                                                   | 77              |

| Table 7 - Electrical Characteristics: Non-Clock CMOS Pins                                                                               |                 |

| Table 8 - Electrical Characteristics: XA Clock Input                                                                                    |                 |

| Table 9 - Electrical Characteristics: Clock Inputs, ICxP/N                                                                              |                 |

| Table 10 - Electrical Characteristics: LVDS Clock Outputs                                                                               |                 |

| Table 12 - Electrical Characteristics: EVY EGE Glock Outputs                                                                            |                 |

| Table 13 - Electrical Characteristics: CMOS and HSTL (Class I) Clock Outputs                                                            |                 |

| Table 14 - Electrical Characteristics: APLL Frequencies                                                                                 | 82              |

| Table 15 - Electrical Characteristics: Jitter and Skew Specifications                                                                   | 82              |

| Table 16 - Electrical Characteristics: Typical Output Phase Jitter from the APLL Integer Divider                                        |                 |

| Table 17 - Electrical Characteristics: Clock Buffer (APLL Bypass Path)                                                                  | 84              |

| Table 18 - Electrical Characteristics: Typical Input-to-Output Clock Delay Through APLL                                                 |                 |

| Table 19 - Electrical Characteristics: SPI Slave Interface Timing, Device Registers                                                     |                 |

| Table 20 - Electrical Characteristics: SPI Slave Interface Timing, Internal EEPROM                                                      |                 |

| Table 21 - Electrical Characteristics: SPI Master Interface Timing (ZL30264 and ZL30266 Only                                            | <i>ı</i> ) 87   |

Table 22 - Electrical Characteristics: I²C Slave Interface Timing88Table 23 - 8x8mm QFN Package Thermal Properties89Table 24 - Number of OCx Outputs Available, No Airflow, 3.3V-Only Operation89

#### 1. Application Example

Figure 2 - Application Example: ZL30267 Ethernet, PCle, Wireless and USB Clocks Simultaneously

#### 2. Detailed Features

#### 2.1 Input Clock Features

- Four input clocks: one crystal/CMOS, two differential/CMOS, one single-ended/CMOS

- Input clocks can be any frequency from 9.72MHz to 1250MHz (differential) or 300MHz (single-ended)

- Supported telecom frequencies include PDH, SDH, Synchronous Ethernet, OTN, wireless

- Activity monitor and glitchless input switching

#### 2.2 APLL Features

- Two APLLs with very high-resolution fractional (i.e. non-integer) frequency multiplication

- Any-to-any frequency conversion with 0ppm error

- Two output dividers per APLL: one integer divider (4 to 15 plus half divides 4.5 to 7.5) and one fractional divider to make a total of four output frequency families

- Easy-to-configure, completely encapsulated design requires no external VCXO or loop filter

- Bypass mode supports system testing

#### 2.3 Output Clock Features

- Six (ZL30264 or ZL30265) or ten (ZL30266 or ZL30267) low-jitter output clocks

- Each output can be one differential output or two CMOS outputs

- Output clocks can be any frequency from 1Hz to 1045MHz (250MHz max for HCSL, CMOS and HSTL)

- Output jitter from integer multiply and integer dividers as low as 0.17ps RMS (12kHz to 20MHz)

- Output jitter from fractional dividers is typically <1ps RMS, many frequencies <0.5ps RMS (12kHz to 20MHz)

- In CMOS mode, the OCxP and OCxN pins can be different divisors (Example 1: OC3P 125MHz, OC3N 25MHz; Example 2: OC3P 25MHz, OC3N 1Hz/1PPS)

- Outputs directly interface (DC coupled) with LVDS, LVPECL, HSTL, HCSL and CMOS components

- Supported telecom frequencies include PDH, SDH, Synchronous Ethernet, OTN

- Can produce clock frequencies for microprocessors, ASICs, FPGAs and other components

- Can produce PCle-compliant clocks (PCle 1, 2, 3 and 4)

- Sophisticated output-to-output phase alignment

- Per-output phase adjustment

- Per-output enable/disable

- Per-output glitchless start/stop (stop high or low)

## 2.4 General Features

- SPI or I<sup>2</sup>C serial microprocessor interface

- Automatic self-configuration at power-up; pin control to specify one of 8 stored configurations

ZL30264 and ZL30266: preset configurations in ROM or user configurations in external EEPROM

ZL30265 and ZL30267: user configurations in internal EEPROM

- Numerically controlled oscillator (NCO) mode allows system software to steer DPLL frequency with resolution better than 0.01ppb (1ppt can be achieved with fractional output divider value >14.56)

- Spread-spectrum modulation mode (meets PCI Express requirements)

- · Zero-delay buffer configuration using an external feedback path

- Four general-purpose I/O pins each with many possible status and control options

- Reference can be fundamental-mode crystal, low-cost XO or clock signal from elsewhere in the system

#### 2.5 Evaluation Software

- Simple, intuitive Windows-based graphical user interface

- Supports all device features and register fields

- Makes lab evaluation of the ZL30264/5/6/7 quick and easy

- Generates configuration scripts to be stored in external (ZL30264/6) or internal (ZL30265/7) EEPROM

- Generates full or partial configuration scripts to be run on a system processor

- · Works with or without an evaluation board

## 3. Pin Diagram

The device is packaged in a 8x8mm 56-pin QFN.

Figure 3 - Pin Diagram

## 4. Pin Descriptions

All device inputs and outputs are LVCMOS unless described otherwise. The Type column uses the following symbols: I – input, O – output, A – analog, P – power supply pin. All GPIO and SPI/I $^2$ C interface pins have Schmitt-trigger inputs and have output drivers that can be disabled (high impedance).

Table 1 - Pin Descriptions

| Table 1 -                                                                                  | able 1 - Pin Descriptions                                                                                                                  |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|--------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Pin#                                                                                       | Name                                                                                                                                       | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| 15, 16<br>18, 19<br>20                                                                     | IC1P, IC1N<br>IC2P, IC2N<br>IC3P                                                                                                           |      | <ul> <li>Input Clock Pins</li> <li>Differential or Single-ended signal format. Programmable frequency.</li> <li>Differential: See Table 9 for electrical specifications, and see Figure 15 for recommended external circuitry for interfacing these differential inputs to LVDS, LVPECL, CML or HSCL output pins on neighboring devices.</li> <li>Single-ended: For input signal amplitude &gt;2.5V, connect the signal directly to ICxP pin. For input signal amplitude ≤2.5V, AC-coupling the signal to ICxP is recommended. Connect the N pin to a capacitor (0.1μF or 0.01μF) to VSS. As shown in Figure 15, the ICxP and ICxN pins are internally biased to approximately 1.3V. Treat the ICxN pin as a sensitive node; minimize stubs; do not connect to anything else including other ICxN pins.</li> <li>Unused: Set ICEN.ICxEN=0. The ICxP and ICxN pins can be left floating.</li> <li>Note that the IC3N pin is not bonded out. A differential signal can be connected to IC3P by AC-coupling the POS trace to IC3P and terminating</li> </ul> |  |

| 12<br>13                                                                                   | XA<br>XB                                                                                                                                   | A/I  | the signal on the driver side of the coupling cap.  Crystal or Input Clock Pins  Crystal: MCR2.XAB=01. An on-chip crystal driver circuit is designed to work with an external crystal connected to the XA and XB pins. See section 5.3.2 for crystal characteristics and recommended external components.  Input Clock: MCR2.XAB=10. An external local oscillator or clock signal can be connected to the XA pin. The XB pin must be left unconnected. The signal on XA can be as large as 3.3V even when VDDH is only 2.5V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| 8, 9<br>6, 5<br>2, 3<br>55, 56<br>53, 52<br>47, 48<br>45, 44<br>41, 40<br>37, 38<br>35, 34 | OC1P, OC1N<br>OC2P, OC2N<br>OC3P, OC3N<br>OC4P, OC4N<br>OC5P, OC5N<br>OC6P, OC6N<br>OC7P, OC7N<br>OC8P, OC8N<br>OC9P, OC9N<br>OC10P, OC10N | 0    | Output Clock Pins LVDS, programmable differential (which includes LVPECL), HCSL, HSTL of 1 or 2 CMOS. Programmable frequency. Programmable VCM and VOD in programmable differential mode. Programmable drive strength in CMOS and HSTL modes. See Figure 17 for example external interface circuitry. See Table 10, Table 11 and Table 12 for electrical specifications for LVDS, LVPECL and HCSL, respectively.  See Table 13 for electrical specifications for interfacing to CMOS and HSTL inputs on neighboring devices.  Outputs OC2, OC5, OC7 and OC10 are not present on 6-output products.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| 29                                                                                         | RSTN                                                                                                                                       | I    | Reset (Active Low) When this global asynchronous reset is pulled low, all internal circuitry is reset to default values. The device is held in reset as long as RSTN is low. Minimum low time is 1µs. See section 5.9.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| 23<br>22<br>28                                                                             | AC0/GPIO0<br>AC1/GPIO1<br>AC2/GPIO2                                                                                                        | I/O  | Auto-Configure [2:0] / General Purpose I/O 0, 1 and 2  Auto Configure: On the rising edge of RSTN these pins behave as AC[2:0] and specify one of the configurations stored in ROM or EEPROM. See section 5.2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| Pin # | Name           | Туре         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |                                                                                                                                                         |

|-------|----------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|---------------------------------------------------------------------------------------------------------------------------------------------------------|

|       |                |              | General-Purpose I/O: After reset these pins are GPIO0, GPIO1 and GPIO2. GPIOCR1 and GPIOCR2.GPIO2C configure these pins. Their states are indicated in GPIOSR which has both real-time and latched status bits.                                                                                                                                                                                                                                                         |  |                                                                                                                                                         |

|       |                |              | Note that when the power supply arrangement for the device has VDDL=1.8V, during the interval between VDDH ramping and VDDL ramping these pins can briefly behave as an output driving high.                                                                                                                                                                                                                                                                            |  |                                                                                                                                                         |

|       |                |              | Factory Test / General Purpose I/O 3                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |                                                                                                                                                         |

|       |                |              | Factory Test: On the rising edge of RSTN the pin behaves as TEST. Factory test mode is enabled when TEST is high. Typically TEST should be low on the rising edge of RSTN, but see section 5.2 for some options where TEST can be high on the rising edge of RSTN.                                                                                                                                                                                                      |  |                                                                                                                                                         |

| 21    | TEST/GPIO3     | I/O          | General-Purpose I/O: After reset this pin is GPIO3. GPIOCR2.GPIO3C configures the pin. It state is indicated in GPIOSR which has both real-time and latched status bits.                                                                                                                                                                                                                                                                                                |  |                                                                                                                                                         |

|       |                |              | Note that when the power supply arrangement for the device has VDDL=1.8V, during the interval between VDDH ramping and VDDL ramping this pin can briefly behave as an output driving high.                                                                                                                                                                                                                                                                              |  |                                                                                                                                                         |

|       |                |              | Interface Mode 0 / SPI Chip Select (Active Low)                                                                                                                                                                                                                                                                                                                                                                                                                         |  |                                                                                                                                                         |

|       |                |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  | Interface Mode: On the rising edge of RSTN the pin behaves as IF0 and, together with IF1, specifies the interface mode for the device. See section 5.2. |

| 27    | 27 IF0/CSN I/O |              | SPI Chip Select: After reset this pin is CSN. When the device is configured as a SPI slave, an external SPI master must assert (low) CSN to access device registers. When the device is configured as a SPI master (ZL30264, ZL30266 only), the device asserts CSN to access an external SPI EEPROM during auto-configuration and then changes CSN to an input during normal operation. CSN should not be allowed to float.  Interface Mode 1 / SPI Master-In-Slave-Out |  |                                                                                                                                                         |

|       |                |              | Interface Mode: On the rising edge of RSTN the pin behaves as IF1 and,                                                                                                                                                                                                                                                                                                                                                                                                  |  |                                                                                                                                                         |

|       |                |              | together with IF0, specifies the interface mode for the device. See section 5.2.                                                                                                                                                                                                                                                                                                                                                                                        |  |                                                                                                                                                         |

| 26    | 26 IF1/MISO I/ |              | SPI MISO: After reset this pin is MISO. When the device is configured as a SPI slave, the device outputs data to an external SPI master on MISO during SPI read transactions. When the device is configured as a SPI master (ZL30264, ZL30266 only), the device receives data on MISO from an external SPI EEPROM during auto-configuration.                                                                                                                            |  |                                                                                                                                                         |

|       |                |              | I <sup>2</sup> C Clock / SPI Clock                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |                                                                                                                                                         |

| 24    | SCL/SCLK       | I/O          | $\it PC Clock:$ When the device is configured as an $\it I^2C$ slave, an external $\it I^2C$ master must provide the $\it I^2C$ clock signal on the SCL pin. In $\it I^2C$ mode this pin should be externally pulled high by a $\it 1k\Omega$ to $\it 5k\Omega$ resistor.                                                                                                                                                                                               |  |                                                                                                                                                         |

| 24    |                | SGL/SGLK I/O | SPI Clock: When the device is configured as a SPI slave, an external SPI master must provide the SPI clock signal on SCLK. When the device is configured as a SPI master (ZL30264, ZL30266 only), the device drives SCLK as an output to clock accesses to an external SPI EEPROM during auto-configuration.                                                                                                                                                            |  |                                                                                                                                                         |

| 25    | SDA/MOSI       | I/O          | I <sup>2</sup> C Data / SPI Master-Out-Slave-In                                                                                                                                                                                                                                                                                                                                                                                                                         |  |                                                                                                                                                         |

|       |                |              | PC Data: When the device is configured as an I2C slave, SDA is the                                                                                                                                                                                                                                                                                                                                                                                                      |  |                                                                                                                                                         |

| Pin#                                      | Name  | Туре | Description                                                                                                                                                                                                                                                                                                                |  |

|-------------------------------------------|-------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                           |       |      | bidirectional data line between the device and an external I <sup>2</sup> C master. In I <sup>2</sup> C mode this pin should be externally pulled high by a $1 \text{k}\Omega$ to $5 \text{k}\Omega$ resistor.                                                                                                             |  |

|                                           |       |      | SPI MOSI: When the device is configured as a SPI slave, an external SPI master sends commands, addresses and data to the device on MOSI. When the device is configured as a SPI master (ZL30264, ZL30266 only), the device sends commands, addresses and data on MOSI to an external SPI EEPROM during auto-configuration. |  |

| 11,17,<br>32,42                           | VDDH  | Р    | <b>Higher Core Power Supply.</b> 2.5V or 3.3V $\pm$ 5%. When VDDH=3.3V the device has additional internal power supply regulators enabled.                                                                                                                                                                                 |  |

| 4,10,<br>14,31,<br>33,39,<br>49,50,<br>51 | VDDL  | Р    | <b>Lower Core Power Supply.</b> 1.8V ±5% or same voltage as VDDH.                                                                                                                                                                                                                                                          |  |

| 30                                        | VDDIO | Р    | Digital Power Supply for Non-Clock I/O Pins. 1.8V to VDDH.                                                                                                                                                                                                                                                                 |  |

| 7                                         | VDDOA | Р    | Power Supply for OC1P/N and OC2P/N. 1.5V to VDDH.                                                                                                                                                                                                                                                                          |  |

| 1                                         | VDDOB | Р    | Power Supply for OC3P/N. 1.5V to VDDH.                                                                                                                                                                                                                                                                                     |  |

| 54                                        | VDDOC | Р    | Power Supply for OC4P/N and OC5P/N. 1.5V to VDDH.                                                                                                                                                                                                                                                                          |  |

| 46                                        | VDDOD | Р    | Power Supply for OC6P/N and OC7P/N. 1.5V to VDDH.                                                                                                                                                                                                                                                                          |  |

| 43                                        | VDDOE | Р    | Power Supply for OC8P/N. 1.5V to VDDH.                                                                                                                                                                                                                                                                                     |  |

| 36                                        | VDDOF | Р    | Power Supply for OC9P/N and OC10P/N. 1.5V to VDDH.                                                                                                                                                                                                                                                                         |  |

| E-pad                                     | VSS   | Р    | Ground. 0 Volts.                                                                                                                                                                                                                                                                                                           |  |

**Important Note**: The voltages on VDDL, VDDIO, and all VDDOx pins must not exceed VDDH. Not complying with this requirement may damage the device.

## 5. Functional Description

#### 5.1 Device Identification

The 12-bit read-only ID field and the 4-bit revision field are found in the ID1 and ID2 registers. Contact the factory to interpret the revision value and determine the latest revision.

#### 5.2 Pin-Controlled Automatic Configuration at Reset

The device configuration is determined at reset (i.e. on the rising edge of RSTN) by the signal levels on these device pins: TEST/GPIO3, AC2/GPIO2, AC1/GPIO1, AC0/GPIO0, IF1/MISO and IF0/CSN. For these pins, the first name (TEST, AC2, AC1, AC0, IF1, IF0) indicates their function when they are sampled by the rising edge of the RSTN pin. The second name refers to their function after reset. The values of these pins are latched into the CFGSR register when RSTN goes high. To ensure the device properly samples the reset values of these pins, the following guidelines should be followed:

- 1. Any pullup or pulldown resistors used to set the value of these pins at reset should be  $1k\Omega$ .

- 2. RSTN must be asserted at least as long as specified in section 5.9.

The hardware configuration pins are grouped into three sets:

- 1. TEST Manufacturing test mode

- 2. IF[1:0] Microprocessor interface mode and I<sup>2</sup>C address

- 3. AC[2:0] Auto-config configuration number (0 to 7)

The TEST pin selects manufacturing test modes when TEST=1 (the AC[2:0] pins specify the test mode). For ZL30265 and ZL30267 (devices with internal EEPROM), TEST=1, AC[2:0]=000, IF[1:0]=11 configures the part so that production SPI EEPROM programmers can program the internal EEPROM (see section 5.11.2). TEST=1 and

AC[2:0]=011 causes the part to start normally except it does not auto-configure from EEPROM or ROM. For more information about auto-configuration from EEPROM or ROM see section 5.11.

For all of these pins Microsemi recommends that board designs include component sites for both pullup and pulldown resistors (only one or the other populated per pin).

#### 5.2.1 ZL30264 and ZL30266—Internal ROM, External or No EEPROM

For these part numbers the IF[1:0] pins specify the processor interface mode, the I<sup>2</sup>C slave address and whether the device should auto-configure from internal ROM or external EEPROM. The AC[2:0] pins specify which device configuration in the ROM or EEPROM to execute after reset. Descriptions of the standard-product ROM configurations are available from Microsemi.

| IF1 | IF0 | Processor Interface                                 | Configuration Memory to Use |

|-----|-----|-----------------------------------------------------|-----------------------------|

| 0   | 0   | I <sup>2</sup> C, slave address 11101 00            | Internal ROM                |

| 0   | 1   | I <sup>2</sup> C, slave address 11101 01            | Internal ROM                |

| 1   | 0   | SPI Slave                                           | Internal ROM                |

| 1   | 1   | SPI Master during auto-configuration then SPI Slave | External SPI EEPROM         |

To configure the device as specified in the first three rows above but *without* auto-configuring from internal ROM, wire devices pins as follows: TEST=1 and AC[2:0]=011, as described in section 5.2.

| AC2 | AC1 | AC0 | Auto Configuration |

|-----|-----|-----|--------------------|

| 0   | 0   | 0   | Configuration 0    |

| 0   | 0   | 1   | Configuration 1    |

| 0   | 1   | 0   | Configuration 2    |

| 0   | 1   | 1   | Configuration 3    |

| 1   | 0   | 0   | Configuration 4    |

| 1   | 0   | 1   | Configuration 5    |

| 1   | 1   | 0   | Configuration 6    |

| 1   | 1   | 1   | Configuration 7    |

Notes about the device auto-configuring from external EEPROM:

- 1. The device's CSN pin should have a pull-up resistor to VDD to ensure its processor interface is inactive after auto-configuration is complete. The SCLK, MISO and MOSI pins should also have pull-up resistors to VDD to keep them from floating.

- 2. If a processor or similar device will access device registers after the device has auto-configured from external EEPROM, the SPI SCLK, MOSI and MISO wires can be connected directly to the processor, the device and the external EEPROM. The processor and device CSN pins can be wired together also. The EEPROM CSN signal must be controlled by the device's CSN pin during device auto-configuration and then held inactive when the processor accesses device registers.

- 3. The bits of the I<sup>2</sup>C address are as shown above by default but can be changed in the I<sup>2</sup>CA register.

#### 5.2.2 ZL30265 and ZL30267—Internal EEPROM

For these part numbers the IF[1:0] pins specify the processor interface mode and the I<sup>2</sup>C slave address. The AC[2:0] pins specify which device configuration in the EEPROM to execute after reset.

| IF1 | IF0 | Processor Interface                      |  |

|-----|-----|------------------------------------------|--|

| 0   | 0   | I <sup>2</sup> C, slave address 11101 00 |  |

| 0   | 1   | I <sup>2</sup> C, slave address 11101 01 |  |

| 1   | 0   | I <sup>2</sup> C, slave address 11101 10 |  |

| 1   | 1   | SPI Slave                                |  |

| AC2 | AC1 | AC0 | Auto Configuration |

|-----|-----|-----|--------------------|

| 0   | 0   | 0   | Configuration 0    |

| 0   | 0   | 1   | Configuration 1    |

| AC2 | AC1 | AC0 | Auto Configuration |

|-----|-----|-----|--------------------|

| 0   | 1   | 0   | Configuration 2    |

| 0   | 1   | 1   | Configuration 3    |

| 1   | 0   | 0   | Configuration 4    |

| 1   | 0   | 1   | Configuration 5    |

| 1   | 1   | 0   | Configuration 6    |

| 1   | 1   | 1   | Configuration 7    |

Note: the bits of the I<sup>2</sup>C address are as shown above by default but can be changed in the I<sup>2</sup>CA register. A device's I<sup>2</sup>C slave address can be set to any value during auto-configuration at power-up by writing the I<sup>2</sup>CA register as part of the configuration script.

#### 5.3 Local Oscillator or Crystal

Section 5.3.1 describes how to connect an external oscillator and the required characteristics of the oscillator. Section 5.3.2 describes how to connect an external crystal to the on-chip crystal driver circuit and the required characteristics of the crystal. The device does not require an external oscillator or crystal for operation.

#### 5.3.1 External Oscillator

A signal from an external oscillator can be connected to the XA pin (XB must be left unconnected).

Table 8 specifies the range of possible frequencies for the XA input. To minimize jitter, the signal must be properly terminated and must have very short trace length. A poorly terminated single-ended signal can greatly increase output jitter, and long single-ended trace lengths are more susceptible to noise. When MCR2.XAB=10, XA is enabled as a single-ended input.

While the stability of the external oscillator can be important, its absolute frequency accuracy is less important because any known frequency inaccuracy of the oscillator can be compensated by adjusting the APLL's fractional feedback divider value (AFBDIV) by ppb or ppm.

The jitter on output clock signals depends on the phase noise and frequency of the external oscillator. For the device to operate with the lowest possible output jitter, the external oscillator should have the following characteristics:

- Phase Jitter: less than 0.1ps RMS over the 12kHz to 5MHz integration band

- Frequency: The higher the better, all else being equal

#### 5.3.2 External Crystal and On-Chip Driver Circuit

The on-chip crystal driver circuit is designed to work with a <u>fundamental mode, AT-cut</u> crystal resonator. See <u>Table 2</u> for recommended crystal specifications. To enable the crystal driver, set MCR2.XAB=01.

Figure 4 - Crystal Equivalent Circuit / Recommended Crystal Circuit

See Figure 4 for the crystal equivalent circuit and the recommended external component connections. The driver circuit design includes configurable internal load capacitors. For a 10pF crystal the total capacitance on each of XA and XB should be 2 x 10pF = 20pF. To achieve these loads without external capacitors, register field XACR3.XACAP should be set to 20pF minus actual XA external board trace capacitance minus XA's minimum

internal capacitance of 6pF. For example, if external trace capacitance is 2pF then XACAP should be set to 20pF – 2pF – 6pF = 12pF. Register field XACR3.XBCAP should be set in a similar manner for XB load capacitance. Crystals with nominal load capacitance other than 10pF usually can be supported with only internal load capacitance. If the XACAP and XBCAP fields do not have sufficient range for the application, capacitance can be increased by using external caps C1 and C2.

Users should also note that on-chip capacitors are not nearly as accurate as discrete capacitors (which can have 1% accuracy). If tight frequency accuracy is required for the crystal driver circuit then set XACAP and XBCAP both to 0 and choose appropriate C1 and C2 capacitors with 1% tolerance.

The crystal, traces, and two external capacitors sites (if included) should be placed on the board as close as possible to the XA and XB pins to reduce crosstalk of active signals into the oscillator. Also no active signals should be routed under the crystal circuitry.

Note: Crystals have temperature sensitivies that can cause frequency changes in response to ambient temperature changes. In applications where significant temperature changes are expected near the crystal, it is recommended that the crystal be covered with a thermal cap, or an external XO or TCXO should be used instead.

**Table 2 - Crystal Selection Parameters**

| Parameter                                  | Symbol       | Min. | Тур. | Max.      | Units |     |

|--------------------------------------------|--------------|------|------|-----------|-------|-----|

| Crystal Oscillation Frequency <sup>1</sup> |              | fosc | 25   |           | 60    | MHz |

| Shunt Capacitance                          | Co           |      | 2    | 5         | pF    |     |

| Load Capacitance <sup>3</sup>              |              | CL   | 8    | 10        | 16    | pF  |

| Equivalent Series Resistance               | fosc < 40MHz | Rs   |      |           | 60    | Ω   |

| (ESR) <sup>2</sup>                         | fosc > 40MHz | Rs   |      |           | 50    | Ω   |

| Maximum Crystal Drive Level                |              |      | 100  | 100, 200, |       | μW  |

|                                            |              |      |      | 300       |       |     |

Note 1: Higher frequencies give lower output jitter, all else being equal.

Note 2: These ESR limits are chosen to constrain crystal drive level to less than  $100\mu W$ . If the crystal can tolerate a drive level greater than  $100\mu W$  then proportionally higher ESR is acceptable.

Note 3: For crystals with  $100\mu W$  max drive level: (a)  $f_{OSC}>55MHz$  and  $C_L\geq 12pF$  is not supported, and (b)  $f_{OSC}>45MHz$  and  $C_L\geq 16pF$  is not supported. Crystals with max drive level of  $200\mu W$  or higher do not have these limitations.

| Parameter                                    | Symbol           | Min. | Тур. | Max. | Units                   |

|----------------------------------------------|------------------|------|------|------|-------------------------|

| Crystal Frequency Stability vs. Power Supply | f <sub>FVD</sub> |      | 0.2  | 0.5  | ppm per 10%<br>∆ in VDD |

Any known frequency inaccuracy of the crystal can be compensated in the APLL by adjusting the APLL's fractional feedback divider value (AFBDIV) by ppb or ppm to compensate for crystal frequency error.

#### 5.3.3 Clock Doublers

Figure 1 shows an optional clock doubler ("x2" block) following the crystal driver block. This XA doubler, which is enabled by setting MCR2.DBL=1, can be used to double the frequency of the internal crystal driver circuit or a 20MHz to 78.125MHz clock signal on the XA pin. For input clock frequencies from 25MHz to 78.125MHz the duty cycle of the signal can be anywhere in the 40% to 60% range. For input clock frequencies from 20MHz to 25MHz the duty cycle must be in the 45% to 55% range. Figure 1 also shows an optional doubler at the input of each APLL. This APLL input doubler, which is enabled by setting ACR1.INDBL=1 for APLL1 or A2CR1.INDBL=1 for APLL2, can be used to double the frequency of any of the inputs. The following table shows scenarios when the clock doubler can be used.

| Scenario                  | With Crystal     | With XO or Clock Signal |

|---------------------------|------------------|-------------------------|

| APLL, Integer Multiply    | Yes <sup>1</sup> | Maybe <sup>1</sup>      |

| APLL, Fractional Multiply | Yes              | Yes                     |

| NCO                       | Yes              | Yes                     |

| Spread-Spectrum           | Yes              | Yes                     |

| APLL bypass path          | No <sup>2</sup>  | No <sup>2</sup>         |

ZL30264-ZL30267

Note 1: For APLL integer multiplication, use of the doubler is application-dependent. On the positive side, use of the doubler reduces random jitter. On the negative side, the doubler causes a spur at the XA frequency (but this spur may be outside the band of interest for the application).

Note 2: The signal generated by the doubler has a very narrow and variable pulse width and therefore it is not recommended to connect the doubler signal directly to the OCx outputs using an APLL bypass path. The doubler signal is fine as an input to the APLL, which filters the duty cycle distortion and produces a 50% duty cycle output.

Note 3: Using both doublers in series to double the XA-doubled signal is not supported.

#### 5.3.4 Ring Oscillator (for Auto-Configuration)

After reset the internal auto-configuration boot controller is clocked by an internal ring oscillator. After autoconfiguration is complete (GLOBISR.BCDONE=1) the ring oscillator can be disabled by setting MCR1.ROSCD=1. The device's processor interface is asynchronous and does not require the ring oscillator.

### **Input Signal Format Configuration**

Input clocks IC1, IC2 and IC3 are enabled by setting the enable bits in the ICEN register. The power consumed by a differential receiver is shown in Table 6. The electrical specifications for these inputs are listed in Table 9. Each input clock can be configured to accept nearly any differential signal format by using the proper set of external components (see Figure 15). To configure these differential inputs to accept single-ended CMOS signals, connect the single-ended signal to the ICxP pin, and connect the ICxN pin to a capacitor (0.1μF or 0.01μF) to VSS. Each ICxP and ICxN pin is internally biased to approximately 1.3V. If an input is not used, both ICxP and ICxN pins can be left floating. Note that the IC3N pin is not present. A differential signal can be connected to IC3P by AC-coupling the POS trace to IC3P and terminating the signal on the driver side of the coupling cap.

#### 5.5 **APLL Configuration**

ZL30264 through ZL30267 have two independent APLLs. Each APLL has all of the functionality described in the subsections below. For brevity, only APLL1-specific registers are mentioned. APLL2 has equivalent registers.

#### **APLL Input Frequency**

The frequencies of all enabled input clocks (ICx and XA) associated with an APLL must divide to a common APLL phase-frequency detector (PFD) frequency from 9.72MHz to 156.25MHz. In this mode the input high-speed dividers (ICxCR1.HSDIV) can be used to divide the ICx frequencies by 1, 2, 4 or 8 and the XA divider (MCR2. XODIV2) can be used to divide the XA frequency by 1 or 2. The polarity of an ICx input signal can be inverted by setting ICxCR1.POL.

#### 5.5.2 APLL Input Monitors

Each of the APLL's four inputs—IC1, IC2, IC3 and XA—have a simple activity monitor. If the monitor counts approximately four (eight if the input clock is doubled) APLL feedback clock cycles without seeing an input clock edge, the input is declared invalid and the corresponding ICxSR.ICV bit or XASR.ICV bit is set to 0. The input clock is declared valid, and the corresponding ICxSR.ICV bit or XASR.ICV bit is set to 1, when the input clock has no missing edges in an interval specified by the corresponding ICxCR1.VALTIME or XACR1.VALTIME field. The XASR and ICxSR registers provide real-time and latched status bits indicating the state of each input.

The feedback clock to use for each input monitor is specified by the MCR2.XAMCK and MCR2.ICxMCK bits.

#### 5.5.3 APLL Input Selection

The APLL can lock to any of inputs IC1 through IC3, a clock signal on XA (optionally clock-doubled), or the crystal driver circuit (optionally clock-doubled) when a crystal is connected to XA and XB.

The input to the APLL can be controlled by a register field, a GPIO pin, or a simple input activity monitor. When ACR3.EXTSW=0 and ACR3.INMON=0, the ACR3.APLLMUX register field controls the APLL input mux.

When ACR3.EXTSW=1, a GPIO pin controls the APLL input mux. When the GPIO pin is low, the mux selects the input specified by ACR3.APLLMUX. When the GPIO pin is high, the mux selects the input specified by ACR3.ALTMUX. ACR1.EXTSS specifies which GPIO pin controls this behavior.

When ACR3.EXTSW=0 and ACR3.INMON=1, an input monitor (see section 5.5.2) controls the APLL input mux. When the monitor for the input specified by ACR3.APLLMUX says that input is valid (ICxSR.ICV=1 or

XASR.ICV=1), the mux selects the input specified by ACR3.APLLMUX otherwise the mux selects the input specified by ACR3.ALTMUX.

The APLL1SR.SELREF and APLL2SR.SELREF real-time status fields indicate the APLL's selected reference.

#### 5.5.4 APLL Output Frequency

Figure 5 - APLL Block Diagram

The APLL is enabled when PLLEN.APLLEN=1. The APLL has a fractional-N architecture and therefore can produce output frequencies that are either integer or non-integer multiples of the input clock frequency. Figure 5 shows a block diagram of the APLL, which is built around an ultra-low-jitter multi-GHz VCO. Register fields AFBDIV, AFBREM, AFBDEN and AFBBP configure the frequency multiplication ratio of the APLL. The ACR2.INTDIV field specifies how the VCO frequency is divided down by the APLL's integer divider (which can also do some half divides). Dividing by 6 is the typical setting to produce 622.08MHz for SDH/SONET or 625MHz for Ethernet applications. The configuration registers for the APLL's fractional divider are described in section 5.5.5.

Internally, the exact APLL feedback divider value is expressed in the form AFBDIV + AFBREM / AFBDEN \*  $2^{-(33\text{-AFBBP})}$ . This feedback divider value must be chosen such that APLL\_input\_frequency \* feedback\_divider\_value is in the operating range of the VCO (as specified in Table 14). The AFBDIV term is a fixed-point number with 9 integer bits and a configurable number of fractional bits (up to 33, as specified by AFBBP). Typically AFBBP is set to 9 to specify that AFBDIV has 33-9=24 fractional bits. Using more than 24 fractional bits does not yield a detectable benefit. Using less than 12 fractional bits is not recommended.

The following equations show how to calculate the feedback divider values for the situation where the APLL should multiply the APLL input frequency by integer M and also fractionally scale by the ratio of integers N / D. In other words, VCO\_frequency = input\_frequency \* M \* N / D. An example of this is multiplying 77.76MHz by M=48 and scaling by N / D = 255 / 237 for forward error correction applications.

| afbdiv = trunc( $M * N / D * 2^{24}$ )        | (1) |

|-----------------------------------------------|-----|

| $lsb\_fraction = M * N / D * 2^{24} - afbdiv$ | (2) |

| AFBDEN = D                                    | (3) |

AFBBP =

$$33 - 24 = 9$$

(5)

$$AFBDIV[41:0] = afbdiv * 2^{AFBBP}$$

(6)

The trunc() function returns only the integer portion of the number. The round() function rounds the number to the nearest integer. In Equation (1), the temporary variable 'afbdiv' is set to the full-precision feedback divider value, M  $^*$  N / D, truncated after the 24<sup>th</sup> fractional bit. In Equation (2) the temporary variable 'lsb\_fraction' is the fraction that was truncated in Equation (1) and therefore is not represented in the afbdiv value. In Equation (3), AFBDEN is set to the denominator of the original M  $^*$  N / D ratio. In Equation (4), AFBREM is calculated as the integer numerator of a fraction (with denominator AFBDEN) that equals the 'lsb\_fraction' temporary variable. In Equation (5) AFBBP is set to 33 - 24 = 9 to correspond with AFBDIV having 24 fractional bits. Finally, in equation (6) the afbdiv bits are shifted into the proper position for the AFBDIV registers.

When a fractional scaling scenario involves multiplying an integer M times multiple scaling ratios  $N_1$  /  $D_1$  through  $N_n$  /  $D_n$ , the equations above can still be used if the numerators are multiplied together to get  $N = N_1 \times N_2 \times ... \times N_n$  and the denominators are multiplied together to get  $D = D_1 \times D_2 \times ... \times D_n$ .

The easiest way to calculate the exact values to write to the APLL registers is to use the ZL3026x evaluation software, available on the Microsemi website. This software can be used even when no evaluation board is attached to the computer.

Note: After the APLL's feedback divider settings are configured in register fields AFBDIV, AFBREM, AFBDEN and AFBBP, the APLL enable bit PLLEN.APLLEN should be changed from 0 to 1 to cause the APLL to reacquire lock with the new settings. The real-time lock/unlock status of the APLL is indicated by APLL1SR.ALK.

#### 5.5.5 Fractional Output Divider

As shown in Figure 1 and Figure 5, each APLL has a fractional output divider. This allows each APLL to be the source of two unrelated frequency families, one from the integer divider, and one from the fractional divider.

Configuration of the fractional output divider is very similar to configuration of the APLL's feedback divider. The fractional divider is enabled by setting ACR1.ENFDIV. Internally, the exact divider value is expressed in the form  $FDIV + FREM / FDEN * 2^{-(36-FBP)}$ . The input clock to the fractional divider is APLL VCO frequency divided by 2 ( $f_{VCO}/2$ ). The FDIV term is a fixed-point number with 4 integer bits and a configurable number of fractional bits (up to 36, as specified by FBP). Typically FBP is set to 12 to specify that FDIV has 36 - 12 = 24 fractional bits.

The output clock from the fractional divider has good phase noise on rising edges but worse phase noise on falling edges and can have non-50% duty cycle. Applications that only use clock rising edges can use the fractional divider's output clock directly. For applications that care about 50% duty cycle and/or the phase noise of both rising edges and falling edges, the fractional divider should be followed by an even medium-speed divider value (2, 4, 6, 8...). The low-speed divider can be used to further divide the output clock if needed.

The maximum output frequency for the fractional divider is  $f_{VCO}/10$ . This means the minimum fractional divider value is 5.0. Including the need for a divide-by-2 in the medium-speed divider, the maximum frequency for a 50% duty-cycle output clock signal is  $f_{VCO}/20$ . The minimum output frequency for the fractional divider is  $f_{VCO}/32$  since the internal FDIV value has 4 integer bits. The combination FDIV=0, FREM=0, FDEN=1 specifies to divide by 16.0. The medium-speed and low-speed dividers can be configured to follow the fractional output divider to create output frequencies down to <1Hz.

The following equations show how to calculate the register values for the situation where the fractional divider should divide by the integer M and the ratio of integers N / D. In other words,

An example of this is starting with VCO\_freq = 3750MHz (to get low-jitter Ethernet frequencies through the APLL's integer divider) and using the APLL's fractional divider to get 155.52MHz for SONET/SDH applications. In this example, M=12, N=15625, D=15552 are appropriate values to get 155.52MHz.

| $fdiv = trunc(M * N / D * 2^{24})$          | (1) |

|---------------------------------------------|-----|

| $lsb\_fraction = M * N / D * 2^{24} - fdiv$ | (2) |

| FDEN = D                                    | (3) |

| FREM = round(lsb_fraction * FDEN)           | (4) |

| FBP = 36 - 24 = 12                          | (5) |

| FDIV[39:0] = fdiv * 2 <sup>FBP</sup>        | (6) |

The trunc() function returns only the integer portion of the number. The round() function rounds the number to the nearest integer. In Equation (1), the temporary variable 'fdiv' is the full-precision feedback divider value, M  $^{\star}$  N / D, truncated after the 24<sup>th</sup> fractional bit. In Equation (2) the temporary variable 'lsb\_fraction' is the fraction that was truncated in Equation (1) and therefore is not represented in the fdiv value. In Equation (3), FDEN is set to the denominator of the original M  $^{\star}$  N / D ratio. In Equation (4), FREM is calculated as the integer numerator of a

fraction (with denominator FDEN) that equals the 'lsb\_fraction' temporary variable. In Equation (5) FBP is set to 36 - 24 = 12 to correspond with FDIV having 24 fractional bits. Finally, in equation (6) the fdiv bits are shifted into the proper position for the FDIV registers.

When a fractional scaling scenario involves multiplying an integer M times multiple scaling ratios  $N_1 / D_1$  through  $N_n / D_n$ , the equations above can still be used if the numerators are multiplied together to get  $N = N_1 \times N_2 \times ... \times N_n$  and the denominators are multiplied together to get  $D = D_1 \times D_2 \times ... \times D_n$ .

The easiest way to calculate the exact values to write to the APLL's fractional output divider registers is to use the ZL3026x evaluation software, available on the Microsemi website. This software can be used even when no evaluation board is attached to the computer.

#### 5.5.6 Numerically Controlled Oscillator (NCO) Mode

#### 5.5.6.1 Using the APLL's Feedback Divider

System software can steer output frequencies with high resolution by manipulating the APLL's AFBDIV value. The resolution can be better than 0.01ppb.

The nominal AFBDIV value, hereafter referred to as AFBDIV0, is the 0ppm nominal value for the desired device configuration.

(Fractional frequency offset (FFO) is defined as (actual\_frequency – nominal\_frequency) / nominal\_frequency. FFO is a unitless number but is typically expressed in parts per billion (ppb), parts per million (ppm) or percent.)

To control the NCO, system software first reads the AFBDIV0 value from the device. Even though the AFBDIV register description describes AFBDIV as having 9 integer bits and 33 fractional bits, for the NCO calculations that follow, AFBDIV values should be treated as 42-bit unsigned integers.

To change the NCO frequency to a specific FFO (in ppm), system software calculates newAFBDIV (a 42-bit unsigned integer) as follows:

newAFBDIV = round(AFBDIV0 \* (1 + FFO/1e6))

System software then writes the newAFBDIV value directly to the AFBDIV registers.

Note that any subsequent frequency changes are calculated using the same equation from the original AFBDIV0 value and are <u>not</u> a function of the previous newAFBDIV value. The value of newAFBDIV should be kept within ±1000ppm of AFBDIV0 and within ±500ppm of the previous newAFBDIV value to avoid causing the APLL to lose lock. If spread spectrum modulation is also in use, the total frequency change caused by spread spectrum modulation and NCO control should be kept within ±5000ppm of AFBDIV0 to avoid causing the APLL to lose lock.

During NCO operation using the APLL's feedback divider, AFBREM should be set to 0, AFBDEN should be set to 1 and AFBBP should be set to 0.

#### 5.5.6.2 Using the Fractional Output Divider

System software can steer output frequencies derived from the fractional output divider with high resolution by manipulating the divider's FDIV value. The resolution can be better than 0.01ppb. In the case of fractional output divider value >14.55192, the resolution is better than 1ppt.

The nominal FDIV value, hereafter referred to as FDIV0, is the 0ppm nominal value for the desired device configuration.