NOT RECOMMENDED FOR NEW DESIGNS RECOMMENDED REPLACEMENT PART ISL9000A

# DATASHEET

ISL9000

Dual LDO with Low Noise, Very High PSRR and Low IQ

FN9217 Rev 4.00 March 11, 2008

ISL9000 is a high performance dual LDO capable of sourcing 300mA current from each output. It has a low standby current and very high PSRR and is stable with output capacitance of  $1\mu F$  to  $10\mu F$  with ESR of up to  $200m\Omega$ .

The device integrates an individual Power-On-Reset (POR) function for each output. The POR delay for VO2 can be externally programmed by connecting a timing capacitor to the CPOR pin. The POR delay for VO1 is internally fixed at approximately 2ms. A reference bypass pin is also provided for connecting a noise filtering capacitor for low noise and high-PSRR applications.

The quiescent current is typically only  $42\mu A$  with both LDOs enabled and active. Separate enable pins control each individual LDO output. When both enable pins are low, the device is in shutdown, typically drawing less than  $0.1\mu A$ .

Several combinations of voltage outputs are standard. Output voltage options for each LDO range are from 1.5V to 3.3V. Other output voltage options may be available upon request.

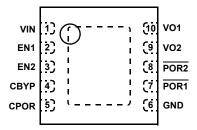

### **Pinout**

ISL9000 (10 LD 3X3 DFN) TOP VIEW

#### **Features**

- · Integrates two 300mA high performance LDOs

- · Excellent transient response to large current steps

- ±1.8% accuracy over all operating conditions

- Excellent load regulation:

- < 0.1% voltage change across full range of load current

- Low output noise: typically 30μV<sub>RMS</sub> @ 100μA (1.5V)

- · Very high PSRR: 90dB @ 1kHz

- Extremely low quiescent current: 42µA (both LDOs active)

- Wide input voltage capability: 2.3V to 6.5V

- Low dropout voltage: typically 200mV @ 300mA

- Stable with 1µF to 10µF ceramic capacitors

- Separate enable and POR pins for each LDO

- Soft-start and staged turn-on to limit input current surge during enable

- · Current limit and overheat protection

- Tiny 10 Ld 3mmx3mm DFN package

- -40°C to +85°C operating temperature range

- Pb-free (RoHS compliant)

### **Applications**

- · PDAs, Cell Phones and Smart Phones

- · Portable Instruments, MP3 Players

- · Handheld Devices including Medical Handhelds

## **Ordering Information**

| PART NUMBER<br>(Notes 1, 2, 3) | PART MARKING | VO1 VOLTAGE<br>(V) | VO2 VOLTAGE<br>(V) | TEMP RANGE (°C) | PACKAGE<br>(Pb-Free) | PKG DWG. # |

|--------------------------------|--------------|--------------------|--------------------|-----------------|----------------------|------------|

| ISL9000IRNNZ                   | DCGA         | 3.3                | 3.3                | -40 to +85      | 10 Ld 3x3 DFN        | L10.3x3C   |

| ISL9000IRNJZ                   | DAAA         | 3.3                | 2.8                | -40 to +85      | 10 Ld 3x3 DFN        | L10.3x3C   |

| ISL9000IRNFZ                   | DBAA         | 3.3                | 2.5                | -40 to +85      | 10 Ld 3x3 DFN        | L10.3x3C   |

| ISL9000IRNCZ                   | DABH         | 3.3                | 1.8                | -40 to +85      | 10 Ld 3x3 DFN        | L10.3x3C   |

| ISL9000IRMNZ                   | DCHA         | 3.0                | 3.3                | -40 to +85      | 10 Ld 3x3 DFN        | L10.3x3C   |

| ISL9000IRMMZ                   | DSAA         | 3.0                | 3.0                | -40 to +85      | 10 Ld 3x3 DFN        | L10.3x3C   |

| ISL9000IRMGZ                   | DCJA         | 3.0                | 2.7                | -40 to +85      | 10 Ld 3x3 DFN        | L10.3x3C   |

| ISL9000IRLLZ                   | DRAA         | 2.9                | 2.9                | -40 to +85      | 10 Ld 3x3 DFN        | L10.3x3C   |

| ISL9000IRKNZ                   | DABF         | 2.85               | 3.3                | -40 to +85      | 10 Ld 3x3 DFN        | L10.3x3C   |

| ISL9000IRKKZ                   | DCAA         | 2.85               | 2.85               | -40 to +85      | 10 Ld 3x3 DFN        | L10.3x3C   |

| ISL9000IRKJZ                   | DDAA         | 2.85               | 2.8                | -40 to +85      | 10 Ld 3x3 DFN        | L10.3x3C   |

| ISL9000IRKFZ                   | DEAA         | 2.85               | 2.5                | -40 to +85      | 10 Ld 3x3 DFN        | L10.3x3C   |

| ISL9000IRKPZ                   | DABG         | 2.85               | 1.85               | -40 to +85      | 10 Ld 3x3 DFN        | L10.3x3C   |

| ISL9000IRKCZ                   | DHAA         | 2.85               | 1.8                | -40 to +85      | 10 Ld 3x3 DFN        | L10.3x3C   |

| ISL9000IRJNZ                   | DCKA         | 2.8                | 3.3                | -40 to +85      | 10 Ld 3x3 DFN        | L10.3x3C   |

| ISL9000IRJMZ                   | DPAA         | 2.8                | 3.0                | -40 to +85      | 10 Ld 3x3 DFN        | L10.3x3C   |

| ISL9000IRJRZ                   | DNAA         | 2.8                | 2.6                | -40 to +85      | 10 Ld 3x3 DFN        | L10.3x3C   |

| ISL9000IRJCZ                   | DMAA         | 2.8                | 1.8                | -40 to +85      | 10 Ld 3x3 DFN        | L10.3x3C   |

| ISL9000IRJBZ                   | DFAA         | 2.8                | 1.5                | -40 to +85      | 10 Ld 3x3 DFN        | L10.3x3C   |

| ISL9000IRGPZ                   | DABE         | 2.7                | 1.85               | -40 to +85      | 10 Ld 3x3 DFN        | L10.3x3C   |

| ISL9000IRGCZ                   | DLAA         | 2.7                | 1.8                | -40 to +85      | 10 Ld 3x3 DFN        | L10.3x3C   |

| ISL9000IRFJZ                   | DGAA         | 2.5                | 2.8                | -40 to +85      | 10 Ld 3x3 DFN        | L10.3x3C   |

| ISL9000IRFDZ                   | DCLA         | 2.5                | 2.0                | -40 to +85      | 10 Ld 3x3 DFN        | L10.3x3C   |

| ISL9000IRFCZ                   | DCMA         | 2.5                | 1.8                | -40 to +85      | 10 Ld 3x3 DFN        | L10.3x3C   |

| ISL9000IRPLZ                   | DKAA         | 1.85               | 2.9                | -40 to +85      | 10 Ld 3x3 DFN        | L10.3x3C   |

| ISL9000IRPPZ                   | DABJ         | 1.85               | 1.85               | -40 to +85      | 10 Ld 3x3 DFN        | L10.3x3C   |

| ISL9000IRCJZ                   | DCNA         | 1.8                | 2.8                | -40 to +85      | 10 Ld 3x3 DFN        | L10.3x3C   |

| ISL9000IRCCZ                   | DCPA         | 1.8                | 1.8                | -40 to +85      | 10 Ld 3x3 DFN        | L10.3x3C   |

| ISL9000IRBLZ                   | DABD         | 1.5                | 2.9                | -40 to +85      | 10 Ld 3x3 DFN        | L10.3x3C   |

| ISL9000IRBJZ                   | DJAA         | 1.5                | 2.8                | -40 to +85      | 10 Ld 3x3 DFN        | L10.3x3C   |

| ISL9000IRBCZ                   | DABC         | 1.5                | 1.8                | -40 to +85      | 10 Ld 3x3 DFN        | L10.3x3C   |

| ISL9000IRBBZ                   | DABB         | 1.5                | 1.5                | -40 to +85      | 10 Ld 3x3 DFN        | L10.3x3C   |

#### NOTES:

- 1. Add "-T" suffix for tape and reel. Please refer to TB347 for details on reel specifications.

- 2. For other output voltages, contact Intersil Marketing.

- 3. These Intersil Pb-free plastic packaged products employ special Pb-free material sets; molding compounds/die attach materials and 100% matte tin plate PLUS ANNEAL e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

### **Absolute Maximum Ratings**

| Supply Voltage (VIN)                    | +7.1V                |

|-----------------------------------------|----------------------|

| V <sub>O</sub> 1, V <sub>O</sub> 2 Pins | +3.6V                |

| All Other Pins                          | 0.3 to (VINI + 0.3)V |

### **Recommended Operating Conditions**

| Ambient Temperature Range (TA). | 40°C to +85°C |

|---------------------------------|---------------|

| Supply Voltage (VIN)            | 2.3V to 6.5V  |

### **Thermal Information**

| Thermal Resistance (Notes 4, 5)         | $\theta_{JA}$ (°C/W) | $\theta_{JC}$ (°C/W) |

|-----------------------------------------|----------------------|----------------------|

| 10 Ld 3x3 DFN Package                   | 50                   | 10                   |

| Junction Temperature Range              | 40°                  | °C to +125°C         |

| Operating Temperature Range             | 40                   | 0°C to +85°C         |

| Storage Temperature Range               | 65°                  | °C to +150°C         |

| Pb-free Reflow Profile                  |                      | ee link below        |

| http://www.intersil.com/pbfree/Pb-FreeF | Reflow.asp           |                      |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

#### NOTES

- θ<sub>JA</sub> is measured in free air with the component mounted on a high effective thermal conductivity test board with "direct attach" features. See Tech Brief TB379.

- 5. For  $\theta_{JC}$ , the "case temp" location is the center of the exposed metal pad on the package underside.

### **Electrical Specifications**

Unless otherwise noted, all parameters are guaranteed over the operational supply voltage and temperature range of the device as follows:

$T_A=-40^{\circ}C$  to +85°C;  $V_{IN}$  = (V\_O + 0.5V) to 6.5V with a minimum  $V_{IN}$  of 2.3V;  $C_{IN}$  = 1µF;  $C_O$  = 1µF;  $C_{BYP}$  = 0.01µF;  $C_{POR}$  = 0.01µF.

| PARAMETER                     | SYMBOL           | DL TEST CONDITIONS                                                                                                                    |      | TYP | MAX<br>(Note 8) | UNITS             |  |

|-------------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------|------|-----|-----------------|-------------------|--|

| DC CHARACTERISTICS            |                  |                                                                                                                                       |      |     |                 |                   |  |

| Supply Voltage                | V <sub>IN</sub>  |                                                                                                                                       | 2.3  |     | 6.5             | V                 |  |

| Ground Current                |                  | Quiescent condition: I <sub>O1</sub> = 0μA; I <sub>O2</sub> = 0μA                                                                     |      |     |                 |                   |  |

|                               | I <sub>DD1</sub> | One LDO active                                                                                                                        |      | 25  | 32              | μΑ                |  |

|                               | I <sub>DD2</sub> | Both LDO active                                                                                                                       |      | 42  | 52              | μΑ                |  |

| Shutdown Current              | I <sub>DDS</sub> | @ +25°C                                                                                                                               |      | 0.1 | 1.0             | μA                |  |

| UVLO Threshold                | V <sub>UV+</sub> |                                                                                                                                       | 1.9  | 2.1 | 2.3             | V                 |  |

|                               | V <sub>UV-</sub> |                                                                                                                                       | 1.6  | 1.8 | 2.0             | ٧                 |  |

| Regulation Voltage Accuracy   |                  | Initial accuracy at $V_{IN} = V_O + 0.5V$ , $I_O = 10$ mA, $T_J = +25$ °C                                                             | -0.7 |     | +0.7            | %                 |  |

|                               |                  | $V_{IN}$ = $V_O$ + 0.5V to 5.5V, $I_O$ = 10 $\mu$ A to 300mA, $T_J$ = +25°C                                                           | -0.8 |     | +0.8            | %                 |  |

|                               |                  | $V_{IN} = V_O + 0.5V \text{ to } 5.5V, I_O = 10\mu\text{A to } 300\text{mA},$<br>$T_J = -40^{\circ}\text{C to } +125^{\circ}\text{C}$ | -1.8 |     | +1.8            | %                 |  |

| Maximum Output Current        | I <sub>MAX</sub> | Continuous                                                                                                                            | 300  |     |                 | mA                |  |

| Internal Current Limit        | I <sub>LIM</sub> |                                                                                                                                       | 350  | 475 | 600             | mA                |  |

| Dropout Voltage (Note 7)      | V <sub>DO1</sub> | I <sub>O</sub> = 300mA; V <sub>O</sub> < 2.5V                                                                                         |      | 300 | 500             | mV                |  |

|                               | V <sub>DO2</sub> | $I_O$ = 300mA; 2.5V $\leq$ V <sub>O</sub> $\leq$ 2.8V                                                                                 |      | 250 | 400             | mV                |  |

|                               | $V_{DO3}$        | I <sub>O</sub> = 300mA; V <sub>O</sub> > 2.8V                                                                                         |      | 200 | 325             | mV                |  |

| Thermal Shutdown Temperature  | T <sub>SD+</sub> |                                                                                                                                       |      | 145 |                 | °C                |  |

|                               | T <sub>SD-</sub> |                                                                                                                                       |      | 110 |                 | °C                |  |

| AC CHARACTERISTICS            |                  |                                                                                                                                       |      |     |                 |                   |  |

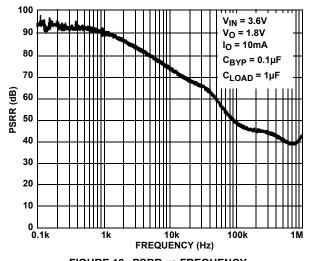

| Ripple Rejection (Note 6)     |                  | $I_O$ = 10mA, $V_{IN}$ = 2.8V(min), $V_O$ = 1.8V, $C_{BYP}$ = 0.1 $\mu$ F                                                             |      |     |                 |                   |  |

|                               |                  | @ 1kHz                                                                                                                                |      | 90  |                 | dB                |  |

|                               |                  | @ 10kHz                                                                                                                               |      | 70  |                 | dB                |  |

|                               |                  | @ 100kHz                                                                                                                              |      | 50  |                 | dB                |  |

| Output Noise Voltage (Note 6) |                  | $I_O$ = 100 $\mu$ A, $V_O$ = 1.5V, $T_A$ = +25°C, $C_{BYP}$ = 0.1 $\mu$ F BW = 10Hz to 100kHz                                         |      | 30  |                 | μV <sub>RMS</sub> |  |

| DEVICE START-UP CHARACTE      | RISTICS          |                                                                                                                                       |      |     | 1               |                   |  |

### **Electrical Specifications**

Unless otherwise noted, all parameters are guaranteed over the operational supply voltage and temperature range of the device as follows:

$T_A$  = -40°C to +85°C;  $V_{IN}$  = ( $V_O$  + 0.5V) to 6.5V with a minimum  $V_{IN}$  of 2.3V;  $C_{IN}$  = 1 $\mu$ F;  $C_O$  = 1 $\mu$ F;  $C_{BYP}$  = 0.01 $\mu$ F;  $C_{POR}$  = 0.01 $\mu$ F. (**Continued**)

| PARAMETER                                     | SYMBOL                            | TEST CONDITIONS                                                                          | MIN<br>(Note 8) | TYP | MAX<br>(Note 8)       | UNITS |

|-----------------------------------------------|-----------------------------------|------------------------------------------------------------------------------------------|-----------------|-----|-----------------------|-------|

| Device Enable Time                            | t <sub>EN</sub>                   | Time from assertion of the ENx pin to when the output voltage reaches 95% of the VO(nom) |                 | 250 | 500                   | μs    |

| LDO Soft-Start Ramp Rate                      | t <sub>SSR</sub>                  | Slope of linear portion of LDO output voltage ramp during start-up                       |                 | 30  | 60                    | µs/V  |

| EN1, EN2 PIN CHARACTERISTI                    | cs                                |                                                                                          | 1               |     |                       |       |

| Input Low Voltage                             | V <sub>IL</sub>                   |                                                                                          | -0.3            |     | 0.5                   | V     |

| Input High Voltage                            | V <sub>IH</sub>                   |                                                                                          | 1.4             |     | V <sub>IN</sub> + 0.3 | V     |

| Input Leakage Current                         | I <sub>IL</sub> , I <sub>IH</sub> |                                                                                          |                 |     | 0.1                   | μΑ    |

| Pin Capacitance                               | C <sub>PIN</sub>                  | Informative                                                                              |                 | 5   |                       | pF    |

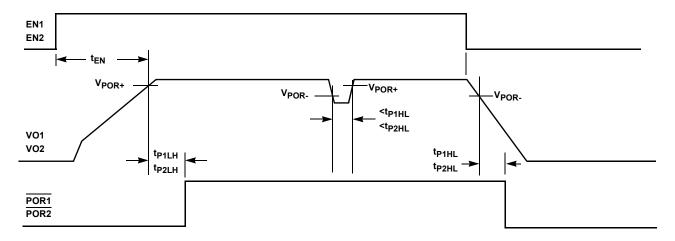

| POR1, POR2 PIN CHARACTERI                     | STICS                             |                                                                                          |                 |     |                       |       |

| POR1, POR2 Thresholds                         | V <sub>POR+</sub>                 | As a percentage of nominal output voltage                                                | 91              | 94  | 97                    | %     |

|                                               | V <sub>POR-</sub>                 |                                                                                          | 87              | 90  | 93                    | %     |

| POR1 Delay                                    | t <sub>P1LH</sub>                 |                                                                                          | 1.0             | 2.0 | 3.0                   | ms    |

|                                               | t <sub>P1HL</sub>                 |                                                                                          |                 | 25  |                       | μs    |

| POR2 Delay                                    | t <sub>P2LH</sub>                 | C <sub>POR</sub> = 0.01μF                                                                | 100             | 200 | 300                   | ms    |

|                                               | t <sub>P2HL</sub>                 |                                                                                          |                 | 25  |                       | μs    |

| POR1, POR2 Pin Output Low<br>Voltage          | V <sub>OL</sub>                   | @I <sub>OL</sub> = 1.0mA                                                                 |                 |     | 0.2                   | V     |

| POR1, POR2 Pin Internal Pull-Up<br>Resistance | R <sub>POR</sub>                  |                                                                                          | 78              | 100 | 180                   | kΩ    |

### NOTES:

- 6. Limits established by characterization and are not production tested.

- 7. VOx = 0.98\*VOx(NOM); Valid for VOx greater than 1.85V.

- 8. Parts are 100% tested at +25°C. Temperature limits established by characterization and are not production tested.

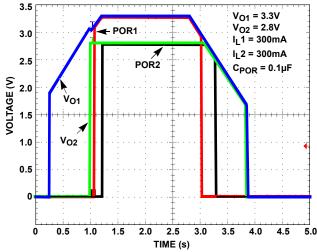

FIGURE 1. TIMING PARAMETER DEFINITION

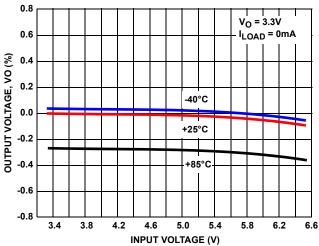

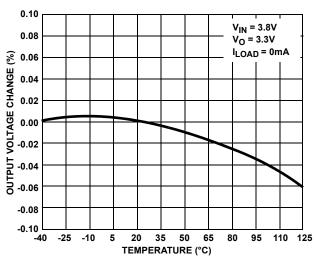

### **Typical Performance Curves**

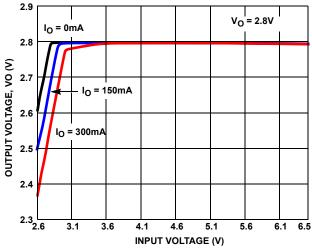

FIGURE 2. OUTPUT VOLTAGE vs INPUT VOLTAGE (3.3V OUTPUT)

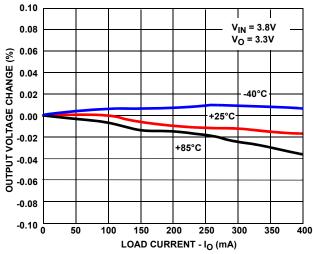

FIGURE 4. OUTPUT VOLTAGE CHANGE vs TEMPERATURE

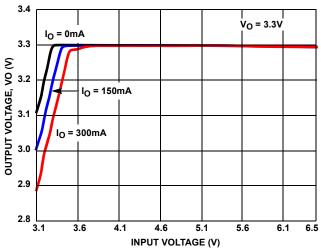

FIGURE 6. OUTPUT VOLTAGE vs INPUT VOLTAGE (2.8V OUTPUT)

FIGURE 3. OUTPUT VOLTAGE CHANGE vs LOAD CURRENT

FIGURE 5. OUTPUT VOLTAGE vs INPUT VOLTAGE (3.3V OUTPUT)

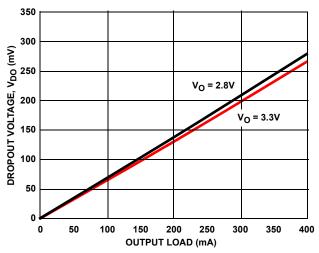

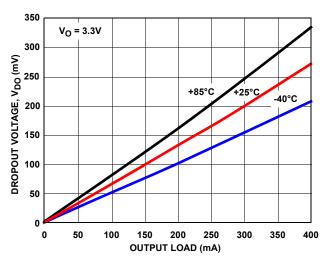

FIGURE 7. DROPOUT VOLTAGE vs LOAD CURRENT

### Typical Performance Curves (Continued)

FIGURE 8. DROPOUT VOLTAGE vs LOAD CURRENT

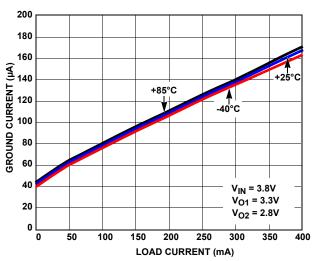

FIGURE 10. GROUND CURRENT vs LOAD

55 50 +125°C GROUND CURRENT (µA) +25°C 45 -40°C 40 35  $V_{O1} = 3.3V$  $V_{O2} = 2.8V$ 30  $I_O(BOTH CHANNELS) = 0\mu A$ 25 3.0 3.5 4.0 4.58 5.0 6.0 5.5 6.5 INPUT VOLTAGE (V)

FIGURE 9. GROUND CURRENT vs INPUT VOLTAGE

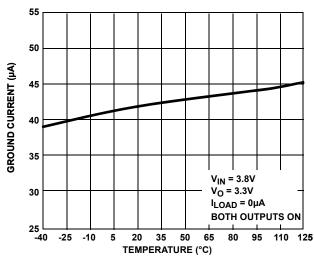

FIGURE 11. GROUND CURRENT vs TEMPERATURE

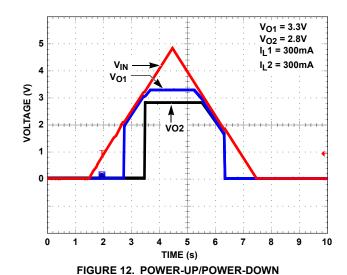

FIGURE 13. POWER-UP/POWER-DOWN WITH POR SIGNALS

### Typical Performance Curves (Continued)

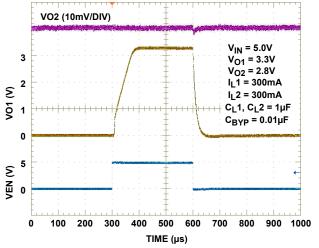

FIGURE 14. TURN ON/TURN OFF RESPONSE

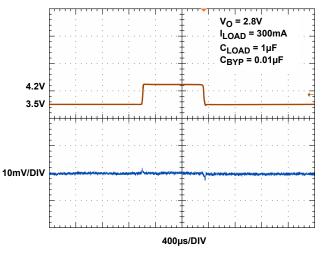

FIGURE 16. LINE TRANSIENT RESPONSE (2.8V OUTPUT)

FIGURE 18. PSRR vs FREQUENCY

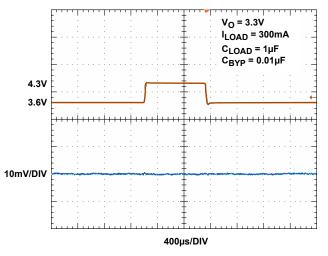

FIGURE 15. LINE TRANSIENT RESPONSE (3.3V OUTPUT)

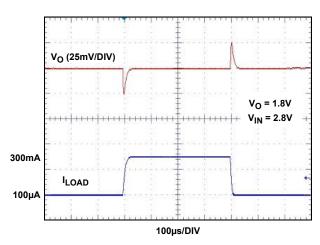

FIGURE 17. LOAD TRANSIENT RESPONSE

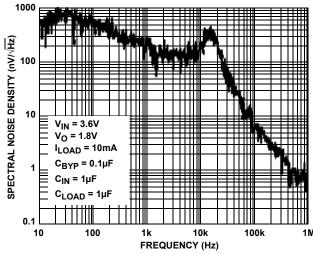

FIGURE 19. SPECTRAL NOISE DENSITY vs FREQUENCY

# Pin Description

| PIN<br>NUMBER | PIN<br>NAME | TYPE                                 | DESCRIPTION                                                                                                                                                                                              |

|---------------|-------------|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1             | VIN         | Analog I/O                           | Supply Voltage/LDO Input:<br>Connect a 1µF capacitor to GND.                                                                                                                                             |

| 2             | EN1         | Low Voltage Compatible<br>CMOS Input | LDO-1 Enable.                                                                                                                                                                                            |

| 3             | EN2         | Low Voltage Compatible<br>CMOS Input | LDO-2 Enable.                                                                                                                                                                                            |

| 4             | CBYP        | Analog I/O                           | Reference Bypass Capacitor Pin: Optionally connect capacitor of value $0.01\mu F$ to $1\mu F$ between this pin and GND to tune in the desired noise and PSRR performance.                                |

| 5             | CPOR        | Analog I/O                           | POR2 Delay Setting Capacitor Pin: Connect a capacitor between this pin and GND to delay the POR2 output release after LDO-2 output reaches 94% of its specified voltage level. (200ms delay per 0.01µF). |

| 6             | GND         | Ground                               | GND is the connection to system ground. Connect to PCB Ground plane.                                                                                                                                     |

| 7             | POR1        | Open Drain Output (1mA)              | Open-drain POR Output for LDO-1 (active-low): Internally connected to VO1 through 100kΩ resistor.                                                                                                        |

| 8             | POR2        | Open Drain Output (1mA)              | Open-drain POR Output for LDO-2 (active-low): Internally connected to VO2 through 100kΩ resistor.                                                                                                        |

| 9             | VO2         | Analog I/O                           | LDO-2 Output:<br>Connect capacitor of value 1µF to 10µF to GND (1µF recommended).                                                                                                                        |

| 10            | VO1         | Analog I/O                           | LDO-1 Output:<br>Connect capacitor of value 1µF to 10µF to GND (1µF recommended).                                                                                                                        |

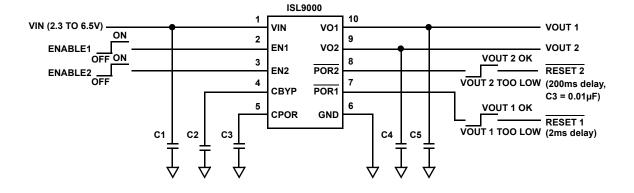

# **Typical Application**

C1, C4, C5: 1µF X5R ceramic capacitor

C2:  $0.1\mu F$  X7R ceramic capacitor

C3: 0.01µF X7R ceramic capacitor

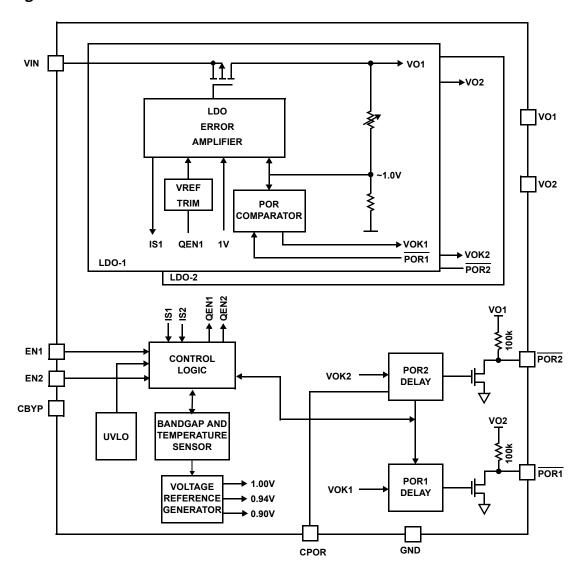

### **Block Diagram**

### Functional Description

The ISL9000 contains two high performance LDOs. High performance is achieved through a circuit that delivers fast transient response to varying load conditions. In a quiescent condition, the ISL9000 adjusts its biasing to achieve the lowest standby current consumption.

The device also integrates current limit protection, smart thermal shutdown protection, staged turn-on and soft-start. Smart thermal shutdown protects the device against overheating. Staged turn-on and soft-start minimize start-up input current surges without causing excessive device turn-on time.

#### **Power Control**

The ISL9000 has two separate enable pins, EN1 and EN2, to individually control power to each of the LDO outputs. When both EN1 and EN2 are low, the device is in shutdown

mode. During this condition, all on-chip circuits are off, and the device draws minimum current, typically less than 0.1µA.

When one or both of the enable pins are asserted, the device first polls the output of the UVLO detector to ensure that VIN voltage is at least about 2.1V. Once verified, the device initiates a start-up sequence. During the start-up sequence, trim settings are first read and latched. Then, sequentially, the bandgap, reference voltage and current generation circuitry power-up. Once the references are stable, a fast-start circuit quickly charges the external reference bypass capacitor (connected to the CBYP pin) to the proper operating voltage. After the bypass capacitor has been charged, the LDOs power-up in their specified sequence.

Soft-start circuitry integrated into each LDO limits the initial ramp-up rate to about 30µs/V to minimize current surge.

If EN1 is brought high, and EN2 goes high before the VO1 output stabilizes, the ISL9000 delays the VO2 turn-on until the VO1 output reaches its target level.

If EN2 is brought high, and EN1 goes high before VO2 starts its output ramp, then VO1 turns on first and, the ISL9000 delays the VO2 turn-on until the VO1 output reaches its target level.

If EN2 is brought high, and EN1 goes high after VO2 starts its output ramp, then the ISL9000 immediately starts to ramp up the VO1 output.

If both EN1 and EN2 are brought high at the same time, the VO1 output has priority, and is always powered up first.

During operation, whenever the VIN voltage drops below about 1.8V, the ISL9000 immediately disables both LDO outputs. When VIN rises back above 2.1V, the device re-initiates its start-up sequence and LDO operation will resume automatically.

#### Reference Generation

The reference generation circuitry includes a trimmed bandgap, a trimmed voltage reference divider, a trimmed current reference generator, and an RC noise filter. The filter includes the external capacitor connected to the CBYP pin. A  $0.01\mu F$  capacitor connected CBYP implements a 100Hz lowpass filter, and is recommended for most high performance applications. For the lowest noise application, a  $0.1\mu F$  or greater CBYP capacitor should be used. This filters the reference noise below the 10Hz to 1kHz frequency band, which is crucial in many noise-sensitive applications.

The bandgap generates a zero temperature coefficient (TC) voltage for the reference divider. The reference divider provides the regulation reference, POR detection thresholds, and other voltage references required for current generation and over-temperature detection.

The current generator provides the references required for adaptive biasing as well as references for LDO output current limit and thermal shutdown determination.

#### LDO Regulation and Programmable Output Divider

The LDO Regulator is implemented with a high-gain operational amplifier driving a PMOS pass transistor. The design of the ISL9000 provides a regulator that has low quiescent current, fast transient response, and overall stability across all operating and load current conditions. LDO stability is guaranteed for a  $1\mu F$  to  $10\mu F$  output capacitor that has a tolerance better than 20% and ESR less than  $200m\Omega$ . The design is performance-optimized for a  $1\mu F$  capacitor. Unless limited by the application, use of an output capacitor value above  $4.7\mu F$  is not normally needed as LDO performance improvement is minimal.

Each LDO uses an independently trimmed 1V reference. An internal resistor divider drops the LDO output voltage down to 1V. This is compared to the 1V reference for regulation.

The resistor division ratio is programmed in the factory to one of the following output voltages: 1.5V, 1.8V, 1.85V, 2.5V, 2.6V, 2.7V, 2.8V, 2.85V, 2.9V, 3.0V, and 3.3V.

#### Power-On Reset Generation

Each LDO has a separate Power-on Reset signal generation circuit which outputs to the respective POR pins. The POR signal is generated as follows:

A POR comparator continuously monitors the output of each LDO. The LDO enters a power-good state when the output voltage is above 94% of the expected output voltage for a period exceeding the LDO PGOOD entry delay time (see the following). In the power-good state, the open-drain  $\overline{\text{PORx}}$  output is in a high-impedance state. An internal  $100\text{k}\Omega$  pull-up resistor pulls the pin up to the respective LDO output voltage. An external resistor can be added between the  $\overline{\text{PORx}}$  output and the LDO output for a faster rise time, however, the  $\overline{\text{PORx}}$  output should not connect through an external resistor to a supply greater than the associated LDO voltage.

The power-good state is exited when the LDO output falls below 90% of the expected output voltage for a period longer than the PGOOD exit delay time. While power-good is false, the ISL9000 pulls the respective POR pin low.

For LDO-1, the PGOOD entry delay time is fixed at about 2ms while the PGOOD exit delay is about 25µs. For LDO-2, the PGOOD entry and exit delays are determined by the value of the external capacitor connected to the CPOR pin. For a 0.01µF capacitor, the entry and exit delays are 200ms and 25µs respectively. Larger or smaller capacitor values will yield proportionately longer or shorter delay times. The POR exit delay should never be allowed to be less than 10µs to ensure sufficient immunity against transient induced false POR triggering.

#### **Overheat Detection**

The bandgap provides a proportional-to-temperature current that is indicative of the temperature of the silicon. This current is compared with references to determine if the device is in danger of damage due to overheating. When the die temperature reaches about +145°C, one or both of the LDOs momentarily shut down until the die cools sufficiently. In the overheat condition, only the LDO sourcing more than 50mA will be shut off. This does not affect the operation of the other LDO. If both LDOs source more than 50mA and an overheat condition occurs, both LDO outputs are disabled. Once the die temperature falls back below about +110°C, the disabled LDO(s) are re-enabled and soft-start automatically takes place.

The ISL9000 provides short-circuit protection by limiting the output current to about 475mA. If short circuited, an output current of 475mA will cause die heating. If the short circuit lasts long enough, the overheat detection circuit will turn off the output.

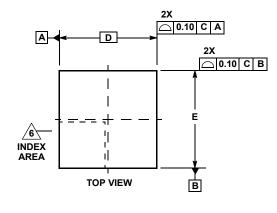

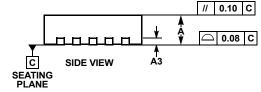

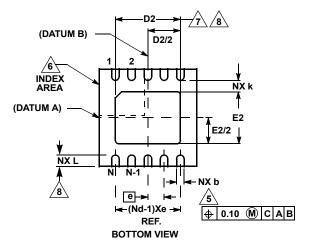

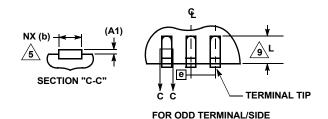

## Dual Flat No-Lead Plastic Package (DFN)

L10.3x3C

10 LEAD DUAL FLAT NO-LEAD PLASTIC PACKAGE

|        | ı        |          |      |       |

|--------|----------|----------|------|-------|

| SYMBOL | MIN      | NOMINAL  | MAX  | NOTES |

| Α      | 0.85     | 0.90     | 0.95 | -     |

| A1     | -        | -        | 0.05 | -     |

| A3     |          | 0.20 REF |      | -     |

| b      | 0.20     | 0.25     | 0.30 | 5, 8  |

| D      | 3.00 BSC |          |      | -     |

| D2     | 2.33     | 2.38     | 2.43 | 7, 8  |

| E      | 3.00 BSC |          |      | -     |

| E2     | 1.59     | 1.64     | 1.69 | 7, 8  |

| е      | 0.50 BSC |          |      | -     |

| k      | 0.20     | -        | -    | -     |

| L      | 0.35     | 0.40     | 0.45 | 8     |

| N      | 10       |          |      | 2     |

| Nd     | 5        |          |      | 3     |

Rev. 1 4/06

#### NOTES:

- 1. Dimensioning and tolerancing conform to ASME Y14.5-1994.

- 2. N is the number of terminals.

- 3. Nd refers to the number of terminals on D.

- 4. All dimensions are in millimeters. Angles are in degrees.

- 5. Dimension b applies to the metallized terminal and is measured between 0.15mm and 0.30mm from the terminal tip.

- The configuration of the pin #1 identifier is optional, but must be located within the zone indicated. The pin #1 identifier may be either a mold or mark feature.

- Dimensions D2 and E2 are for the exposed pads which provide improved electrical and thermal performance.

- 8. Nominal dimensions are provided to assist with PCB Land Pattern Design efforts, see Intersil Technical Brief TB389.

- 9. COMPLIANT TO JEDEC MO-229-WEED-3 except for dimensions E2 & D2.

© Copyright Intersil Americas LLC 2005-2008. All Rights Reserved. All trademarks and registered trademarks are the property of their respective owners.

For additional products, see <a href="www.intersil.com/en/products.html">www.intersil.com/en/products.html</a>

Intersil products are manufactured, assembled and tested utilizing ISO9001 quality systems as noted in the quality certifications found at <a href="https://www.intersil.com/en/support/qualandreliability.html">www.intersil.com/en/support/qualandreliability.html</a>

Intersil products are sold by description only. Intersil may modify the circuit design and/or specifications of products at any time without notice, provided that such modification does not, in Intersil's sole judgment, affect the form, fit or function of the product. Accordingly, the reader is cautioned to verify that datasheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see <a href="https://www.intersil.com">www.intersil.com</a>