Sample &

Buy

Support &

20

#### **DRV201**

SLVSB25C - AUGUST 2011-REVISED JUNE 2015

# DRV201 Voice Coil Motor Driver for Camera Auto Focus

Technical

Documents

#### Features 1

- Configurable for Linear or PWM Mode VCM Current Generation

- High Efficiency PWM Current Control for VCM

- Advanced Ringing Compensation

- Integrated 10-bit D/A Converter for VCM Current Control

- Protection

- Open and Short-Circuit Detection on VCM Pins

- Undervoltage Lockout (UVLO)

- Thermal Shutdown

- Open and Short-Circuit Protection on VCM Output

- Internal Current Limit for VCM Driver

- 4-kV ESD-HBM

- I<sup>2</sup>C Interface

- Operating Temperature Range: -40°C to 85°C

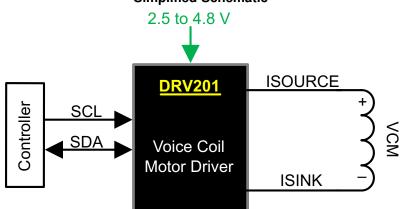

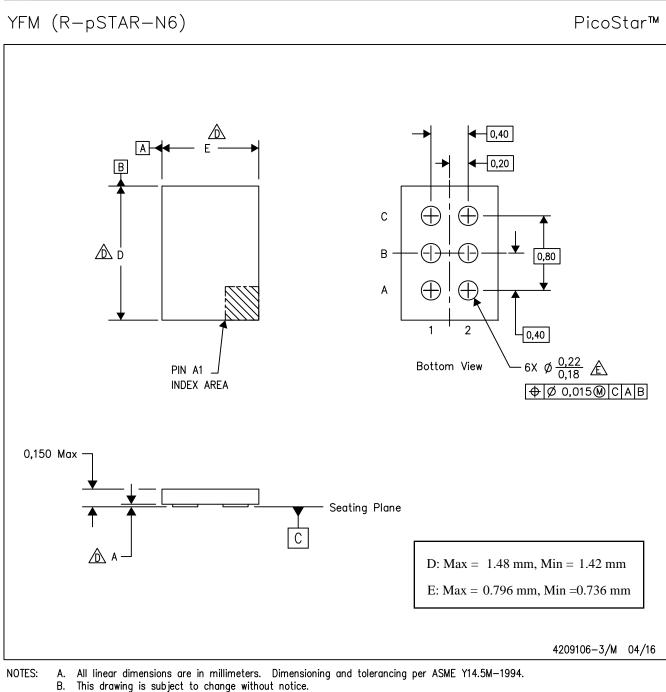

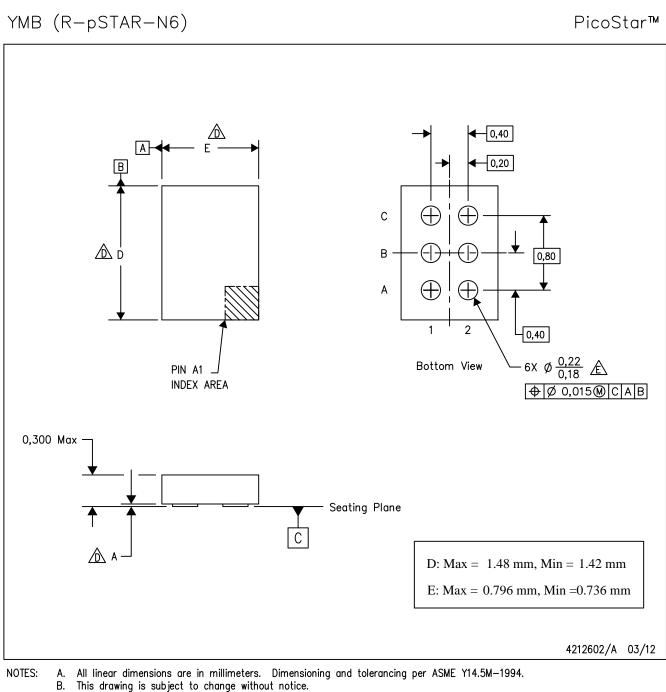

- 6-Ball WCSP Package With 0.4-mm Pitch

- Max Die Size: 0.8 mm × 1.48 mm

- Package Heights:

- YFM: 0.15 mm

- YMB: 0.3 mm

## 2 Applications

Cell Phone Auto Focus

Tools &

Software

- **Digital Still Camera Auto Focus**

- Iris and Exposure Controls

- Security Cameras

- Web and PC Cameras

- Actuator Controls

## 3 Description

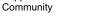

The DRV201 device is an advanced voice coil motor driver for camera auto focus. It has an integrated D/A converter for setting the VCM current. VCM current is controlled with a fixed frequency PWM controller or a linear mode driver. Current generation can be selected via I<sup>2</sup>C register. The DRV201 device has an integrated sense resistor for current regulation and the current can be controlled through  $I^2C$ .

When changing the current in the VCM, the lens ringing is compensated with an advanced ringing compensation function. Ringing compensation reduces the needed time for auto focus significantly. The device also has VCM short and open protection functions.

#### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE      | BODY SIZE (NOM)   |

|-------------|--------------|-------------------|

|             | DSBGA (6)    | 0.80 mm × 1.48 mm |

| DRV201      | PICOSTAR (6) | 0.80 mm × 1.48 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

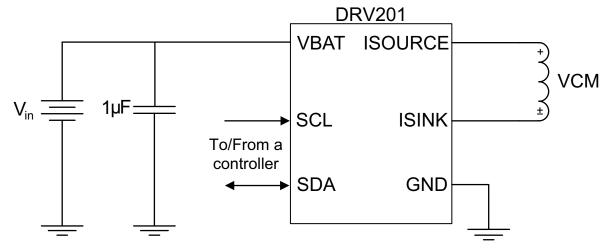

## **Simplified Schematic**

Features ..... 1

Applications ..... 1

Description ..... 1

Revision History..... 2

Pin Configuration and Functions ...... 3

Absolute Maximum Ratings ...... 3

ESD Ratings ...... 3

Recommended Operating Conditions ...... 4

Thermal Information ...... 4

Electrical Characteristics...... 4

6.6 Data Transmission Timing ...... 6

6.7 Typical Characteristics ...... 7

Detailed Description ...... 8

1

2

3

4

5

6

7

6.1

6.2

6.3

6.4

6.5

7.1

7.2

7.3

Page

|                                            | 7.5  | Programming                     | 12              |

|--------------------------------------------|------|---------------------------------|-----------------|

|                                            | 7.6  | Register Maps                   | 15              |

| 8                                          | Арр  | lication and Implementation     | 19              |

|                                            | 8.1  | Application Information         | 19              |

|                                            | 8.2  | Typical Application             | 19              |

| 9                                          | Pow  | er Supply Recommendations       | <mark>22</mark> |

| <b>10 Layout</b><br>10.1 Layout Guidelines |      | <mark>22</mark>                 |                 |

|                                            | 10.1 | Layout Guidelines               | 22              |

|                                            | 10.2 | Layout Example                  | 22              |

| 11                                         | Dev  | ice and Documentation Support   | <mark>23</mark> |

|                                            | 11.1 | Community Resources             | 23              |

|                                            | 11.2 | Trademarks                      | 23              |

|                                            | 11.3 | Electrostatic Discharge Caution | 23              |

|                                            | 11.4 | Glossary                        | 23              |

12 Mechanical, Packaging, and Orderable Information ...... 23

7.4 Device Functional Modes..... 11

## 4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

#### Changes from Revision B (November 2013) to Revision C

|                                                                                                                                                                                                                                                                                     | Page |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Added ESD Ratings table, Feature Description section, Device Functional Modes, Application and Implementation section, Power Supply Recommendations section, Layout section, Device and Documentation Support section, and Mechanical, Packaging, and Orderable Information section |      |

**Table of Contents**

#### Changes from Revision A (June 2012) to Revision B

#### XAS STRUMENTS

www.ti.com

## 5 Pin Configuration and Functions

#### **Pin Functions**

| PIN      |     | 1/0 | DESCRIPTION                                                      |  |

|----------|-----|-----|------------------------------------------------------------------|--|

| NAME     | NO. | I/O | DESCRIPTION                                                      |  |

| VBAT     | 2A  | Р   | Power                                                            |  |

| GND      | 1A  | Р   | Ground                                                           |  |

| I_SOURCE | 2B  | 0   | Voice coil positive terminal                                     |  |

| I_SINK   | 1B  | 0   | Voice coil negative terminal                                     |  |

| SCL      | 2C  | I   | I <sup>2</sup> C serial interface clock input                    |  |

| SDA      | 1C  | I/O | I <sup>2</sup> C serial interface data input/output (open drain) |  |

## 6 Specifications

## 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) <sup>(1)</sup>

|                  |                                                 | MIN       | MAX       | UNIT |

|------------------|-------------------------------------------------|-----------|-----------|------|

|                  | VBAT, ISOURCE, ISINK pin voltage <sup>(2)</sup> | -0.3      | 5.5       | V    |

|                  | Voltage at SDA, SCL                             | -0.3      | 3.6       | V    |

|                  | Continuous total power dissipation              | Internall | y limited |      |

| TJ               | Operating junction temperature                  | -40       | 125       | °C   |

| T <sub>A</sub>   | Operating ambient temperature                   | -40       | 85        | °C   |

| T <sub>stg</sub> | Storage temperature                             | 55        | 150       | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltage values are with respect to network ground terminal.

## 6.2 ESD Ratings

|             |                         |                                                                                   | VALUE | UNIT |

|-------------|-------------------------|-----------------------------------------------------------------------------------|-------|------|

|             |                         | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup>       | ±4000 |      |

| $V_{(ESD)}$ | Electrostatic discharge | Charged device model (CDM), per JEDEC specification JESD22-C101, all $pins^{(2)}$ | ±500  | V    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

SLVSB25C - AUGUST 2011 - REVISED JUNE 2015

# 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                                                 | MIN  | NOM | MAX | UNIT |

|-------------------------------------------------|------|-----|-----|------|

| VBAT - Supply voltage                           | 2.5  | 3.7 | 4.8 | V    |

| Voltage Range - SDA and SCL                     | -0.1 | 3.3 | 3.6 | V    |

| T <sub>J</sub> - Operating junction temperature | -40  |     | 125 | °C   |

### 6.4 Thermal Information

|                       |                                              | DR                | S<br>°C/W<br>°C/W |      |

|-----------------------|----------------------------------------------|-------------------|-------------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | YFM<br>(PICOSTAR) | YMB (DSBGA)       | UNIT |

|                       |                                              | 6 PINS            | 6 PINS            |      |

| R <sub>0JA</sub>      | Junction-to-ambient thermal resistance       | 130.6             | 116.9             | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 1.4               | 1.4               | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 37                | 22.2              | °C/W |

| $\Psi_{JT}$           | Junction-to-top characterization parameter   | 5.2               | 0.1               | °C/W |

| $\psi_{JB}$           | Junction-to-board characterization parameter | 37                | 22.2              | °C/W |

(1) For more information about traditional and new thermal metrics, see the *Semiconductor and IC Package Thermal Metrics* application report, SPRA953.

## 6.5 Electrical Characteristics

Over recommended free-air temperature range and over recommended input voltage range (typical at an ambient temperature range of 25°C) (unless otherwise noted)

|                       | PARAMETER                                                       | TEST CONDITIONS               | MIN | TYP   | MAX | UNIT        |

|-----------------------|-----------------------------------------------------------------|-------------------------------|-----|-------|-----|-------------|

| INPUT VOL             | TAGE                                                            |                               |     |       |     |             |

| V <sub>BAT</sub>      | Input supply voltage                                            |                               | 2.5 | 3.7   | 4.8 | V           |

|                       |                                                                 | V <sub>BAT</sub> rising       |     |       | 2.2 |             |

| V <sub>UVLO</sub>     | Undervoltage lockout threshold                                  | V <sub>BAT</sub> falling      | 2   |       |     | V           |

| V <sub>HYS</sub>      | Undervoltage lockout hysteresis                                 |                               | 50  | 100   | 250 | mV          |

| INPUT CUP             | RENT                                                            | ·                             | L   |       |     |             |

| I <sub>SHUTDOWN</sub> | Input supply current shutdown, includes switch leakage currents | MAX: V <sub>BAT</sub> = 4.4 V |     | 0.15  | 1   | μA          |

| ISTANDBY              | Input supply current standby, includes switch leakage currents  | MAX: $V_{BAT} = 4.4 V$        |     | 120   | 200 | μA          |

| STARTUP,              | MODE TRANSITIONS, AND SHUTDO                                    | WN                            |     |       |     |             |

| t <sub>1</sub>        | Shutdown to standby                                             |                               |     |       | 100 | μs          |

| t <sub>2</sub>        | Standby to active                                               |                               |     |       | 100 | μs          |

| t <sub>3</sub>        | Active to standby                                               |                               |     |       | 100 | μs          |

| t <sub>4</sub>        | Shutdown time                                                   | Active or standby to shutdown | 0.5 |       | 1   | ms          |

| VCM DRIVI             | ER STAGE                                                        |                               |     |       |     |             |

|                       | Resolution                                                      |                               |     | 10    |     | bits        |

| I <sub>RES</sub>      | Relative accuracy                                               |                               | -10 |       | 10  | LSB         |

|                       | Differential nonlinearity                                       |                               | -1  |       | 1   | LOD         |

|                       | Zero code error                                                 |                               |     | 0     |     | mA          |

|                       | Offset error                                                    | At code 32                    |     |       | 3   | mA          |

|                       | Gain error                                                      |                               |     | ±3    |     | % of<br>FSR |

|                       | Gain error drift                                                |                               |     | 0.3   | 0.4 | %/°C        |

|                       | Offset error drift                                              |                               |     | 0.3   | 0.5 | %/°C        |

| I <sub>MAX</sub>      | Maximum output current                                          |                               |     | 102.3 |     | mA          |

#### **Electrical Characteristics (continued)**

Over recommended free-air temperature range and over recommended input voltage range (typical at an ambient temperature range of 25°C) (unless otherwise noted)

|                      | PARAMETER                                     | TEST CONDITIONS                              | MIN      | ТҮР                | MAX  | UNIT |

|----------------------|-----------------------------------------------|----------------------------------------------|----------|--------------------|------|------|

| I <sub>LIMIT</sub>   | Average VCM current limit                     | See <sup>(1)</sup>                           | 110      | 160                | 240  | mA   |

| IDETCODE             | Minimum VCM code for OPEN and SHORT detection | See <sup>(2)</sup>                           | 256      |                    |      | mA   |

| f <sub>SW</sub>      | Switching frequency                           | Selectable through CONTROL register          | 0.5      |                    | 4    | MHz  |

| V <sub>DRP</sub>     | Internal dropout                              | See <sup>(3)</sup>                           |          |                    | 0.4  | V    |

| L <sub>VCM</sub>     | VCM inductance                                |                                              | 30       |                    | 150  | μH   |

| R <sub>VCM</sub>     | VCM resistance                                |                                              | 11       |                    | 22   | Ω    |

| LENS MO              | /EMENT CONTROL                                |                                              | -        |                    |      |      |

| t <sub>set1</sub>    | Lens settling time                            | ±10% error band                              |          | 2/f <sub>VCM</sub> |      | ms   |

| t <sub>set2</sub>    | Lens settling time                            | ±10% error band                              |          | 1/f <sub>VCM</sub> |      | ms   |

|                      | VCM resonance frequency                       |                                              | 50       |                    | 150  | Hz   |

| f <sub>VCM</sub>     |                                               | When 1/f <sub>VCM</sub> compensation is used | -10%     |                    | 10%  |      |

|                      | VCM resonance frequency tolerance             | When 2/f <sub>VCM</sub> compensation is used | sed -30% |                    | 30%  |      |

| LOGIC I/O            | s (SDA AND SCL)                               |                                              |          |                    |      |      |

|                      | leased by all a second second                 | V = 1.8 V, SCL                               | -4.25    |                    | 4.25 |      |

| I <sub>IN</sub>      | Input leakage current                         | V = 1.8 V, SDA                               | -1       |                    | 1    | μA   |

| R <sub>PullUp</sub>  | I <sup>2</sup> C pull-up resistors            | SDA and SCL pins                             |          | 4.7                |      | kΩ   |

| V <sub>IH</sub>      | Input high level                              | See <sup>(4)</sup>                           | 1.17     |                    | 3.6  | V    |

| V <sub>IL</sub>      | Input low level                               | See <sup>(5)</sup>                           | 0        |                    | 0.63 | V    |

| t <sub>TIMEOUT</sub> | SCL timeout for shutdown detection            |                                              | 0.5      |                    | 1    | ms   |

| R <sub>PD</sub>      | Pull down resistor at SCL line                |                                              |          | 500                |      | kΩ   |

| f <sub>SCL</sub>     | I <sup>2</sup> C clock frequency              |                                              |          |                    | 400  | kHz  |

| INTERNAL             | OSCILLATOR                                    |                                              | •        |                    |      |      |

| f <sub>OSC</sub>     | Internal oscillator                           | $20^{\circ}C \le T_A \le 70^{\circ}C$        | -3%      |                    | 3%   |      |

|                      | Frequency accuracy                            | -40°C ≤ T <sub>A</sub> ≤ 85°C                | -5%      |                    | 5%   |      |

| THERMAL              | SHUTDOWN                                      |                                              | 1        |                    |      |      |

| T <sub>TRIP</sub>    | Thermal shutdown trip point                   |                                              |          | 140                |      | °C   |

|                      |                                               |                                              | 1        |                    |      |      |

(1) During short circuit condition driver current limit comparator will trip and short is detected and driver goes into STANDBY and short flag is set high in the status register.

When testing VCM open or short this is the recommended minimum VCM code (in dec) to be used. (2)

This is the voltage that is needed for the feedback resistor and high side driver. It should be noted that the maximum VCM resistance is (3) limited by this voltage and supply voltage. For example, 3-V supply maximum VCM resistance is: R<sub>VCM</sub> = (V<sub>BAT</sub> - V<sub>DRP</sub>)/I<sub>VCM</sub> = (3 V - $0.4 \text{ V})/102.3 \text{ mA} = 25.4 \Omega.$

During shutdown to standby transition V<sub>IH</sub> low limit is 1.28 V. During shutdown to standby transition V<sub>IL</sub> high limit is 0.51 V. (4)

(5)

#### TEXAS INSTRUMENTS

www.ti.com

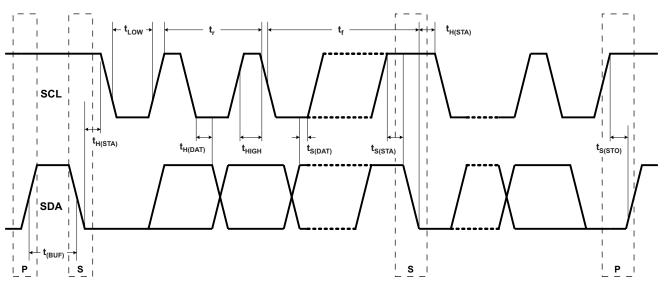

# 6.6 Data Transmission Timing

$V_{BAT}$  = 3.6 V ±5%,  $T_A$  = 25°C,  $C_L$  = 100 pF (unless otherwise noted)

|                     | PARAMETER                                      | TEST CONDITIONS | MIN | ΤΥΡ Μ | ٩X  | UNIT |

|---------------------|------------------------------------------------|-----------------|-----|-------|-----|------|

| f <sub>(SCL)</sub>  | Serial clock frequency                         |                 | 100 | 4     | 00  | kHz  |

| •                   | Due Free Time Detween Step and Start Condition | SCL = 100 KHz   | 4.7 |       |     |      |

| t <sub>BUF</sub>    | Bus Free Time Between Stop and Start Condition | SCL = 400 KHz   | 1.3 |       |     | μs   |

|                     | Toloroble enike width on hue                   | SCL = 100 KHz   |     |       | 50  | 20   |

| t <sub>SP</sub>     | Tolerable spike width on bus                   | SCL = 400 KHz   |     |       |     | ns   |

| +                   | SCL low time                                   | SCL = 100 KHz   | 4.7 |       |     |      |

| t <sub>LOW</sub>    | SCL low lime                                   | SCL = 400 KHz   | 1.3 |       |     | μs   |

|                     |                                                | SCL = 100 KHz   | 4   |       |     | μs   |

| t <sub>HIGH</sub>   | SCL high time                                  | SCL = 400 KHz   | 600 |       |     | ns   |

|                     |                                                | SCL = 100 KHz   | 250 |       |     |      |

| t <sub>S(DAT)</sub> | $SDA \rightarrow SCL$ setup time               | SCL = 400 KHz   | 100 |       |     | ns   |

|                     | Ctart condition actual time                    | SCL = 100 KHz   | 4.7 |       |     | μs   |

| t <sub>S(STA)</sub> | Start condition setup time                     | SCL = 400 KHz   | 600 |       |     | ns   |

|                     |                                                | SCL = 100 KHz   | 4   |       |     | μs   |

| t <sub>S(STO)</sub> | Stop condition setup time                      | SCL = 400 KHz   | 600 |       |     | ns   |

|                     |                                                | SCL = 100 KHz   | 0   | 3.    | 45  |      |

| t <sub>H(DAT)</sub> | $SDA \rightarrow SCL$ hold time                | SCL = 400 KHz   | 0   |       | ).9 | μs   |

|                     | Obert engeliting held time                     | SCL = 100 KHz   | 4   |       |     | μs   |

| t <sub>H(STA)</sub> | Start condition hold time                      | SCL = 400 KHz   | 600 |       |     | ns   |

|                     | Disc time of COL Circal                        | SCL = 100 KHz   |     | 10    | 00  |      |

| t <sub>r(SCL)</sub> | Rise time of SCL Signal                        | SCL = 400 KHz   |     | 3     | 00  | ns   |

|                     |                                                | SCL = 100 KHz   |     | 3     | 00  |      |

| t <sub>f(SCL)</sub> | Fall time of SCL Signal                        | SCL = 400 KHz   |     | 3     | 00  | ns   |

|                     | Disc time of CDA Circal                        | SCL = 100 KHz   |     | 10    | 00  |      |

| t <sub>r(SDA)</sub> | Rise time of SDA Signal                        | SCL = 400 KHz   |     | 3     | 00  | ns   |

|                     | Disc time of CDA Circal                        | SCL = 100 KHz   |     | 3     | 00  |      |

| t <sub>f(SDA)</sub> | Rise time of SDA Signal                        | SCL = 400 KHz   |     | 3     | 00  | ns   |

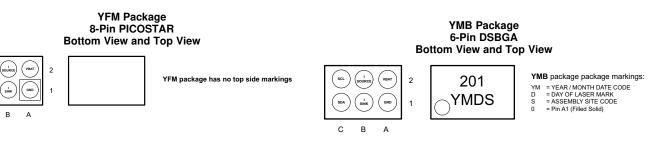

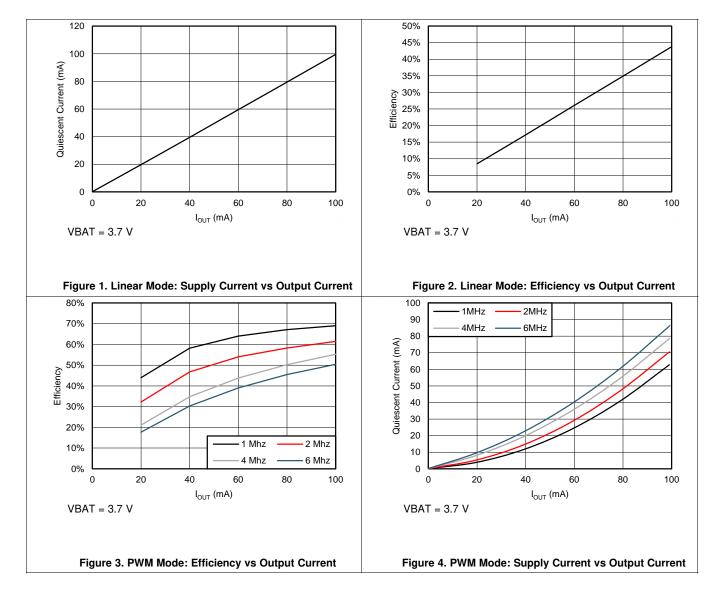

## 6.7 Typical Characteristics

TEXAS INSTRUMENTS

## 7 Detailed Description

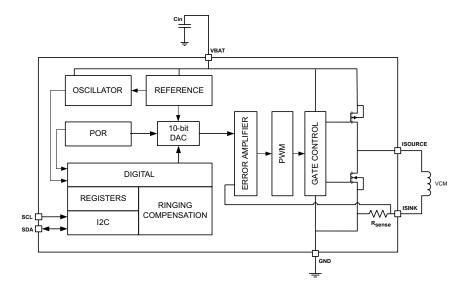

#### 7.1 Overview

The DRV201 device is intended for high performance autofocus in camera modules. The device is used to control the current in the voice coil motor (VCM). The current in the VCM generates a magnetic field which forces the lens stack connected to a spring to move. The VCM current and thus the lens position can be controlled via the I<sup>2</sup>C interface and an auto focus function can be implemented.

The device connects to a video processor or image sensor through a standard I<sup>2</sup>C interface which supports up to 400-kbit/s data rate. The digital interface supports IO levels from 1.8 V to 3.3 V. All pins have 4-kV HBM ESD rating.

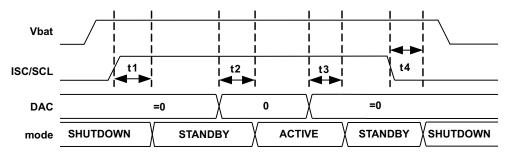

When SCL is low for at least 0.5 ms, the device enters SHUTDOWN mode. If SCL goes from low to high the driver enters STANDBY mode in less than 100 µs and default register values are set as shown in Figure 5. ACTIVE mode is entered whenever the VCM\_CURRENT register is set to something else than zero.

Figure 5. Power-up and Power-down Sequence

VCM current can be controlled via an I<sup>2</sup>C interface and VCM\_CURRENT registers. Lens stack is connected to a spring which causes a dampened ringing in the lens position when current is changed. This mechanical ringing is compensated internally by generating an optimized ramp whenever the current value in the VCM\_CURRENT register is changed. This enables a fast autofocus algorithm and pleasant user experience.

Current in the VCM can be generated with a linear or PWM control. In linear mode the high side PMOS is configured as a current source and current is set by the VCM\_CURRENT control register. In PWM control the VCM is driven with a half bridge driver. With PWM control the VCM current is increased by connecting the VCM between  $V_{BAT}$  and GND through the high side PMOS and then released to a freewheeling mode through the sense resistor and low side NMOS. PWM mode switching frequency can be selected from 0.5 MHz up to 4 MHz through a CONTROL register. PWM or linear mode can be selected with the PWM/LIN bit in the MODE register.

#### 7.2 Functional Block Diagram

#### 7.3 Feature Description

#### 7.3.1 VCM Driver Output Stage Operation

Current in the VCM can be controlled with a linear or PWM mode output stage. Output stage is enabled in ACTIVE mode which can be controlled through VCM\_CURRENT control register and the output stage mode is selected from MODE register bit PWM/LIN.

In linear mode the output PMOS is configured to a high side current source and current can be controlled from a VCM\_CURRENT registers.

In PWM control the VCM is driven with a half bridge driver. With PWM control the VCM current is increased by connecting the VCM between  $V_{BAT}$  and GND through the high side PMOS and then released to a freewheeling mode through the sense resistor and low side NMOS. Current in the VCM is sensed with a 1- $\Omega$  sense resistor which is connected into an error amplifier input where the other input is controlled by the 10-bit DAC output. PWM mode switching frequency can be selected from 0.5 MHz up to 4 MHz through a CONTROL register. PWM or linear mode can be selected with the PWM/LIN bit in the MODE register.

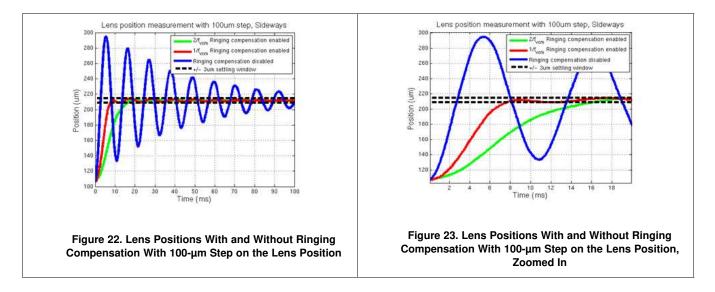

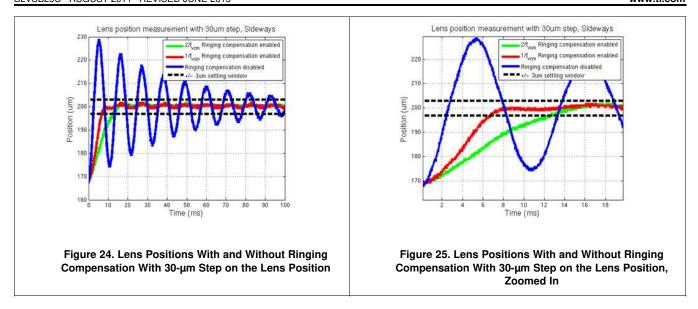

#### 7.3.2 Ringing Compensation

VCM current can be controlled via an I<sup>2</sup>C interface and VCM\_CURRENT registers. Lens stack is connected to a spring which causes a dampened ringing in the lens position when current is changed. This mechanical ringing is compensated internally by generating an optimized ramp whenever the current value in the VCM\_CURRENT register is changed. This enables a fast auto focus algorithm and pleasant user experience.

Ringing compensation is dependent on the VCM resonance frequency, and this can be controlled via VCM\_FREQ register (07h) from 50 Hz up 150 Hz. Table 1 shows the VCM\_FREQ register setting for each resonance frequency in 1-Hz steps. If more accurate resonance frequency is available, the control value can be calculated with Equation 1.

Ringing compensation is designed in a way that it can tolerate  $\pm 30\%$  frequency variation in the VCM resonance frequency when  $2/f_{VCM}$  compensation is used and  $\pm 10\%$  variation with  $1/f_{VCM}$  so only statistical data from the VCM is needed in production.

## Feature Description (continued)

## Table 1. VCM Resonance Frequency Control Register (07h) Table

| VCM                            | VCM_FREQ[7:0] (07h) |          | VCM VCM_FREQ[7:0] (07h)        |     | VCM      | VCM_FREQ[7:0] (07h)            |     |          |

|--------------------------------|---------------------|----------|--------------------------------|-----|----------|--------------------------------|-----|----------|

| RESONANCE<br>FREQUENCY<br>[Hz] | DEC                 | BIN      | RESONANCE<br>FREQUENCY<br>[Hz] | DEC | BIN      | RESONANCE<br>FREQUENCY<br>[Hz] | DEC | BIN      |

| 50                             | 0                   | 0        | 84                             | 154 | 10011010 | 118                            | 220 | 11011100 |

| 51                             | 7                   | 111      | 85                             | 157 | 10011101 | 119                            | 222 | 11011110 |

| 52                             | 14                  | 1110     | 86                             | 160 | 10100000 | 120                            | 223 | 11011111 |

| 53                             | 21                  | 10101    | 87                             | 162 | 10100010 | 121                            | 224 | 11100000 |

| 54                             | 27                  | 11011    | 88                             | 165 | 10100101 | 122                            | 226 | 11100010 |

| 55                             | 34                  | 100010   | 89                             | 167 | 10100111 | 123                            | 227 | 11100011 |

| 56                             | 40                  | 101000   | 90                             | 170 | 10101010 | 124                            | 228 | 11100100 |

| 57                             | 46                  | 101110   | 91                             | 172 | 10101100 | 125                            | 229 | 11100101 |

| 58                             | 52                  | 110100   | 92                             | 174 | 10101110 | 126                            | 231 | 11100111 |

| 59                             | 58                  | 111010   | 93                             | 177 | 10110001 | 127                            | 232 | 11101000 |

| 60                             | 63                  | 111111   | 94                             | 179 | 10110011 | 128                            | 233 | 11101001 |

| 61                             | 68                  | 1000100  | 95                             | 181 | 10110101 | 129                            | 234 | 11101010 |

| 62                             | 73                  | 1001001  | 96                             | 183 | 10110111 | 130                            | 235 | 11101011 |

| 63                             | 78                  | 1001110  | 97                             | 185 | 10111001 | 131                            | 236 | 11101100 |

| 64                             | 83                  | 1010011  | 98                             | 187 | 10111011 | 132                            | 238 | 11101110 |

| 65                             | 88                  | 1011000  | 99                             | 189 | 10111101 | 133                            | 239 | 11101111 |

| 66                             | 92                  | 1011100  | 100                            | 191 | 10111111 | 134                            | 240 | 11110000 |

| 67                             | 96                  | 1100000  | 101                            | 193 | 11000001 | 135                            | 241 | 11110001 |

| 68                             | 101                 | 1100101  | 102                            | 195 | 11000011 | 136                            | 242 | 11110010 |

| 69                             | 105                 | 1101001  | 103                            | 197 | 11000101 | 137                            | 243 | 11110011 |

| 70                             | 109                 | 1101101  | 104                            | 198 | 11000110 | 138                            | 244 | 11110100 |

| 71                             | 113                 | 1110001  | 105                            | 200 | 11001000 | 139                            | 245 | 11110101 |

| 72                             | 116                 | 1110100  | 106                            | 202 | 11001010 | 140                            | 246 | 11110110 |

| 73                             | 120                 | 1111000  | 107                            | 204 | 11001100 | 141                            | 247 | 11110111 |

| 74                             | 124                 | 1111100  | 108                            | 205 | 11001101 | 142                            | 248 | 11111000 |

| 75                             | 127                 | 1111111  | 109                            | 207 | 11001111 | 143                            | 249 | 11111001 |

| 76                             | 130                 | 10000010 | 110                            | 208 | 11010000 | 144                            | 250 | 11111010 |

| 77                             | 134                 | 10000110 | 111                            | 210 | 11010010 | 145                            | 251 | 11111011 |

| 78                             | 137                 | 10001001 | 112                            | 212 | 11010100 | 146                            | 251 | 11111011 |

| 79                             | 140                 | 10001100 | 113                            | 213 | 11010101 | 147                            | 252 | 11111100 |

| 80                             | 143                 | 10001111 | 114                            | 215 | 11010111 | 148                            | 253 | 11111101 |

| 81                             | 146                 | 10010010 | 115                            | 216 | 11011000 | 149                            | 254 | 11111110 |

| 82                             | 149                 | 10010101 | 116                            | 217 | 11011001 | 150                            | 255 | 11111111 |

| 83                             | 152                 | 10011000 | 117                            | 219 | 11011011 | _                              | _   | _        |

### 7.4 Device Functional Modes

#### 7.4.1 Modes of Operation

- **SHUTDOWN** If the driver detects SCL has a DC level below 0.63 V for duration of at least 0.5 ms, the driver will enter SHUTDOWN mode. This is the lowest power mode of operation. The driver will remain in SHUTDOWN for as long as SCL pin remain low.

- **STANDBY** If SCL goes from low to high the driver enters STANDBY mode and sets the default register values. In this mode registers can be written to through the I<sup>2</sup>C interface. Device will be in STANDBY mode when VCM\_CURRENT register is set to zero. From ACTIVE mode the device will enter STANDBY if the SW\_RST bit of the CONTROL register is set. In this case all registers will be reset to default values.

STANDBY mode is entered from ACTIVE mode if any of the following faults occur: Over temperature protection fault (OTPF), VCM short (VCMS), or VCM open (VCMO). When STANDBY mode is entered due to a fault condition current register is cleared.

ACTIVE The device is in ACTIVE mode whenever the VCM\_CURRENT control is set to something else than zero through the I<sup>2</sup>C interface. In ACTIVE mode VCM driver output stage is enabled all the time resulting in higher power consumption. The device remains in ACTIVE mode until the SW\_RST bit in the CONTROL register is set, SCL is pulled low for duration of 0.5 ms, VCM\_CURRENT control is set to zero, or any of the following faults occur: Over temperature protection fault (OTPF), VCM short (VCMS), or VCM open (VCMO). If ACTIVE mode is entered after fault the status register is automatically cleared.

## 7.5 Programming

#### 7.5.1 I<sup>2</sup>C Bus Operation

The I<sup>2</sup>C bus is a communications link between a controller and a series of slave terminals. The link is established using a two-wired bus consisting of a serial clock signal (SCL) and a serial data signal (SDA). The serial clock is sourced from the controller in all cases where the serial data line is bi-directional for data communication between the controller and the slave terminals. Each device has an open drain output to transmit data on the serial data line. An external pullup resistor must be placed on the serial data line to pull the drain output high during data transmission.

The DRV201 hosts a slave I<sup>2</sup>C interface that supports data rates up to 400 kbit/s and auto-increment addressing and is compliant to I<sup>2</sup>C standard 3.

DRV201 supports four different read and two different write operations: single read from a defined location, single read from a current location, sequential read starting from a defined location, sequential read from current location, single write to a defined location, sequential write starting from a defined location. All different read and write operations are described below.

#### 7.5.1.1 Single Write to a Defined Location

Figure 6 shows the format of a single write to a defined register. First, the master issues a start condition followed by a seven-bit I2C address. Next, the master writes a zero to conduct a write operation. Upon receiving an acknowledge from the slave, the master writes the eight-bit register number across the bus. Following a second acknowledge, DRV201 sets the I<sup>2</sup>C register to a defined value and the master writes the eight-bit data value across the bus. Upon receiving a third acknowledge, DRV201 auto increments the internal I<sup>2</sup>C register number by one and the master issues a stop condition. This action concludes the register write.

SINGLE WRITE TO A DEFINED LOCATION

Figure 6. Single Write

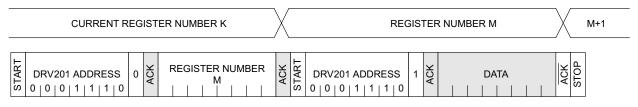

#### 7.5.1.2 Single Read from a Defined Location and Current Location

Figure 7 shows the format of a single read from a defined location. First, the master issues a start condition followed by a seven-bit I<sup>2</sup>C address. Next, the master writes a zero to conduct a write operation. Upon receiving an acknowledge from the slave, the master writes the eight-bit register number across the bus. Following a second acknowledge, DRV201 sets the internal I<sup>2</sup>C register number to a defined value. Then the master issues a repeat start condition and a seven-bit I<sup>2</sup>C address followed by a one to conduct a read operation. Upon receiving a third acknowledge, the master releases the bus to the DRV201. The DRV201 then writes the eight-bit data value from the register across the bus. The master acknowledges receiving this byte and issues a stop condition. This action concludes the register read.

Figure 7. Single Read from a Defined Location

Figure 8 shows the single read from the current location. If the read command is issued without defining the register number first, DRV201 writes out the data from the current register from the device memory.

## Programming (continued)

Figure 8. Single Read from the Current Location

#### 7.5.1.3 Sequential Read and Write

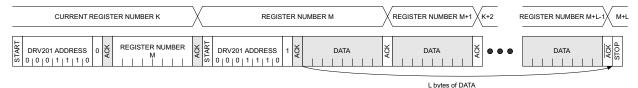

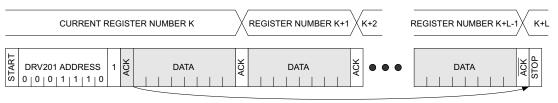

Sequential read and write allows simple and fast access to DRV201 registers. Figure 9 shows sequential read from a defined location. If the master doesn't issue a stop condition after giving ACK, DRV201 auto increments the register number and writes the data from the next register.

Figure 9. Sequential Read from a Defined Location

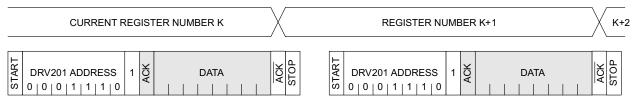

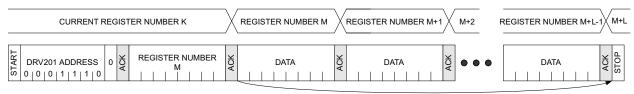

Figure 10 shows the sequential write. If the master doesn't issue a stop condition after giving ACK, DRV201 auto increments it's register by one and the master can write to the next register.

L bytes of DATA

If read is started without writing the register value first, DRV201 writes out data from the current location. If the master doesn't issue a stop condition after giving ACK, DRV201 auto increments the I<sup>2</sup>C register and writes out the data. This continues until the master issues a stop condition. This is shown in Figure 11.

L bytes of DATA

#### **Programming (continued)**

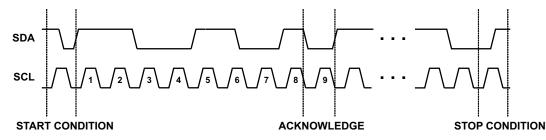

#### 7.5.2 I<sup>2</sup>C Device Address, Start and Stop Condition

Data transmission is initiated with a start bit from the controller as shown in Figure 12. The start condition is recognized when the SDA line transitions from high to low during the high portion of the SCL signal. Upon reception of a start bit, the device will receive serial data on the SDA input and check for valid address and control information. SDA data is latched by DRV201 on the rising edge of the SCL line. If the appropriate device address bits are set for the device, DRV201 issues the ACK by pulling the SDA line low on the next falling edge after 8th bit is latched. SDA is kept low until the next falling edge of the SCL line.

Data transmission is completed by either the reception of a stop condition or the reception of the data word sent to the device. A stop condition is recognized as a low to high transition of the SDA input during the high portion of the SCL signal. All other transitions of the SDA line must occur during the low portion of the SCL signal. An acknowledge is issued after the reception of valid address, sub-address and data words. Reference Figure 13.

Figure 12. I<sup>2</sup>C Start/Stop/Acknowledge Protocol

Figure 13. I<sup>2</sup>C Data Transmission Protocol

### 7.6 Register Maps

#### 7.6.1 Register Address Map

| REGISTER | ADDRESS (HEX) | NAME            | DEFAULT<br>VALUE | DESCRIPTION                          |

|----------|---------------|-----------------|------------------|--------------------------------------|

| 1        | 01            | not used        |                  |                                      |

| 2        | 02            | CONTROL         | 0000 0010        | Control register                     |

| 3        | 03            | VCM_CURRENT_MSB | 0000 0000        | Voice coil motor MSB current control |

| 4        | 04            | VCM_CURRENT_LSB | 0000 0000        | Voice coil motor LSB current control |

| 5        | 05            | STATUS          | 0000 0000        | Status register                      |

| 6        | 06            | MODE            | 0000 0000        | Mode register                        |

| 7        | 07            | VCM_FREQ        | 1000 0011        | VCM resonance frequency              |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

## 7.6.2 Control Register (Control) Address – 0x02h

#### Figure 14. Control Register (Control) Address – 0x02h Map

| DATA BIT          | D7       | D6       | D5       | D4       | D3       | D2       | D1      | D0    |

|-------------------|----------|----------|----------|----------|----------|----------|---------|-------|

| FIELD NAME        | not used | EN_RING | RESET |

| <b>READ/WRITE</b> | R        | R        | R        | R        | R        | R        | R/W     | R/W   |

| RESET VALUE       | 0        | 0        | 0        | 0        | 0        | 0        | 1       | 0     |

### Table 2. Bit Definitions

| FIELD NAME | BIT DEFINITION                                                                                                                                    |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

|            | Forced software reset (reset all registers to default values) and device goes into STANDBY. RESET bit is automatically cleared when written high. |

| RESET      | 0 – inactive                                                                                                                                      |

|            | 1 – device goes to STANDBY                                                                                                                        |

|            | Enables ringing compensation.                                                                                                                     |

| EN_RING    | 0 – disabled                                                                                                                                      |

|            | 1 – enabled                                                                                                                                       |

## 7.6.3 VCM MSB Current Control Register (VCM\_Current\_MSB) Address – 0x03h

## Figure 15. VCM MSB Current Control Register (VCM\_Current\_MSB) Address – 0x03h Map

| DATA BIT    | D7       | D6       | D5       | D4       | D3       | D2       | D1               | D0 |

|-------------|----------|----------|----------|----------|----------|----------|------------------|----|

| FIELD NAME  | not used | VCM_CURRENT[9:8] |    |

| READ/WRITE  | R        | R        | R        | R        | R        | R        | R/W              |    |

| RESET VALUE | 0        | 0        | 0        | 0        | 0        | 0        | 0                | 0  |

#### Table 3. Bit Definitions

| FIELD NAME       | BIT DEFINITION                                                                                                                                                                                             |  |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|                  | VCM current control                                                                                                                                                                                        |  |  |  |  |  |  |

|                  | 00 0000 0000b – 0 mA                                                                                                                                                                                       |  |  |  |  |  |  |

|                  | 00 0000 0001b - 0.1 mA                                                                                                                                                                                     |  |  |  |  |  |  |

|                  | 00 0000 0010b – 0.2 mA                                                                                                                                                                                     |  |  |  |  |  |  |

|                  |                                                                                                                                                                                                            |  |  |  |  |  |  |

|                  | 11 1111 1110b – 102.2 mA                                                                                                                                                                                   |  |  |  |  |  |  |

| VCM_CURRENT[9:8] | 11 1111 1111b – 102.3 mA                                                                                                                                                                                   |  |  |  |  |  |  |

|                  | <b>NOTE</b><br>When setting the current in DRV201 both<br>VCM_CURRENT_MSB and VCM_CURRENT_LSB<br>registers have to be updated. DRV201 starts updates the<br>current after LSB register write is completed. |  |  |  |  |  |  |

## 7.6.4 VCM LSB Current Control Register (VCM\_Current\_LSB) Address – 0x04h

### Figure 16. VCM LSB Current Control Register (VCM\_Current\_LSB) Address – 0x04h Map

| DATA BIT    | D7               | D6 | D5 | D4 | D3 | D2 | D1 | D0 |  |

|-------------|------------------|----|----|----|----|----|----|----|--|

| FIELD NAME  | VCM_CURRENT[7:0] |    |    |    |    |    |    |    |  |

| READ/WRITE  | R/W              |    |    |    |    |    |    |    |  |

| RESET VALUE | 0                | 0  | 0  | 0  | 0  | 0  | 0  | 0  |  |

#### Table 4. Bit Definitions

| FIELD NAME       | BIT DEFINITION                                         |

|------------------|--------------------------------------------------------|

|                  | VCM current control                                    |

|                  | 00 0000 0000b – 0 mA                                   |

|                  | 00 0000 0001b - 0.1 mA                                 |

|                  | 00 0000 0010b – 0.2 mA                                 |

|                  |                                                        |

|                  | 11 1111 1110b – 102.2 mA                               |

| VCM_CURRENT[7:0] | 11 1111 1111b – 102.3 mA                               |

|                  | <b>NOTE</b><br>When setting the current in DRV201 both |

#### 7.6.5 Status Register (Status) Address – 0x05h

## Figure 17. Status Register (Status) Address – 0x05h Map<sup>(1)</sup>

| DATA BIT    | D7       | D6       | D5       | D4  | D3   | D2   | D1   | D0  |

|-------------|----------|----------|----------|-----|------|------|------|-----|

| FIELD NAME  | not used | not used | not used | TSD | VCMS | VCMO | UVLO | OVC |

| READ/WRITE  | R        | R/WR     | R        | R   | R    | R    | R    | R   |

| RESET VALUE | 0        | 0        | 0        | 0   | 0    | 0    | 0    | 0   |

(1) Status bits are cleared when device changes it's state from standby to active. If TSD was tripped the device goes into Standby and will not allow the transition into Active until the device cools down and TSD is cleared.

### Table 5. Bit Definitions

| FIELD NAME | BIT DEFINITION                  |

|------------|---------------------------------|

| OVC        | Over current detection          |

| UVLO       | Undervoltage Lockout            |

| VCMO       | Voice coil motor open detected  |

| VCMS       | Voice coil motor short detected |

| TSD        | Thermal shutdown detected       |

#### 7.6.6 Mode Register (Mode) Address – 0x06h

#### Figure 18. Mode Register (Mode) Address – 0x06h Map

| DATA BIT    | D7       | D6       | D5       | D4            | D3  | D2  | D1      | D0            |

|-------------|----------|----------|----------|---------------|-----|-----|---------|---------------|

| FIELD NAME  | not used | not used | not used | PWM_FREQ[2:0] |     |     | PWM/LIN | RING_MO<br>DE |

| READ/WRITE  | R        | R        | R        | R/W           | R/W | R/W | R/W     | R/W           |

| RESET VALUE | 0        | 0        | 0        | 0             | 0   | 0   | 0       | 0             |

#### Table 6. Bit Definitions

| FIELD NAME    | BIT DEFINITION                            |

|---------------|-------------------------------------------|

|               | Ringing compensation settling time        |

| RING_MODE     | $0-2x(1/f_{VCM})$                         |

|               | $1 - 1x(1/f_{VCM})$                       |

|               | Driver output stage in linear or PWM mode |

| PWM/LIN       | 0 – PWM mode                              |

|               | 1 – Linear mode                           |

|               | Output stage PWM switching frequency      |

|               | 000 – 0.5 MHz                             |

|               | 001 – 1 MHz                               |

|               | 010 – N/A                                 |

| PWM_FREQ[2:0] | 011 – 2 MHz                               |

|               | 100 – N/A                                 |

|               | 101 – 4.8 MHz                             |

|               | 110 – 6.0 MHz                             |

|               | 111 – 4 MHz                               |

#### 7.6.7 VCM Resonance Frequency Register (VCM\_FREQ) Address – 0x07h

#### Figure 19. VCM Resonance Frequency Register (VCM\_FREQ) Address – 0x07h Map

| DATA BIT    | D7            | D6  | D5 | D4 | D3 | D2 | D1 | D0 |  |  |

|-------------|---------------|-----|----|----|----|----|----|----|--|--|

| FIELD NAME  | VCM_FREQ[7:0] |     |    |    |    |    |    |    |  |  |

| READ/WRITE  |               | R/W |    |    |    |    |    |    |  |  |

| RESET VALUE | 1             | 0   | 0  | 0  | 0  | 0  | 1  | 1  |  |  |

NSTRUMENTS

Texas

#### Table 7. Bit Definitions

| FIELD NAME    | BIT DEFINITION                                                                                                                                                                                                     |    |  |  |  |  |  |  |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|--|--|--|--|--|

| VCM_FREQ[7:0] | VCM mechanical ringing frequency for the ringing compensation can be selected with the below formula. The formula gives the VCM_FREQ[7:0] register value in decimal which should be rounded t the nearest integer. | to |  |  |  |  |  |  |

|               | $VCM\_FREQ = 383 - \frac{19200}{F_{res}} $ (1)                                                                                                                                                                     | 1) |  |  |  |  |  |  |

|               | Default VCM mechanical ringing frequency is 76.4 Hz.                                                                                                                                                               |    |  |  |  |  |  |  |

|               | $VCM\_FREQ = 383 - \frac{19200}{76.4} = 131.69 \Rightarrow 132 \Rightarrow '1000\ 0011'$ (2)                                                                                                                       | 2) |  |  |  |  |  |  |

(4)

## 8 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

#### 8.1 Application Information

The DRV201 device is a voice coil motor driver designed for camera auto focus control. The device allows for a highly efficient PWM current control for VCM, while reducing lens ringing in order to significantly lower the time needed for the lens to auto focus. The following design is a common application of the DRV201 device.

#### 8.1.1 VCM Mechanical Ringing Frequency

Ringing compensation is dependent on the VCM resonance frequency, and this can be controlled through the VCM\_FREQ register (07h) from 50 Hz up to 150 Hz. VCM mechanical ringing frequency for the ringing compensation can be selected using Equation 3. The formula gives the VCM\_FREQ[7:0] register value in decimal which should be rounded to the nearest integer.

$$VCM\_FREQ = 383 - \frac{19200}{F_{res}}$$

(3)

Default VCM mechanical ringing frequency is 76.4 Hz.

$$VCM\_FREQ = 383 - \frac{19200}{76.4} = 131.69 \Rightarrow 132 \Rightarrow '1000\ 0011'$$

### 8.2 Typical Application

Figure 20. Typical Application Schematic

TEXAS INSTRUMENTS

www.ti.com

## **Typical Application (continued)**

## 8.2.1 Design Requirements

| Table 0. Design Tatameters  |           |                      |  |  |  |  |  |  |

|-----------------------------|-----------|----------------------|--|--|--|--|--|--|

| DESIGN PARAMETER            | REFERENCE | EXAMPLE VALUE        |  |  |  |  |  |  |

| Supply voltage              | Vin       | 3.7                  |  |  |  |  |  |  |

| Motor Winding<br>Resistance | RL        | 15 Ω                 |  |  |  |  |  |  |

| Motor Winding<br>Inductance | IL        | 100 µH               |  |  |  |  |  |  |

| Actuator Size               |           | 8.5 x 8.5 x 3.4 (mm) |  |  |  |  |  |  |

| Lens in the VCM             |           | M6 (Pitch: 0.35)     |  |  |  |  |  |  |

| Weight of VCM               |           | 75 mg                |  |  |  |  |  |  |

| TTL                         |           | 4.2 mm               |  |  |  |  |  |  |

| FB                          |           | 1.1 mm               |  |  |  |  |  |  |

## **Table 8. Design Parameters**

#### 8.2.2 Detailed Design Procedure

#### 8.2.2.1 User Example 1

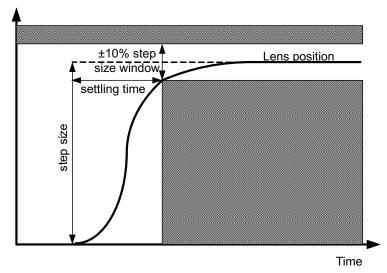

In Figure 21, lens settling time and settling window shows how lens control is defined. Below is an example case how the lens is controlled and what settling time is achieved:

Measured VCM resonance frequency = 100 Hz

• According to Table 1, VCM\_FREQ[7:0] = '10111111' (reg 0x07h)

VCM resonance frequency, f<sub>VCM</sub>, variation is within ±10% (minimum 90 Hz, maximum 110 Hz)

• 1/f<sub>VCM</sub> ringing compensation is used : RING\_MODE = '1' (reg 0x06h)

Stepping the lens by 50 µm

The lens is settled into a ±5-µm window within 10 ms (1/f<sub>VCM</sub>)

#### 8.2.2.2 User Example 2

If the case is otherwise exactly the same, but VCM resonance frequency cannot be guaranteed to stay at more than ±30% variation, slower ringing compensation should be used:

Measured VCM resonance frequency = 100 Hz

• According to Table 1, VCM\_FREQ[7:0] = '10111111' (reg 0x07h)

VCM resonance frequency, f<sub>VCM</sub>, variation is within ±30% (minimum 70 Hz, maximum 130 Hz)

•  $2/f_{VCM}$  ringing compensation is used : RING\_MODE = '0' (reg 0x06h)

Stepping the lens by 50 µm

The lens is settled into a ±5-µm window within 20 ms (2/f<sub>VCM</sub>)

Figure 21. Lens Settling Time and Settling Window

## 8.2.3 Application Curves

NSTRUMENTS

ÈXAS

DRV201 SLVSB25C – AUGUST 2011 – REVISED JUNE 2015

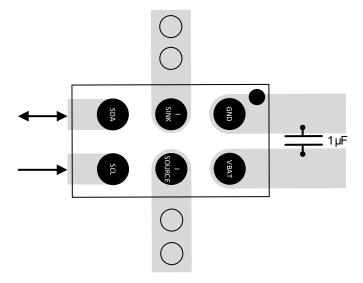

## 9 Power Supply Recommendations

The DRV201 device is designed to operate from an input voltage supply, VBAT, range between 2.5 and 4.8 V. The user must place at least a 1-uF ceramic bypass capacitor rated for a minimum of 6.3 V as close as possible to VBAT and GND pin.

## 10 Layout

### 10.1 Layout Guidelines

The VBAT pin should be bypassed to GND using a low-ESR ceramic bypass capacitor with a recommended value of at least  $1-\mu$ F rated for a minimum of 6.3 V. Place this capacitor as close to the VBAT and GND pins as possible with a thick trace or ground plane connection to the device GND pin.

## 10.2 Layout Example

## **11** Device and Documentation Support

## **11.1 Community Resources**

The following links connect to TI community resources. Linked contents are provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

TI E2E<sup>™</sup> Online Community *TI's Engineer-to-Engineer (E2E) Community.* Created to foster collaboration among engineers. At e2e.ti.com, you can ask questions, share knowledge, explore ideas and help solve problems with fellow engineers.

**Design Support** *TI's Design Support* Quickly find helpful E2E forums along with design support tools and contact information for technical support.

#### 11.2 Trademarks

E2E is a trademark of Texas Instruments. All other trademarks are the property of their respective owners.

#### 11.3 Electrostatic Discharge Caution

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

## 11.4 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

## 12 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

## PACKAGING INFORMATION

| Orderable Device | Status | Package Type | Package | Pins | Package | Eco Plan     | Lead finish/  | MSL Peak Temp      | Op Temp (°C) | Device Marking | Samples |

|------------------|--------|--------------|---------|------|---------|--------------|---------------|--------------------|--------------|----------------|---------|

|                  | (1)    |              | Drawing |      | Qty     | (2)          | Ball material | (3)                |              | (4/5)          |         |

|                  |        |              |         |      |         |              | (6)           |                    |              |                |         |

| DRV201YFMR       | ACTIVE | DSLGA        | YFM     | 6    | 3000    | RoHS & Green | CUNIPD        | Level-1-260C-UNLIM | -40 to 85    |                | Samples |

| DRV201YFMT       | ACTIVE | DSLGA        | YFM     | 6    | 250     | RoHS & Green | CUNIPD        | Level-1-260C-UNLIM | -40 to 85    |                | Samples |

| DRV201YMBR       | ACTIVE | PICOSTAR     | YMB     | 6    | 3000    | RoHS & Green | CUNIPD        | Level-1-260C-UNLIM | -40 to 85    | 201            | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

(5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

(6) Lead finish/Ball material - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:**The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

# PACKAGE OPTION ADDENDUM

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# PACKAGE MATERIALS INFORMATION

www.ti.com

Texas Instruments

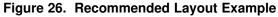

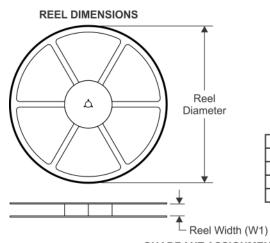

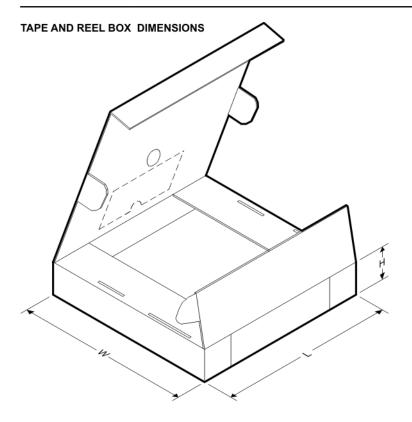

## TAPE AND REEL INFORMATION

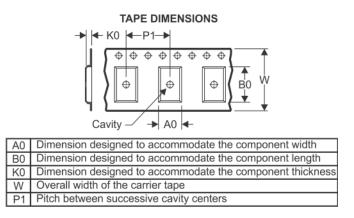

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| *All dimensions are nominal |                 |                    |   |      |                          |                          |            |            |            |            |           |                  |

|-----------------------------|-----------------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| Device                      | Package<br>Type | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

| DRV201YFMR                  | DSLGA           | YFM                | 6 | 3000 | 180.0                    | 8.4                      | 0.85       | 1.52       | 0.19       | 4.0        | 8.0       | Q1               |

| DRV201YFMT                  | DSLGA           | YFM                | 6 | 250  | 180.0                    | 8.4                      | 0.85       | 1.52       | 0.19       | 4.0        | 8.0       | Q1               |

| DRV201YMBR                  | PICOST<br>AR    | YMB                | 6 | 3000 | 180.0                    | 8.4                      | 0.91       | 1.59       | 0.36       | 4.0        | 8.0       | Q1               |

TEXAS INSTRUMENTS

www.ti.com

# PACKAGE MATERIALS INFORMATION

1-Jul-2015

\*All dimensions are nominal

| Device     | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|------------|--------------|-----------------|------|------|-------------|------------|-------------|

| DRV201YFMR | DSLGA        | YFM             | 6    | 3000 | 182.0       | 182.0      | 20.0        |

| DRV201YFMT | DSLGA        | YFM             | 6    | 250  | 182.0       | 182.0      | 20.0        |

| DRV201YMBR | PICOSTAR     | YMB             | 6    | 3000 | 182.0       | 182.0      | 20.0        |

# **MECHANICAL DATA**

- PicoStar™ package configuration. C.

/ The package size (Dimension D and E) of a particular device is specified in the device Product Data Sheet version of this drawing, in case it cannot be found in the product data sheet please contact a local TI representative. Reference Product Data Sheet for array population. 2 x 3 matrix pattern is shown for illustration only. F. This package is a Pb-free solder land design.

PicoStar is a trademark of Texas Instruments.

# **MECHANICAL DATA**

C. PicoStar™ package configuration.

The package size (Dimension D and E) of a particular device is specified in the device Product Data Sheet version of this drawing, in case it cannot be found in the product data sheet please contact a local TI representative.

Reference Product Data Sheet for array population. 2 x 3 matrix pattern is shown for illustration only.

F. This package is a Pb-free solder land design.

PicoStar is a trademark of Texas Instruments.

## IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated