# ARM966E-S<sup>™</sup> 16/32-Bit Flash MCU with Ethernet, USB, CAN, AC motor control, 4 timers, ADC, RTC, DMA

#### ■ 16/32-bit 96 MHz ARM9E based MCU

- ARM966E-S RISC core: Harvard architecture, 5-stage pipeline, Tightly-Coupled Memories (SRAM and Flash)

- STR91xF implementation of core adds highspeed burst Flash memory interface, instruction prefetch queue, branch cache

- Up to 96 MIPS directly from Flash memory

- Single-cycle DSP instructions are supported

- Binary compatible with 16/32-bit ARM7 code

#### ■ Dual burst Flash memories, 32-bits wide

- 256KB/512KB Main Flash, 32KB 2nd Flash

- Sequential Burst operation up to 96 MHz

- 100K min erase cycles, 20 yr min retention

#### ■ SRAM, 32-bits wide

- 64K or 96K bytes, optional battery backup

- 9 programmable DMA channels

- One for Ethernet, eight programmable channels

- Clock, reset, and supply management

- Two supplies required. Core: 1.8 V +/-10%, I/O: 2.7 to 3.6 V

- Internal oscillator operating with external 4-25 MHz crystal

- Internal PLL up to 96MHz

- Real-time clock provides calendar functions, tamper detection, and viake-up functions

Reset Supervisor nonitors voltage supplies,

- watchdog timer, wake-up unit, ext. reset

- Brown-c.t monitor for early warning interrupt Run,  $\sin\epsilon$ , and Sleep Mode as low as 50 uA

## Operating temperature -40 to +85°C

- Vectored interrupt controller (VIC)

- 32 IRQ vectors, 30 intr pins, any can be FIQ

Branch cache minimizes interrupt latency

- 8-channel, 10-bit A/D converter (ADC) - 0 to 3.6V range, 0.7 usec conversion

- 11 Communication interfaces

- 10/100 Ethernet MAC with LNA and MII port

- USB Full-speed (12 Mbos' slave device

- CAN interface (2.03 Active)

- 3 16550-style VARTs with IrDA protocol

- 2 Fast I<sup>2</sup>C<sup>™</sup>, 400 kHz

- 2 charme's for SPI™, SSI™, or Microwire™

- 8/19 bit EMI bus on 128 packages

- ປະການ 80 I/O pins (muxed with interfaces)

- 5 V tolerant, 16 have high sink current (8 mA)

- Bit-wise manipulation of pins within a port

- 16-bit standard timers (TIM)

- 4 timers each with 2 input capture, 2 output compare, PWM and pulse count modes

- 3-Phase induction motor controller (IMC)

- 3 pairs of PWM outputs, adjustable centers

- Emergency stop, dead-time gen, tach input

- JTAG interface with boundary scan

- ARM EmbeddedICE® RT for debugging

- In-System Programming (ISP) of Flash

- Embedded trace module (ARM ETM9)

- Hi-speed instruction tracing, 9-pin interface

1/73

# Contents

| 1          | Intro | action                                                                |  |  |  |

|------------|-------|-----------------------------------------------------------------------|--|--|--|

| 2          | Func  | tional overview                                                       |  |  |  |

|            | 2.1   | System-in-a-Package (SiP)                                             |  |  |  |

|            | 2.2   | Package choice                                                        |  |  |  |

|            | 2.3   | ARM966E-S CPU core                                                    |  |  |  |

|            | 2.4   |                                                                       |  |  |  |

|            |       | Burst Flash memory interface    7      2.4.1    Pre-Fetch Queue (PFQ) |  |  |  |

|            |       | 2.4.2 Branch Cache (BC)                                               |  |  |  |

|            |       | 2.4.3 Management of literals                                          |  |  |  |

|            | 2.5   | 2.4.3 Management of literals    8      SRAM (64K or 96K Bytes)    10  |  |  |  |

|            |       | 2.5.1 Arbitration                                                     |  |  |  |

|            |       | 2.5.2 Battery backup                                                  |  |  |  |

|            | 2.6   | DMA data movement                                                     |  |  |  |

|            | 2.7   | 2.5.2Battery backup10DMA data movement10Non-volatile memories10       |  |  |  |

|            |       | 2.7.1 Primary Flash memory                                            |  |  |  |

|            |       | 2.7.2 Secondary Flash memory                                          |  |  |  |

|            | 2.8   | One-time-programmable (OTP) memory 11                                 |  |  |  |

|            | 2.9   | Vectored interrupt controller (VIC) 11                                |  |  |  |

|            |       | 2.9.1 FIQ handling                                                    |  |  |  |

|            |       | 2.9.2 IRQ handling                                                    |  |  |  |

|            | 10V   | 2.9.3 Interrupt sources                                               |  |  |  |

| G          | 2.10  | Clock control unit (CCU) 14                                           |  |  |  |

| 005        | ,     | 2.10.1 Master clock sources                                           |  |  |  |

| U.         | , A   | 2.10.2 Reference clock (RCLK)                                         |  |  |  |

| 0,05       | 06    | 2.10.3 AHB clock (HCLK)                                               |  |  |  |

| 205        |       | 2.10.4 APB clock (PCLK)                                               |  |  |  |

| <b>O</b> P |       | 2.10.5 Flash memory interface clock (FMICLK)                          |  |  |  |

|            |       | 2.10.6 Baud rate clock (BRCLK)                                        |  |  |  |

|            |       | 2.10.7 External memory interface bus clock (BCLK)                     |  |  |  |

|            |       | 2.10.8 USB interface clock                                            |  |  |  |

|            |       | 2.10.9 Ethernet MAC clock                                             |  |  |  |

|            |       | 2.10.10 External RTC calibration clock                                |  |  |  |

|            |      | 2.10.11 Operation example                                     | . 16 |

|------------|------|---------------------------------------------------------------|------|

|            | 2.11 | Flexible power management                                     | 17   |

|            |      | 2.11.1 Run mode                                               | . 17 |

|            |      | 2.11.2 Idle mode                                              | . 17 |

|            |      | 2.11.3 Sleep mode                                             | . 17 |

|            | 2.12 | Voltage supplies                                              | 18   |

|            |      | 2.12.1 Independent A/D converter supply and reference voltage | . 18 |

|            |      | 2.12.2 Battery supply                                         | . 18 |

|            | 2.13 | System supervisor                                             | 19   |

|            |      | 2.13.1 Supply voltage brownout                                | . 19 |

|            |      | 2.13.2 Supply voltage dropout                                 | . 19 |

|            |      | 2.13.3 Watchdog timer                                         | . 19 |

|            |      | 2.13.4 External RESET_INn pin      2.13.5 Power-up            | . 20 |

|            |      | 2.13.5 Power-up                                               | . 20 |

|            |      | 2.13.6 JTAG debug command                                     | . 20 |

|            |      | 2.13.7 Tamper detection                                       | . 20 |

|            | 2.14 | Real-time clock (RTC)     JTAG interface                      | 20   |

|            | 2.15 | JTAG interface                                                | 21   |

|            |      | 2.15.1 In-system-programming                                  | . 22 |

|            |      | 2.15.2 Boundary scan                                          | . 22 |

|            |      | 2.15.3 CPU debug                                              |      |

|            |      | 2.15.4 JTAG security bit                                      | . 23 |

|            | 2.16 | Embedded trace module (ARM ETM9, v. r2p2)                     | 23   |

|            | 2.17 | Ethernet MAC interface with DMA                               | 24   |

|            | 2.18 | USB 2.0 slave device interface with DMA                       | 24   |

| GC         |      | 2.18.1 Packet buffer interface (PBI)                          | . 25 |

| 00-        |      | 2.18.2 DMA                                                    | . 25 |

|            | , A  | 2.18.3 Suspend mode                                           | . 25 |

| ~          | 2.19 | CAN 2.0B interface                                            | 25   |

| ~05        | 2.20 | UART interfaces with DMA                                      | 26   |

| <b>O</b> P |      | 2.20.1 DMA                                                    | . 26 |

|            | 2.21 | I2C interfaces with DMA                                       | 27   |

|            |      | 2.21.1 DMA                                                    | . 27 |

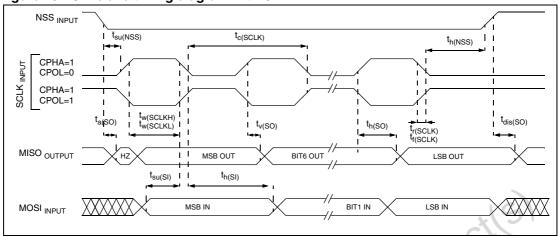

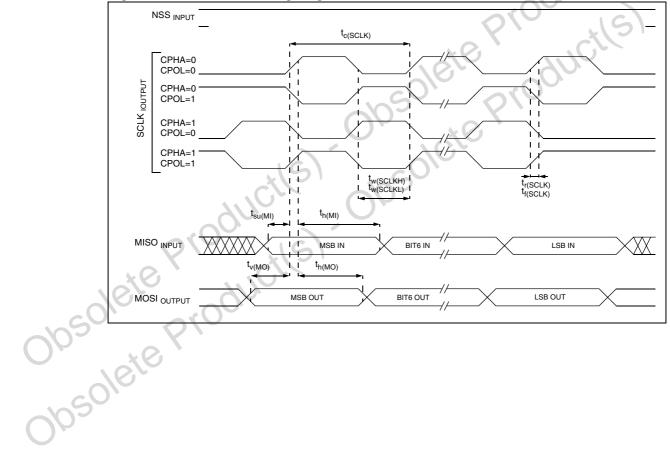

|            | 2.22 | SSP interfaces (SPI, SSI, and Microwire) with DMA             | 27   |

|            |      | 2.22.1 DMA                                                    | . 28 |

57

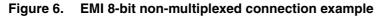

|     | <ul> <li>2.23</li> <li>2.24</li> <li>2.25</li> <li>2.26</li> <li>2.27</li> </ul> | General purpose I/O         A/D converter (ADC)         Standard timers (TIM) with DMA         2.25.1 DMA         Three-phase induction motor controller (IMC)         External memory interface (EMI) | 29<br>29<br>. 30<br>30 |

|-----|----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| 3   |                                                                                  | ed documentation                                                                                                                                                                                       |                        |

| -   |                                                                                  |                                                                                                                                                                                                        |                        |

| 4   | Pin d                                                                            |                                                                                                                                                                                                        | 34                     |

|     | 4.1                                                                              | Default pin functions                                                                                                                                                                                  |                        |

| 5   | Mem                                                                              | ory mapping                                                                                                                                                                                            | 42                     |

|     | 5.1                                                                              | Buffered and non-buffered writes                                                                                                                                                                       | 42                     |

|     | 5.2                                                                              | System (AHB) and peripheral (APB) buses                                                                                                                                                                | 42                     |

|     | 5.3                                                                              | SRAM Two independent Flash memories                                                                                                                                                                    | 42                     |

|     | 5.4                                                                              | Two independent Flash memories                                                                                                                                                                         | 43                     |

|     |                                                                                  | 5.4.1 Default configuration                                                                                                                                                                            | . 43                   |

|     |                                                                                  | 5.4.2 Optional configuration                                                                                                                                                                           | . 43                   |

| 6   | Elect                                                                            | rical characteristics                                                                                                                                                                                  | 46                     |

| ·   | 6.1                                                                              | Absolute maximum ratings                                                                                                                                                                               |                        |

|     | 6.2                                                                              | Operating conditions                                                                                                                                                                                   |                        |

|     | 6.3                                                                              | LVD electrical characteristics                                                                                                                                                                         |                        |

|     | 6.4                                                                              | DC electrical characteristics                                                                                                                                                                          |                        |

| 56  | 6.5                                                                              | AC electrical characteristics                                                                                                                                                                          |                        |

| 002 | 6.6                                                                              | RESET_INn and power-on-reset characteristics                                                                                                                                                           | 50                     |

|     | 6.7                                                                              | Main oscillator electrical characteristics                                                                                                                                                             | 51                     |

| 5   | 6.8                                                                              | RTC oscillator electrical characteristics                                                                                                                                                              | 51                     |

| 005 | 6.9                                                                              | PLL electrical characteristics                                                                                                                                                                         | 52                     |

| U   | 6.10                                                                             | Flash memory characteristics                                                                                                                                                                           | 53                     |

|     | 6.11                                                                             | EMC characteristics                                                                                                                                                                                    | 54                     |

|     |                                                                                  | 6.11.1 Functional EMS (Electro Magnetic Susceptibility)                                                                                                                                                | . 54                   |

|     |                                                                                  | 6.11.2 Electro Magnetic Interference (EMI)                                                                                                                                                             | . 54                   |

|     |                                                                                  | 6.11.3 Absolute Maximum Ratings (Electrical Sensitivity)                                                                                                                                               | . 55                   |

|              |                  | 6.11.4 Electro-Static Discharge (ESD)                      | 55        |

|--------------|------------------|------------------------------------------------------------|-----------|

|              |                  | 6.11.5 Static and Dynamic Latch-Up                         | 55        |

|              |                  | 6.11.6 Designing hardened software to avoid noise problems | 55        |

|              |                  | 6.11.7 Electrical Sensitivities                            | 56        |

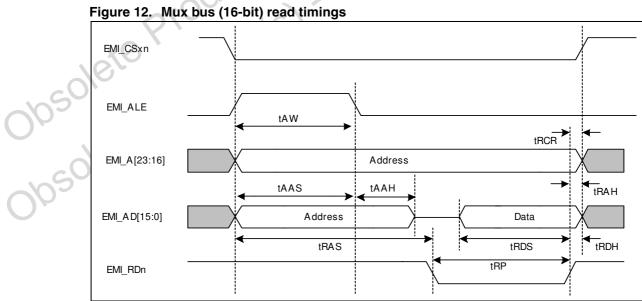

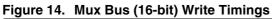

|              | 6.12             | External memory bus timings                                | 56        |

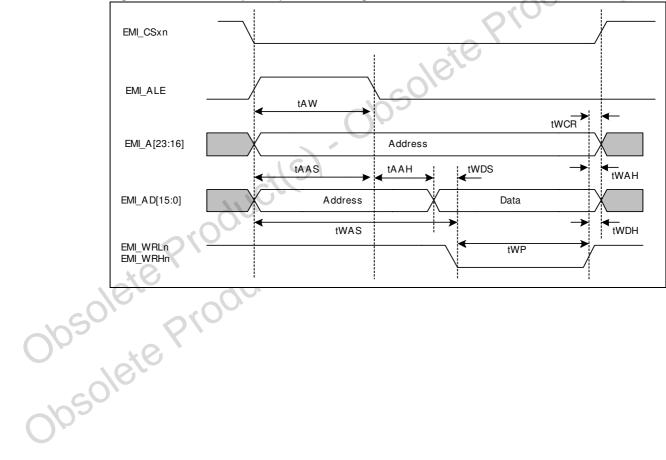

|              | 6.13             | ADC electrical characteristics                             | 60        |

|              | 6.14             | Communication interface electrical characteristics         | 62        |

|              |                  | 6.14.1 10/100 Ethernet MAC electrical characteristics      | 62        |

|              |                  | 6.14.2 USB electrical interface characteristics            | 64        |

|              |                  | 6.14.3 CAN interface electrical characteristics            | 64        |

|              |                  | 6.14.4 I2C electrical characteristics                      |           |

|              |                  | 6.14.5 SPI electrical characteristics                      | 66        |

| 7            | Deela            |                                                            | 60        |

| 7            |                  |                                                            | <b>68</b> |

|              | 7.1              | Thermal characteristics                                    | 69        |

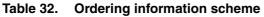

| 8            | Orde             | ring information                                           | 70        |

| -            |                  |                                                            |           |

| 9            | Revis            | sion history                                               | 72        |

|              |                  | Product(S) Obsole                                          |           |

|              | (e <sup>tt</sup> | dul                                                        |           |

| Obst         | let(             | spro                                                       |           |

| 0650<br>0650 | )\-              |                                                            |           |

57

#### Introduction 1

STR91xF is a series of ARM-powered microcontrollers which combines a 16/32-bit ARM966E-S RISC processor core, dual-bank Flash memory, large SRAM for data or code, and a rich peripheral set to form an ideal embedded controller for a wide variety of applications such as point-of-sale terminals, industrial automation, security and surveillance, vending machines, communication gateways, serial protocol conversion, and medical equipment. The ARM966E-S core can perform single-cycle DSP instructions, good for speech processing, audio algorithms, and low-end imaging.

This datasheet provides STR91xF ordering information, functional overview, mechanical information, and electrical device characteristics.

For complete information on STR91xF memory, registers, and peripherals, please refer to the STR91xF Reference Manual.

For information on programming the STR91xF Flash memory please refer to the STR9 Flash **Programming Reference Manual**

For information on the ARM966E-S core, please refer to the ARM966E-S Rev. 2 Technical Nete Reference Manual.

| M32X6         W32X6         M42X6         M44X6         W42X6           Flash         256+32         256+32         512+32         256+32           RAM -         64         96         96         64           Peripheral functions         CAN, 40 I/Os         CAN, EMI, 80 I/Os         USB, CAN, 40 I/Os         Ethernet, USB, 000 | STR912F       |       | 911F   | STR    | R910F   | Features                         |          |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-------|--------|--------|---------|----------------------------------|----------|--|

| Kbytes     256+32     256+32     512+32     256+32       RAM -<br>Kbytes     64     96     96       Peripheral<br>functions     CAN, 40 I/Os     CAN, EMI,<br>80 I/Os     USB, CAN, 40 I/Os     Ethernet, US<br>80       Packages     LQFP80     LQFP128     LQFP80     LQI                                                              | W44X6         | W42X6 | M44X6  | M42X6  | W32X6   | M32X6                            | realures |  |

| Kbytes     64     96       Peripheral<br>functions     CAN, 40 I/Os     CAN, EMI,<br>80 I/Os     USB, CAN, 40 I/Os     Ethernet, US<br>80       Packages     LQFP80     LQFP128     LQFP80     LQI                                                                                                                                       | 256+32 512+32 |       | 512+32 | 256+32 | 6+32    |                                  |          |  |

| functions     CAN, 40 I/OS     80 I/Os     05B, CAN, 40 I/OS     80       Packages     LQFP80     LQFP128     LQFP80     LQI                                                                                                                                                                                                             | 96            |       | 65     | 90     | C       | (                                |          |  |

| dete Product(S)                                                                                                                                                                                                                                                                                                                          | I/Os          |       |        |        | 80 I/Os | Peripheral CAN 40 1/Os CAN, EMI, |          |  |

| psolete Product(S)                                                                                                                                                                                                                                                                                                                       | P128          | LQFF  | P80    | LQF    | LQFP128 | LQFP80                           | Packages |  |

| 10,10                                                                                                                                                                                                                                                                                                                                    |               |       |        |        | 000     | 0                                | SO       |  |

#### Table 1. **Device summary**

# 2 Functional overview

## 2.1 System-in-a-Package (SiP)

The STR91xF is a SiP device, comprised of two stacked die. One die is the ARM966E-S CPU with peripheral interfaces and analog functions, and the other die is the burst Flash. The two die are connected to each other by a custom high-speed 32-bit burst memory interface and a serial JTAG test/programming interface.

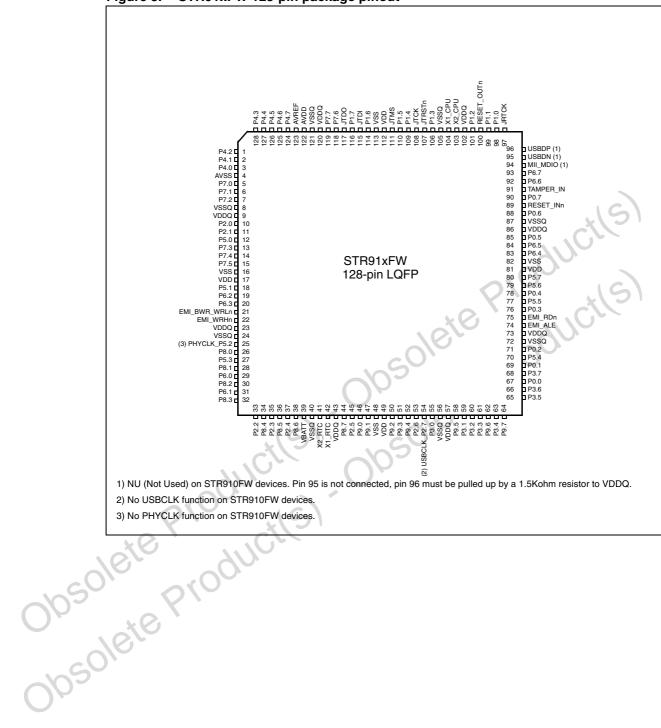

## 2.2 Package choice

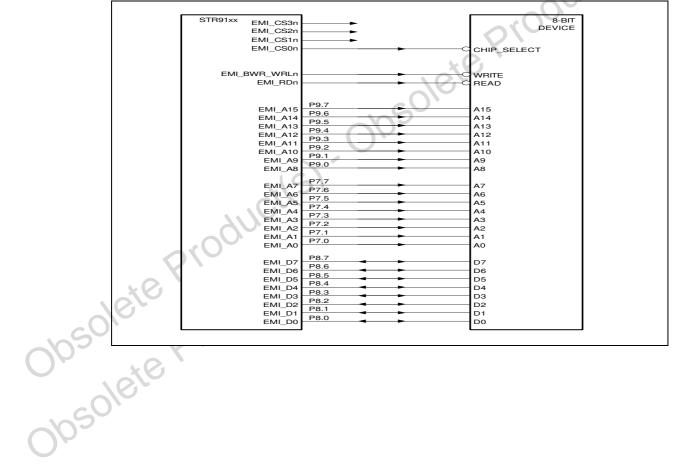

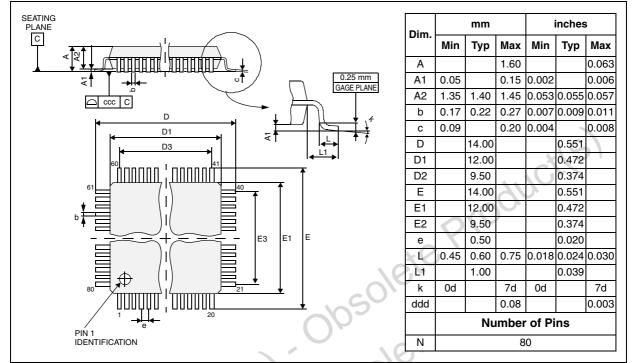

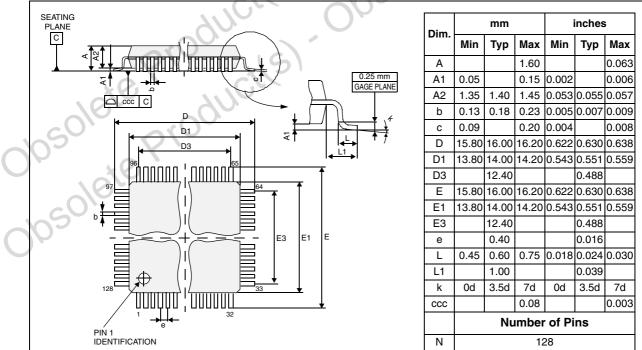

STR91xF devices are available in 128-pin (14 x 14 mm) and 80-pin (12 x 12 mm) LQFP packages. Refer to the *Table 1 on page 6* and to *Table 31 on page 70* for a list of available peripherals for each of the package choices.

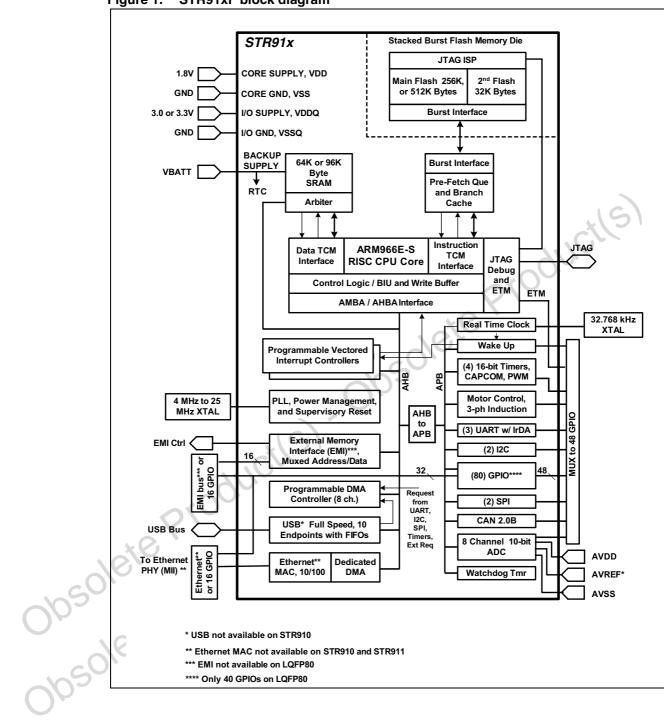

## 2.3 ARM966E-S CPU core

The ARM966E-S core inherently has separate instruction and data memory interfaces (Harvard architecture), allowing the CPU to simultaneously fetch an instruction, and read or write a data item through two Tightly-Coupled Memory (TCM) interfaces as shown in *Figure 1*. The result is streamlined CPU Load and Store operations and a significant reduction in cycle count per instruction. In addition to this, a 5-stage pipeline is used to increase the amount of operational parallelism, giving the most performance out of each clock cycle.

Ten DSP-enhanced instruction extensions are supported by this core, including single-cycle execution of 32x16 Multiply-Accumulate, saturating addition/subtraction, and count leading-zeros.

The ARM966E-S core is binary compatible with 32-bit ARM7 code and 16-bit Thumb<sup>®</sup> code.

## 2.4 Burst Flash memory interface

A Burst Flash memory interface (*Figure 1*) has been integrated into the Instruction TCM (I-TCM) path of the ARM966E-S core. Also in this path is a 4-instruction Pre-Fetch Queue (PFQ) and a 4-entry Branch Cache (BC), enabling the ARM966E-S core to perform up to 96 MIPS while executing code directly from Flash memory. This architecture provides high performance levels without a costly instruction SRAM, instruction cache, or external SDRAM. Eliminating the instruction cache also means interrupt latency is reduced and code execution becomes more deterministic.

#### Pre-Fetch Queue (PFQ)

As the CPU core accesses sequential instructions through the I-TCM, the PFQ always looks ahead and will pre-fetch instructions, taking advantage any idle bus cycles due to variable length instructions. The PFQ will fetch 32-bits at a time from the Burst Flash memory at a rate of up to 96 MHz.

2.4.1

#### 2.4.2 Branch Cache (BC)

When instruction addresses are not sequential, such as a program branch situation, the PFQ would have to flush and reload which would cause the CPU to stall if no BC were present. Before reloading, the PFQ checks the BC to see if it contains the desired target branch address. The BC contains up to four of the most recently taken branch addresses and the first four instructions associated with each of these branches. This check is extremely fast, checking all four BC entries simultaneously for a branch address match (cache hit). If there is a hit, the BC rapidly supplies the instruction and reduces the CPU stall. This gives the PFQ time to start pre-fetching again while the CPU consumes these four instructions from the BC. The advantage here is that program loops (very common with embedded control applications) run very fast if the address of the loops are contained in the BC.

In addition, there is a 5th branch cache entry that is dedicated to the Vectored Interrupt Controller (VIC) to further reduce interrupt latency by eliminating the stall latency typically imposed by fetching the instruction that reads the interrupt vector address from the VIC.

#### 2.4.3 Management of literals

Typical ARM architecture and compilers do not place literals (data constants) sequentially in Flash memory with the instructions that use them, but instead the literals are placed at some other address which looks like a program branch from the PFQ's point of view. The STR91xF implementation of the ARM966E-S core has special circuitry to prevent flushing the PFQ when literals are encountered in program flow to keep performance at a maximum.

## 2.5 SRAM (64K or 96K Bytes)

A 32-bit wide SRAM resides on the CPU's Data TCM (D-TCM) interface, providing single-cycle data accesses. As shown in *Figure 1*, the D-TCM shares SRAM access with the Advanced High-performance Bus (AHB). Sharing is controlled by simple arbitration logic to allow the DMA unit on the AHB to also access to the SRAM.

#### 2.5.1 Arbitration

Zero-wait state access occurs for either the D-TCM or the AHB when only one of the two is requesting SRAM. When both request SRAM simultaneously, access is granted on an interleaved basis so neither requestor is starved, granting one 32-bit word transfer to each requestor before relinquishing SRAM to the other. When neither the D-TCM or the AHB are requesting SRAM, the arbiter leaves access granted to the most recent user (if D-TCM was last to use SRAM then the D-TCM will not have to arbitrate to get access next time).

The CPU may execute code from SRAM through the AHB. There are no wait states as long as the D-TCM is not contending for SRAM access and the AHB is not sharing bandwidth with peripheral traffic. The ARM966E-S CPU core has a small pre-fetch queue built into this instruction path through the AHB to look ahead and fetch instructions during idle bus cycles.

#### 2.5.2 Battery backup

When a battery is connected to the designated battery backup pin (VBATT), SRAM contents are automatically preserved when the normal operating voltage on VDD pins is lost or sags below threshold. Automatic switchover to SRAM can be disabled by firmware if it is desired that the battery will power only the RTC and not the SRAM during standby.

## 2.6 DMA data movement

DMA channels on the Advanced High-performance Bus (AHB) take full advantage of the separate data path provided by the Harvard architecture, moving data rapidly and largely independent of the instruction path. There are two DMA units, one is dedicated to move data between the Ethernet interface and SRAM, the other DMA unit has eight programmable channels with 16 request signals to service other peripherals and interfaces (USB, SSP, I2C, UART, Timers, EMI, and external request pins). Both single word and burst DMA transfers are supported. Memory-to-memory transfers are supported in addition to memory-peripheral transfers. DMA access to SRAM is shared with D-TCM accesses, and arbitration is described in *Section 2.5.1*. Efficient DMA transfers are managed by firmware using linked list descriptor tables. Of the 16 DMA request signals, two are assigned to external inputs. The DMA unit can move data between external devices and resources inside the STR91xF through the EMI bus.

# 2.7

## Non-volatile memories

There are two independent 32-bit wide Burst Flash memories enabling true read-while-write operation. The Flash memories are single-voltage erase/program with 20 year minimum data retention and 100K minimum erase cycles. The primary Flash memory is much larger than the secondary Flash.

Both Flash memories are blank when devices are shipped from ST. The CPU can boot only from Flash memory (configurable selection of which Flash bank).

Flash memories are programmed half-word (16 bits) at a time, but are erased by sector or by full array.

#### 2.7.1 Primary Flash memory

Using the STR91xF device configuration software tool and 3rd party Integrated Developer Environments, it is possible to specify that the primary Flash memory is the default memory from which the CPU boots at reset, or otherwise specify that the secondary Flash memory is the default boot memory. This choice of boot memory is non-volatile and stored in a location that can be programmed and changed only by JTAG In-System Programming. See *Section 5: Memory mapping*, for more detail.

The primary Flash memory has equal length 64K byte sectors. Devices with 256 Kbytes of primary Flash have four sectors and 512K devices have eight sectors.

#### 2.7.2 Secondary Flash memory

The smaller of the two Flash memories can be used to implement a bootloader, capable of storing code to perform robust In-Application Programming (IAP) of the primary Flash memory. The CPU executes code from the secondary Flash, while updating code in the primary Flash memory. New code for the primary Flash memory can be downloaded over any of the interfaces on the STR91xF (USB, Ethernet, CAN, UART, etc.)

Additionally, the Secondary Flash memory may also be used to store small data sets by emulating EEPROM though firmware, eliminating the need for external EEPROM memories. This raises the data security level because passcodes and other sensitive information can be securely locked inside the STR91xF device.

The secondary Flash memory is 32 Kbytes and has four equal length sectors of 8 Kbytes each.

Both the primary Flash memory and the secondary Flash memory can be programmed with code and/or data using the JTAG In-System Programming (ISP) channel, totally independent of the CPU. This is excellent for iterative code development and for manufacturing.

## 2.8 One-time-programmable (OTP) memory

There are 32 bytes of OTP memory ideally suited for serial numbers, security keys, factory calibration constants, or other permanent data constants. These OTP data bytes can be programmed only one time through either the JTAG interface or by the CPU, and these bytes can never be altered afterwards. As an option, a "lock bit" can be set by the JTAG interface or the CPU which will block any further writing to the this OTP area. The "lock bit" itself is also OTP. If the OTP array is unlocked, it is always possible to go back and write to an OTP byte location that has not been previously written, but it is never possible to change an OTP byte location if any one bit of that particular byte has been written before. The last two OTP bytes are reserved for the STR91xF product ID and revision level. Byte 30 contains the device revision level. For STR91xF devices, the revision is 0x13.

## 2.9 Vectored interrupt controller (VIC)

Interrupt management in the STR91xF is implemented from daisy-chaining two standard ARM VIC units. This combined VIC has 32 prioritized interrupt request channels and generates two

interrupt output signals to the CPU. The output signals are FIQ and IRQ, with FIQ having higher priority.

#### 2.9.1 FIQ handling

FIQ (Fast Interrupt reQuest) is the only non-vectored interrupt and the CPU can execute an Interrupt Service Routine (ISR) directly without having to determine/prioritize the interrupt source, minimizing ISR latency. Typically only one interrupt source is assigned to FIQ. An FIQ interrupt has its own set of banked registers to minimize the time to make a context switch. Any of the 32 interrupt request input signals coming into the VIC can be assigned to FIQ.

#### 2.9.2 IRQ handling

IRQ is a vectored interrupt and is the logical OR of all 32 interrupt request signals coming into the 32 IRQ channels. Priority of individual vectored interrupt requests is determined by hardware (IRQ channel Intr 0 is highest priority, IRQ channel Intr 31 is lowest). However, CPU firmware may re-assign individual interrupt sources to individual hardware IRQ channels, meaning that firmware can effectively change interrupt priority levels as needed.

When the IRQ signal is activated by an interrupt request, VIC hardware will resolve the IRQ interrupt priority, then the ISR reads the VIC to determine both the interrupt source and the vector address to jump to the service code.

The STR91xF has a feature to reduce ISR response time for IRQ interrupts. Typically, it requires two memory accesses to read the interrupt vector address from the VIC, but the STR91xF reduces this to a single access by adding a 5th entry in the instruction branch cache, dedicated for interrupts. This 5th cache entry always holds the instruction that reads the interrupt vector address from the VIC, eliminating one of the memory accesses typically required in traditional ARM implementations.

#### 2.9.3 Interrupt sources

The 32 interrupt request signals coming into the VIC on 32 IRQ channels are from various sources; 5 from a wake-up unit and the remaining 27 come from internal sources on the STR91xF such as on-chip peripherals, see *Table 2*. Optionally, firmware may force an interrupt on any IRQ channel.

One of the 5 interrupt requests generated by the wake-up unit (IRQ25 in *Table 2*) is derived from the logical OR of all 32 inputs to the wake-up unit. Any of these 32 inputs may be used to wake up the CPU and cause an interrupt. These 32 inputs consist of 30 external interrupts on selected and enabled GPIO pins, plus the RTC interrupt, and the USB Resume interrupt.

Each of 4 remaining interrupt requests generated by the wake-up unit (IRQ26 in *Table 2*) are derived from groupings of 8 interrupt sources. One group is from GPIO pins P3.2 to P3.7 plus the RTC interrupt and the USB Resume interrupt; the next group is from pins P5.0 to P5.7; the next group is from pins P6.0 to P6.7; and last the group is from pins P7.0 to P7.7. This allows individual pins to be assigned directly to vectored IRQ interrupts or one pin assigned directly to the non-vectored FIQ interrupt.

See *Table 2* for recommended interrupt source assignments to physical IRQ interrupt channels. Interrupt source assignments are made by CPU firmware during initialization, thus establishing interrupt priorities.

|    | VIC IRQ Channel   | Logic Block     | Interrupt Source                                                         |  |  |  |

|----|-------------------|-----------------|--------------------------------------------------------------------------|--|--|--|

|    | 0 (high priority) | WatchDog        | Timeout in WDT mode, Terminal Count in Counter Mode                      |  |  |  |

|    | 1                 | CPU Firmware    | Firmware generated interrupt                                             |  |  |  |

|    | 2                 | CPU Core        | Debug Receive Command                                                    |  |  |  |

|    | 3                 | CPU Core        | Debug Transmit Command                                                   |  |  |  |

|    | 4                 | TIM Timer 0     | Logic OR of ICI0_0, ICI0_1, OCI0_0, OCI0_1, Timer overflow               |  |  |  |

|    | 5                 | TIM Timer 1     | Logic OR of ICI1_0, ICI1_1, OCI1_0, OCI1_1, Timer overflow               |  |  |  |

|    | 6                 | TIM Timer 2     | Logic OR of ICI2_0, ICI2_1, OCI2_0, OCI2_1, Timer overflow               |  |  |  |

|    | 7                 | TIM Timer 3     | Logic OR of ICI3_0, ICI3_1, OCI3_0, OCI3_1, Timer overflow               |  |  |  |

|    | 8                 | USB             | Logic OR of high priority USB interrupts                                 |  |  |  |

|    | 9                 | USB             | Logic OR of low priority USB interrupts                                  |  |  |  |

|    | 10                | CCU             | Logic OR of all interrupts from Clock Control Unit                       |  |  |  |

|    | 11                | Ethernet MAC    | Logic OR of Ethernet MAC interrupts via its own dedicated DMA channel.   |  |  |  |

|    | 12                | DMA             | Logic OR of interrupts from each of the 8 individual DMA channels        |  |  |  |

|    | 13                | CAN             | Logic OR of all CAN interface interrupt sources                          |  |  |  |

|    | 14                | IMC             | Logic OR of 8 Induction Motor Control Unit interrupts                    |  |  |  |

|    | 15                | ADC             | End of AtoD conversion interrupt                                         |  |  |  |

|    | 16                | UART0           | Logic OR of 5 interrupts from UART channel 0                             |  |  |  |

|    | 17                | UART1           | Logic OR of 5 interrupts from UART channel 1                             |  |  |  |

|    | 18                | UART2           | Logic OR of 5 interrupts from UART channel 2                             |  |  |  |

|    | 19                | 12C0            | Logic OR of transmit, receive, and error interrupts of I2C channel 0     |  |  |  |

|    | 20                | I2C1            | Logic OR of transmit, receive, and error interrupts of I2C channel 1     |  |  |  |

|    | 21                | SSP0            | Logic OR of all interrupts from SSP channel 0                            |  |  |  |

|    | 22                | SSP1            | Logic OR of all interrupts from SSP channel 1                            |  |  |  |

|    | 23                | BROWNOUT        | LVD warning interrupt                                                    |  |  |  |

|    | 24                | RTC             | Logic OR of Alarm, Tamper, or Periodic Timer interrupts                  |  |  |  |

| 30 | 25                | Wake-Up (all)   | Logic OR of all 32 inputs of Wake-Up unit (30 pins, RTC, and USB Resume) |  |  |  |

| 50 | 26                | Wake-up Group 0 | Logic OR of 8 interrupt sources: RTC, USB Resume, pins<br>P3.2 to P3.7   |  |  |  |

|    | 27                | Wake-up Group 1 | Logic OR of 8 interrupts from pins P5.0 to P5.7                          |  |  |  |

| SU | 28                | Wake-up Group 2 | Logic OR of 8 interrupts from pins P6.0 to P6.7                          |  |  |  |

|    | 29                | Wake-up Group 3 | Logic OR of 8 interrupts from pins P7.0 to P7.7                          |  |  |  |

|    | 30                | USB             | USB Bus Resume Wake-up (also input to wake-up unit)                      |  |  |  |

|    | 31 (low priority) | PFQ-BC          | Special use of interrupts from Prefetch Queue and Branch Cache           |  |  |  |

Table 2.

Recommended IRQ Channel assignments (set by CPU firmware)

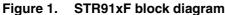

## 2.10 Clock control unit (CCU)

The CCU generates a master clock of frequency  $f_{MSTR}$ . From this master clock the CCU also generates individually scaled and gated clock sources to each of the following functional blocks within the STR91xF.

- CPU, f<sub>CPUCLK</sub>

- Advanced High-performance Bus (AHB), f<sub>HCLK</sub>

- Advanced Peripheral Bus (APB), f<sub>PCLK</sub>

- Flash Memory Interface (FMI), f<sub>FMICLK</sub>

- External Memory Interface (EMI), f<sub>BCLK</sub>

- UART Baud Rate Generators, f<sub>BAUD</sub>

- USB, f<sub>USB</sub>

#### 2.10.1 Master clock sources

The master clock in the CCU (f<sub>MSTR</sub>) is derived from one of three clock input sources. Under firmware control, the CPU can switch between the three CCU inputs without introducing any glitches on the master clock output. Inputs to the CCU are:

- Main Oscillator (f<sub>OSC</sub>). The source for the main oscillator input is a 4 to 25 MHz external crystal connected to STR91xF pins X1\_CPU and X2\_CPU, or an external oscillator device connected to pin X1\_CPU.

- PLL (f<sub>PLL</sub>). The PLL takes the 4 to 25 MHz oscillator clock as input and generates a master clock output up to 96 MHz (programmable). By default, at power-up the master clock is sourced from the main oscillator until the PLL is ready (locked) and then the CPU may switch to the PLL source under firmware control. The CPU can switch back to the main oscillator source at any time and turn off the PLL for low-power operation. The PLL is always turned off in Sleep mode.

- RTC (f<sub>RTC</sub>). A 32.768 kHz external crystal can be connected to pins X1\_RTC and X2\_RTC, or an external oscillator connected to pin X1\_RTC to constantly run the real-time clock unit. This 32.768 kHz clock source can also be used as an input to the CCU to run the CPU in slow clock mode for reduced power.

As an option, there are a number of peripherals that do not have to receive a clock sourced from the CCU. The USB interface can receive an external clock on pin P2.7, TIM timers TIM0/ TIM1 can receive an external clock on pin P2.4, and timers TIM2/TIM3 on pin P2.5.

#### Figure 2. Clock control

#### 2.10.2 Reference clock (RCLK)

The main clock ( $f_{MSTR}$ ) can be divided to operate at a slower frequency reference clock (RCLK) for the ARM core and all the peripherals. The RCLK provides the divided clock for the ARM core, and feeds the dividers for the AHB, APB, External Memory Interface, and FMI units.

#### 2.10.3 AHB clock (HCLK)

The RCLK can be divided by 1, 2 or 4 to generate the AHB clock. The AHB clock is the bus clock for the AHB bus and all bus transfers are synchronized to this clock. The maximum HCLK frequency is 96 MHz.

#### 2.10.4 APB clock (PCLK)

The RCLK can be divided by 1, 2, 4 or 8 to generate the APB clock. The APB clock is the bus clock for the APB bus and all bus transfers are synchronized to this clock. Many of the peripherals that are connected to the AHB bus also use the PCLK as the source for external bus data transfers. The maximum PCLK frequency is 48 MHz.

#### 2.10.5 Flash memory interface clock (FMICLK)

The FMICLK clock is an internal clock derived from RCLK, defaulting to RCLK frequency at power up. The clock can be optionally divided by 2. The FMICLK determines the bus bandwidth between the ARM core and the Flash memory. Typically, codes in the Flash memory can be fetched one word per FMICLK clock in burst mode. The maximum FMICLK frequency is 96MHz.

#### 2.10.6 Baud rate clock (BRCLK)

The baud rate clock is an internal clock derived from  $f_{MSTR}$  that is used by the three on-chip UART peripherals for baudrate generation. The frequency can be optionally divided by 2.

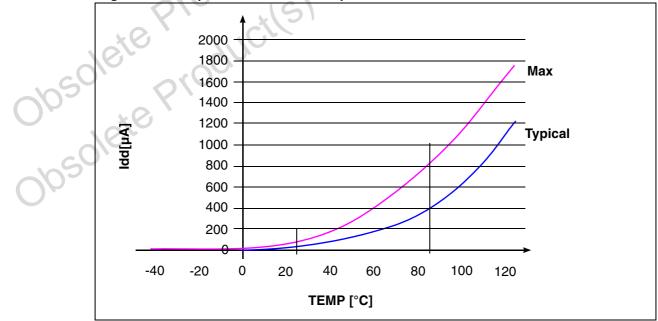

#### 2.10.7 External memory interface bus clock (BCLK)

The BCLK is an internal clock that controls the EMI bus. All EMI bus signals are synchronized to the BCLK. The BCLK is derived from the HCLK and the frequency can be configured to be the same or half that of the HCLK. Refer to *Table 9 on page 50* for the maximum BCLK frequency ( $f_{BCLK}$ ).

#### 2.10.8 USB interface clock

Special consideration regarding the USB interface: The clock to the USB interface must operate at 48 MHz and comes from one of three sources, selected under firmware control:

- CCU master clock output of 48 MHz.

- CCU master clock output of 96 MHz. An optional divided-by-two circuit is available to produce 48 MHz for the USB while the CPU system runs at 96MHz.

- STR91xF pin P2.7. An external 48 MHz oscillator connected to pin P2.7 can directly source the USB while the CCU master clock can run at some frequency other than 48 or 96 MHz.

#### 2.10.9 Ethernet MAC clock

Special consideration regarding the Ethernet MAC: The external Ethernet PHY interface device requires it's own 25 MHz clock source. This clock can come from one of two sources:

- A 25 MHz clock signal coming from a dedicated output pin (P5.2) of the STR91xF. In this case, the STR91xF must use a 25 MHz signal on its main oscillator input in order to pass this 25 MHz clock back out to the PHY device through pin P5.2. The advantage here is that an inexpensive 25 MHz crystal may be used to source a clock to both the STR91xF and the external PHY device.

- An external 25 MHz oscillator connected directly to the external PHY interface device. In this case, the STR91xF can operate independent of 25 MHz.

#### 2.10.10 External RTC calibration clock

The RTC\_CLK ( $f_{RTC/8}$ ) can be enabled as an output on the JRTCK pin. The RTC\_CLK is used for RTC oscillator calibration. The RTC\_CLK is active in Sleep mode and can be used as a system wake up control clock.

## 2.10.11 Operation example

As an example of CCU operation, a 25 MHz crystal can be connected to the main oscillator input on pins X1\_CPU and X2\_CPU, a 32.768 kHz crystal connected to pins X1\_RTC and X2\_RTC, and the clock input of an external Ethernet PHY device is connected to STR91xF output pin P5.2. In this case, the CCU can run the CPU at 96 MHz from PLL, the USB interface at 48 MHz, and the Ethernet interface at 25 MHz. The RTC is always running in the background at 32.768 kHz, and the CPU can go to very low power mode dynamically by running from 32.768 kHz and shutting off peripheral clocks and the PLL as needed.

## 2.11 Flexible power management

The STR91xF offers configurable and flexible power management control that allows the user to choose the best power option to fit the application. Power consumption can be dynamically managed by firmware and hardware to match the system's requirements. Power management is provided via clock control to the CPU and individual peripherals.

Clocks to the CPU and peripherals can be individually divided and gated off as needed. In addition to individual clock divisors, the CCU master clock source going to the CPU, AHB, APB, EMI, and FMI can be divided dynamically by as much as 1024 for low power operation. Additionally, the CCU may switch its input to the 32.768 kHz RTC clock at any time for low power.

The STR91xF supports the following three global power control modes:

- Run Mode: All clocks are on with option to gate individual clocks off via clock mask registers.

- Idle Mode: CPU and FMI clocks are off until an interrupt, reset, or wake-up occurs. Preconfigured clock mask registers selectively allow individual peripheral clocks to continue run during Idle Mode.

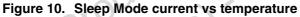

- Sleep Mode: All clocks off except RTC clock. Wake up unit remains powered, PLL is forced off.

A special mode is used when JTAG debug is active which never gates off any clocks even if the CPU enters Idle or Sleep mode.

#### 2.11.1 Run mode

This is the default mode after any reset occurs. Firmware can gate off or scale any individual clock. Also available is a special Interrupt Mode which allows the CPU to automatically run full speed during an interrupt service and return back to the selected CPU clock divisor rate when the interrupt has been serviced. The advantage here is that the CPU can run at a very low frequency to conserve power until a periodic wake-up event or an asynchronous interrupt occurs at which time the CPU runs full speed immediately.

#### 2.11.2 Idle mode

In this mode the CPU suspends code execution and the CPU and FMI clocks are turned off immediately after firmware sets the Idle Bit. Various peripherals continue to run based on the settings of the mask registers that exist just prior to entering Idle Mode. There are 3 ways to exit Idle Mode and return to Run Mode:

- Any reset (external reset pin, watchdog, low-voltage, power-up, JTAG debug command)

- Any interrupt (external, internal peripheral, RTC alarm or interval)

- Input from wake-up unit on GPIO pins

It is possible to remain in Idle Mode for the majority of the time and the RTC can be programmed to periodically wake up to perform a brief task or check status.

#### 2.11.3 Sleep mode

In this mode all clock circuits except the RTC are turned off and main oscillator input pins X1\_CPU and X2\_CPU are disabled. The RTC clock is required for the CPU to exit Sleep Mode. The entire chip is quiescent (except for RTC and wake-up circuitry). There are three means to exit Sleep Mode and re-start the system:

Note:

- Some resets (external reset pin, low-voltage, power-up, JTAG debug command)

- RTC alarm

- Input from wake-up unit

## 2.12 Voltage supplies

The STR91xF requires two separate operating voltage supplies. The CPU and memories operate from a 1.65V to 2.0V on the VDD pins, and the I/O ring operates at 2.7V to 3.6V on the VDDQ pins.

#### 2.12.1 Independent A/D converter supply and reference voltage

The ADC unit on 128-pin packages has an isolated analog voltage supply input at pin AVDD to accept a very clean voltage source, independent of the digital voltage supplies. The analog voltage supply range on pin AVDD is the same range as the digital voltage supply on pin VDDQ. Additionally, an isolated analog supply ground connection is provided on pin AVSS only on 128-pin packages for further ADC supply isolation. On 80-pin packages, the analog voltage supply is shared with the ADC reference voltage pin (as described next), and the analog ground is shared with the digital ground at a single point in the STR91xF device on pin AVSS\_VSSQ.

A separate external analog reference voltage input for the ADC unit is available on 128-pin packages at the AVREF pin for better accuracy on low voltage inputs, and the voltage on AVREF can range from 1.0V to  $V_{DDQ}$ . For 80-pin packages, the ADC reference voltage is tied internally to the ADC unit supply voltage at pin AVCC\_AVREF, meaning the ADC reference voltage is fixed to the ADC unit supply voltage.

#### 2.12.2 Battery supply

An optional stand-by voltage from a battery or other source may be connected to pin VBATT to retain the contents of SRAM in the event of a loss of the V<sub>DD</sub> supply. The SRAM will automatically switch its supply from the internal V<sub>DD</sub> source to the VBATT pin when the voltage of V<sub>DD</sub> drops below that of VBATT.

The VBATT pin also supplies power to the RTC unit, allowing the RTC to function even when the main digital supplies (V<sub>DD</sub> and V<sub>DDQ</sub>) are switched off. By configuring the RTC register, it is possible to select whether or not to power from VBATT only the RTC unit, or power the RTC unit and the SRAM when the STR91xF device is powered off.

## 2.13 System supervisor

The STR91xF monitors several system and environmental inputs and will generate a global reset, a system reset, or an interrupt based on the nature of the input and configurable settings. A global reset clears all functions on the STR91xF, a system reset will clear all but the Clock Control Unit (CCU) settings and the system status register. At any time, firmware may reset individual on-chip peripherals. System supervisor inputs include:

- GR: CPU voltage supply (V<sub>DD</sub>) drop out or brown out

- GR: I/O voltage supply (V<sub>DDQ</sub>) drop out or brown out

- GR: Power-Up condition

- SR: Watchdog timer timeout

- SR: External reset pin (RESET\_INn)

- SR: JTAG debug reset command

- Note: GR: means the input causes Global Reset, SR: means the input causes System Reset

The CPU may read a status register after a reset event to determine if the reset was caused by a watchdog timer timeout or a voltage supply drop out. This status register is cleared only by a power up reset.

#### 2.13.1 Supply voltage brownout

Each operating voltage source ( $V_{DD}$  and  $V_{DDQ}$ ) is monitored separately by the Low Voltage Detect (LVD) circuitry. The LVD will generate an early warning interrupt to the CPU when voltage sags on either  $V_{DD}$  or  $V_{DDQ}$  voltage inputs. This is an advantage for battery powered applications because the system can perform an orderly shutdown before the batteries become too weak. The voltage trip point to cause a brown out interrupt is typically 0.25V above the LVD dropout thresholds that cause a reset.

CPU firmware may prevent all brown-out interrupts by writing to interrupt mask registers at runtime.

## 2.13.2 Supply voltage dropout

LVD circuitry will always cause a global reset if the CPU's  $V_{\text{DD}}$  source drops below it's fixed threshold of 1.4V.

However, the LVD trigger threshold to cause a global reset for the I/O ring's  $V_{DDQ}$  source is set to one of two different levels, depending if  $V_{DDQ}$  will be operated in the range of 2.7V to 3.3V, or 3.0V to 3.6V. If  $V_{DDQ}$  operation is at 2.7V to 3.3V, the LVD dropout trigger threshold is 2.4V. If  $V_{DDQ}$  operation is 3.0V and 3.6V, the LVD threshold is 2.7V. The choice of trigger level is made by STR91xF device configuration software from STMicroelectronics or IDE from 3rd parties, and is programmed into the STR91xF device along with other configurable items through the JTAG interface when the Flash memory is programmed.

CPU firmware may prevent some LVD resets if desired by writing a control register at run-time. Firmware may also disable the LVD completely for lowest-power operation when an external LVD device is being used.

#### 2.13.3 Watchdog timer

The STR91xF has a 16-bit down-counter (not one of the four TIM timers) that can be used as a watchdog timer or as a general purpose free-running timer/counter. The clock source is the

peripheral clock from the APB, and an 8-bit clock pre-scaler is available. When enabled by firmware as a watchdog, this timer will cause a system reset if firmware fails to periodically reload this timer before the terminal count of 0x0000 occurs, ensuring firmware sanity. The watchdog function is off by default after a reset and must be enabled by firmware.

#### 2.13.4 External RESET\_INn pin

This input signal is active-low with hystereses ( $V_{RHYS}$ ). Other open-drain, active-low system reset signals on the circuit board (such as closure to ground from a push-button) may be connected directly to the RESET\_INn pin, but an external pull-up resistor to  $V_{DDQ}$  must be present as there is no internal pullup on the RESET\_INn pin.

A valid active-low input signal of  $t_{RINMIN}$  duration on the RESET\_INn pin will cause a system reset within the STR91xF. There is also a RESET\_OUTn pin on the STR91xF that can drive other system components on the circuit board. RESET\_OUTn is active-low and has the same timing of the Power-On-Reset (POR) shown next,  $t_{POR}$ .

#### 2.13.5 Power-up

The LVD circuitry will always generate a global reset when the STR91xF powers up, meaning internal reset is active until  $V_{DDQ}$  and  $V_{DD}$  are both above the LVD thresholds. This POR condition has a duration of  $t_{POR}$ , after which the CPU will fetch its first instruction from address 0x0000.0000 in Flash memory. It is not possible for the CPU to boot from any other source other than Flash memory.

#### 2.13.6 JTAG debug command

When the STR91xF is in JTAG debug mode, an external device which controls the JTAG interface can command a system reset to the STR91xF over the JTAG channel.

#### 2.13.7 Tamper detection

On 128-pin STR91xF devices only, there is a tamper detect input pin, TAMPER\_IN, used to detect and record the time of a tamper event on the end product such as malicious opening of an enclosure, unwanted opening of a panel, etc. The activation mode of the tamper pin is programmable to one of two modes. One is Normally Closed/Tamper Open, the other mode will detect when a signal on the tamper input pin is driven from low-to-high, or high-to-low depending on firmware configuration. Once a tamper event occurs, the RTC time (millisecond resolution) and the date are recorded in the RTC unit. Simultaneously, the SRAM standby voltage source will be cut off to invalidate all SRAM contents. Tamper detection control and status logic are part of the RTC unit.

## 4 Real-time clock (RTC)

The RTC combines the functions of a complete time-of-day clock (millisecond resolution) with an alarm programmable up to one month, a 9999-year calender with leap-year support, periodic interrupt generation from 1 to 512 Hz, tamper detection (described in *Section 2.13.7*), and an optional clock calibration output on the JRTCK pin. The time is in 24 hour mode, and time/calendar values are stored in binary-coded decimal format.

The RTC also provides a self-isolation mode that is automatically activated during power down. This feature allows the RTC to continue operation when  $V_{DDO}$  and  $V_{DD}$  are absent, as long as

an alternate power source, such as a battery, is connected to the VBATT input pin. The current drawn by the RTC unit on the VBATT pin is very low in this standby mode, I<sub>RTC STBY</sub>.

## 2.15 JTAG interface

An IEEE-1149.1 JTAG interface on the STR91xF provides In-System-Programming (ISP) of all memory, boundary scan testing of pins, and the capability to debug the CPU.

STR91xF devices are shipped from ST with blank Flash memories. The CPU can only boot from Flash memory (selection of which Flash bank is programmable). Firmware must be initially programmed through JTAG into one of these Flash memories before the STR91xF is used.

Six pins are used on this JTAG serial interface. The five signals JTDI, JTDO, JTMS, JTCK, and JTRSTn are all standard JTAG signals complying with the IEEE-1149.1 specification. The sixth signal, JRTCK (Return TCK), is an output from the STR91xF and it is used to pace the JTCK clock signal coming in from the external JTAG test equipment for debugging. The frequency of the JTCK clock signal coming from the JTAG test equipment must be at least 10 times less than the ARM966E-S CPU core operating frequency (f<sub>CPUCLK</sub>). To ensure this, the signal JRTCK is output from the STR91xF and is input to the external JTAG test equipment to hold off transitions of JTCK until the CPU core is ready, meaning that the JTAG equipment cannot send the next rising edge of JTCK until the equipment receives a rising edge of JRTCK from the STR91xF. The JTAG test equipment must be able to interpret the signal JRTCK and perform this adaptive clocking function. If it is known that the CPU clock will always be at least ten times faster than the incoming JTCK clock signal, then the JRTCK signal is not needed.

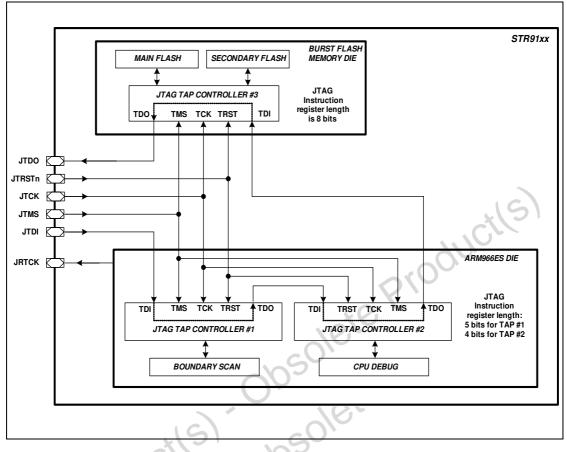

The two die inside the STR91xF (CPU die and Flash memory die) are internally daisy-chained on the JTAG bus, see *Figure 3 on page 22*. The CPU die has two JTAG Test Access Ports (TAPs), one for boundary scan functions and one for ARM CPU debug. The Flash memory die has one TAP for program/erase of non-volatile memory. Because these three TAPs are daisychained, only one TAP will converse on the JTAG bus at any given time while the other two TAPs are in BYPASS mode. The TAP positioning order within this JTAG chain is the boundary scan TAP first, followed by the ARM debug TAP, followed by the Flash TAP. All three TAP controllers are reset simultaneously by one of two methods:

- A chip-level global reset, caused only by a Power-On-Reset (POR) or a Low Voltage Detect (LVD).

- A reset command issued by the external JTAG test equipment. This can be the assertion of the JTAG JTRSTn input pin on the STR91xF or a JTAG reset command shifted into the STR91xF serially.

This means that chip-level system resets from watchdog time-out or the assertion of RESET\_INn pin do not affect the operation of any JTAG TAP controller. Only global resets effect the TAPs.

Figure 3. JTAG chaining inside the STR91xF

#### 2.15.1 In-system-programming

The JTAG interface is used to program or erase all memory areas of the STR91xF device. The pin RESET\_INn must be asserted during ISP to prevent the CPU from fetching invalid instructions while the Flash memories are being programmed.

Note that the 32 bytes of OTP memory locations cannot be erased by any means once programmed by JTAG ISP or the CPU.

## 2.15.2 Boundary scan

Standard JTAG boundary scan testing compliant with IEEE-1149.1 is available on the majority of pins of the STR91xF for circuit board test during manufacture of the end product. STR91xF pins that are not serviced by boundary scan are the following:

- JTAG pins JTCK, JTMS, JTDI, JTDO, JTRSTn, JRTCK

- Oscillator input pins X1 CPU, X2 CPU, X1 RTC, X2 RTC

- Tamper detect input pin TAMPER\_IN (128-pin packages only)

## 2.15.3 CPU debug

The ARM966E-S CPU core has standard ARM EmbeddedICE-RT logic, allowing the STR91xF to be debugged through the JTAG interface. This provides advanced debugging features making it easier to develop application firmware, operating systems, and the hardware itself.

Debugging requires that an external host computer, running debug software, is connected to the STR91xF target system via hardware which converts the stream of debug data and commands from the host system's protocol (USB, Ethernet, etc.) to the JTAG EmbeddedICE-RT protocol on the STR91xF. These protocol converters are commercially available and operate with debugging software tools.

The CPU may be forced into a Debug State by a breakpoint (code fetch), a watchpoint (data access), or an external debug request over the JTAG channel, at which time the CPU core and memory system are effectively stopped and isolated from the rest of the system. This is known as Halt Mode and allows the internal state of the CPU core, memory, and peripherals to be examined and manipulated. Typical debug functions are supported such as run, halt, and single-step. The EmbeddedICE-RT logic supports two hardware compare units. Each can be configured to be either a watchpoint or a breakpoint. Breakpoints can also be data-dependent.

Debugging (with some limitations) may also occur through the JTAG interface while the CPU is running full speed, known as Monitor Mode. In this case, a breakpoint or watchpoint will not force a Debug State and halt the CPU, but instead will cause an exception which can be tracked by the external host computer running monitor software. Data can be sent and received over the JTAG channel without affecting normal instruction execution. Time critical code, such as Interrupt Service Routines may be debugged real-time using Monitor Mode.

#### 2.15.4 JTAG security bit

This is a non-volatile bit (Flash memory based), which when set will not allow the JTAG debugger or JTAG programmer to read the Flash memory contents.

Using JTAG ISP, this bit is typically programmed during manufacture of the end product to prevent unwanted future access to firmware intellectual property. The JTAG Security Bit can be cleared only by a JTAG "Full Chip Erase" command, making the STR91xF device blank and ready for programming again. The CPU can read the status of the JTAG Security Bit, but it may not change the bit value.

## 2.16 Embedded trace module (ARM ETM9, v. r2p2)

The ETM9 interface provides greater visibility of instruction and data flow happening inside the CPU core by streaming compressed data at a very high rate from the STR91xF though a small number of ETM9 pins to an external Trace Port Analyzer (TPA) device. The TPA is connected to a host computer using USB, Ethernet, or other high-speed channel. Real-time instruction flow and data activity can be recorded and later formatted and displayed on the host computer running debugger software, and this software is typically integrated with the debug software used for EmbeddedICE-RT functions such as single-step, breakpoints, etc. Tracing may be triggered and filtered by many sources, such as instruction address comparators, data watchpoints, context ID comparators, and counters. State sequencing of up to three triggers is also provided. TPA hardware is commercially available and operates with debugging software tools.

The ETM9 interface is nine pins total, four of which are data lines, and all pins can be used for GPIO after tracing is no longer needed. The ETM9 interface is used in conjunction with the JTAG interface for trace configuration. When tracing begins, the ETM9 engine compresses the data by various means before broadcasting data at high speed to the TPA over the four data lines. The most common ETM9 compression technique is to only output address information when the CPU branches to a location that cannot be inferred from the source code. This means

the host computer must have a static image of the code being executed for decompressing the ETM9 data. Because of this. self-modified code cannot be traced.

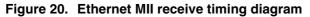

#### Ethernet MAC interface with DMA 2.17

STR91xF devices in 128-pin packages provide an IEEE-802.3-2002 compliant Media Access Controller (MAC) for Ethernet LAN communications through an industry standard Medium Independent Interface (MII). The STR91xF requires an external Ethernet physical interface device (PHY) to connect to the physical LAN bus (twisted-pair, fiber, etc.). The PHY is connected to the STR91xF MII port using as many as 18 signals (see pins which have signal names MII \* in Table 3).

The MAC corresponds to the OSI Data Link layer and the PHY corresponds to the OSI Physical layer. The STR91xF MAC is responsible for:

- Data encapsulation, including frame assembly before transmission, and frame parsing/ error detection during and after reception.

- Media access control, including initiation of frame transmission and recover from transmission failure. te ' nouc'

The STR91xF MAC includes the following features:

- Supports 10 and 100 Mbps rates

- Tagged MAC frame support (VLAN support)

- Half duplex (CSMA/CD) and full duplex operation

- MAC control sublayer (control frames) support

- 32-bit CRC generation and removal

- Several address filtering modes for physical and multicast address (multicast and group addresses)

- 32-bit status code for each transmitted or received frame

- Internal FIFOs to buffer transmit and receive frames. Transmit FIFO depth is 4 words (32 bits each), and the receive FIFO is 16 words deep.

A 32-bit burst DMA channel residing on the AHB is dedicated to the Ethernet MAC for highspeed data transfers, side-stepping the CPU for minimal CPU impact during transfers. This DMA channel includes the following features:

- Direct SRAM to MAC transfers of transmit frames with the related status, by descriptor chain

- Direct MAC to SRAM transfers of receive frames with the related status, by descriptor chain

- Open and Closed descriptor chain management

#### 2.18USB 2.0 slave device interface with DMA

The STR91xF provides a USB slave controller that implements both the OSI Physical and Data Link layers for direct bus connection by an external USB host on pins USBDP and USBPN. The USB interface detects token packets, handles data transmission and reception, and processes handshake packets as required by the USB 2.0 standard.

The USB slave interface includes the following features:

- Supports USB low and full-speed transfers (12 Mbps), certified to comply with the USB 2.0 specification

- Supports isochronous, bulk, control, and interrupt endpoints

- Configurable number of endpoints allowing a mixture of up to 20 single-buffered monodirectional endpoints or up to 10 double-buffered bidirectional endpoints

- Dedicated, dual-port 2 Kbyte USB Packet Buffer SRAM. One port of the SRAM is connected by a Packet Buffer Interface (PBI) on the USB side, and the CPU connects to the other SRAM port.

- CRC generation and checking

- NRZI encoding-decoding and bit stuffing

- USB suspend resume operations

#### 2.18.1 Packet buffer interface (PBI)

The PBI manages a set of buffers inside the 2 Kbyte Packet Buffer, both for transmission and reception. The PBI will choose the proper buffer according to requests coming from the USB Serial Interface Engine (SIE) and locate it in the Packet SRAM according to addresses pointed by endpoint registers. The PBI will also auto-increment the address after each exchanged byte until the end of packet, keeping track of the number of exchanged bytes and preventing buffer overrun. Special support is provided by the PBI for isochronous and bulk transfers, implementing double-buffer usage which ensures there is always an available buffer for a USB packet while the CPU uses a different buffer.

#### 2.18.2 DMA

A programmable DMA channel may be assigned by CPU firmware to service the USB interface for fast and direct transfers between the USB bus and SRAM with little CPU involvement. This DMA channel includes the following features:

- Direct USB Packet Buffer SRAM to system SRAM transfers of receive packets, by descriptor chain for bulk or isochronous endpoints.

- Direct system SRAM to USB Packet Buffer SRAM transfers of transmit packets, by descriptor chain for bulk or isochronous endpoints.

- Linked-list descriptor chain support for multiple USB packets

#### 2.18.3 Suspend mode

CPU firmware may place the USB interface in a low-power suspend mode when required, and the USB interface will automatically wake up asynchronously upon detecting activity on the USB pins.

## CAN 2.0B interface

The STR91xF provides a CAN interface complying with CAN protocol version 2.0 parts A and B. An external CAN transceiver device connected to pins CAN\_RX and CAN\_TX is required for connection to the physical CAN bus.

The CAN interface manages up to 32 Message Objects and Identifier Masks using a Message SRAM and a Message Handler. The Message Handler takes care of low-level CAN bus activity such as acceptance filtering, transfer of messages between the CAN bus and the Message

2.19

SRAM, handling of transmission requests, and interrupt generation. The CPU has access to the Message SRAM via the Message Handler using a set of 38 control registers.

The follow features are supported by the CAN interface:

- Bitrates up to 1 Mbps

- Disable Automatic Retransmission mode for Time Triggered CAN applications

- 32 Message Objects

- Each Message Object has its own Identifier Mask

- Programmable FIFO mode

- Programmable loopback mode for self-test operation

The CAN interface is not supported by DMA.

#### 2.20 UART interfaces with DMA

The STR91xF supports three independent UART serial interfaces, designated UART0, UART1, and UART2. Each interface is very similar to the industry-standard 16C550 UART device. All three UART channels support IrDA encoding/decoding, requiring only an external LED transceiver to pins UARTx\_RX and UARTx\_Tx for communication. One UART channel (UART0) supports full modem control signals.

UART interfaces include the following features:

- Maximum baud rate of 1.5 Mbps

- Separate FIFOs for transmit and receive, each 16 deep, each FIFO can be disabled by firmware if desired

- Programmable FIFO trigger levels between 1/8 and 7/8

- Programmable baud rate generator based on CCU master clock, or CCU master clock divided by two

- Programmable serial data lengths of 5, 6, 7, or 8 bits with start bit and 1 or 2 stop bits

- Programmable selection of even, odd, or no-parity bit generation and detection

- False start-bit detection

- Line break generation and detection

- Support of IrDA SIR ENDEC functions for data rates of up to 115.2K bps

- IrDA bit duration selection of 3/16 or low-power (1.14 to 2.23 µsec)

- Channel UART0 supports modem control functions CTS, DCD, DSR, RTS, DTR, and RI

For your reference, only two standard 16550 UART features are not supported, 1.5 stop bits and independent receive clock.

#### 2.20.1 DMA

A programmable DMA channel may be assigned by CPU firmware to service channels UART0 and UART1 for fast and direct transfers between the UART bus and SRAM with little CPU involvement. Both DMA single-transfers and DMA burst-transfers are supported for transmit and receive. Burst transfers require that UART FIFOs are enabled.

## 2.21 I<sup>2</sup>C interfaces with DMA

The STR91xF supports two independent I2C serial interfaces, designated I2C0, and I2C1. Each interface allows direct connection to an I2C bus as either a bus master or bus slave device (firmware configurable). I2C is a two-wire communication channel, having a bidirectional data signal and a single-directional clock signal based on open-drain line drivers, requiring external pull-up resistors.

Byte-wide data is transferred between a Master device and a Slave device on two wires. More than one bus Master is allowed, but only one Master may control the bus at any given time. Data is not lost when another Master requests the use of a busy bus because I2C supports collision detection and arbitration. More than one Slave device may be present on the bus, each having a unique address. The bus Master initiates all data movement and generates the clock that permits the transfer. Once a transfer is initiated by the Master, any device that is addressed is considered a Slave. Automatic clock synchronization allows I2C devices with different bit rates to communicate on the same physical bus. A single device can play the role of Master or Slave, or a single device can be a Slave only. A Master or Slave device has the ability to suspend data transfers if the device needs more time to transmit or receive data.

Each I2C interface on the STR91xF has the following features:

- Programmable clock supports various rates up to I2C Standard rate (100 KHz) or Fast rate (400 KHz).

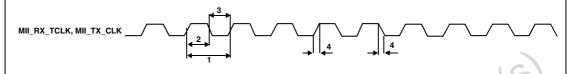

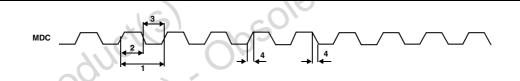

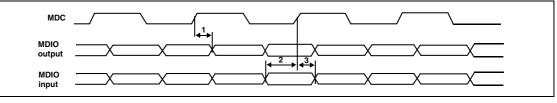

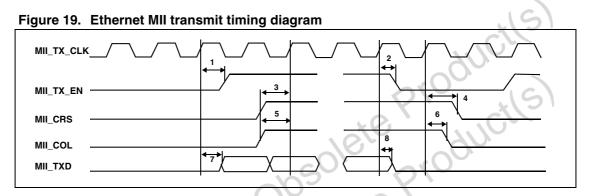

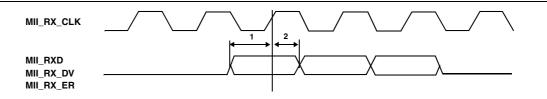

- Serial I/O Engine (SIOE) takes care of serial/parallel conversion; bus arbitration; clock generation and synchronization; and handshaking